# "Certification of Macros and Memories for VLSI in Nanometer Technology"

A Major Project Report

Submitted in Partial Fulfillment of the Requirements

For the Degree of

# Master of Technology

IN

**Electronics & Communication Engineering**

(VLSI Design)

By

Jani Rachna Dhaval

(05MEC006)

Department of Electronics & Communication Engineering Institute of Technology Nirma University of Science & Technology Ahmedabad-382481 May 2007

# "Certification of Macros and Memories for VLSI in Nanometer Technology"

A Major Project Report

Submitted in Partial Fulfillment of the Requirements

For the Degree of

# Master of Technology

# IN

**Electronics & Communication Engineering**

(VLSI Design)

By

Jani Rachna Dhaval (05MEC006)

Under the Guidance of Mr. Shiv Om Sharma Prof. Senior Design Engineer Institu S.T.Microelectronics, Nirma Greater Noida Ahme

Prof. Amisha Naik Institute of Technology, Nirma University, Ahmedabad

Department of Electronics & Communication Engineering Institute of Technology Nirma University of Science & Technology Ahmedabad-382481 May 2007

#### ACKNOWLEDGEMENT

I would like to express my sincere thanks to Mr. Jwalant Joshipura, Section Manager, Testing Certification and Design Support (TCD) group, of S.T. Microelectronics, Noida, for providing me an opportunity to carry out my project work at the TCD group.

I would like to express my profound gratitude to my project guide Mr. Shiv Om Sharma, Team Leader, Library Certification Team of S.T. Microelectronics, Noida, for his outstanding support and guidance throughout the course of the Project work.

I would like to express my sincere thanks to Ms. Swati Mattoo and Mr. Apurva Chaure for their constant help during my learning phase. I am especially grateful for their limitless patience and encouragement during trying times.

I would like to express my heart-felt thanks to my internal project guide Mrs. Amisha Naik for her kind guidance and support during the project.

I would also like to express my sincere thanks to the Course Coordinator Dr. N.M. Devashrayee for his support and encouragement at every moment of the Major Project.

My sincere thanks to all my team members of the Library Certification Team especially, Ms. Lipika Parwani, Mr. Varinder Kumar, Mr. RipuTapan Singh, Mr. Suresh Godavarthy, Mr. Rishi Sharma, Mrs. Sonia Sharma, Ms. Neha Agrawal, Mr. Sachin Gupta for their time to time help and guidance during the course of the project.

I would also like to express my sincere thanks to the professors at the Institute of Technology, Nirma University, Ahmedabad especially Prof. N.P.Gajjar, Prof. D.A. Pujara, Prof. Usha S. Mehta and Prof. M. A. Upadhayay for providing me very good foundations which have proved useful throughout my studies and project work.

I would like to thank Ms. Niti Awasthi, Ms. Renuka Patel, Ms. Krupaxi Patel and for their kind support during the project work.

Finally, I would like to thank my family members for their constant encouragements and support.

#### (Jani Rachna Dhaval)

iii

# TABLE OF CONTENTS

| Project Title                                                                                                                                                                                                 | i                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Acknowledgement                                                                                                                                                                                               | iii                                    |

| Abstract                                                                                                                                                                                                      | X                                      |

| Nomenclature                                                                                                                                                                                                  | xi                                     |

| About ST Microelectronics                                                                                                                                                                                     | xiv                                    |

| CHAPTER :1 INTRODUCTION                                                                                                                                                                                       | 1                                      |

| 1.1 Introduction To Certification                                                                                                                                                                             | 2                                      |

| 1.2 IO Libraries                                                                                                                                                                                              | 3                                      |

| 1.3 Memories                                                                                                                                                                                                  | 4                                      |

| 1.4 Analog and Mixed Signal Libraries                                                                                                                                                                         | 4                                      |

| 1.5 CORE Libraries                                                                                                                                                                                            | 4                                      |

| CHAPTER : 2 PLACE AND ROUTE FLOW                                                                                                                                                                              | 5                                      |

| 2.1 Overview                                                                                                                                                                                                  | 6                                      |

| 2.2 Methods of Certification                                                                                                                                                                                  | 7                                      |

| 2.3 Design Entry                                                                                                                                                                                              | 7                                      |

| 2.4 PAR Flow<br>2.4.1 Avanti Design Flow<br>2.4.1.1 Design Setup<br>2.4.1.2 Floorplan<br>2.4.1.3 Placement<br>2.4.1.4 Clock Tree Synthesis                                                                    | <b>8</b><br>10<br>10<br>12<br>13<br>14 |

| <ul><li>2.4.1.5 Routing</li><li>2.4.1.6 Finish Design</li><li>2.4.2 Benefits of the Astro</li><li>2.4.3 Magma PAR Flow</li></ul>                                                                              | 15<br>16<br>18<br>18                   |

| <ul> <li>2.4.3.1 Optimization Features</li> <li>2.4.3.2 Placement Features</li> <li>2.4.3.3 Routing Features</li> <li>2.4.3.4 Clock Tree Features</li> <li>2.4.4 Benefits of the Magma Design Tool</li> </ul> | 20<br>21<br>21<br>21<br>21<br>22       |

| CHAPTER: 3 SIGNOFF FLOW                           | 23        |

|---------------------------------------------------|-----------|

| 3.1 Introduction                                  | 24        |

| 3.2 Formality                                     | 28        |

| 3.3 DRC                                           | 29        |

| 3.4 LVS                                           | 29        |

| 3.5 Extraction                                    | 30        |

| 3.6 Delay Calculation                             | 31        |

| 3.7 Timing Calculation                            | 31        |

| 3.8 Back-Annotation                               | 32        |

| <b>CHAPTER : 4 ANALYSIS OF RESULTS</b>            | 34        |

| 4.1 Macro Libraries                               | 35        |

| 4.1.1 Design Entry and Netlist generation         | 35        |

| 4.1.2 PAR Flow                                    | 40        |

| 4.1.2.1 Flow Setup                                | 41        |

| 4.1.3 Signoff Flow<br>4.1.3.1 Formality           | 49<br>49  |

| 4.1.3.2 Verification                              | 49<br>50  |

| 4.1.3.3 Extraction                                | 51        |

| 4.1.3.4 Delay Calculation                         | 52        |

| 4.2 Memory                                        | 53        |

| 4.2.1 PAR Flow                                    | 56        |

| 4.2.2 Signoff flow                                | 63        |

| 4.2.2.1 Delay Analysis<br>4.2.2.2 Timing Analysis | 63<br>64  |

|                                                   |           |

| 4.3 STD Cell Libraries                            | <b>66</b> |

| 4.3.1 PAR Flow                                    | 70<br>79  |

| 4.3.2 Signoff flow<br>4.3.2.1 Delay Analysis      | 79<br>79  |

| 4.3.2.2 Timing Analysis                           | 79<br>79  |

| 4.4 Method-1 Certification                        | 81        |

| 4.4.1 Back-Annotation for Verilog Models          | 85        |

| 4.4.2 SPIVsCDL Check                              | 89        |

| <b>CHAPTER : 5 CONCLUSION AND FUTURE SCOPE</b> | 90 |

|------------------------------------------------|----|

| 5.1 Conclusion                                 | 91 |

| 5.2 Future Scope                               | 91 |

| References                                     | 92 |

# LIST OF FIGURES

| Fig. No.       | Title                               | Page No. |

|----------------|-------------------------------------|----------|

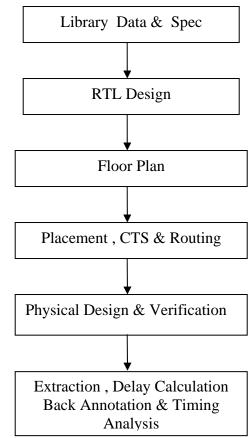

| Fig. 2.1.1     | Certification Execution Process     | 06       |

| Fig. 2.4.1.1   | Avanti Design Flow                  | 10       |

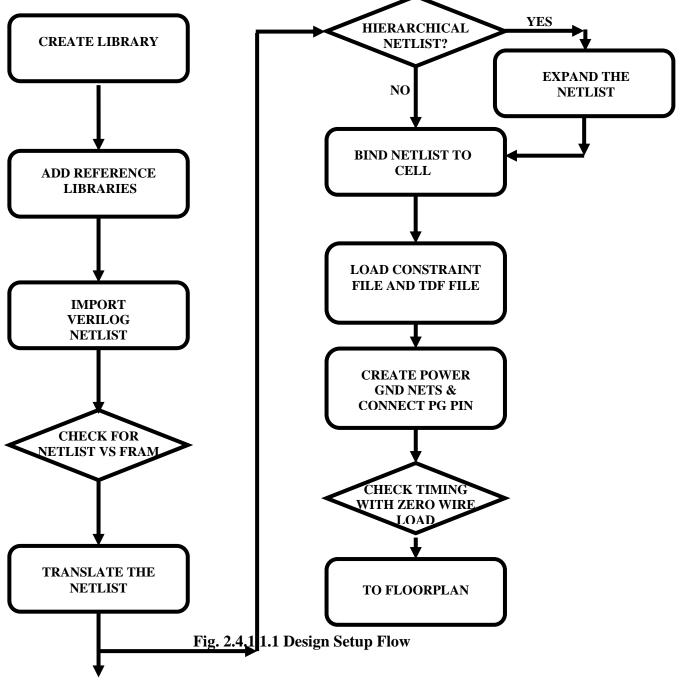

| Fig. 2.4.1.1.1 | Design Setup Flow                   | 11       |

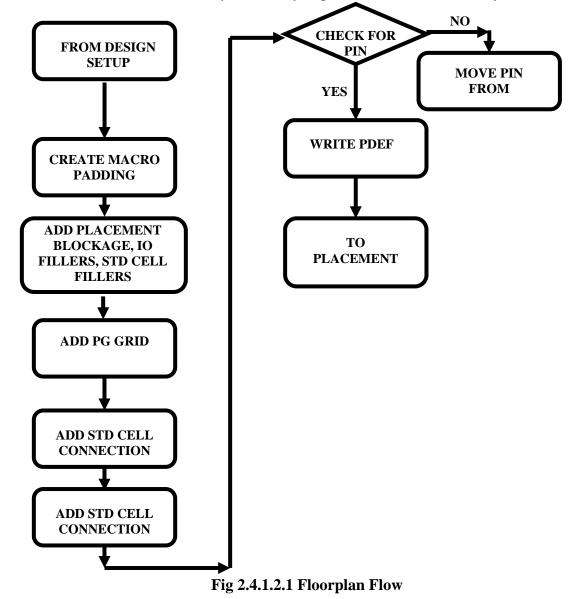

| Fig 2.4.1.2.1  | Floorplan Flow                      | 12       |

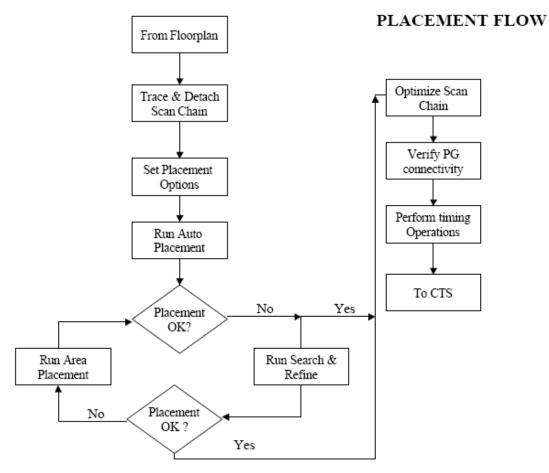

| Fig. 2.4.1.3.1 | Placement Flow                      | 13       |

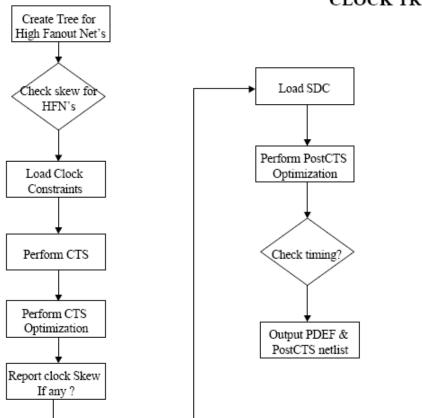

| Fig.2.4.1.4.1  | Clock Tree Synthesis                | 14       |

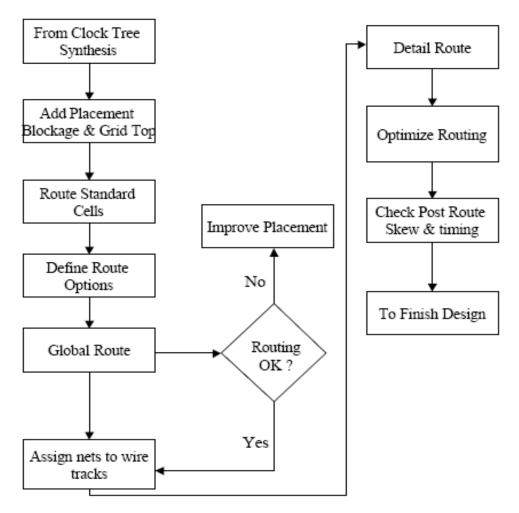

| Fig. 2.4.1.5.1 | Routing Flow                        | 16       |

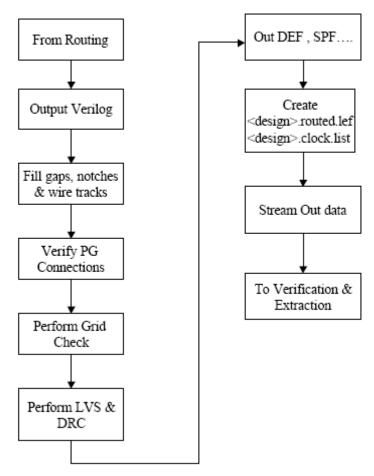

| Fig. 2.4.1.6.1 | Finish Design Flow                  | 17       |

| Fig. 2.4.2.1   | Magma Design Flow                   | 19       |

| Fig. 2.4.2.2   | Blast Fusion Design Flow            | 20       |

| Fig.3.1        | Signoff Flow                        | 24       |

| Fig. 3.1.2     | Netlist & Layout Verification Tasks | 26       |

| Fig. 3.1.3     | Delay Calculation Tasks             | 27       |

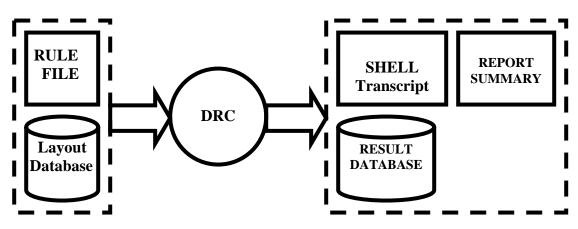

| Fig. 3.3.1     | DRC Data Flow                       | 29       |

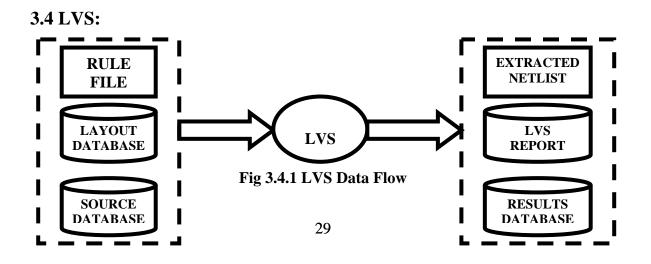

| Fig 3.4.1      | LVS Data Flow                       | 29       |

| Fig .4.1.1     | RTL Netlist                         | 36       |

| Fig 4.1.2      | Verilog Netlist                     | 38       |

| Fig 4.1.3      | Standard Design Constraints         | 40       |

| Fig. 4.1.2.1.1 | Layout of Macro after Import Design | 42       |

| Fig. 4.1.2.1.2 | Layout of Macros after Floorplan    | 43       |

| Fig. 4.1.2.1.3 | Layout of Macros Post Routing       | 44       |

| Fig 4.1.2.1.4  | Gate level netlist (CERT_COMP.v)    | 45       |

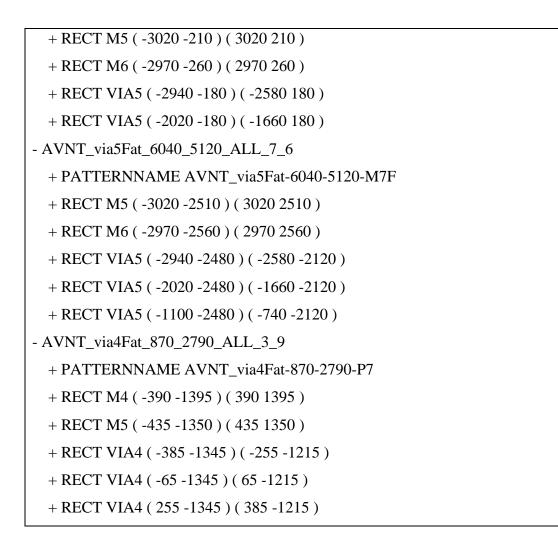

| Fig. 4.1.2.1.5 | CERT_COMP.Routed.def                | 46       |

| Fig. 4.2.1     | CERT_MEM.ref.v                      | 53       |

| Fig. 4.2.2     | CERT_MEM.sdc                        | 55       |

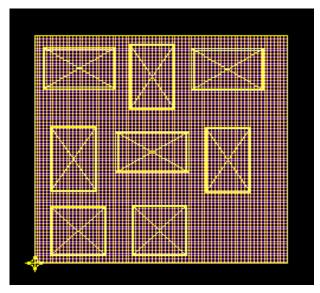

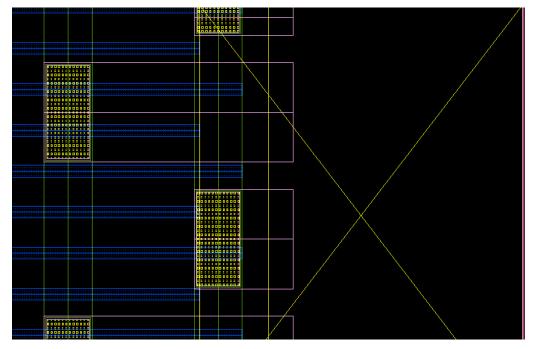

| Fig.4.2.1.1    | Abstract view of SPUHD9gp_2048*8m16 | 56       |

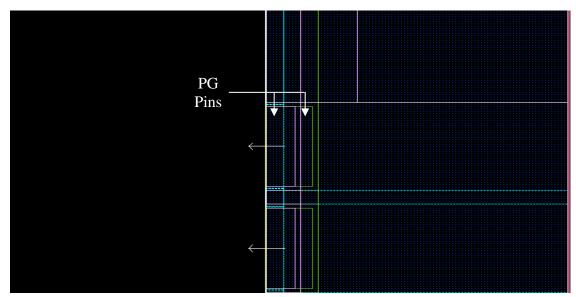

| Fig. 4.2.1.2   | After PG Routing                    | 57       |

| Fig. 4.2.1.3   | After PG Routing                    | 58       |

|                |                                     |          |

| Fig. 4.2.1.4   | CERT_MEM.v                         | 58 |

|----------------|------------------------------------|----|

| Fig.4.2.1.5    | CERT_MEM.routed.def                | 61 |

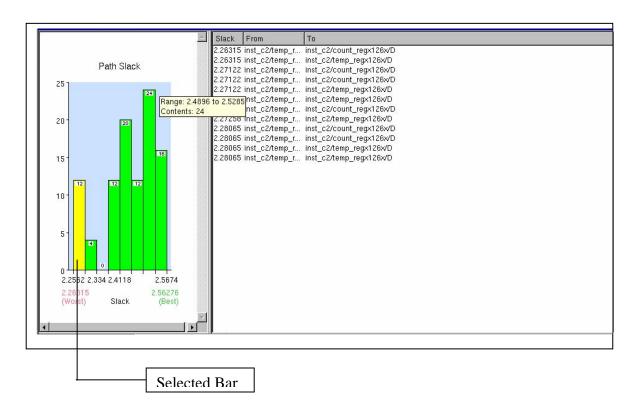

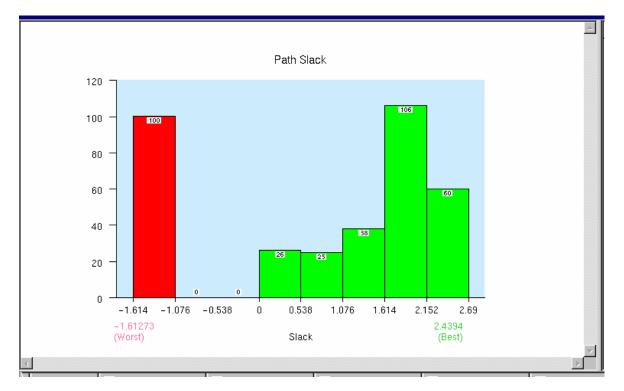

| Fig. 4.2.2.2.1 | Path Slack                         | 65 |

| Fig. 4.3.1     | cert_65hv_gate.v                   | 66 |

| Fig. 4.3.2     | cert_65hv.sdc                      | 69 |

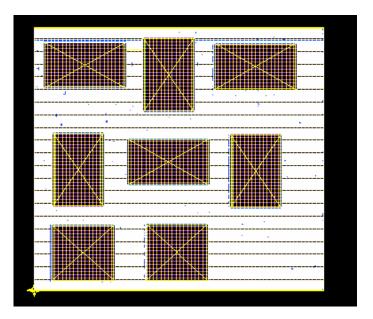

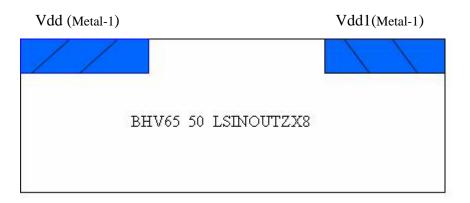

| Fig 4.3.1.2    | BHV65_50_LSINOUTZX8                | 71 |

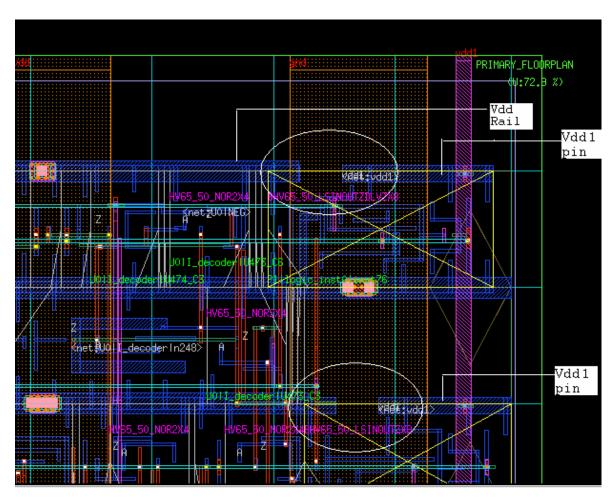

| Fig. 4.3.1.2   | After PG Routing (Magma view)      | 71 |

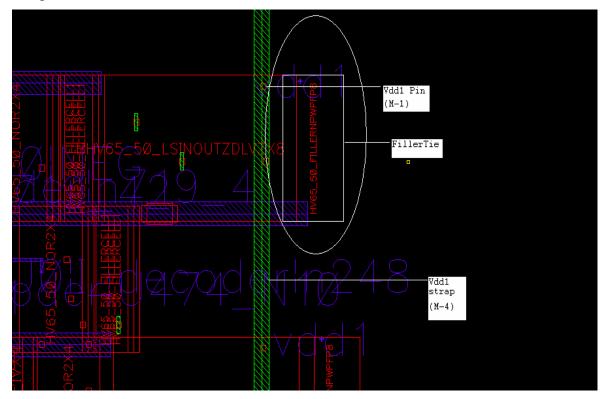

| Fig. 4.3.1.3   | OPUS view after adding filler tie  | 72 |

| Fig.4.3.1.4    | cert_65hv.v                        | 72 |

| Fig. 4.3.1.5   | cert_65hv.routed.def               | 75 |

| Fig. 4.3.1.6   | cert_65hv.routed.lef               | 76 |

| Fig. 4.3.2.2.1 | Path Slack for above table         | 80 |

| Fig. 4.4.1     | .synopsys_pt.setup file            | 82 |

| Fig. 4.4.2     | command file                       | 83 |

| Fig. 4.4.1.1   | Verilog module for Back-annotation | 85 |

| Fig. 4.4.1.2   | .synopsys_dc.setup file            | 85 |

| Fig. 4.4.1.3   | cds.lib file                       | 87 |

| Fig. 4.4.1.4   | sdf_command file                   | 88 |

----

# LIST OF TABLES

| Table no.       | Title                                              | Page no. |

|-----------------|----------------------------------------------------|----------|

| Table 3.1.1     | The tools to be used for SignOff Flow              | 25       |

| Table 4.2.2.1.1 | Delay Analysis for memory                          | 63       |

| Table 4.2.2.2.1 | Analysis Coverage for memory (Uncertainty 0.5 ns)  | 64       |

| Table 4.2.2.2.2 | Analysis Coverage for memory (Period – 8 ns)       | 64       |

| Table 4.2.2.2.3 | Analysis Coverage for memory (Period – 10 ns)      | 65       |

| Table 4.3.2.1.1 | Delay Analysis                                     | 79       |

| Table 4.3.2.2.1 | Annotation Coverage                                | 79       |

| Table 4.3.2.2.2 | Analysis Coverage for Std_cell (Period – 4 ns)     | 80       |

| Table 4.3.2.2.3 | Analysis Coverage for Std_cell (Period – 6 ns)     | 80       |

| Table 4.3.2.2.4 | Analysis Coverage for Std_cell (Period – 8 ns)     | 81       |

| Table 4.3.2.2.5 | Analysis Coverage for Std_cell (Period – 12 ns)    | 81       |

| Table 4.3.2.2.6 | Analysis Coverage for Std_cell (Uncertainty 0.2ns) | 81       |

#### ABSTRACT

In the domain of deep submicron (DSM) and nanometer ASIC technologies (180 nm and below), the traditional separation between logical (synthesis) and physical (place and route) design methods often causes a problem—designs cannot meet their realistic timing objectives; creating the well known "timing closure problem". Timing closure is now considered the biggest area of difficulty for ASIC performance-oriented designs. The underlying reason is that circuit delays are dominated by net delays, which are influenced by the placement of the cells. The traditional fanout-based wireload models, for estimating interconnect delay during synthesis, are considered inaccurate and are the key factor causing the lack of timing predictability between post synthesis and post layout results. It is evident that synthesis and placement technologies must merge to create properly placed and routable designs that meet realistic performance goals.

This thesis described Certification of different libraries. Hereby Certification flow and issues faced during Certification are discussed.

Certification of libraries is defined as the process of certifying an Intellectual Property (I.P.) through various design flows. Inputs to the certification process are the cell views available in libraries. These cell views are schematic, layout, symbol and abstract of the various combinational and sequential logic blocks. To make logical design CORE library is also required. The process starts by generating a gate level netlist using the cells available in the library to be certified. Next, the place and route flow operations like floorplanning, placement, clock tree synthesis (CTS), post CTS optimization, routing and post-route optimization are performed on this netlist to generate the layout at each and every level of flow. Ultimately, the post-routed design is fed to the finish design flow, wherein, the gdscad file (GDS-II) is generated along with some other files which are useful for the signoff flow of the design. By Signoff, one can do the operations like Formality Verification, DRC, LVS, Delay Calculation, Timing Analysis, Backannotation and many more. The aim of certification is to verify that the libraries when violations regarding used won't create timing closure. area constraints.

# Nomenclature

Different companies might use different terminology for designs and their components. To understand Astro, it is needed to understand how these terms are used at Synopsys:

| Term      | Definition                                                              |

|-----------|-------------------------------------------------------------------------|

| Abstract  | Abstract is a view which has pin, pin text information and blockage     |

|           | information. In Avanti/Astro flow, an abstract is referred to as        |

|           | FRAM.                                                                   |

| Block     | The meaning of block depends on the context in which the term is        |

|           | used.                                                                   |

|           | • In the logical hierarchy, a block is also called a module,            |

|           | logic block, or sub-block.                                              |

|           | • In the physical hierarchy, a block is also called a cluster,          |

|           | physical block, or floorplan block.                                     |

| Blockage  | Rectangular areas in which cells cannot be placed. A soft blockage      |

|           | allows cells to be added for optimization; a hard blockage does not     |

|           | allow cells to be added for optimization.                               |

| Cluster   | Partitioning of cells in a design on a physical chip, used to guide the |

|           | layout tools and optimization commands. Clusters in the hierarchy       |

|           | for the top level must match the hierarchy for the logic modules in     |

|           | the top level. Clusters are sometimes called physical blocks or         |

|           | floorplan blocks. Clusters have hard boundaries.                        |

| Core Area | The area where standard cells are placed.                               |

| Die Area  | The silicon area of the chip.                                           |

| DRC       | The DRC performs physical verification of integrated circuit design.    |

|           | It performs dimensions and spacing checks based on process design       |

|           | rules ensuring successful fabrication. Design rule checking differs     |

|           | between the logic and physical domains.                                 |

|           | • Logic domain: Timing design rule constraints that must be             |

|           | met before further optimization for skew and insertion                  |

|           | delay; examples are fanout, transition, and capacitance.                |

- Physical domain: Wire spacing and so forth.

- Filler CellFiller cell is defined as a physical-only cell used by silicon vendors<br/>to fill open areas in the rows to make sure all power nets are<br/>connected. Usually this is done after placement is complete.

- **Floorplanning** In floorplanning, the estimation of sizes and setting of initial relative locations of the various blocks in the ASIC is done. The floorplan is the physical description of an ASIC.

- **GDS-II** A **GDS-II** (Graphic Design Station) file is a binary file with the layout information.

- Hot SpotA place in the floorplan that is highly congested with highswitching activity leading to more power dissipation.

- LayoutLayout is the Physical description of the cell (or macros) with all<br/>the layer information. In Avanti flow, a layout is referred to as CEL.

- **LEF LEF** is a textual representation of abstract view. It contains site information at library level and cell level information.

- Legalized Cell A placed cell that does not overlap other cells or blockages and is placed on a legal site location. Different die technologies have different rules that specify which cells are legal and where.

- LegalizedA placement in which no row contains more cells than the numberPlacementof sites available. All cells are placed on legal locations, snapped to<br/>the site array grid.

- .lib .lib contains the text representation of a unidata with some additional library information. TIM : .lib representation in Avanti, TLF: .lib representation in SE.

- LVS LVS ensures equivalence between layout and schematic in terms of devices and connectivity.

- NetlistNetlist is defined as the description of the logic cells and theirinterconnection. The netlist is the logical description of an ASIC.

- **Pin** The input and output of cells within a design (such as gates and flip-flops). The ports of a sub-design are pins within the parent design.

| Placement             | Placement defines the location of the logic cells within the flexible    |

|-----------------------|--------------------------------------------------------------------------|

|                       | blocks and sets aside space for interconnection to each logic cell.      |

| pLib                  | pLib is Physical library which contains library information.             |

| Port                  | The inputs and outputs of a design. Port direction is designated as      |

|                       | input, output, or inout.                                                 |

| <b>RC</b> Correlation | The process of comparing RC parameters before and after routing          |

|                       | and then tuning RC parameter values to reflect the true wire delays.     |

| Schematic             | Schematic is the representation of a cell at the transistor level. CDL   |

|                       | is the text description of the Schematic. E.g., A SPICE code for an      |

|                       | inverter.                                                                |

| sLib                  | sLib is the text representation of the symbol view.                      |

| Spare Cell            | A logic gate added to a design to allow quick logic changes to be        |

|                       | made without replacing all mask layers of the chip. Spare cells exist    |

|                       | in the netlist and the input PDEF. Spare cells are not the same as       |

|                       | filler cells.                                                            |

| SPF                   | Standard Parasitic Format describes the interconnect delay and           |

|                       | loading due to parasitic resistance and capacitance. There are three     |

|                       | forms of SPF: regular SPF, reduced SPF and detailed SPF.                 |

| Symbol                | Symbol is a pictorial representation of a cell.                          |

| Unidata               | Unidata is a view which contains timing and constraints                  |

|                       | information, input capacitance information, logical information,         |

|                       | SDF (Standard Delay Format) and vital mapping for each cell in the       |

|                       | library.                                                                 |

| Unit Tile Cell        | The smallest unit of placement. The width of the unit tile is the        |

|                       | metal-2 pitch. The height is the standard cell height, unless you are    |

|                       | using double-, triple-, and multiple-height cells. Each standard cell    |

|                       | library contains a unit tile cell. There is no need to redefine the unit |

|                       | tile cell when using double-, triple-, and multiple-height cells.        |

| View                  | A View is defined as a representation of a cell in various levels of     |

|                       | abstraction.                                                             |

#### **About ST Microelectronics**

STMicroelectronics is a global independent semiconductor company and is a leader in developing and delivering semiconductor solutions across the spectrum of microelectronics applications. An unrivaled combination of silicon and system expertise, manufacturing strength, Intellectual Property (IP) portfolio and strategic partners positions the Company at the forefront of System-on-Chip (SOC) technology and its products play a key role in enabling today's convergence trends.

ST is one of the world's largest semiconductor companies. In 2004, ST's net revenues were US\$8,760 million and net earnings were US\$601 million.

According to the most recent data from independent sources, ST is the world's leading supplier of application-specific analog ICs overall with number one rankings in various segments within this field, including wireless ASICs, computer peripheral ASICs and automotive ASSPs. ST is also the leader in MPEG-2 decoder ICs, and ASICs/ASSPs overall, including a number one position in digital consumer ASSPs. Additionally, ST is ranked at number two for discrete products, and in the memory market, ST holds third rank in NOR Flash ICs. In application segments overall: ST is number one for ICs in set-top boxes; at number two in smart cards, at number three in automotive; and at number four in wireless.

The Company's products are manufactured and designed using a broad range of fabrication processes and proprietary design methods. To complement this depth and diversity of process and design technology, the Company also possesses a broad intellectual property portfolio that it has used to enter into cross-licensing agreements with many other leading semiconductor manufacturers.

ST has developed a worldwide network of strategic alliances, including product development with key customers, technology development with customers and other semiconductor manufacturers, and equipment and CAD development alliances with major suppliers. By augmenting its rich portfolio of proprietary technologies and core competencies with complementary expertise from a variety of carefully chosen strategic partners, ST has developed an unsurpassed capability to offer leading-edge solutions to customers in all segments of the electronics industry.

The Company currently offers over 3,000 main types of products to more than 1,500 customers, including Alcatel, Bosch, DaimlerChrysler, Ford, Hewlett-Packard, IBM, Motorola, Nokia, Nortel Networks, Philips, Seagate Technology, Siemens, Sony, Thomson and Western Digital. Approximately two-thirds of ST's revenue is derived from differentiated products, a combination of dedicated, semi-custom and programmable products designed to suit a specific customer or a specific application and therefore having high system content. This result reflects ST's exceptionally early recognition of the importance of system-on-chip technology, which is a key for addressing the fast growing market for convergence products, and the success of the strategies it developed to ensure its leading position in this key emerging field.

The ST group was formed in June 1987 as a result of the merger between SGS Microelettronica of Italy and Thomson Semiconducteurs of France. In May 1998, the company changed its name from SGS-THOMSON Microelectronics to STMicroelectronics.

Since its formation, the Company has significantly broadened and upgraded its range of products and technologies and has strengthened its manufacturing and distribution capabilities in Europe, North America, and the Asia Pacific region. This capacity expansion is an ongoing process with the upgrading of existing facilities and the creation of new 8-inch, sub-micron fabs around the world. ST currently has five 8-inch fabs in operation in: Rousset (France); Agrate Brianza, R2 (Italy); Crolles (France); Phoenix (Arizona); Catania (Italy); and Singapore. Furthermore, a new 12-inch manufacturing facility is currently under construction in Catania; and the company is now ramping up production from a 12-inch pilot line called Crolles2, in partnership with Philips and Freescale Semiconductor. The Crolles2 operation is also host to the joint development program between the three companies to develop leading-edge CMOS process technology down to the 32nm node, in conjunction with TSMC for process alignment.

Corporate Headquarters, as well as the headquarters for Europe and for Emerging Markets, are in Geneva. The Company's U.S. Headquarters are in Carrollton (Dallas, Texas); those for Asia/Pacific are based in Singapore; and Japanese operations are headquartered in Tokyo.

To guarantee continued technological development and consistently offer customers true leading-edge products, ST each year invests a significant proportion of its sales in R&D and capital expenditures. ST has maintained an average R&D spend of close to 17% of revenue over the last three years, and an average of more than 15% of revenue from the date of the company's creation. In 2004, ST spent US\$1,532 million in R&D, or 17.5% of its net revenues. Additionally, ST filed 711 patent applications in 2004, maintaining its track record as one of the industry's most prolific inventors. The new inventions protected with these filings covered a wide range of technologies, products and applications, in line with the broad range supplier mission of the Company. ST is also active in numerous collaborative research projects worldwide as well as playing a key role in Europe's advanced technology research programs such as MEDEA+, and its predecessors, MEDEA and JESSI.

ST's technical, marketing and manufacturing strengths are matched and further enhanced by an unswerving commitment to Total Quality and Environmental Management (TQEM) that has earned prestigious awards around the world. Since 1991, the Company's sites have received more than 70 awards, of which more than 40 were for environmental issues.

In addition to ST's previous honors for quality over the last few years which include the Malaysian Prime Minister Quality Award, the Malta Quality Award and the European Quality Award - STMicroelectronics Asia Pacific was the winner of the 1999 Singapore Quality Award for Business Excellence; and the Company's US subsidiary STMicroelectronics Inc, was awarded the 1999 Malcolm Baldrige National Quality Award, the highest level of national recognition for quality that a US company can receive. And in 2000, ST's Moroccan operations received the Morocco National Quality Award.

ST's commitment to environmental responsibility has resulted in substantial reductions in the consumption of energy, water, paper and hazardous chemicals, increased recycling of waste products and a significant cut in CO2 emissions. In 1999, ST received the United States Environmental Protection Agency's Climate Protection Award for its outstanding accomplishments in protecting the Earth's climate. In 2000, ST was ranked first in environmental management among 14 semiconductor companies by Innovest Strategic Value Advisors and received the only AAA ranking in eco-efficiency. Also in 2002, ST received the Seal of Sustainability from the Sustainable Business Institute and ST's back-end Malta plant received the Management Award for Sustainable Development as part of the European Awards for the Environment 2002, organized by the European Commission Directorate-General Environment. And most recently, ST was awarded the 'Best Industrial Renewable Energy Partnership' as part of the European Commission's 'Campaign for Take-Off for Renewable Energy Awards 2003.

Since December 8, 1994, when ST completed its initial public offering, the Company has been quoted on the New York Stock Exchange (NYSE: STM) and on Euronext Paris (NXT: STM) and since June 1998 also listed in Milan on Borsa Italiana (MIB: STM). The Company has around 900 million outstanding shares, over 69% of which are publicly traded on the various stock exchanges. The balance of the shares is held by STMicroelectronics Holding II B.V., a company whose shareholders are CASSA DEPOSITI E PRESTITI and Finmeccanica of Italy, and a French consortium comprising Areva and France Telecom.

xvii

Chapter -1

# Introduction

# CHAPTER 1 INTRODUCTION

# **1.1 Introduction To Certification:**

Today's Systems on Chips (SoCs) are requested to be more and more complex whereas the associated Time-To-Market is getting shorter and shorter. Such SoCs are typically made up of building blocks, some of them actually providing innovative functions, others addressing more classical ones. The design data for such building blocks is provided in the form of a Library Database. This database can be reused in various SoCs. The overall process of system design begins with identifying the system requirements. They are the required functions, performance, power, cost, reliability and development time for the system.

The level of circuit performance which can be reached within a certain design time strongly depends on the efficiency of the design methodologies, as well as on the design styles. The choice of the particular design style for a VLSI product depends on the performance requirements, the technology being used, the expected lifetime of the product and the cost of the project.

The technology always impacts the design process. The design flow starts with laying down the specifications, RTL is generated and Macro and Memory Libraries are generated. These Macro and Memory libraries contain information regarding

- Cell characteristics (Cell and pin names, area, delay arcs and pin loading).

- Design rule Constraints (DRC).

- Operating Conditions.

- Wire Load Models.

All this information is used

- To implement the design function.

- To calculate timing values and path delays.

- To calculate power consumption.

The operating conditions specify the characteristics like operating temperature variations, supply voltage variations and process variation. The wire-load models estimate the effect of wire length and fan-out on resistance, capacitance and area of nets.

All these characteristics are used to make a physical description of the design. The physical specification is used to define how a particular part has to be constructed to yield a specific structure and hence a behavior.

The actual transistor sizes and physical capacitances are calculated to a high degree of accuracy. This information is mapped back to the structural description to place more accurate delays on gates and nets. This back-annotation is crucial to obtain accurate performance estimations.

All these comprise the process of certification, wherein the logical and physical characteristics of the design are verified for equivalence using the various ASIC design flow operations such as floorplanning, placement, clock tree synthesis (CTS), post CTS optimization, routing and post-route optimization followed by the signing-off of the design.

## **1.2 IO Libraries:**

IO Libraries consists of a group of cells called I/O buffers. Those cells are already designed in a specific process technology. Which contain Physical/ logical / timing/ electrical information about the cells. I/O buffers are designed to interface the off-chip signals to inside chip environment and vice-versa and to provide Power/Ground Signals to the Chip. I/O's are placed on the periphery of the chip .Any signal which comes from off-chip environment (external voltages are at a typical voltage of 2.5V, 3.3V or 5V) into the chip, must be checked by I/O for any discrepancy in its behavior other than defined by the core for that particular signal. If I/O finds any signal defying the behavior expected from it, it modifies the signal so as to ensure proper functioning of chip. I/O's also act as protection devices for the core. I/O also scans the signal which is going from core to off-chip world.

# **1.3 Memories:**

In the present-day SoC, approximately 50% to 60% of the SoC area is occupied by memories. Even in the modern microprocessors, more than 30% of the chip is occupied by embedded cache. So certification of these libraries is very important.

These contain Memories of Various Architectures like SRAM, DRAM, ROM. The basic building blocks are already designed in a specific process technology.

## **1.4 Analog and Mixed Signal Libraries:**

These contain IPs providing some innovative functions like PLL, DAC, USB, high speed I/Os. The primary design issue in analog circuits is the precise specifications of various parameters. For SoC design, the design of analog circuit must meet the specifications of a significantly large number of parameters to ensure that the analog behavior of these circuits will be within the useful range after manufacturing. These can be implemented as full custom hand crafted cells or in a semi-custom manner using the CORE libraries.

# **1.5 CORE Libraries:**

It consists of a group of cells called standard cells. They implement the basic logic functions. Examples are Inverter, AND, Flops, Latches etc. Those cells are already designed in a specific process technology. Physical/logic/timing/electric models are already created for those cells.

Chapter – 2

# Place and Route Flow

# CHAPTER 2 PLACE AND ROUTE FLOW

## 2.1 Overview:

The Certification is a process of applying various ASIC design flow operations on the design, to verify whether the design is fit to be used in the particular design environment.

The operations include generation of design, binding the netlist with the standard cells, floorplanning, placement and routing, clock tree synthesis, parasitic extraction, Design Rule Check (DRC), Layout Vs Schematic (LVS) and many more.

Purpose of library certification is to meet library CAD view quality demands w.r.t. cell-based design flow, while meeting cycle time constraints and following correct certification processes. Develop new methods to improve the existing methodology and provide support to customers.

**Fig. 2.1.1 Certification Execution Process**

# 2.2 Methods of Certification:

Depending upon the updates done in the new versions of the library, the certification can be classified in four different categories:

• Method Zero Certification: Method 0 is the most preliminary method of certification. The method 0 is applied when there are updates in Release notes, Known Problems and Solutions document (KPS) or UserManual.

Also, at times the report of the product is submitted depending on the logs during the development stage checked by certification team.

- Method One Certification: Method-1 certification is used when there are updates in .lib file but the changes made in .lib file are not reflected in the layout and postlayout calculations. This could be related to the timing updates. Since .def and .lef files are not available, wireload models are used to generate .dspf file. This is then used in delay calculation in order to generate sdf file which will be then used for back-annotation using ncsim/ncverilog. Tests run during this method are:

- Read sdf to check the cross-compatibility of stf and map file.

- Pre-layout back-annotation for Verilog and Vital models.

- o Tag Checks.

- Method Two Certification: Method-2 certification is used when there are backend updates in the standard cell library. Thus, during the Method-2 the Design Rule Check (DRC) and Layout Versus Schematic (LVS) checks are performed.

- **Method Four Certification:** Method-4 certification is the most commonly used method when the library is to be certified for the first time. This means during this method, the entire flow is to be exercised.

# 2.3 Design Entry:

RTL design and Netlist can be created using plugin "**Fusion**" or manually. Connectivity of pins has to be taken care as per the manual for special connections. This provision is provided within "**Special Connections**" feature of Fusion.

# 2.4 PAR Flow:

The physical design of ASICs is normally divided into System partitioning, Floorplanning, Placement and routing.

# System partitioning:

Microelectronic systems typically consist of many functional blocks. If a functional block is too large to fit in one ASIC, we may have to split, or **partition**, the function into pieces using goals and objectives that we need to specify.

- Goal Partition a system into a number of ASICs

- Objectives Minimize the number of external connection between the ASICs.

# **Floorplanning:**

The input to a floorplanning tool is a hierarchical netlist that describes the interconnection of the blocks, the logic cells within the blocks; and the logic cell connectors. The netlist is a logical description of the ASIC; the floorplan is a physical description of an ASIC. Floorplanning is thus a mapping between the logical description and the physical description.

The goals of floorplanning are:

- arrange the blocks on a chip

- decide the location of the I/O pads

- decide the location and number of the power pads

- decide the type of power distribution

- decide the location and type of clock distribution.

# **Placement:**

The goal of a placement tool is to arrange all the logic cells within the flexible blocks on a chip. Ideally, the objectives of the placement step are to

- Guarantee the router can complete the routing step

- Minimize all the critical net delays

- Make the chip as dense as possible

- Minimize power dissipation

- Minimize cross talk between signals

- Minimize the total estimated interconnect length

- Meet the timing requirements for critical nets

#### • Minimize the interconnect congestion

### **Routing:**

Routing is of two kinds - Global routing and detailed routing

## **Global routing**

A global router does not make any connections, it just plans them. One can typically global route the whole chip before detail routing the whole chip. There are two types of areas to global route: inside the flexible blocks and between blocks.

The goal of global routing is to provide complete instructions to the detailed router on where to route every net.

The objectives of global routing are

- Minimize the total interconnect length

- Maximize the probability that the detailed router can complete the routing

- Minimize the critical path delay

## **Detailed routing**

The global routing step determines the channels to be used for each interconnect. Using this information the detailed router decides the exact location and layers for each interconnect.

The goal of detailed routing is to complete all the connections between the logic cells. The most common objective is to minimize one or more of the following:

- The total interconnect length and area.

- The number of layer changes that the connections have to make

- The delay of critical paths minimizing the number of layer changes corresponds to minimizing the number of vias that add parasitic resistance and capacitance to a connection.

# 2.4.1 Avanti Design Flow:

Avanti Design flow is used for place and routing. Which is shown below:

Fig. 2.4.1.1 Avanti Design Flow

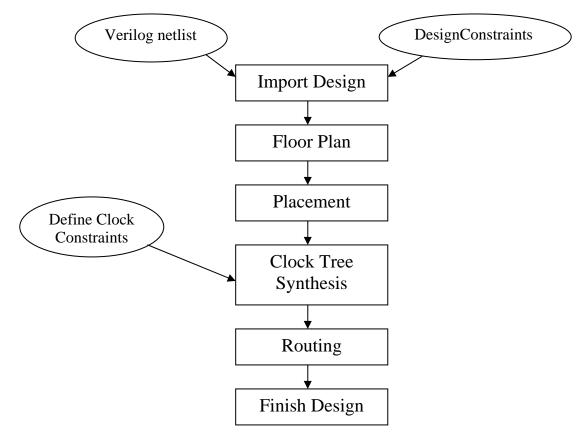

# 2.4.1.1 Design Setup:

This first step performs:

- design library creation if non existent

- addition of RefLibs in case of library creation

- Attach TLUplus files to library

- generates dont't use and delay cell list in line with Ref Libraries in

COLLECT\_DATA.

- import the verilog netlist .

- flattening (expand)

- creation of CEL view (for P&R task)

- bind the netlist to cell

- preserve hierarchy

- create initial floorplan

- load converted tdf file (optional)

- load converted bond file (optional)

- make a Power/Ground Connection for All Cells

- load timing constraints file

- performs timing check (file ttiming\_check.rpt in REPORT directory)

- do Timing Analysis with zero Wireload

- save the resulting cell in <TopCellName>\_fp

## 2.4.1.2 Floorplan:

Floor planning is the exercise of arranging blocks of layout within a chip to minimize area or maximize speed. It can be called, allotment of the silicon real estate to different blocks in the design. The input to the floor planning is typically the dimension of the chip, the area constraints. It is almost always necessary to place hard macros manually.

The Floorplan executes following sequence:

- pins for block are snapped on wiretracks.

- add IOFILLER (padFiller) for a top + PG connect IOfiller

- add placement blockage around each Macro Cell

- add Power and Ground Grid

- pre-route the standard cell rails.

- performs PGConnect of Pads and IOFillers for a top

- check and repair the placement of pin for a block

# 2.4.1.3 Placement:

Placement is the task of placing Logic Cells or Gates in some pre-allocated rows to minimize area or cycle time. Cells are placed adjacent to each other so as to minimize the interconnections. Placement reads the PDEF, for placing the modules.

Fig. 2.4.1.3.1 Placement Flow

## 2.4.1.4 Clock Tree Synthesis:

Method constructs a tree of clock buffers with some suitable geometry such that modules those communicate with each other receive well-defined clocks. Gated CTS processes the active gated clock net from root to the clock pin. Given the root net Gated CTS traverses through all the gated subnets, determines the structure of buffer trees & performs CTS to optimize skew. Need clock constraints (min & max insertion delay, max transition, max skew, Buffers & Inverters to be inserted), as an input to CTS.

The TreeSynthesis.cmd script performs:

- High Fanout Net Synthesis (non gated CTS by default)

- Timing analysis pre-cts

- Clock Tree synthesis (gated CTS by default)

- Pre-route clock skew report

- Route clock + global route/track assign for signals

- Post-route skew report

## Fig.2.4.1.4.1 Clock Tree Synthesis

# CLOCK TREE SYNTHESIS

## 2.4.1.5 Routing:

A router takes a module placement and a list of connections and connects the module with wires. **Global Routing** maps general pathways through the design for each unrouted net. The global router uses a two dimensional array of GR cells to model the demand & capacity of Global Routing. **Detail Routing** uses the general pathway suggested by global routing & track assignments to place paths & contacts in order to route the nets.

The Route Design executes following sequences:

- pre-route the padring, based on the PG Connect commands

- buffers insertion on nets with length > threshold defined in Project\_variables

- Add Diodes protection on pins for a block

- Route the clock tree nets

- route the design

- post-route timing report

- postRoute clock skew report

# ROUTING FLOW

Fig. 2.4.1.5.1 Routing Flow

# 2.4.1.6 Finish Design:

This is the last step of PAR flow. This operation generates verilog netlist for timing analysis and LVS. It also stream out GDSII and defout. It verifies power and ground connections.

# FLOW FOR FINISH DESIGN

Fig. 2.4.1.6.1 Finish Design Flow

# 2.4.2 Benefits of the Astro:

Astro addresses ultradeep submicron (UDSM) effects during design processes. Its unique technology eliminates iterations, by concurrently accounting for all physical effects throughout the design process.

- Astro increases clock speeds and provides fast design completion.

- Astro improves productivity, by providing placement change controls such as incremental overlap removal and incremental placement. It also ensures the lowest possible clock skew with its early timing capability and ability to predict congestion impact.

- Design data created with the previous generation of Synopsys place and route tools is fully compatible with Astro.

- Astro follows the latest, advanced manufacturing process rules, thereby improving design reliability. It handles antenna repair, via optimization, metal fill, and metal slotting automatically. Effects such as conformal dielectrics, copper dishing, and shallow trench isolation are incorporated into the Astro parasitic extraction engine.

- Astro shortens design cycles. Its new high-performance algorithms and distributed routing capabilities enable you to get designs out the door quickly.

# 2.4.3 Magma PAR Flow:

The Magma flow includes a family of products that performs RTL synthesis (the Blast Create and Blast RTL tools) in addition to timing optimization and analysis, floorplanning, power planning, place and route, scan-based analysis and synthesis, and RC extraction technologies (the Blast Fusion tool). The system integrates these technologies with a common, open data model. There are no translations among the engines that implement these technologies, so intertool communication is fast and performance is excellent.

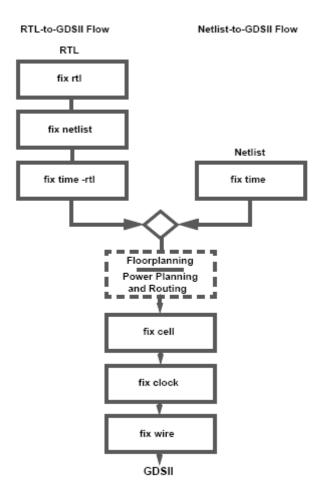

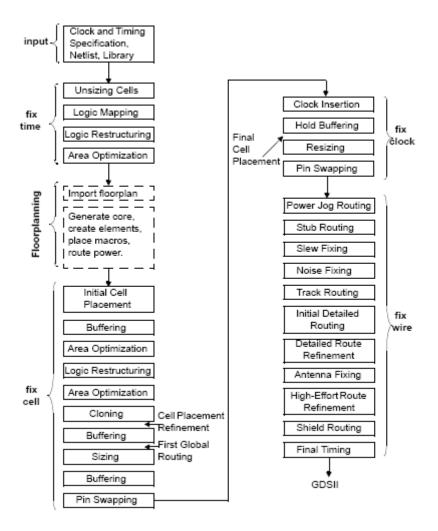

Fig. 2.4.2.1 Magma Design Flow

The Magma design flow includes a complete RTL-to-GDSII chip design and implementation system. Blast Create provides RTL-to-netlist implementation; Blast Fusion is the netlist-to-GDSII design and implementation system.

Fig. 2.4.2.2 Blast Fusion Design Flow

#### 2.4.3.1 Optimization Features:

Blast Fusion includes the following optimization features:

- FixedTiming methodology, which allows Blast Fusion to determine the design's optimal timing prior to detailed physical implementation

- SuperCell abstraction, which replaces each logic function with automatically abstracted SuperCell models with variable sizes and fixed delay

- Gain trimming

- Logic restructuring

- Buffering to handle heavy loads

- Cloning and trimming

- Incremental static timing analysis

• Incremental parasitic extraction

#### 2.4.3.2 Placement Features:

Blast Fusion includes the following placement features:

- High-capacity placement for handling large, complex, multimillion-gate designs

- Comprehensive congestion analysis based on placement, optimization, and routing Constraints.

- Full-chip, concurrent macro and cell placement

- Top-down and bottom-up methodologies for optimal I/O pin placement

- Scan chain reordering

- Interactive and user-defined I/O placement, including staggered I/Os

- Multi-height cell placement with power and ground rail sharing

#### 2.4.3.3 Routing Features:

Blast Fusion includes the following routing features:

- Virtual gridless router, which blends the speed and capacity of a gridded router with the flexibility of a shape-based router

- Variable width and space routing

- Antenna avoidance

- Automatic metal slotting

- Stacked vias

- Custom via rule support

- Congestion-based capacitance estimation

- N-layer routing

- Top-level chip assembly routing and block-level standard cell routing

- Built-in polygon-based DRC engine

- Complete Engineering Change Order (ECO) support

- Power routing and support for various power mesh styles

- Automatic ring routing and wire tapping

- Interactive bus routing

- Scan chain routing

#### 2.4.3.4 Clock Tree Features:

Blast Fusion includes the following advanced clock tree features:

- Balanced H-trees

- Bottom-up clustering algorithm

- Zero skew and useful skew

- User-controlled buffer specification

- Interclock skew and insertion delay minimization

- Multiple clock domains

- Automatic gated clock checks, wire sizing, shielding, wire spacing, and obstruction avoidance.

#### 2.4.4 Benefits of the Magma Design Tool:

The Magma design tools provide the following benefits:

• Faster time to market

Eliminate the time-consuming iteration cycles that can delay the completion of your critical chip design project. You can create complex, high-quality deep submicron designs in less time.

• Better chip performance

Design chips with greater speed, smaller area, and lower power consumption. Powerful optimization technology coupled with the Magma embedded timing analyzer ensures the highest performance for your designs.

• Greater design capacity

Synthesize several million gates at a time—an order of magnitude larger than possible using traditional synthesis tools. The innovative Magma SuperCell technology and unified data model use memory efficiently, enabling increased capacity.

• Enhanced quality and reliability

The Magma single unified data model architecture allows automatic detection and active avoidance of potential signal integrity problems. The Blast Noise product provides automatic detection and avoidance of crosstalk noise and delay, and corrects potential signal electromigration (EM) problems. Additionally, both Blast Create and Blast Fusion provide automatic correction of potential antenna problems that can lead to lower chip yields.

Chapter – 3

Signoff Flow

# CHAPTER 3 SIGNOFF FLOW

# **3.1 Introduction:**

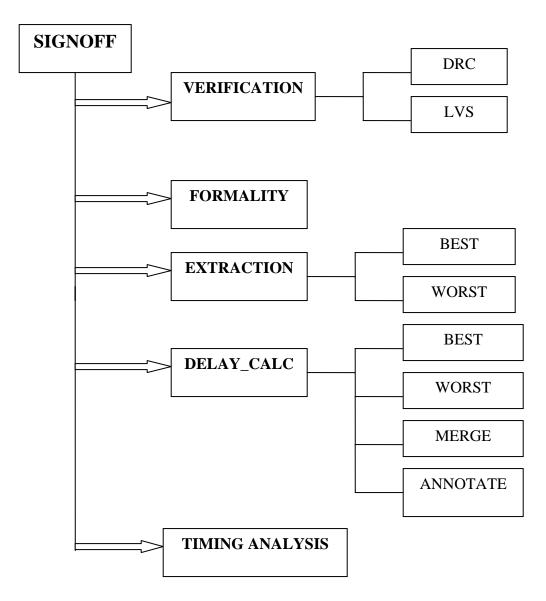

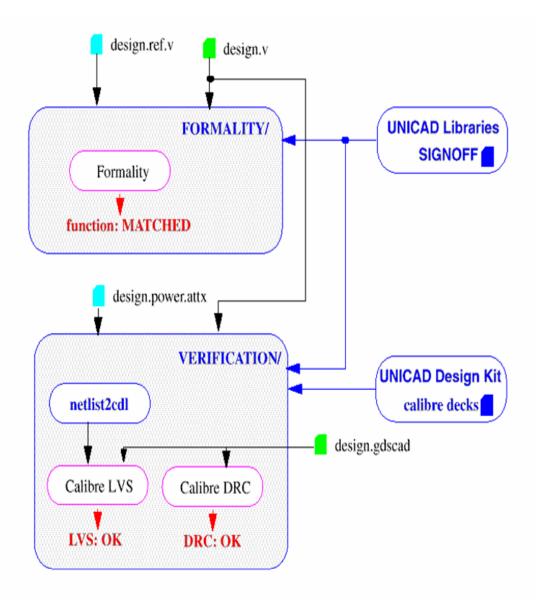

**Fig.3.1 Signoff Flow**

One purpose of a sign-off checklist is to ensure that certain checks were made during design, simulation and verification so that the final files meet certain criteria. Another objective of the checklist is to ensure that all necessary design, simulation and verification files have been created and that installation script and required documentation have been developed.

The Sign-Off Flow is an environment to perform design Sign-Off verification. This flow consists of sequence of tasks to be performed by the user in a hierarchical manner. A script is provided to automate each task and generate reports. User has to carefully analyze each report.

Tasks that have to be run for design sign-off are:

Netlist and Layout Verification Tasks

**D** Timing Verification Tasks

Among the tasks to be run are netlist and layout verification tasks:

FORMALITY: Formal proof between the verilog netlists before and after design implementation.

VERIFICATION: GDSII verification with calibre DRC/LVS and generation of the CDL netlist.

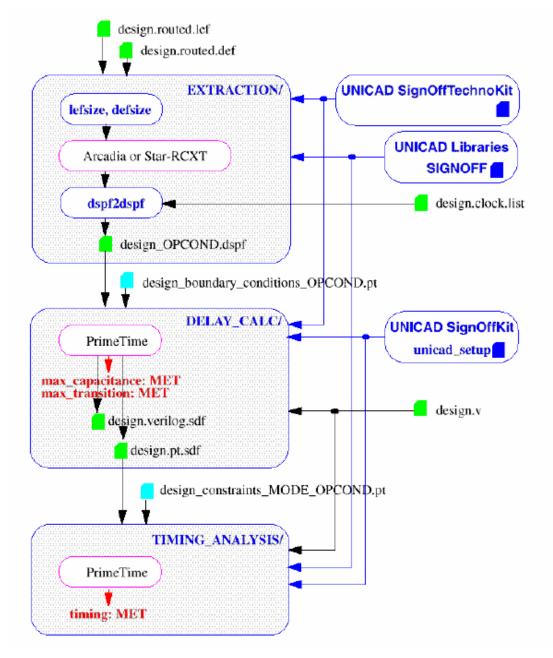

Timing verification tasks need to be run in following sequence:

EXTRACTION: Lef/Def extraction with StarRCXT.

DELAY\_CALC: Verilog netlist annotated with parasitic into PrimeTime for delay calculation (max\_capacitance, max\_transition, max\_fanout). SDF Worst, Best, merging and verilog SDF annotation are the used for simulation.

#### Table 3.1.1 The tools to be used for SignOff Flow are stated below:

| Formal Verification                    | Synopsys Formality      |

|----------------------------------------|-------------------------|

| Design rule check (DRC)                | Mentor Graphics Calibre |

| Layout vs. Schematic                   | Mentor Graphics Calibre |

| Parasitic Extraction                   | Synopsys Star-RCXT      |

| Post-layout delay calculation          | Synopsys Prime Time     |

| Post-layout Gate level timing analysis | Synopsys Prime Time     |

| Back Annotation                        | ncVerilog, modelsim     |

#### Fig. 3.1.3 Delay Calculation Tasks:

# **3.2 Formality:**

Formality is an application that uses formal techniques to prove or disprove the functional equivalence of two designs or two cell libraries. Formality is used to compare a gate-level netlist to its register transfer level (RTL) source or to a modified version of that gate-level netlist. After the comparison, Formality reports whether the two designs or cell libraries are functionally equivalent. The Formality tool can significantly reduce your design cycle by providing an alternative to simulation for regression testing.

The techniques Formality uses are static and do not require simulation vectors. Consequently, for design verification you only need to provide a functionally correct, or golden design (called the reference design), and a modified version of the design (called the implementation). By comparing the implementation against the reference design, one can determine whether the implementation is functionally equivalent to the reference design. Cell library verification is similar except that each cell in the implementation library is compared against each cell in the reference library one cell at a time. As designs become larger and more complex and require more simulation vectors, regression testing with traditional simulation tools becomes a bottleneck in the design flow. Formality gives two distinct advantages: significantly reduced verification times and complete verification. Reduced verification times occur because Formality requires no input vectors. Reducing gate-level simulation time means one can spend more time verifying the initial golden RTL design to get better functional coverage.

The following list summarizes the Formality features:

- Proves two designs or cell libraries are functionally equivalent, faster than verification using event-driven simulators.

- Provides complete verification (not vector-dependent).

- Performs RTL-to-RTL, RTL-to-gate, and gate-to-gate design verifications.

- Performs Verilog-to-DB, Verilog-to-Verilog, DB-to-DB, Verilog-to-SPICE, and DB-to-SPICE cell library verifications.

- Offers diagnostic capabilities to help you locate and correct functional discrepancies between designs.

- Reads synthesizable VHDL, Verilog, Synopsys internal .db format, and EDIF netlists. "Performs automatic hierarchical verification.

- Uses existing Synopsys Design Compiler technology libraries.

- Saves and restores designs and verification sessions.

- Offers a graphical user interface (GUI) and a shell command-line interface (fm\_shell).

- Verifies a wide range of design transforms or modifications, including pipeline retiming and reencoded finite state machines.

- Offers schematic views and isolated cone of logic views that support location of design discrepancies.

#### 3.3 DRC:

Fig. 3.3.1 DRC Data Flow

The Calibre DRC/DRC-H tools perform physical verification of integrated circuit layout designs in flat, hierarchical configurations. The inputs to Calibre DRC are an SVRF rule file and a layout database. The outputs are a run transcript and a DRC Results Database, with an optional DRC Summary Report.

LVS comparison occurs after device recognition in LVS applications. The LVS outputs that always occur include a run transcript and an LVS Report. Calibre LVS applications compare electrical circuits from the specified source netlist and layout geometry.

# **3.5 Extraction:**

Star-RCXT is a software tool that extracts parasitics from connected databases that represent integrated circuit layout designs. One can use Star-RCXT to generate netlists to conduct a timing, clock, noise, or power analysis. one can also extract parasitics like resistors, capacitors, and inductors from a layout design database.

Star-RCXT performs these extraction tasks:

- Produces accurate, full-chip extraction for noise, signal electromigration, voltage (IR) drop, and timing verification.

- Does selective extraction and netlisting for critical path analysis.

- Provides a complete, production-proven solution for different design types, such as ASIC, full custom, microprocessor, memory, and analog designs.

- Offers consistent interconnect modeling for physical design and optimization. Efficient post-layout analysis enables fast timing convergence and rapid time to market.

- Includes advanced process effects such as copper interconnect, local interconnect, silicon on insulator (SOI), and in-die process variation.

- Ensures inductance extraction for multi-million gate SoC designs with automatic modeling of single or multiple current-return paths.

- Creates process characterization files for Star-RCXT which can also be obtained from major foundries.

- Integrates into existing design flows.

- Provides hierarchical and distributed processing.

#### **3.6 Delay Calculation:**

After breaking down a design into a set of timing paths, PrimeTime calculates the delay along each path. The total delay of a path is the sum of all cell and net delays in the path. The method of delay calculation depends on whether chip layout has been completed. Before layout, the chip topography is unknown, so PrimeTime must estimate the net delays using wire load models. After layout, an external tool can accurately determine the delays and write them to a Standard Delay Format (SDF) file.

With report\_delay\_calculation command one can generate a detailed report on how PrimeTime calculates the delay for a specified cell or net timing arc. This information is useful for debugging a timing problem or verifying the timing data in a technology library. The reported delay calculation takes into account the operating conditions and wire load models.

For initial static timing analysis, PrimeTime estimates net delays based on a wire load model. Actual delays depend on the physical placement and routing of the cells and nets in the design.

A floorplanner or router can provide more detailed and accurate delay information, which you can provide to PrimeTime for a more accurate analysis. This process is called delay back-annotation. Back-annotated information often is provided in a Standard Delay Format (SDF) file. Worst and Best SDF are merged into a single SDF. SDF annotation is performed on the verilog netlist using NC-VERILOG and ensure that post-layout back annotated simulations can be performed.

#### **3.7 Timing Calculation:**

Timing analysis is typically an iterative process. You begin with a gate-level design description and analyze the timing using wire load models to estimate the net delays. Then, after placement and routing, one can back-annotate the design description with detailed delay information provided by the layout tools, allowing PrimeTime to do a more accurate, layout-specific analysis. PrimeTime is a full-chip, gate-level static timing analysis tool targeted for complex, multimillion-gate designs. It offers an unsurpassed combination of speed, capacity, ease of use, and compatibility with industry-standard data formats and workflows. To check a design for violations, PrimeTime breaks the design down into a set of timing paths, calculates the signal propagation delay along each path, and checks for violations of timing constraints inside the design and at the input/output interface. PrimeTime supports a wide range of advanced timing analysis features, including the following:

- Multiple clocks and clock frequencies

- Multicycle path timing exceptions

- False path timing exceptions and automatic false path detection

- Transparent latch analysis and time borrowing

- Simultaneous minimum/maximum delay analysis for setup and hold constraints

- Analysis with on-chip variation of process, voltage, and temperature (PVT) conditions

- Case analysis (analysis with constants or specific transitions applied to specified inputs).

- Mode analysis (analysis with module-specific operating modes, such as read mode or write mode for a RAM module)

- Bottleneck analysis (reporting of cells that cause the most timing violations)

- What-if analysis without modifying the original netlist, using inserted buffers, resized cells, and modified nets.

- Analysis of crosstalk effects between physically adjacent nets using the PrimeTime SI (signal integrity) option.

#### **3.8 Back-Annotation:**

The sole point of entry of timing information into a VITAL compliant model is through the timing generics. With the exception of the use of VITAL\_Timing and VITAL\_Memory routines, all timing calculations are performed outside of the VHDL model, and external timing information is passed to the model through the back-annotation timing generics. Back-annotation is the process of updating the back-annotation timing generics with the external timing information. Signal delays which are used to model negative timing constraints are computed in the negative constraint calculation stage of simulation; their calculation is not part of the back-annotation process.

The rules governing the back-annotation of timing values into a VITAL compliant model and the mapping of SDF constructs to back-annotation timing generics define the semantics assumed by models which adhere to the Level 0 specification.

Chapter – 4

# Analysis of Results

# CHAPTER 4 ANALYSIS OF RESULTS

# 4.1 Macro Libraries:

# • Inputs:

This section explains input contents required for certification flow. Complete flow is explained by taking different reference libraries like **IO90LPHVT\_REF\_COMPENSATION\_1V8\_50A**,

IO90LPHVT\_REF\_COMPENSATION\_2V5\_50A, IO90LPHVT\_REF\_COMPENSATION\_3V3\_50A, IO90LPHVT\_REF\_SSTL\_COMPENSATION\_1V8\_50A, CORE90LPHVT,

#### PR90M7.

All four compensation libraries contain single core macro cell. CORE90LPHVT is a Standard Cell library for 90 nanometer CMOS090LP VLSI digital design platform. This library contains 715 SSI combinational and sequential cells, designed to work at 1.0V (+10%/-10%), 1.20V(+10mv/-10mv) and 1.40V(+10%/-10%) with temperature range from -40 up to 125 C. This library is used to provide logic. PR90M7 is a standard-cell library for CMOS090 VLSI digital designs, dedicated to be used for place & route. It contains 8 special cells (Antenna Protection, Clocktree, and Prober) designed to work at 1.0V (+10%/-10%) and 1.2V (+10%/-10%) with temperature range from -40 up to 125 C.

# **4.1.1 Design Entry and Netlist generation:**

All libraries which need to be certified should be copied in workspace where one has to run complete certification flow. Then with help of fusion script and Ipsceen tool Verilog netlist is generated.

Fusion Script and Ipscreen tool generates following three files:

- 1. RTL Netlist Netlist

- 2. Standard design constraint file <design name>.sdc

- 3. Verilog Netlist file <design name>.ref.v

#### Fig .4.1.1 RTL Netlist

Module CERT\_COMP (clk,rst,dataout);

input clk,rst;

output dataout;

reg dataout;

wire [72:1] a;

wire [108:1] g;

COUNTER\_2 #(72) inst\_COUNTER\_2 (.a(a),.clk(clk),.rst(rst),.dataout(dataout));

COUNTER\_1 #(108) inst\_COUNTER\_1 (.count(g),.clk(clk),.rst(rst));

IOREF\_COMPENSATION\_1V8inst1\_IOREF\_COMPENSATION\_1V8

(.ACCURATE(g[1]),.COMPEN(g[2]),.COMPOK(a[1]),.COMPTQ(g[3])

,.FREEZE(g.NASRC4(a[6]),.NASRC5(a[7]),.NASRC6(a[8]),.RASRC0(g[6]),

.RASRC1(g[7]), ...

IOREF\_COMPENSATION\_1V8inst2\_IOREF\_COMPENSATION\_1V8

(.ACCURATE(g[14]),

.COMPEN(g[15]),.COMPOK(a[10]),.COMPTQ(g[16]),.FREEZE(g[17]),.GNDBGCOMP(g[ 18]),.NASRC0(a[11]),.NASRC1(a[12]),.NASRC2(a[13]),.NASRC3(a[14]),.NASRC4(a[15]), .NASRC5(a[16]),.NASRC6(a[17]),....

IOREF\_COMPENSATION\_2V5inst1\_IOREF\_COMPENSATION\_2V5 (.ACCURATE(g[27]),.COMPEN(g[28]),.COMPOK(a[19]),.COMPTQ(g[29]),.FREEZE(g[3 0]),.GNDBGCOMP(g[31]),.NASRC0(a[20]),.NASRC1(a[21]),....));

IOREF\_COMPENSATION\_2V5inst2\_IOREF\_COMPENSATION\_2V5 (.ACCURATE(g[40]),.COMPEN(g[41]),.COMPOK(a[28]),.COMPTQ(g[42]),.FREEZE(g[4 3]),.GNDBGCOMP(g[44]),.NASRC0(a[29]),.NASRC1(a[30]),...)); IOREF\_COMPENSATION\_3V3inst1\_IOREF\_COMPENSATION\_3V3 (.A0SRC(a[37]), .A1SRC(a[38]),.A2SRC(a[39]),.A3SRC(a[40]),.A4SRC(a[41]),.A5SRC(a[42]),.A6SRC(a[43 ]),.ACCURATE(g[53]),.CHIPSLEEP(g[54]),....)); IOREF\_COMPENSATION\_3V3inst2\_IOREF\_COMPENSATION\_3V3 (.A0SRC(a[46]), .A1SRC(a[47]),.A2SRC(a[48]),.A3SRC(a[49]),.A4SRC(a[50]),.A5SRC(a[51]),.A6SRC(a[52 ]),.ACCURATE(g[68]),.CHIPSLEEP(g[69]),....));

IOREF\_SSTL\_COMPENSATION\_1V8

inst1\_IOREF\_SSTL\_COMPENSATION\_1V8 (.ACCURATE(g[83]),.COMPEN(g[84]), .COMPOK(a[55]),.COMPTQ(g[85]),.FREEZE(g[86]),

.GNDBGCOMP(g[87]),.NASRC0(a[56]),.NASRC1(a[57]),.NASRC2(a[58]),.NASRC3(a[59

]),.NASRC4(a[60]),.NASRC5(a[61]),.NASRC6(a[62]),.RASRC0(g[88]),.RASRC1(g[89]), .RASRC2(g[90]),.RASRC3(g[91]),.RASRC4(g[92]),.RASRC5(g[93]),.RASRC6(g[94]),

.REXT(a[63]), .TQ(g[95]));

IOREF\_SSTL\_COMPENSATION\_1V8 inst2\_IOREF\_SSTL\_COMPENSATION\_1V8 (.ACCURATE(g[96]),.COMPEN(g[97]),.COMPOK(a[64]),.COMPTQ(g[98]),.FREEZE(g[9 9]),.GNDBGCOMP(g[100]),.NASRC0(a[65]),.NASRC1(a[66]),....));

endmodule

```

module COUNTER_1 (count, clk,rst);

```

parameter width=8;

input clk,rst;

output [width-1:0] count;

reg [width-1:0] temp; reg [width-1:0] count;

always @ (posedge clk)

begin

```

if (rst==0)

```

begin

```

count=0; temp=0;

```

end

else

begin

temp=temp+1 ; count=temp;

end

end

endmodule

#### Fig 4.1.2 Verilog Netlist :

```

Module COUNTER 2 (a, clk,rst,dataout);

parameter width=9;

input [width-1:0] a;

input clk,rst;

output dataout; reg dataout;

always @ (posedge clk)

begin

if (rst==1)

dataout<=0:

else

dataout \leq = |(a);

end

endmodule

module CERT COMP ( clk, rst, dataout );

input clk, rst;

output dataout;

wire n4, n1, n2;

wire [72:1] a;

wire [108:1] g;

COUNTER_2_width72 inst_COUNTER_2 ( .a(a), .clk(clk), .rst(n1), .dataout );

COUNTER_1_width108 inst_COUNTER_1 ( .count(g), .clk(clk), .rst(n1) );

IOREF_COMPENSATION_1V8inst1_IOREF_COMPENSATION_1V8

(.ACCURATE(g[1]), .COMPEN(g[2]), .COMPOK(a[1]), .COMPTQ(g[3]), .FREEZE(g[4]),

.GNDBGCOMP(g[5]),.NASRC0(a[2]),.NASRC1(a[3]),.NASRC2(a[4]),

.NASRC3(a[5]),.NASRC4(a[6]),.NASRC5(a[7]),.NASRC6(a[8]),.....

IOREF COMPENSATION 1V8inst2 IOREF COMPENSATION 1V8

(.ACCURATE(g[14]),.COMPEN(g[15]),.COMPOK(a[10]),.COMPTQ(g[16]),

.FREEZE(g[17]),.GNDBGCOMP(g[18]), .NASRC0(a[11]), .NASRC1(a[12]), .....));

IOREF_COMPENSATION_2V5inst1_IOREF_COMPENSATION_2V5

(.ACCURATE(g[27]),.COMPEN(g[28]),.COMPOK(a[19]),.COMPTQ(g[29]),

```

.FREEZE(g[30]),.GNDBGCOMP(g[31]),.NASRC0(a[20]),.NASRC1(a[21]), .NASRC2(a[22]), .NASRC3(a[23]), .NASRC4(a[24]), .NASRC5(a[25]), .NASRC6(a[26]), .RASRC0(g[32]), .RASRC1(g[33]), .RASRC2(g[34]), .....)); IOREF\_COMPENSATION\_2V5inst2\_IOREF\_COMPENSATION\_2V5 (.ACCURATE(g[40]),.COMPEN(g[41]),.COMPOK(a[28]),.COMPTQ(g[42]), .FREEZE(g[43]),.GNDBGCOMP(g[44]),.NASRC0(a[29]),.NASRC1(a[30]), .NASRC2(a[31]),

.NASRC3(a[32]), .NASRC4(a[33]), .NASRC5(a[34]), .NASRC6(a[35]),....)); IOREF\_COMPENSATION\_3V3inst1\_IOREF\_COMPENSATION\_3V3 (A0SRC(a[37]),.A1SRC(a[38]),.A2SRC(a[39]),.A3SRC(a[40]),.A4SRC(a[41]), .A5SRC(a[42]),.A6SRC(a[43]),.ACCURATE(g[53]),.CHIPSLEEP(g[54]), .COMPEN(g[55]),.COMPOK(a[44]),.COMPTQ(g[56]),.FREEZE(g[57]), .GNDBGCOMP(g[58]),.RA0SRC(g[59]),.RA1SRC(g[60]),.RA2SRC(g[61]), .RA3SRC(g[62]), .... ));

IOREF\_COMPENSATION\_3V3inst2\_IOREF\_COMPENSATION\_3V3 (.A0SRC(a[46]),.A1SRC(a[47]),.A2SRC(a[48]),.A3SRC(a[49]),.A4SRC(a[50]), .A5SRC(a[51]),.A6SRC(a[52]),.ACCURATE(g[68]),.CHIPSLEEP(g[69]), .COMPEN(g[70]), .COMPOK(a[53]), .COMPTQ(g[71]), .FREEZE(g[72]), .... )); IOREF\_SSTL\_COMPENSATION\_1V8 inst1\_IOREF\_SSTL\_COMPENSATION\_1V8 (.ACCURATE(g[83]), .COMPEN(g[84]), .COMPOK(a[55]), .COMPTQ(g[85]), .FREEZE(g[86]),.GNDBGCOMP(g[87]),.NASRC0(a[56]),.NASRC1(a[57]), .NASRC2(a[58]),...));

```

IOREF_SSTL_COMPENSATION_1V8 inst2_IOREF_SSTL_COMPENSATION_1V8 (

.ACCURATE(g[96]),.COMPEN(g[97]),.COMPOK(a[64]),.COMPTQ(g[98]),

.FREEZE(g[99]),.GNDBGCOMP(g[100]),.NASRC0(a[65]),.NASRC1(a[66]),

.NASRC2(a[67]),.NASRC3(a[68]),.NASRC4(a[69]),.NASRC5(a[70]),.NASRC6(a[71]),...));

BFHVTX12 U1 (..A(rst), .Z(n1) );

IVHVTX0H U2 (.A(n4), .Z(n2) );

IVHVTX12 U3 (.A(n2), .Z(dataout) );

```

```

Endmodule

```

# Fig 4.1.3 Standard Design Constraints

| # Created by Design Compiler write_sdc on Mon Sep 25 11:32:41 2006      |  |

|-------------------------------------------------------------------------|--|

| #######################################                                 |  |

| set sdc_version 1.4                                                     |  |

| create_clock -period 10 -waveform {0 5} [get_ports {clk}]               |  |

| <pre>set_input_delay 5 -max -clock "clk" [get_ports {rst}]</pre>        |  |

| <pre>set_input_delay 1 -min -clock "clk" [get_ports {rst}]</pre>        |  |

| <pre>set_output_delay 5 -max -clock "clk" [get_ports {dataout}]</pre>   |  |

| <pre>set_output_delay 0.2 -min -clock "clk" [get_ports {dataout}]</pre> |  |

| <pre>set_clock_uncertainty 0.1 [get_clocks {clk}]</pre>                 |  |

| <pre>set_input_transition -max 5 [get_ports {rst}]</pre>                |  |

| <pre>set_input_transition -min 0.2 [get_ports {rst}]</pre>              |  |

| <pre>set_load -pin_load 5 [get_ports {dataout}]</pre>                   |  |

| <pre>set_load -min -pin_load 5 [get_ports {dataout}]</pre>              |  |

# 4.1.2 PAR Flow:

Then Astro PAR flow is used for placement and routing.

# • Input Files Expected

Verilog netlist of the design : <*design*>.*ref.v*

Synopsys Design Constraint file for timing constraints : <design>.sdc

Clock Specification in attx format: : <design>.clock.attx

Muti-supply format in attx format: : <design>.power.attx

design.ref.v and design.sdc files are generated by Ipscreen tool. design.clock.attx file is generated by CTEDIT task. Synopsys kit is required for that purpose. To support multisupply flow user has to create <design>.power.attx file for specifying particular gnd/power connection. If no <Design Name>.powerAttx file is given, default connections will be done according to default.power.attx file which is available in COLLECT\_DATA.

#### 4.1.2.1 Flow Setup:

In order to run the flow, the user must create/use a seed.tcl file, where a number of settings for the design is specified.

# • Workspace Setup :

A utility called avtGenerateTasks reads in the seed.tcl file in the SETUP directory and creates directories described below the argument to pass to this utility are the following [-seed] to specify seed.tcl -default = SETUP/seed.tcl

[- task] to specify the task environment - default = ASTRO

[- work] to specify directory name - default = PLACEANDROUTE for ASTRO task

This generates the design workspace with the following directories:

.AVANTI/

-<WORKSPACE>/

-VERILOGMODELS

-IMPORT

-EXPORT

Besides existing LIBRARIES and SETUP directories.

-LIBRARIES: This directory contains links to the master libraries directory.

-SETUP: Contain source seed.tcl file.

-AVANTI: this directory contains the Astro workspace(s) directory, the IMPORT and EXPORT directories.

•**WORKSPACE**>: This is the directory where Astro will be run. Its content is detailed in the following chapter

•IMPORT: directory where the user will store input data for the Place&Route flow

•EXPORT: directory where the Place&Route flow will store data for HANDOFF and SIGNOFF task

Pdef and verilog File for Physical Compiler (post Floorplan or CTS)

GDS file for DRC/LVS in cad layers

**DEF** file to interface with cadence and/or extraction tools

Lef file with the definition of Vias for SignOff Extraction

# Hierarchical Verilog netlist for Timing Analysis

# • IMPORT DESIGN :

Before the step of NetlistIn, constraints files (<design>\_constraints\_<mode>\_Max.pt, <design>\_constraints\_<mode>\_Min.pt,<design>\_boundary\_conditions\_Max.pt,<design>\_ boundary\_conditions\_Min.pt) should be linked to the .sdc file in (**AVANTI/IMPORT/**). The design to be certified is imported first .This is done by clicking on STM icon and the option Import design.

Timing constraints to different signals used in front-end design (Verilog or VHDL) is need to be propagated to the back-end .This is given as SDC format to Synopsys Design Compiler.

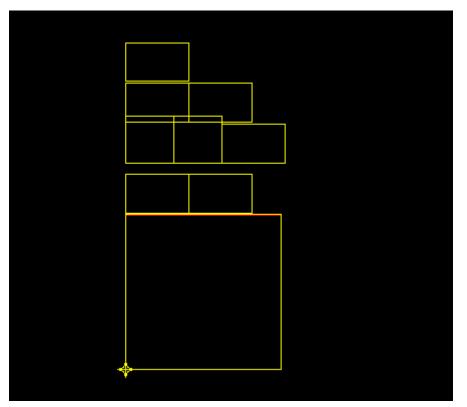

Fig. 4.1.2.1.1 Layout of Macro after Import Design

#### • FLOORPLANNING :

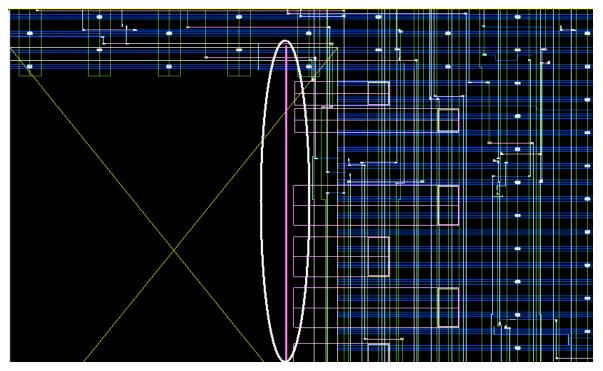

The next step is to do Floorplanning .Before running the **floorplan**, update the width and height of the floorplan such that sufficient area is left for subsequent routing of the cells. Macro should be placed in minimum two orientations R0 and R90 to test the power-Planning & routing related issues. After floorplanning check the grid view for connections of power-pins.Check digital power and ground are properly tapped .

In case, power ground pins are present within the macro(not abutted with the boundary) then check that the pins are present in atleast two orientations for more flexibility. **By default, the PnR flow creates a single power and ground supply. For macros** which have multiple power supplies, create the power straps after the placement-flow is done. Also the power.attx file should be prepared accordingly.

Fig. 4.1.2.1.2 Layout of Macros after Floorplan

# • PLACE DESIGN

Performs placement in three steps:

- Pre-placement Optimization.