# **"STUDY AND IMPLEMENTATION OF CMOS IO's FOR SUB MICRON VLSI CIRCUITS"**

## **A Major Project Report**

Submitted in Partial Fulfillment of the Requirements For the Degree of

# **Master of Technology**

In

## ELECTRONICS & COMMUNICATION ENGINEERING (VLSI Design)

By TRIPTI BHARGAVA (04MEC004)

#### **Project Guide**

Mr. Sandeep Kaushik Project Leader IFL Group FTM Dept ST Microelectronics, G.Noida

#### **Facilitator at Institute**

Dr. N.M. Devashrayee M.Tech Coordinator EC-VLSI Design Nirma University Ahmedabad

Department of Electronics & Communication Engineering INSTITUTE OF TECHNOLOGY, NIRMA UNIVERSITY AHEMADABAD 382481 MAY 2006

# CERTIFICATE

This is to certify that the M.Tech. Dissertation Report entitled "Study and implementation of CMOS I/O's for sub micron VLSI circuit" submitted by Tripti Bhargava (Roll no. 04MEC004) towards the partial fulfillment of the requirements for Semester III-IV of Master of Technology (Electronics and Communication Engineering) in the field of VLSI Design of Nirma University of Science and Technology, Ahmedabad at STMicroelectronics, G.Noida is the record of the work carried out by them under our supervision and guidance. The work submitted has in our opinion reached a level required for being accepted for examination. The results embodied in this Dissertation-Project work to the best of our knowledge have not been submitted to any other University or Institute for award of any degree or diploma.

#### Date:

Project Guide Mr. Sandeep Kaushik STMicroelectronics Greater Noida

HOD Dr. M.D. Desai EE – Department Nirma University, Ahmedabad Facilitator at Institute Dr. N.M. Devashrayee Institute of Technology Nirma University, Ahmedabad.

Director Dr. H.V. Trivedi Institute of Technology, Nirma University, Ahmedabad

# **ACKNOWLEDGEMENT**

Any fruitful effort in a new work needs a direction and guiding hands that shows the way. It is proud privilege and pleasure to bring our indebtedness and warm gratitude to respect Mr. Sandeep Sethi, Ex-Senior Section Manager, Mr. Anil Kalra, Senior Section Manager, Mr. Paras Garg, IFL Section Manager, STMicroelectronics Pvt. Ltd., India for his support during my thesis work.

I would like to express my profound gratitude to my project guide Mr. Sandeep Kaushik, Project Leader, Design support and solution group, STMicroelectronics, Noida, for his outstanding support and guidance during my project work.

I am thankful to my team members Mr. Nobal Preet Singh who in the early stages of the project helped us a lot with all of his heart and Mrs. Monika Gupta, Ms. Shikha Bhardawaj, Mr. Lokesh Pandey and Mr. Manoj Sharma with whom I have been working and have been monitored regularly at different phases of the project which helped me a lot.

I would like to express my warm thanks to my internal project guide Dr. N.M. Devashrayee for his kind guidance and support during the project work.

Last but not the least, I express thanks to all my colleagues and friends, especially, Mr. Apurva Chaure, Mr. Jatin Fultaria, Mr. Pankaj Agarwal and Ms. Keerti Choubey for their continuous support and constant encouragement during project work. I would also like to thank each and everybody who has directly or indirectly helped me in the accomplishment of the project.

Finally, I would like to thank my family member for patient understanding, love and support, which make my work possible.

And at last I am also thankful to **STMicroelectronics**, **GREATER NOIDA** for providing me with an opportunity to work with them and undertake a project of such importance.

Tripti Bhargava

# **ABSTRACT**

The objective of the work carried out is to design and implement the 2.5v IO in the 90nm technology according to the specifications required by the end user which act as an interface between the core and the off chip environment. If package is consider as one of the protective layer, then the IO frame is the second protective layer to the core Any external hazards such as electrostatic discharge (ESD) and noises should be filtered out before propagating to the internal circuit for their protection.

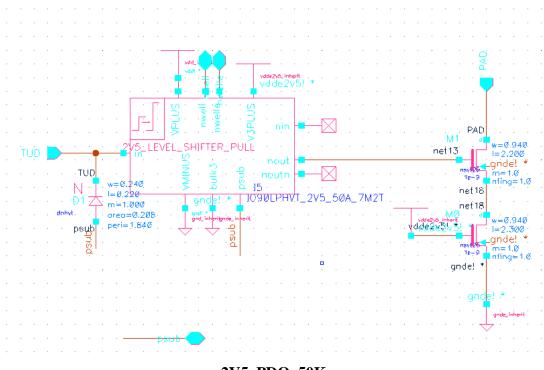

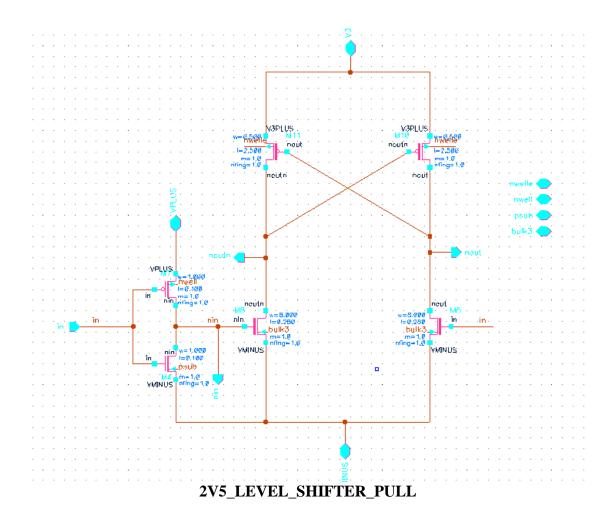

My work concentrates on the designing and the implementation of the output buffer as per the specification required by the end user. On the broader sense an output buffer mainly consist of the Testpin and predriver, Level shifter, Slew rate controller and the 2mAmp driver. To have the complete control over the slew rate against the varied PVT condition compensation codes from the compensation block is used .Implementation of compensation block is out of scope of thesis as it is the property of company STMicroelectronics.In the work carried out various aspects from designing to layout (taking into consideration the latch up issue) to validation have been considered. The design is basically for 90nm technology.

The design quality of I/Os is a critical factor, which is again governed by process corners, voltage and temperature. MOSFET suffer from substantial parameter variations from wafer to wafer and from lot to lot.

Basically four corners have been defined N-fast and P-slow, N-slow and P-slow, N-fast and P-slow, P-fast and N-slow. Besides these four process corners one more process corner has been considered i.e. N-typical and P-typical which may lie some where between fast and slow. Apart from the processes, there may be change in voltage as well as temperature. So for a particular technology high value, typical value and low value of the voltages are decided on which the I/Os as well as core has to operate. Similarly the temperature range has been defined in the range of -40°C to 25°C to 125°C i.e. minimum, typical and maximum respectively.

Besides designing more of the importance has been given to layouts as that is the real system which is going to operate in real world. Certain checks like design rule checks, electrical rule checks and specially latch up prevention has been kept in mind while drawing the layouts as latch up alone can kill whole design by drawing large amount of currents and hence power consumption, which is some thing the deciding factor of a good design and of course for the end user.

## TABLE OF CONTENTS

| Certificate<br>Acknowledgement<br>Abstract<br>Index<br>List of figures<br>List of tables<br>Company profile |                                              | Page<br>I<br>II<br>III<br>IV<br>VI<br>VI<br>VIII<br>IX               |

|-------------------------------------------------------------------------------------------------------------|----------------------------------------------|----------------------------------------------------------------------|

| Chapter 1                                                                                                   | Introduction                                 | 1                                                                    |

|                                                                                                             | 1.1 What are I/O's ?                         | 1                                                                    |

| Chapter 2                                                                                                   | Standard I/O library                         | 3                                                                    |

|                                                                                                             | <ul> <li>2.1 Input Buffers</li></ul>         | 3<br>4<br>7<br>8<br>8<br>9<br>11<br>11<br>12<br>13<br>15<br>16<br>17 |

| Chapter 3                                                                                                   | Design strategy                              | 19                                                                   |

|                                                                                                             | 3.1 Design of I/O elements.3.1.1 Hysteresis. | 19<br>19                                                             |

|                                                                                                             | 3.1.1.1 Circuit Design                       | 20                                                                   |

|                                                                                                             | 3.1.2 Drive strength                         | 22<br><b>Page</b>                                                    |

|                                                                                                             |                                              |                                                                      |

|           | 3.1.3 Basic Design                                    | 23 |

|-----------|-------------------------------------------------------|----|

|           | 3.1.4 Electro static discharge                        | 24 |

|           | 3.1.5 Output pad buffers                              | 28 |

|           | 3.2 Slew control                                      | 34 |

|           | 3.2.1 Active slew rate control                        | 37 |

|           | 3.3 Low power Design Considerations                   | 39 |

|           | 3.4 Input Buffers                                     | 39 |

| Chapter 4 | Design and specifications of bidirectional buffer     | 42 |

|           | 4.1 Naming Convention                                 | 42 |

|           | 4.2 Electrical specifications                         | 43 |

|           | 4.3 I/O specifications for 2.5V BIDIR                 | 43 |

|           | 4.4 Buffers Description (Functionality)               | 44 |

|           | 4.4.1 Bidirectional buffers                           | 44 |

|           | 4.4.2 Output stage                                    | 45 |

|           | 4.4.3 Modes of operation for 2.5 V I/O                | 45 |

| Chapter 5 | Layout Strategy                                       | 47 |

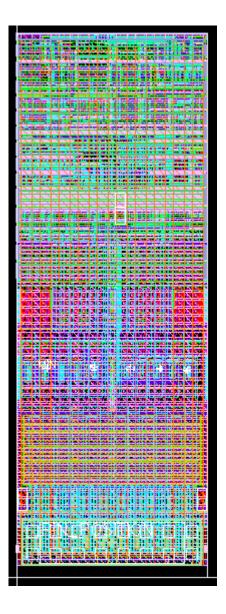

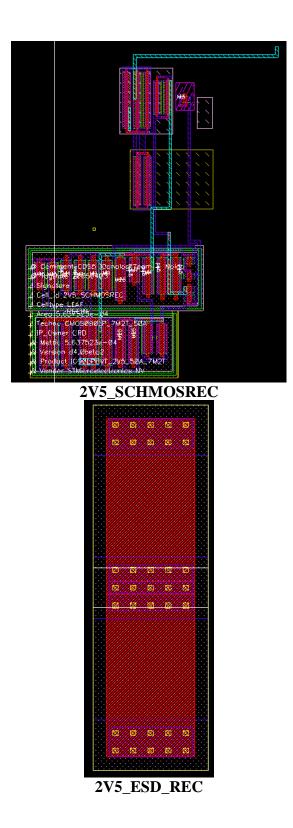

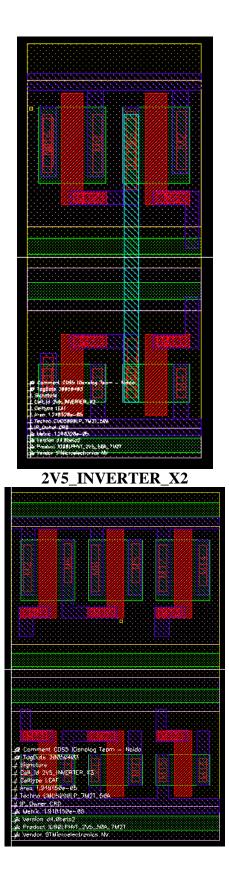

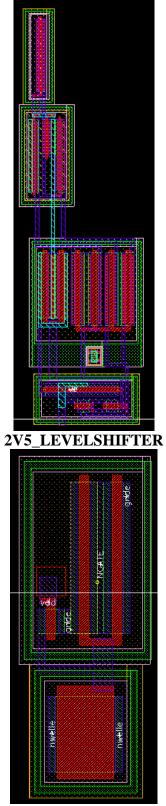

|           | 5.1 Hierarchy                                         | 47 |

|           | 5.1.1 Instantiation and Hierarchy                     | 47 |

|           | 5.1.2 Calibre                                         | 48 |

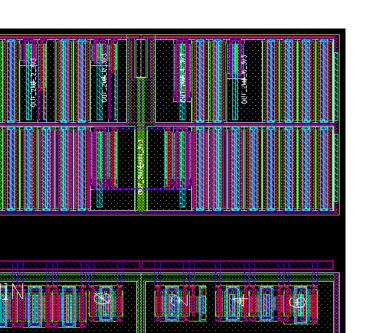

|           | 5.2 Hierarchy in layouts                              | 49 |

|           | 5.2.1 Layout Extraction                               | 49 |

|           | 5.3 Latchup                                           | 50 |

|           | 5.3.1 Tentative latchup design rules                  | 52 |

|           | 5.3.2 Metal thickness rule                            | 55 |

| Chapter 6 | Validation Flow and Analysis of results               | 57 |

|           | 6.1 Flow for simulation of library                    | 57 |

|           | 6.1.1 Eldo simulations and effect of changing W/L     | 60 |

|           | 6.1.2 Simulation results for the bidirectional buffer | 65 |

|           | Future scope                                          | 80 |

|           | Conclusion                                            | 81 |

|           | References                                            | 82 |

|           | Appendix I                                            | 84 |

|           | Appendix II                                           | 89 |

|           | Appendix III                                          | 95 |

## LIST OF FIGURES

|                |                                                    | Page |

|----------------|----------------------------------------------------|------|

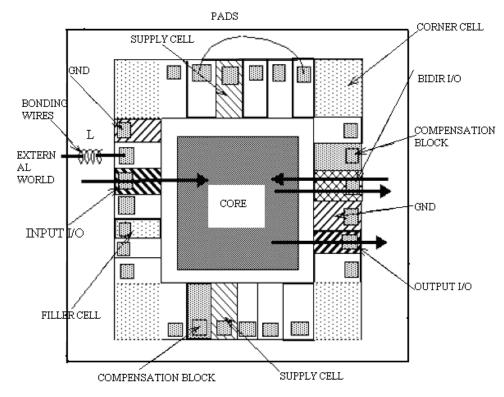

| Figure 1.1     | Input/Output and core in a chip                    | 2    |

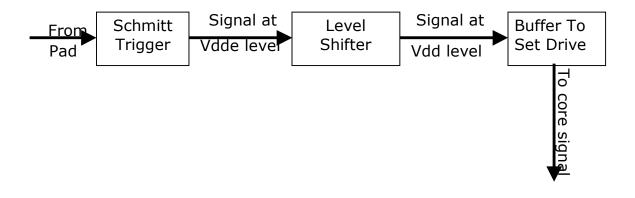

| Figure 2.1     | Block diagram of Input buffer                      | 4    |

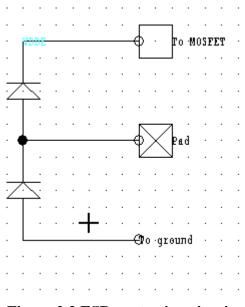

| Figure 2.2     | ESD protection circuit                             | 6    |

| Figure 2.3(a)  | Standard Hysteresis circuit                        | 8    |

| Figure 2.3(b)  | Demonstration of noise decoupling with hysteresis  | 10   |

| Figure 2.4     | Level shifter                                      | 10   |

| Figure 2.5     | Block diagram of O/P buffer                        | 11   |

| Figure 2.6     | Block diagram demonstrating test pin and predriver | 12   |

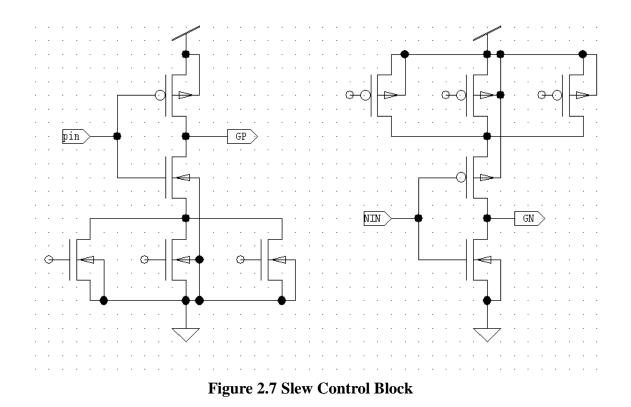

| Figure 2.7     | Slew control block                                 | 14   |

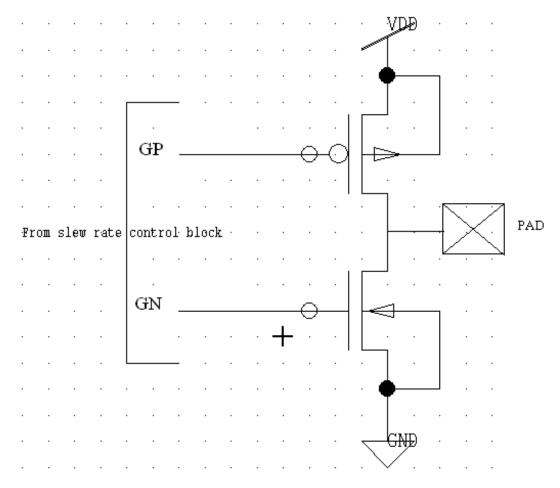

| Figure 2.8     | O/P drivers                                        | 16   |

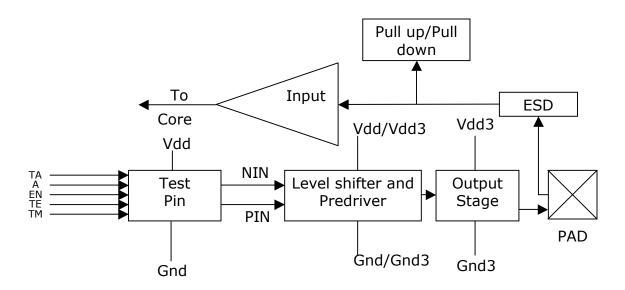

| Figure 2.9     | Block diagram of Input/Output buffer               | 17   |

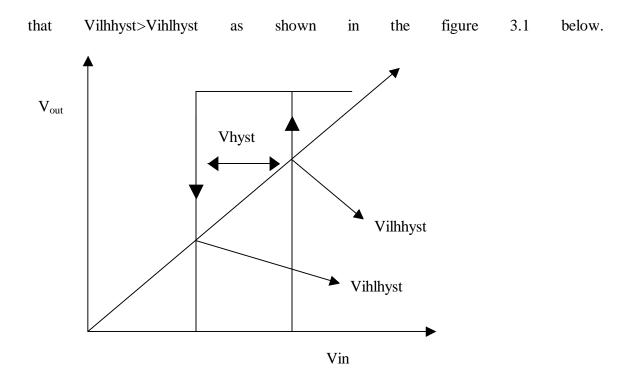

| Figure 3.1     | Hysteresis characteristics                         | 20   |

| Figure 3.2     | Standard Schmitt trigger                           | 21   |

| Figure 3.3     | I/P buffer driving the core                        | 22   |

| Figure 3.4(a)  | Basic inverter circuit                             | 23   |

| Figure 3.4(b)  | Last stage in case of tristate circuit             | 24   |

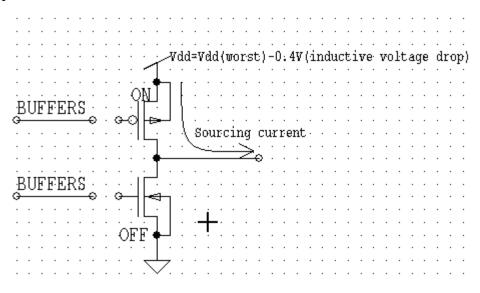

| Figure 3.5(a)  | PMOS sourcing current in X mA buffer               | 29   |

| Figure 3.5(b)  | NMOS sinking current in X mA buffer                | 30   |

| Figure 3.6     | Push pull output stage                             | 31   |

| Figure 3.7     | Open drain O/P stage                               | 32   |

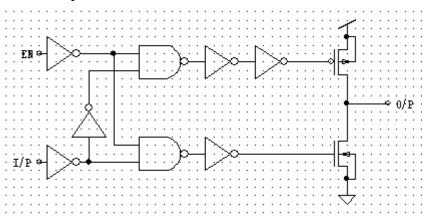

| Figure 3.8(a)  | Tristated pads using NAND gates                    | 33   |

| Figure 3.8(b)  | Tristated pads using NAND and NOR gates            | 33   |

| Figure 3.9     | Output/Input pull-up/down transistors              | 34   |

| Figure 3.10(a) | Slew rate control circuit                          | 35   |

| Figure 3.10(b) | Signal from pre driver stage                       | 36   |

| Figure 3.10(c) | Switched signal at the NMOS driver I/P             | 36   |

| Figure 3.10(d) | Multi stage O/P driver                             | 36   |

| Figure 3.11    | Compensation block                                 | 38   |

| Figure 3.12    | I/P ESD protection circuit                         | 40   |

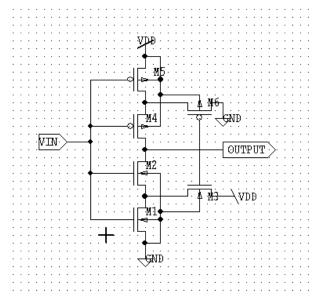

| Figure 3.13    | I/P buffer                                         | 41   |

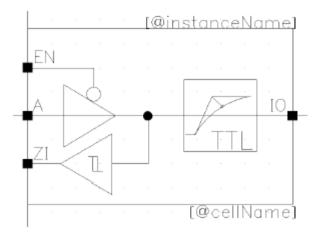

| Figure 4.1     | Bidirectional I/O                                  | 44   |

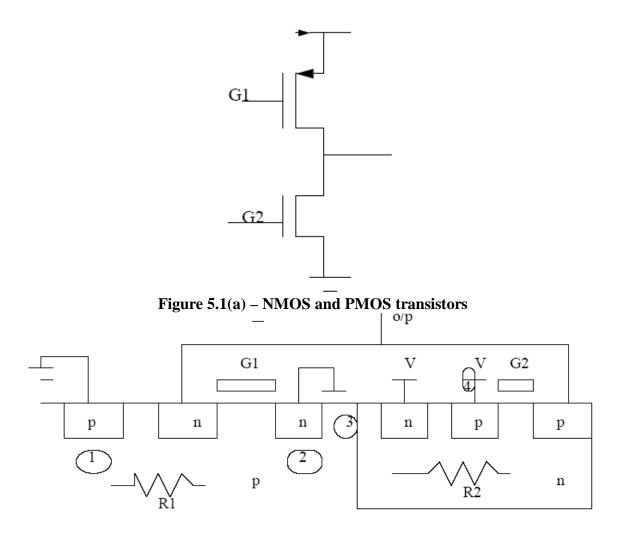

| Figure 5.1(a)  | NMOS and PMOS transistors                          | 50   |

| Figure 5.1(b)  | Effect of latch up                                 | 51   |

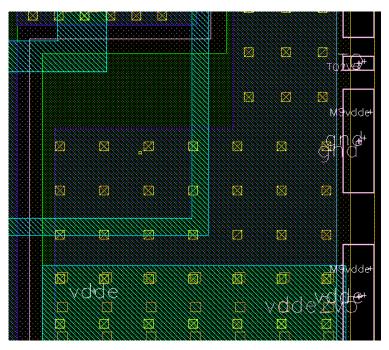

| Figure 5.2(a)  | Measure to avoid latch up                          | 53   |

| Figure 5.2(b)  | Measure to avoid latch up                          | 54   |

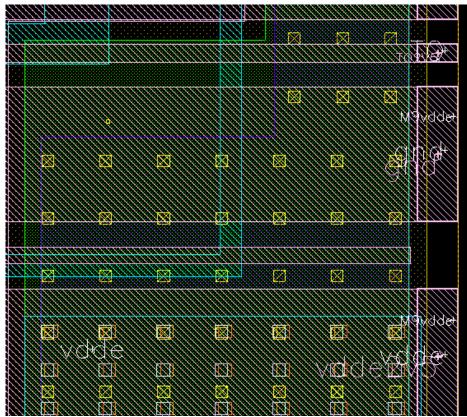

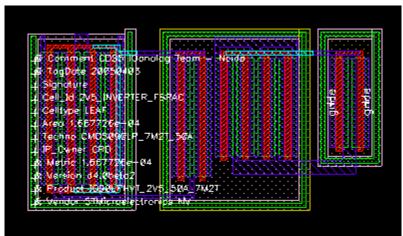

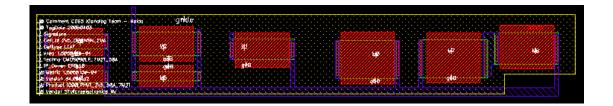

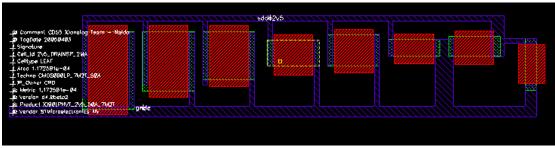

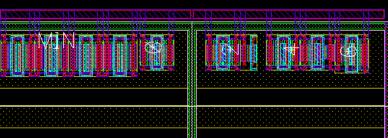

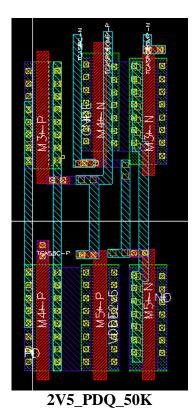

| Figure 5.3     | Layout view corresponding to BD2SCARDQP_2V5_LIN    | 56   |

|                |                                                    | Page |

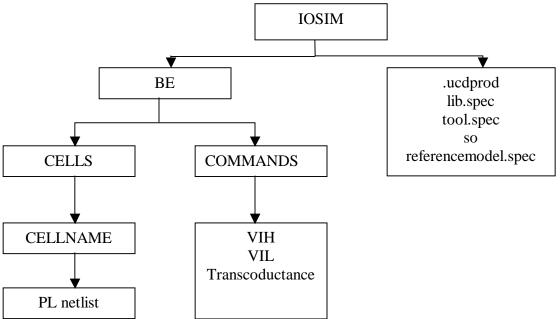

| Figure 6.1  | Directory structure for simulation                 | 58 |

|-------------|----------------------------------------------------|----|

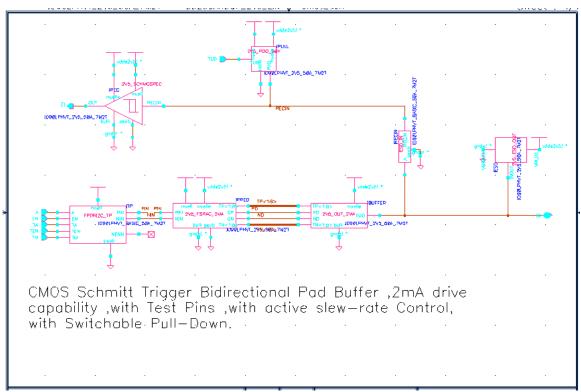

| Figure 6.2  | Block diagram of BD2SCARDQP_2V5_LIN                | 59 |

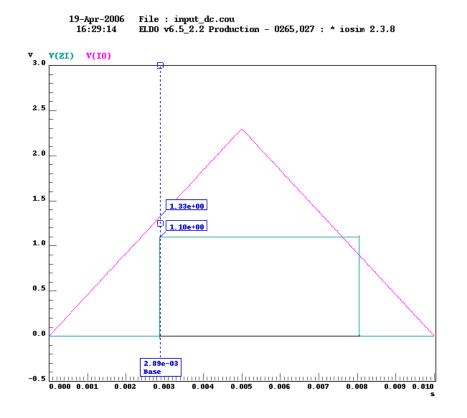

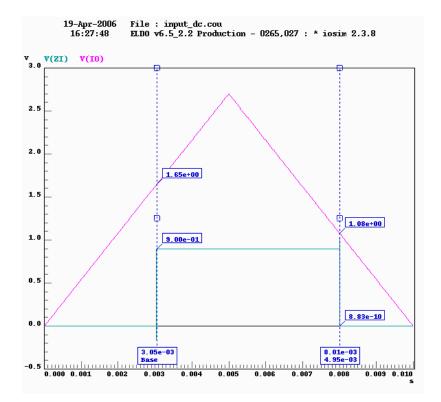

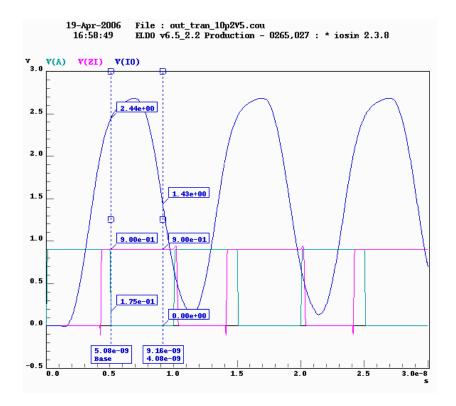

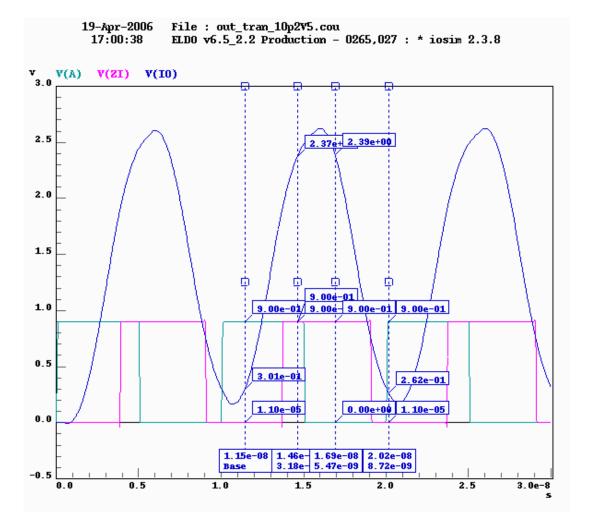

| Figure 6.3  | VIH minimum                                        | 66 |

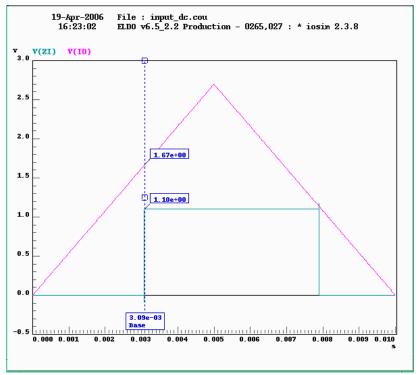

| Figure 6.4  | VIH maximum                                        | 66 |

| Figure 6.5  | VIL minimum                                        | 67 |

| Figure 6.6  | VIL maximum                                        | 67 |

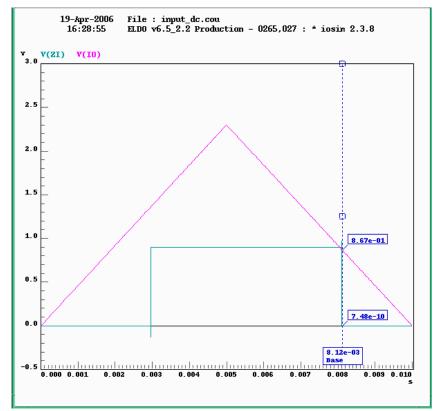

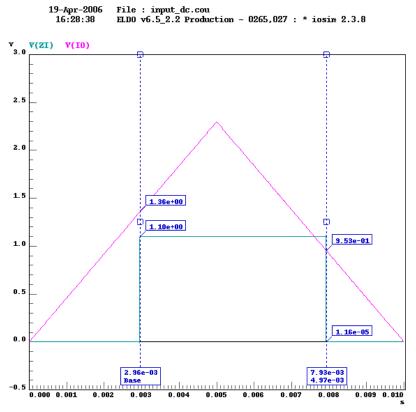

| Figure 6.7  | VHYST minimum                                      | 68 |

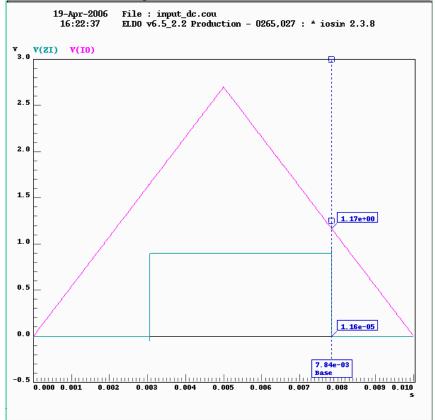

| Figure 6.8  | VHYST maximum                                      | 68 |

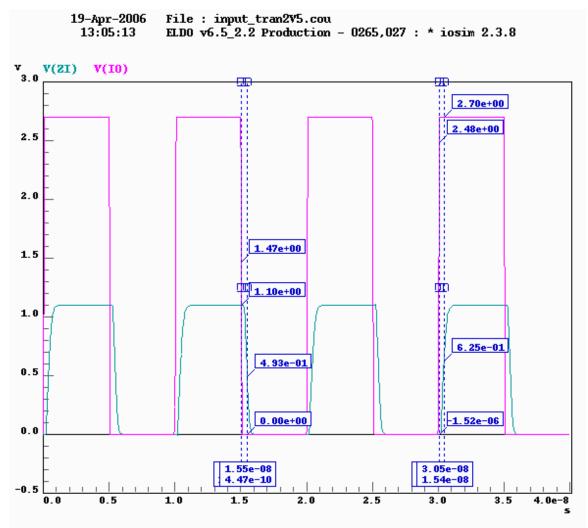

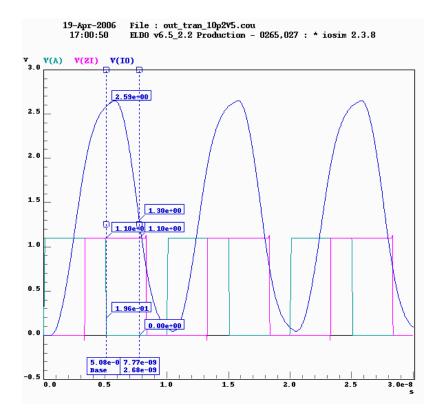

| Figure 6.9  | Minimum Delayfall and Delayrise time in O/P w.r.t. | 69 |

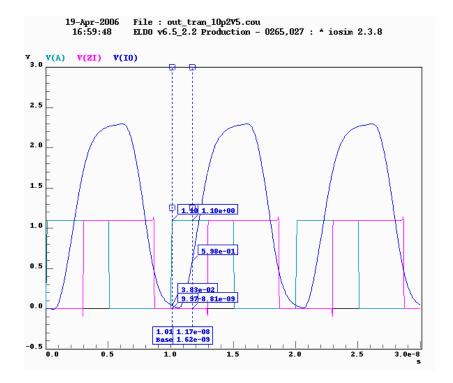

| Figure 6.10 | Maximum Delayfall and Delayrise time in O/P w.r.t. | 70 |

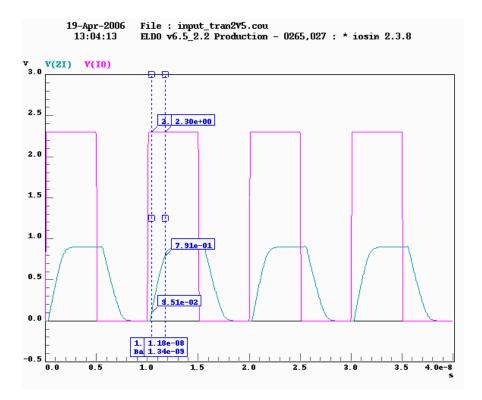

| Figure 6.11 | Minimum duty cycle and fall time                   | 70 |

| Figure 6.12 | Maximum duty cycle and fall time                   | 71 |

| Figure 6.13 | Minimum rise time                                  | 72 |

| Figure 6.14 | Maximum rise time                                  | 72 |

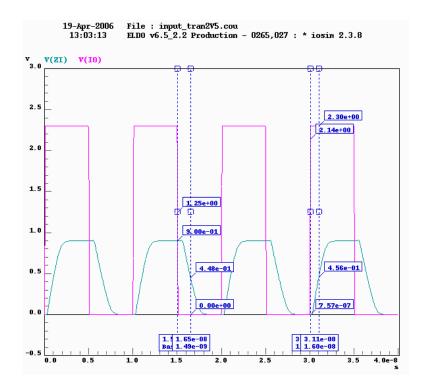

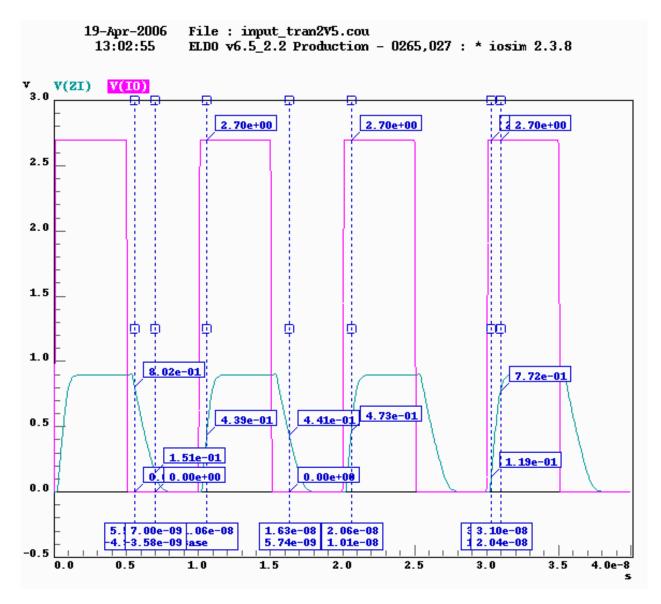

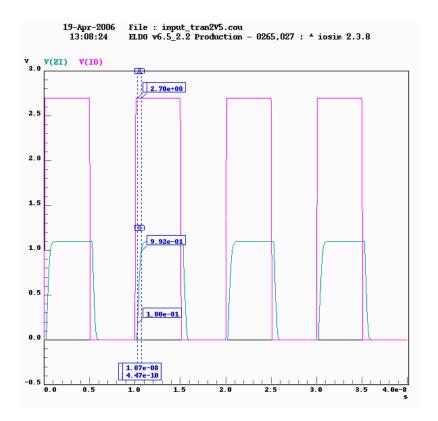

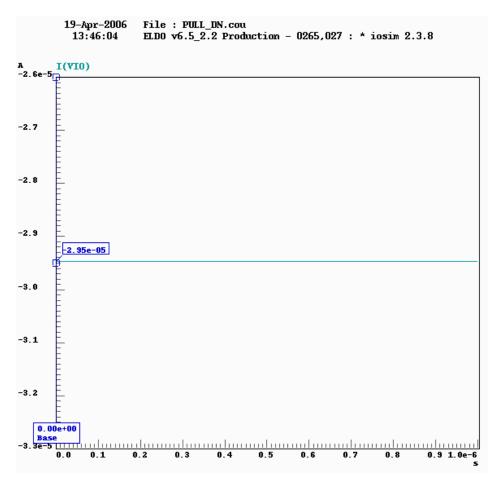

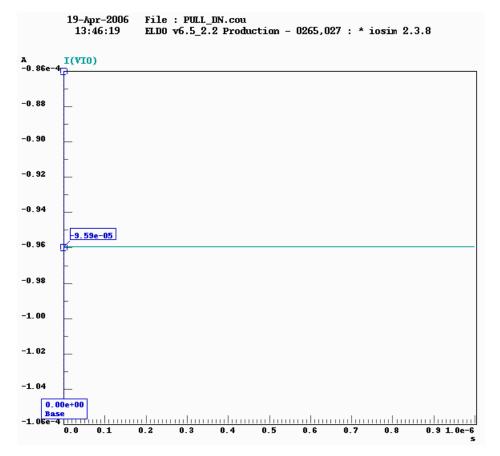

| Figure 6.15 | Minimum pull down current                          | 73 |

| Figure 6.16 | Maximum pull down current                          | 74 |

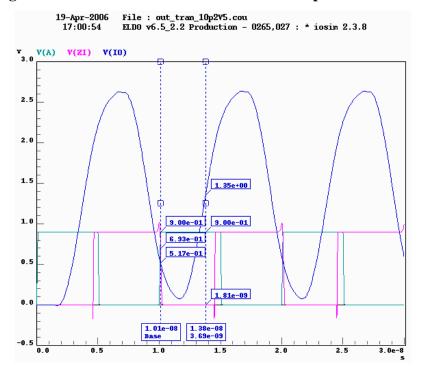

| Figure 6.17 | Minimum fall time in O/P w.r.t. I/P                | 75 |

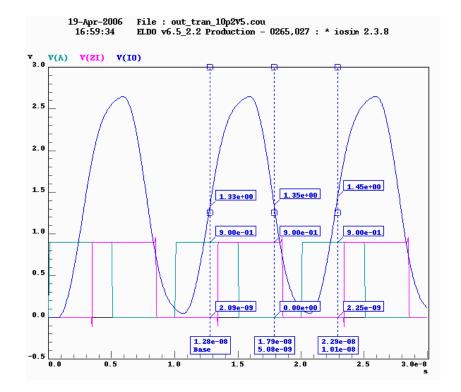

| Figure 6.18 | Maximum fall time in O/P w.r.t. I/P                | 75 |

| Figure 6.19 | Minimum rise time in O/P w.r.t. I/P                | 76 |

| Figure 6.20 | Maximum rise time in O/P w.r.t. I/P                | 76 |

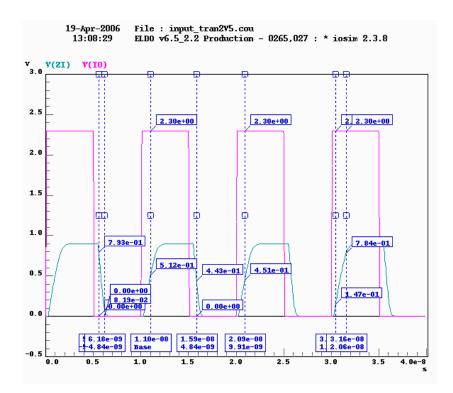

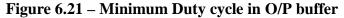

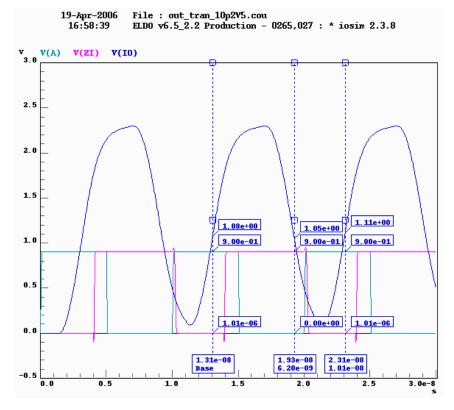

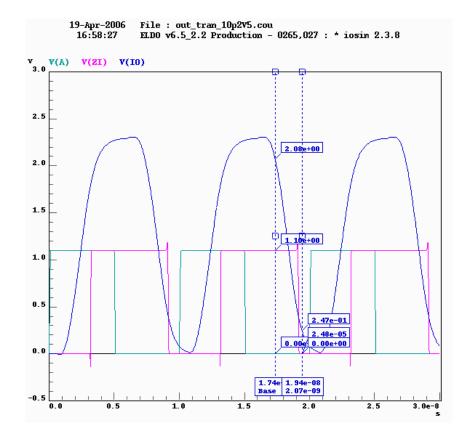

| Figure 6.21 | Minimum duty cycle                                 | 77 |

| Figure 6.22 | Maximum duty cycle                                 | 77 |

| Figure 6.23 | Minimum fall time                                  | 78 |

| Figure 6.24 | Minimum rise time                                  | 78 |

| Figure 6.25 | Maximum fall and rise time                         | 79 |

## LIST OF TABLES

| Table 2.1 | Functionality of test pin block                     | 13 |

|-----------|-----------------------------------------------------|----|

| Table 2.2 | Nomenclature of buffers                             | 18 |

| Table 3.1 | Function of Schmitt trigger                         | 22 |

| Table 3.2 | ESD protection                                      | 26 |

| Table 4.1 | Electrical specifications                           | 43 |

| Table 4.2 | DC I/P specification                                | 43 |

| Table 4.3 | DC O/P specification                                | 43 |

| Table 4.4 | Pull up and pull down characteristics               | 44 |

| Table 4.5 | Modes of operation of a normal bidirectional buffer | 44 |

| Table 5.1 | Metal thickness rule at T=105°C                     | 55 |

| Table 5.2 | Metal thickness rule at T=110°C                     | 55 |

| Table 5.3 | Metal thickness rule at T=125°C                     | 55 |

| Table 6.1 | Results obtained for 2mA block                      | 61 |

| Table 6.2 | Results for slew rate control block                 | 63 |

| Table 6.3 | DC I/P threshold                                    | 65 |

| Table 6.4 | I/P transients                                      | 73 |

| Table 6.5 | Pull down current and resistance                    | 74 |

| Table 6.6 | Sink current and source current                     | 74 |

| Table 6.7 | O/P transients                                      | 74 |

| Table 6.8 | Current consumption                                 | 79 |

## **COMPANY PROFILE**

#### History

The ST group was formed in June 1987 as a result of the merger between SGS Microelettronica of Italy and Thomson Semiconducteurs of France. In May 1998, the company changed its name from SGS-THOMSON Microelectronics to ST Microelectronics. The group totals more than

- 50,000 employees.

- 16 advanced research and development units.

- 39 design and application centers.

- 17 main manufacturing sites.

- 88 sales offices in 31 countries.

STMicroelectronics is a global independent semiconductor company and is a leader in developing and delivering semiconductor solutions across the spectrum of microelectronics applications. An unrivalled combination of silicon and system expertise, manufacturing strength, Intellectual Property (IP) portfolio and strategic partners positions the Company at the forefront of System-on-Chip (SOC) technology and its products play a key role in enabling today's convergence trends.

- Corporate Headquarters, as well as the headquarters for Europe and for Emerging Markets, are in Geneva.

- The Company's U.S. Headquarters are in Carrollton (Dallas, Texas);

- Those for Asia/Pacific are based in Singapore; and Japanese operations are head quartered in Tokyo.

ST is one of the world's largest semiconductor companies

• In 2003, ST's net revenues were US\$7.2 billion and net earnings were US\$253 million.

• ST is also the world's leading supplier of analog ICs, MPEG-2 decoder ICs, and ASICs/ASSPs overall.

- Additionally, in the memory market, ST is ranked fourth in NOR Flash ICs.

- ST is number one for ICs in set-top boxes.

- At number two in smart cards, in hard disk drives, and also in xDSL chips.

- At number three in wireless semiconductors and also in automotive.

The Company's products are manufactured and designed using a broad range of fabrication processes and proprietary design methods. To complement this depth and diversity of process and design technology, the Company also possesses a broad intellectual property portfolio that it has used to enter into cross-licensing agreements with many other leading semiconductor manufacturers.

ST has developed a worldwide network of strategic alliances, including product development with key customers, technology development with customers and other semiconductor manufacturers, and equipment and CAD development alliances with major suppliers. By augmenting its rich portfolio of proprietary technologies and core competencies with complementary expertise from a variety of carefully chosen strategic partners, ST has developed an unsurpassed capability to offer leading-edge solutions to customers in all segments of the electronics industry. The Company currently offers over 3,000 main types of products to more than 1,500 customers.

• Customers: Alcatel, Bosch, DaimlerChrysler, Ford, Hewlett-Packard, IBM, Motorola, Nokia, Nortel Networks, Philips, Seagate Technology, Siemens, Sony, Thomson and Western Digital.

Approximately two-thirds of ST's revenue is derived from differentiated products, a combination of dedicated, semi-custom and programmable products designed to suit a specific customer or a specific application and therefore having high system content. This result reflects ST's exceptionally early recognition of the importance of system-on-chip technology, which is the key for addressing the fast growing market for convergence products, and the success of the strategies it developed to ensure its leading position in this key emerging field.

ST's commitment to environmental responsibility has resulted in substantial reductions in the consumption of energy, water, paper and hazardous chemicals, increased recycling of waste products and a significant cut in CO2 emissions.

In 1999, ST received the United States Environmental Protection Agency's Climate Protection Award for its outstanding accomplishments in protecting the Earth's climate. In 2000, ST was ranked first in environmental management among 14 semiconductor companies by Innovest Strategic Value Advisors and received the only AAA ranking in eco-efficiency. Also in 2002, ST received the Seal of Sustainability from the Sustainable Business Institute and ST's back-end Malta plant received the Management Award for Sustainable Development as part of the European Awards for the Environment 2002, organized by the European Commission Directorate-General Environment. And most recently, ST was awarded the 'Best Industrial Renewable Energy Partnership' as part of the European Commission's Campaign for Take-Off for Renewable Energy Awards 2003.

# Chapter 1

# INTRODUCTION

## 1.1 What are I/O's?

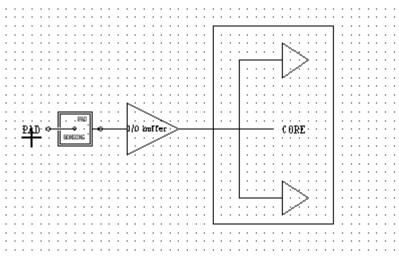

I/O is the specially designed element, which acts as an interface between core signal and off chip environment. A chip can be divided into two main parts:

- 1) Core

- 2) I/O's

Any input signal, which comes from off chip device, has to be checked by the I/O for any discrepancy in its behavior other than the defined for the core and if it finds any characteristic of the signal, which can damage the core, it either modifies the signal or simply rejects it. It also checks the signal going from core to the outside world. So I/Os are responsible for proper functioning of the entire chip and guard the core. Thus however efficient the core design may be, it is the I/O, which determines the efficiency of the chip. It is necessary for the designer to analyze the designed I/O under the practical conditions to verify the deriving strength of the chip, delay in signal, power etc. as they all are heavily dependent on the I/O irrespective of whether the core is compliant with the specifications or not. Because even a minor difference in the performance of the I/O than the desired one can damage the whole circuit or even can cause problems to the off chip circuit, it is the responsibility of the I/O to limit the outgoing signal in all respects like amplitude, frequency, delay etc. (under the specified range), for proper functioning.

Today the I/O structures probably require the most amount of circuit design expertise along with detailed process knowledge [6]. A system designer cannot afford to contemplate I/O pad design and hence has been established the importance of a well characterized I/O library for the process being utilized Any I/P signal which comes from off-chip environment (external voltage are at a typical voltage Vdde level of 2.5V, 3.3V or 5V) into the chip, must be checked by I/O for any discrepancy. I/O acts as protection device for the core. I/O also scans the signal which is going from core to off-chip world. Typically I/Os are placed at the periphery of the core logic i.e. on the sides of the core logic, except on the corners of the cell. They are placed parallel to one another (abutted together using filler cells) and vertical to the enclosure containing the core. Also corner cells are used. This helps in maintaining the power ring continuity throughout the cell, which is very important for uniform distribution of the power to all the I/O inside the chip. [23]

Uniform distribution of power is necessary, as the I/Os are placed all over the periphery and due to large distances between them there is high chance of the power getting degraded, which means I/Os will get power in a broader range than the required one. For e.g. the actual voltage received by one buffer could be 2V and for another one 2.5V Here in CR&D G.NOIDA, general purpose I/O's are designed which can be used for a wide range of applications if they are meeting the required specifications.

# Chapter 2

# **STANDARD I/O LIBRARY**

A Standard I/O library consists of the following components:

- Input Buffers

- Output Buffers

- Bidirectional Buffers

- Compensation cell (If the library contains the active slew rate control buffers)

- Supply cells

- Voltage reference generators

- Leaf cells that constitute above cells

## **2.1 INPUT BUFFERS**

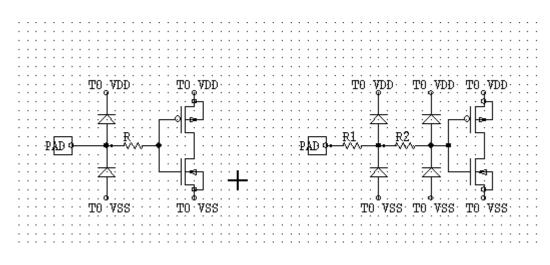

An input buffer couples the external off chip signal to the core elements of the chip. Since the external signal can have voltage ranges much beyond the normal CMOS operating voltages, an input ESD protection is required for these buffers. The non-destructive breakdown of diodes is utilized to clamp the voltage between Vdd and Vss. The resistor tends to decrease the current reaching the gate of devices. The only disadvantage is the introduced RC delay (each diode introducing a capacitance) to the input of the circuit. The design has to be optimized if used in high-speed circuits. ESD protection for buffers today has a major role to play in the efficient chip design. After passing through the ESD block, the signal is applied to the I/P buffer. A typical I/P buffer may be divided into three main stages as represented by the block diagram

Figure 2.1 Block Diagram of Input Buffer

### 2.1.1 ELECTRO STATIC DISCHARGE (ESD)

Electrostatic Discharge, in short ESD, protection is very important to save the chip from unwanted voltage which gets developed at the pin due to some source coming in contact with the pin. These large accumulated charges can destroy the transistor, so a mechanism is needed which can effectively and quickly discharge this unwanted accumulated charge [17]. And here again the importance of metal rings comes into picture as they discharge accumulated charges and protects the chip. Care should be taken that there are no acute angles in the metal layers as they could be a potential areas of hotspots.

An I/P buffer couples the external off chip signal to the core elements of the chip.

Since the external signal can have voltage ranges much beyond the normal CMOS operating voltages, an I/P ESD protection is required for these buffers. Non-Destructive break down of diodes is utilized to clamp the voltages between VDD and VSS. The resistor tends to decrease the current reaching gate. But this block introduces RC delay; hence the design has to be optimized, if used in high-speed circuits.

There are 3 types of ESD stress models [19]

#### 1. Human Body model:

When a charged person touches packaged device, it results in discharge of the charges accumulated at pins when his finger comes in contact with pin, with peak current in Amps of about 100ns duration.

For HBM following factors are important:

Human body capacitance (= 100pf)

- Charging potential (2KV)

- Finger resistance (which limits current in circuit) = 1.5Kohm

### 2. Machine model:

When a machine, which could be a solder iron, bonding machine etc. comes in contact with the pin, charges from the tip of the machine gets transfer to the pin, which results in large current.

In this model, resistance which limits peak current through circuit is much lower (250hm) so RC time constant is small which leads to higher peak current (3-4 amp) as compared to HBM.

### 3. Charged device model (CDM):

In this, ESD event occurs when electro statically charged device (i.e. charge is stored in DUT, Device under Test, itself) is abruptly discharged to ground. CDM pulse has very fast rise time so protection device should turn on fast. Only thermal damage occurs in CDM while both thermal damage & oxide rupture occur in HBM & MM.

Reason for thermal damage:

Flow of high current through circuit results in energy dissipation, which leads to thermal damage.

#### NMOS ESD Phenomena:

For ESD protection, NMOS transistor is used whose drain is connected to PAD. Now if ESD event occurs, it injects minority carrier (holes) in the drain, which leads to substrate current by avalanche phenomena. There is parasitic bipolar with drain as collector, substrate as base, source as emitter. Initially the leakage current flows from drain to bulk via P well, which offers some resistance. The drop across this P well resistance is nothing but voltage across base and emitter of the NPN. As soon as it becomes more than threshold voltage of BJT, the parasitic bipolar turns on. In VI curve it is indicated by snapback region, which starts at ( $V_{t1}$ ,  $It_1$ ) and is followed by second breakdown point ( $V_{t2}$ . $I_{t2}$ ) where thermal damage occurs.  $I_{t2}$  depends on following parameters:

- Heating at drain junction

- Junction depth

- Substrate resistance

- Channel length & finger width

For ESD protection another simple circuit which we use is a diode with one terminal at the pad and other at vdde i.e. the IO cell operating voltage, say 3V3. Under normal condition this diode is reversed biased but if there is some ESD activity the diode will become forward biased and will provide this spike a least resistance path to another very large dimensioned MOSSWI to ground.

Figure 2.2 ESD protection circuit

In the layout we have these diodes as close to the pad as possible. Even the output driver section made of NMOS and PMOS transistors are also close to the PAD. We have two types of diodes in fabrication DP and DN.

- DP diodes are diodes in which we have an outer N-well ring and a P+ inside it.

- DN diodes we have P+ as the outer ring and N+ inside it.

Though these diodes are in no way different from the functioning point of view, it is just the fabrication difference. The diode used by the 5V tolerant library for ESD protection leads to formation of these parasitic transistors, which cause latch-up. The IO buffers will work on a supply of 3.3V (+/-10%), but capable of withstanding standard 5V (+/- 10%) signals at the pad.

#### Effect of Higher voltages on transistors

When 5V on the PAD, the following effects occur: [19]

- For NMOS:

- → Hot electron effect: When 5V on the drain of NMOS, the electron coming from the source may acquire such high energy that they can penetrate the insulting layer of SiO<sub>2</sub> (i.e. they cross the potential barrier of SiO<sub>2</sub> layer) which will affect the threshold voltage of transistor, in other words will change the characteristics of transistor.

Solution Gate -oxide stress potential: When 5V comes on the PAD, the  $V_{ds}$  of NMOS will be 5V, which cross the stress limit (=4V) so transistor becomes stress.

For PMOS:

Flow of substrate current: In case of 5V on the PAD, the diode formed between the p+ of PMOS and the substrate n+ of PMOS becomes forward biased so there will be flow of substrate current pad, without damaging the input/output MOSFETS. For ESD protection of FT libraries, we have this diode when the n-type substrate is at floating potential i.e. VDD5 so if there is a spike greater than 5V on the PAD the diode will be forward biased and will provide a discharge path through MOSSWI which is a very big transistor and provides the ground path.

## 2.1.2 FILLER AND CORNER CELLS (P&R CELLS)

These cells are used for continuity of metal rings which is responsible for uniform distribution of power, ESD protection, and N well closing to prevent latch up. Latch up may be prevented into two basic ways:

1.*latch up resistant CMOS process* – in this method, the substrate is doped with varying degree of doping, bottom is highly doped where as the upper portion is lightly doped compared to bottom. This reduces the parasitic resistance offered by the n well and the substrate; hence reduce the gain of the O/P.

2. *Layout technique* – in this method, P+ substrate of NMOS transistor is surrounded by the N well of the PMOS transistor by collecting minority carriers and preventing them from being injected into the respective bases.

#### 2.1.3 PADS

Pads are basically a sandwich of various metal layers used in the design. The pad consists of pins and metal connections on all sides to provide the power connection to both the core and I/O elements. Multiple power pads are often used to reduce the noise. The internal elements of the I/O circuit being connected to one power pad while the external elements, the circuit part which will have interface with the off chip elements being connected to a different power pad. A metal layer at the bonding pad finally shorts all the power pads. The noisier power pads, the one connected to the O/P transistor are separated from the substrate to prevent the noise coupling through the substrate.

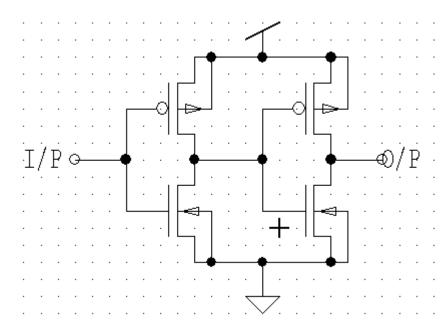

### 2.1.4 SCHMITT TRIGGER

This circuit is used to generate clean pulses from a noisy input signal by providing hysteresis. The basic principle employed for such circuit is the different switching thresholds signals going from 'LOW' to 'HIGH' and 'HIGH' to 'LOW'

Figure 2.3(a) Standard Hysteresis Circuit

#### WORKING:

We can divide the circuit into two parts, depending on whether the output is high or low. If the output is low then M6 is on and M3 is off and we are concerned with the p-channel portion when calculating the switching point voltages, while if the output is high, M3 is on and M6 is off and we are concerned with the n channel portion. Also if the output is high, M4 and M5 are on, providing a DC path to VDD. [16]

Lets begin our analysis of this circuit, assuming that the output is high (=VDD) and the input is low (=0V). MOSFETs M1 and M2 are off while M3 is on. The source of M3 floats to VDD-Vt,n. With Vin less than the threshold voltage of M1, source of M3 remains at approximately VDD-Vt,n. As Vin is increased further, M1 begins to turn on and the voltage, source of M3 starts to fall towards ground. As M2 starts to turn on, the output starts to move towards ground, causing M3 to start turning off. This in turn causes the source of M3 to fall further, turning M2 on even more. This continues until M3 is totally off and M2 and M1 are on. This positive feedback causes the switching point voltage to be very well defined. The curve characteristic of the Schmitt is shown in figure 2.3(b).

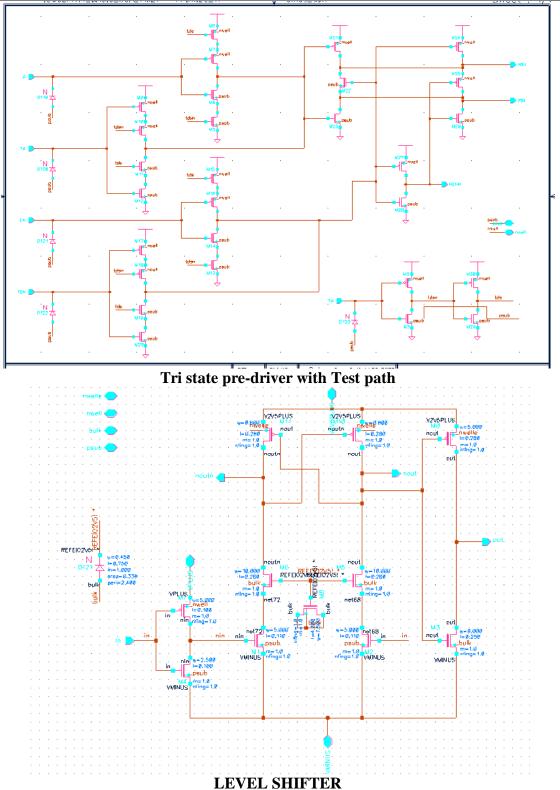

## 2.1.5 - LEVEL SHIFTER

Core circuit works at a voltage of 1.2V (typical) whereas the signals come at higher voltage levels so in order to apply these signals to core we need to lower the voltage level with the help of level shifters.

#### Working

When input is high Nmos-1 (as shown in figure 2.4) will be on and will try to pull down the gate of transistor 4, hence turning it on and simultaneously transistor 2 will be off so the potential at out1 is high and hence transistor 3 is off and as transistor 1 is on, potential at OUT2 is low.

Figure 2.3(b) Demonstration of Noise Decoupling With Hysteresis

Figure 2.4 level shifter

## 2.1.6 - INPUT DRIVER

It is used to set drive i.e. the current capability to charge the load capacitor to the desired value in given time. Circuit is designed in such a way that the aspect ratio (W/L) which is inversely proportional to resistance, of the transistors used in input drive section, has a value which in turn returns the required time constant. Input buffers are available with two possible drives towards the core

- Normal drive which is equivalent to an X4 drive in the standard digital library. These cells are characterized with internal loads up to 80 standard loads i.e. 0.72pF.

- High drive which is equivalent to an X16 drive in the standard digital library. They are characterized with loads up to 316 standard loads i.e.2.84pF.

# **2.2 OUTPUT BUFFER**

These interface the outgoing signals from the core to the off chip environment. Hence these are used to drive large capacitive loads which arise from long interconnect lines such as clock distribution networks, high capacitance fan out and high off chip loads. The drive capability of such a buffer should be such as to achieve the requisite rise and fall times into a given capacitive load. Normally the drive capability of I/O buffers is as high as 8 mA. By driving capability, it means that the output buffer can source or sink the specified amount of current in the worst case.

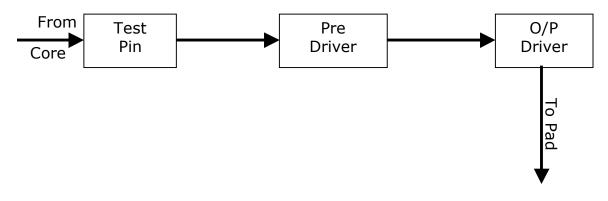

Figure 2.5 Block diagram of output buffer

### 2.2.1 TESTPIN & PREDRIVER

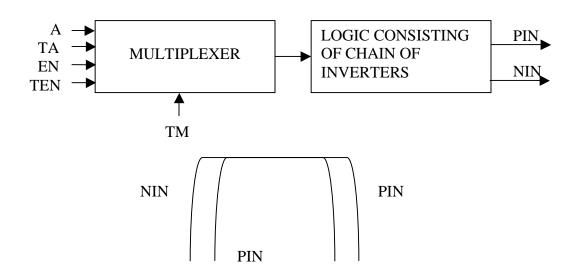

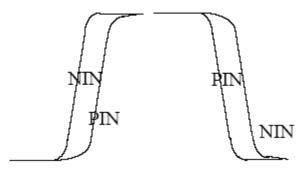

This is connected between the core and Slew Rate Controller. It is basically comprised of multiplexer and chain of inverters It works in two modes test mode and basic operating mode. And multiplexer is there to select test or basic operating mode. The multiplexer is followed by the series of inverter to generate two signals NIN and PIN for slew rate control. Signal at NIN rises faster than PIN signal and signal at PIN falls faster than NIN signal. This is done to ensure that the O/P drivers transistors should not have large dynamic current

TM = 1, buffer goes in test mode

TM =0, Normal operation

A: input data coming from the core and is transmitted to PAD

EN: input enable pin to enable the O/P section

TA: input test mode data pin

TEN: input enable pin, to enable the O/P section when it is in test mode.

| Mode                     | TM | TEN | en | TA | А | NIN | PIN |

|--------------------------|----|-----|----|----|---|-----|-----|

| NORMAL O/P MODE          | 0  | Х   | 0  | Х  | А | А   | А   |

| NORMAL I/P MODE          | 0  | X   | 1  | Х  | Х | VDD | 0   |

| TEST MODE FOR O/P BUFFER | 1  | 0   | Х  | TA | Х | TA  | TA  |

| TEST MODE FOR I/P BUFFER | 1  | 1   | Х  | Х  | Х | VDD | 0   |

**Table2.1 - Functionality of Test Pin Block**

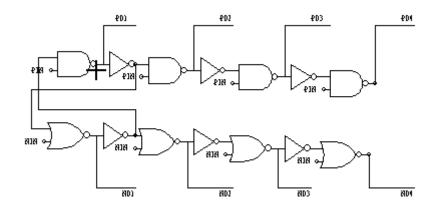

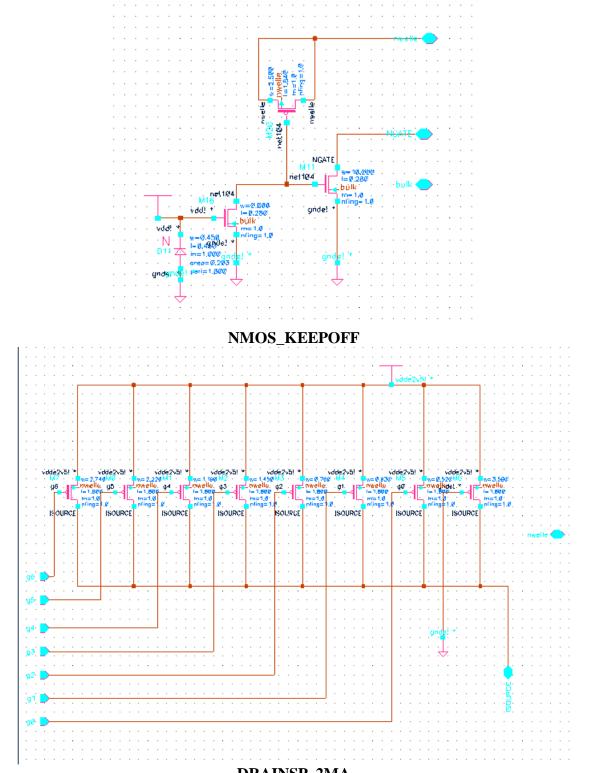

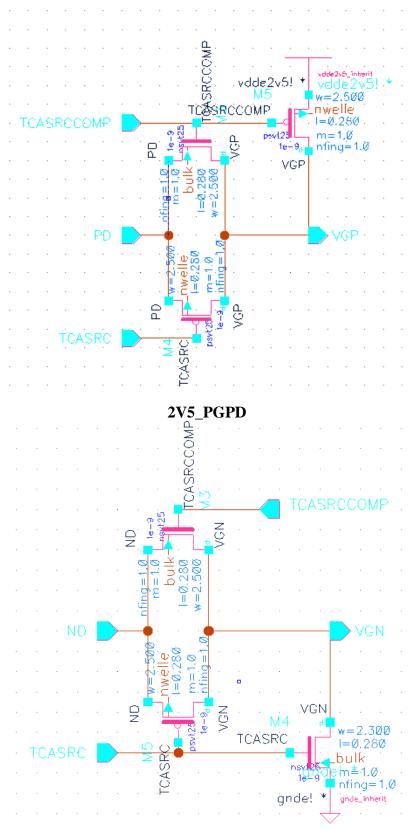

#### **2.2.2 SLEW RATE CONTROLLER**

Inductance introduced by the package pins and transmission wires introduce noise, which is the inductive voltage, in the signal. A fast transition of the signal at the output pad tends to introduce frequencies in UHF range into the off chip load.

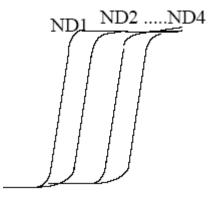

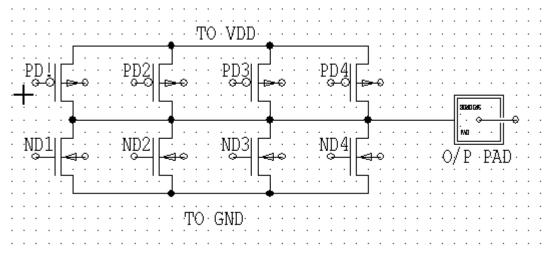

To reduce noise, we generally control the switching which reduces the rate of change of current at the output e=Ldi/dt, e = inductive voltage, L = inductance of pins and wires, di/dt = rate of change of current. Slew rate control circuits thus artificially limit the rate of current. One way to achieve this is by breaking the output driving transistors into a series of parallel transistors and switch the stages sequentially one after the other with some delay [18]. The slew rate control circuit consists of a series of NAND and nor gates which are driven by PIN and NIN signals respectively. As there is sequential delay in both NAND and NOR chain, thus they drive the series of output transistors sequentially. This results in total controllability over the rate of change of output current and hence slew rate can be controlled. These slew rate controllers are hard coded so they are unable to counter PVT variations in slew. So to compensate for the change in slew rate in changing PVT conditions, codes are fed through a compensation block which generates the code according to the conditions. Compensation block has only an enable pin and the output pins. This block senses the change and generates a common code for the entire slew rate controlling devices. If in special cases we require different slew rate for different I/O some modification is done at the cell level by adding special circuitry, which modifies the code generated by the compensation block.

GP and GN are signals, which are connected to the gate of PMOS and NMOS of O/P drivers respectively. So to control the rate current signal at the O/P pad, we control the switching of these O/P transistors i.e. conditional GP and GN signals. Since GP is connected to PMOS so the falling edge of GP is made slow which implies that rising edge of PIN signal has to be controlled i.e. made slow, so NMOS of driver in the slew block is made weak (increasing the length of NMOS) by connecting NMOS in series, similarly to control the GN connected to the NMOS of O/P driver, PMOS is connected in series with PMOS of driver in the slew block (increasing the length of PMOS) to control the rising edge of GN signal.

In most applications, slew gets affected due to change in PVT's condition, than a series of NMOS and PMOS is connected in parallel instead of one NMOS and PMOS. The gates of those transistors are controlled by the codes generated by compensation block. Depending upon the PVT condition, compensation block generate codes which decides the number of parallel connected transistors to turn on, then these combined transistors condition the signal connected to the gate of O/P transistors of drivers which in turn controls the rise and fall of the voltage/current at the O/P pad.

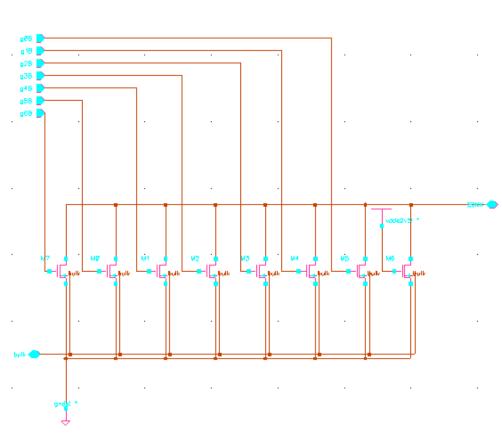

## 2.2.3 - OUTPUT DRIVER

An output buffer must have sufficient drive capability to achieve adequate rise and fall times into a given capacitive load. Drivers are nothing but series of inverter, which sink or source current. Their size depends upon the desired drive strength [3].

The O/P drivers are divided into N inverters, the gate of which is permanently tied to the signal coming from the slew control block, thus this driver decides the current sourcing/sinking capability in best conditions. The gates of other inverters are connected to the signal coming from the slew block through the pass gates, which are controlled by TSASRC codes, which are generated, by the compensation cell. Depending upon PVT condition, compensation will generate the TSASRC codes and these codes select the number of drivers connected in parallel i.e. depending upon PVT condition the driver size are changed which control the falling edge of current at the pad.

To achieve the specified functionality of the output buffer, different types of output stages are used.

#### 1. Push-Pull Stage

A push pull stage consists of p and n transistors at the output pad for sourcing and sinking respectively where each of transistors is controlled through a different chain of tapered inverters fed after buffering. This has two advantages:

1) No direct gate contacts of the two output driver transistors

2) Static and short circuit power dissipation can be avoided by bifurcating the inverter chain in such a way such that while sourcing current at the O/P pad, NMOS driver is made off before PMOS is on and vice versa.

#### 2. Open Drain Output Stage

This has an advantage over the push pull, and that is, it has just one driver stage. Such configuration avoids gate source-drain capacitance, thus making it faster than push pull. But this configuration can either sink or source current at a time, which limits its usage. The output state of the pad can also be driven to tristate and can be connected to buses where high impedance state is required for data transfer. This is mainly used in buses.

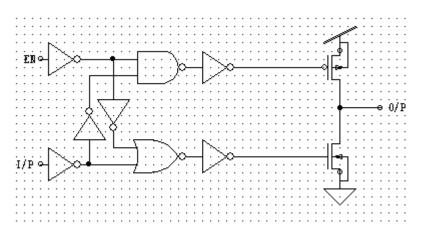

#### 3. Push Up/down Stage

Often the tristated output is put to a particular logic level instead of letting the bus float. Either logic low or high can be made at the output using the pull up or pull down transistors Normally the NMOS transistor is used for pull down and PMOS transistor for pull up. But the strength of the transistor is so chosen that when a logic level appears at the output from core, it must overcome the pulling up or pulling down action.

**Figure 2.8 Output Drivers**

# 2.3 - BIDIRECTIONAL BUFFER

This contains both input and output buffers and signal can enter as well as leave the core as shown in figure 2.9.

Advantage of input buffers or output buffers over bidirectional buffers is that due to smaller circuitry in them there is less leakage current.

In standard libraries, the end user is provided with both so that it can be used as per the requirement.

Figure 2.9 Block Diagram of Input Output Buffer

# 2.4 ABOUT I/O LIBRARIES

A standard library contains the above-explained cells. Each of the above mentioned categories might have different number of cells each pertaining to different specifications.

Each of the I/O libraries is identified by its nomenclature. Input buffers, output buffers and bidirectional buffers have got their own way of nomenclature as mentioned in table 2.2. [23]

| INPUT                  | INPUT BUFFER OUTPUT BUFFER BIDIRECTIONAL |                        | CTIONAL                 |                         |                           |

|------------------------|------------------------------------------|------------------------|-------------------------|-------------------------|---------------------------|

|                        |                                          |                        |                         | BUFFER                  |                           |

| IBUF                   | CMOS I/P                                 | В                      | Push pull               | BD                      | Bidirectional             |

|                        | buffer                                   |                        | O/P buffer              |                         | buffers                   |

| TLCHT                  | TTL for I/P                              | BT                     | Tri state O/P           | 1 <sup>st</sup> suffix  | Drive                     |

|                        | buffer                                   |                        | buffer                  |                         | capability in             |

|                        |                                          |                        |                         |                         | mA                        |

| SCHMT                  | I/P Buffer                               |                        |                         | 2 <sup>nd</sup> suffix  | H for high                |

|                        | with                                     |                        |                         |                         | drive I/P                 |

|                        | Hysteresis                               |                        |                         |                         | stage                     |

| 1 <sup>st</sup> suffix | T for TTL                                | 1 <sup>st</sup> suffix | Drive                   | 3 <sup>rd</sup> suffix  | ZI for tri state          |

|                        | levels,                                  |                        | capability in           |                         | I/P stage, AI             |

|                        | C for CMOS                               |                        | mA                      |                         | for gated I/P             |

|                        | levels                                   |                        |                         | 4b                      | stage                     |

|                        |                                          |                        |                         | 4 <sup>th</sup> suffix  | S for schmitt             |

| nd                     |                                          |                        |                         | da.                     | trigger on I/P            |

| 2 <sup>nd</sup> suffix | H for high                               | 2 <sup>nd</sup> suffix | C for CMOS              | 5 <sup>th</sup> suffix  | T for TTL                 |

|                        | drive I/P                                |                        | (Absence of             |                         | levels, C for             |

| ard arr                | stage                                    | e trid                 | C=TTL)                  | -th art                 | CMOS levels               |

| 3 <sup>rd</sup> suffix | AI for gated                             | 3 <sup>rd</sup> suffix | R for slew              | 6 <sup>th</sup> suffix  | R for slew                |

|                        | I/P                                      |                        | rate control,           |                         | rate control,             |

|                        |                                          |                        | AR for                  |                         | AR for active             |

|                        |                                          |                        | active slew             |                         | slew rate                 |

| 4th cc                 | TT C                                     | th cr                  | rate control            | <b>–</b> th cc          | control                   |

| 4 <sup>th</sup> suffix | U for active                             | 4 <sup>th</sup> suffix | OD for open             | 7 <sup>th</sup> suffix  | OD for open               |

|                        | pull up                                  |                        | drain                   | 8 <sup>th</sup> suffix  | drain O/P                 |

|                        | D for active                             |                        |                         | 8 <sup>th</sup> suffix  | U for active              |

|                        | pull down                                |                        |                         |                         | pullup, D for             |

|                        |                                          |                        |                         |                         | active pull               |

| 5 <sup>th</sup> suffix | O for and 1                              | 5 <sup>th</sup> suffix | D for tost              | 9 <sup>th</sup> suffix  | down                      |

| 5 suffix               | Q for switch                             | 5 SUITIX               | P for test              | 9 suffix                | Q for switch              |

|                        | on pull-up                               |                        | functions               |                         | 0n                        |

| 6 <sup>th</sup> suffix | down<br>_TC for x V                      | 6 <sup>th</sup> suffix | _TC for x V             | 10 <sup>th</sup> suffix | pullup/down<br>P for test |

| o sumx                 | capable                                  | o sumx                 | capable                 | IU SUIIIX               | functions                 |

|                        | FT for y V                               |                        | FT for y V              | 11 <sup>th</sup> suffix | TC for x V                |

|                        | _r i for y v<br>tolerant                 |                        | _r1 for y v<br>tolerant | 11 SUIIIX               | _1C for x v<br>capable    |

|                        | toiciant                                 |                        | tolerallt               |                         | _FT for y V               |

|                        |                                          |                        |                         |                         | _r1 for y v<br>tolerant   |

| 7 <sup>th</sup> suffix | ISO for                                  | 7 <sup>th</sup> suffix | _ISO for                | 12 <sup>th</sup> suffix | ISO for                   |

| / SUIIIX               | isolated from                            | / SUIIIX               | isolated from           | 12 SUIIIX               | isolated from             |

|                        | substrate                                |                        | substrate               |                         | substrate                 |

|                        |                                          | hla ? ? Nam            | substrate               |                         | substrate                 |

Table 2.2- Nomenclature of Buffers

# Chapter 3

# **DESIGN STRATEGY**

## **3.1 Design of I/O elements**

In the design of Input/output buffers, there are some critical aspects, which have to be taken into consideration at various design levels. Main focus will be on designing the circuit for hysteresis, ESD protection circuit, Driver (simple inverter) and Current buffer with Xma driving capability (where X is any number in suitable range) and certain aspects regarding active slew rate control will also be discussed.

## **3.1.1 Hysteresis**

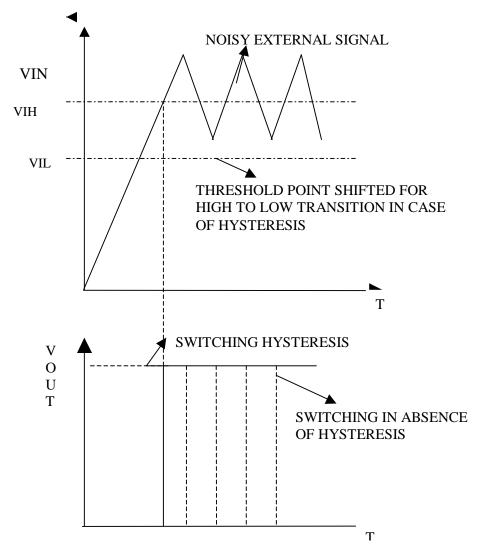

Hysteresis is often required in input buffers to decouple the noisy external signal from the core circuitry of the chip [4]. For a noisy external signal we desire that the buffer doesn't switch it's state due to noise. We should have a margin for the noise considerations as shown in the figure 3.1. As long as the signal doesn't go below Vilhyst the o/p doesn't change. So you have a margin of Vihhyst - Vilhyst. Normally, without hystersis it will start changing as soon as the voltage goes below Vihhyst (in this case).

The basic principle employed for such circuit is the different switching thresholds for input signals from low to high and high to low transitions ie, when we apply low voltage to the i/p and ramp it up to the high level the threshold point comes say at a point Vin = Vilhhyst. Simmiliarly when we apply a high voltage at the i/p and decrease it the threshold point comes at point Vin = Vilhhyst. We need these points to be different such

**Figure 3.1-Hysteresis Characteristics**

#### **3.1.1.1 CIRCUIT DESIGN**

As mentioned above the idea is to achieve different threshold points.

#### 3.1.1.1 Standard hysteresis circuit

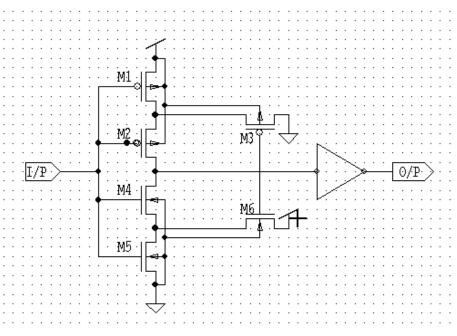

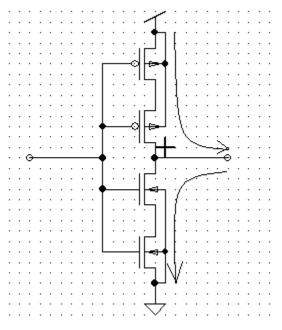

Figure 3.2 shows a very commonly used Hysteresis circuit. Here the different threshold voltages of n-channel and p-channel transistors are used as advantage. The Schmitt trigger proper consists of three p-channel devices M1 to M3 and three n-channel devices M4 to M6.

#### Functioning

For the dc voltage sweep from low to high at the input ,though M5 turns ON after Vin > Vtn5 ,M4 does not turn ON as Vt4 (threshold voltage of M4) is shifted due to body affect. Hence output voltage remains at high level .The source of M4 is initially at a voltage of VDD -Vt6 (body affected).But after Vin> Vtn5, the voltage at node N1 begins to fall. Here M6 and M5 form an inverter pair, having a feedback effect with M6 acting as a resistive load. As soon as VGS4 > Vt4 (body affected), M4 gets ON and output node

is immediately pulled to the ground. Also the drive strength of nMOS M4 and M5 is more compared to the pMOS M2 and M1.This explains the sharp transition characteristics of the circuit. The value of Vihhyst depends primarily on W/L of M6 and M5 for a given technology (Vtn fixed). Keeping M6 fixed, greater is the W/L of M5, and faster is the rate at which the node N1 is pulled down. This pulls up the switching threshold Vihhyst to a lower value towards left in figure 3.1.A similar explanation ensues for the input. Going high to low and feedback transistor M1 and M2 forming the inverter pair with M3 as a resistive load. Here the switching threshold Vilhyst depends primarily on W/L of M1.The difference in the two logic thresholds is achieved by a different pMOS and nMOS body affected threshold voltages.

Figure 3.2 Standard Schmitt trigger

| Approximate values of Vilhyst and Vihhyst can be obtained using [1] |

|---------------------------------------------------------------------|

| k5/k6=((Vdd-Vihhyst)/(Vihhyst-Vtn))2(eq1)                           |

| k1/k3 = ((Vilhyst)/(Vdd-Vilhyst- Vtp ))2(eq2)                       |

#### Advantages/Disadvantages

The driving transistors M2 and M4 show racing conditions when the transition begins. The switching points of the circuit cannot be defined precisely because the circuit is

| Transistor | Change      | Rising    | Falling   |

|------------|-------------|-----------|-----------|

|            |             | threshold | threshold |

|            |             | Vihhyst   | Vilhyst   |

| M3         | W increases | No change | Decreases |

| M6         | W increases | increases | No change |

| M1         | W increases | increases | increases |

| M5         | W increases | Decreases | Decreases |

| M2         | W decreases | Decreases | Decreases |

| M4         | W decreases | increases | increases |

based on a rationed operation. The NMOS inverter M5, M6 and the PMOS inverter M1, M3 are rationed circuits.

Table 3.1- Functioning of Schmitt trigger

## **3.1.2 Drive strength**

"Drive Strength" of an input buffer is the capacity of the buffer to "drive" the specified load inside the CORE as shown in the figure 3.3

Figure 3.3- I/P buffer driving the core

The "Drive Strength" of the Buffer is primarily decided by the size of the last stage transistor. The bigger the size the greater is its drive capability. As expected the PMOS transistor decides its current sourcing capacity whereas the NMOS decides its sinking capacity.

Till a certain point we gain in terms of speed of buffer as the drive capability of the transistor is increasing after which greater area and the capacitance effect at the internal node takes over which slows down the buffer in terms of the slopes and delays. Also this may increase to such extend that previous stage may not be able to drive the large capacitance of the last stage. Tapering of buffers may be required which may result in layout area increase. Smaller the sizes of the transistor may result in very less drive capability, which may prevent the buffer to drive the required number of gates in the CORE.

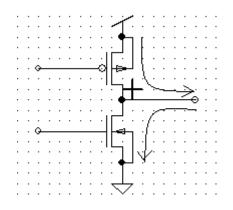

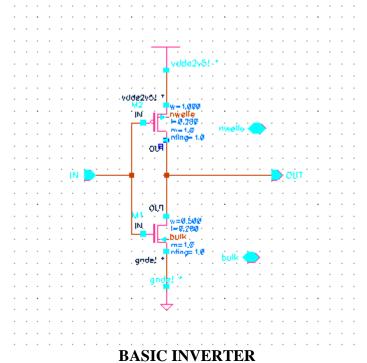

#### **3.1.3 BASIC DESIGN (Simple inverter)**

Mostly the last stage would be a simple inverter whose PMOS and NMOS transistor Width's decide the drive strength. The last stage could also be cascoded transistors as shown in the figure 3.4(a). Here The Widths should be calculated accordingly. The supply should be of the same level as the one driving the CORE

Figure 3.4(a) - Basic inverter circuit

#### ANY OTHER

Some times the last stage may not exactly be an inverter like in a tristate circuit. But the principle remains the same. The PMOS, when ON, should be able to drive the desired load maintaining the slope requirements and similarly the NMOS ON should be able to do the same as shown in the Figure 3.4(b). The last stage is not exactly an inverter. Supply should be of the same level as the one in the CORE.

Figure 3.4(b) - Last stage in case of tristate circuit

#### **GUIDELINES FOR CIRCUIT TUNING**

The Standard drive Widths for CORELIB are calculated by seeing Power\*Delay Product, Rise times, fall times and Delays v/s Wp/Wn of an inverter [21], whereas for the IOLIBs we try to keep the threshold point very close to the center of the swing (vdd/2). This is generally very close the value of the CORELIB cell.

#### TECHNOLOGICAL CONSTRAINTS

The Considerations with the technology generally will include

- Finding the corresponding Wp/Wn ratio.

- The minimum Width technology constraints.

- The Number of transistors minimum sized inverter can drive.

- Accordingly we decide on the drive strength.

## **3.1.4 Electrostatic Discharge**

ESD is the discharge of large amounts of electrostatic charges on to the chip causing irreversible damage to the chip like gate oxide breakdown, snap-back, gate drain shorts

etc. Various reasons could be touching the chip with bare hands, touching with charged instruments etc. This has today become a major study area since a lot of chips are damaged due to these phenomena.

# Optimization of ESD protections in IC is a task to be addressed

# at two different levels:

- 1. Elementary protection structures

- 2. Device protection network

# **Elementary protection structures**

- Components suitable to accomplish a localized and effective energy discharge path.

- Are annexed to pad circuitry

- Can be active elements of the device

- ESD failure modes are related to the pad architecture and the discharge model.

- ESD protection devices should be chosen and optimized to fit the requirements of different pads.

- These structures should have minimum impact on the functional behavior of the device

- Protection architecture should be full consistent with the process flow

# **Device protection network**

- The set of elementary protection structures (e.g. power supply protections) and "passive" elements (metal bus, substrate taps, guard rings) involved in any possible discharge path.

- Optimized elementary protections are necessary but not sufficient to achieve ESD immunity.

- In actual devices it is not possible to implement an elementary protection between any pair of pads.

- Taking advantage of existing metal bus, substrate taps, and guard rings. It is possible to organize the protections in a network providing a safe discharge path for each ESD configuration.

### **Typical ESD failures:**

- Oxide damage at the drain/gate overlap in n channel with drain directly connected to the supply lines

- $V_{ESD} > V_{bkd}$  (OX)

- Drain contact /junction damage in the n-channel biased in snap back by the ESD pulse.

### What is snap - back?

- A parasitic lateral NPN bipolar is associated to any n channel transistor

- Turning -on this bipolar is termed as the snap back.

- Irreversible damage is caused by the snap-back in not optimized structures.

- Junction avalanche inducted by the ESD can turn on this bipolar causing snap back.

- It is possible to rely on snap-back to develop an optimized MOS protection structure

### What should the protection devices protect?

| CMOS INPUTS         | Gate oxide breakdown                             |  |  |

|---------------------|--------------------------------------------------|--|--|

|                     | Gate to Vcc protection                           |  |  |

|                     | Input diffusion to nearby diffusions             |  |  |

| CMOS output buffers | Damage to the drain/substrate junctions          |  |  |

|                     | Damage to the drain contacts                     |  |  |

|                     | Drain gate filament damage                       |  |  |

|                     | Drain source melt filaments                      |  |  |

| POWER pins          | Damage to the internal circuits                  |  |  |

|                     | Increase in the post ESD I <sub>dd</sub> leakage |  |  |

# Table 3.2- ESD protection

# What should the protection devices do?

Input/Output/Supply Pins

• Clamp the ESD voltage to shunt the ESD Stress Current

- Turn on Fast (Less than 1 ns)

- Carry Large Currents of 2 Amps or more for 150ns

- Have Low on-resistance

- Occupy minimum area at the Bond pad

- Have minimum capacitance

- Introduce Minimum series resistance

- Be immune to Process Drifts

- Be robust for numerous pulses

- Offer protection for various ESD stress models

- Not interface with the IC's functional testing

- Not cause increased Vcc or I/O leakage

- Survive the burn-in tests.

# Main requirements for ESD protection

### **Triggering voltage: Vcc < Vtrig < Vbkd (ox)**

- higher than operating voltage i.e. no interference with the device functionality

- lower than failure thresholds

- gate oxide breakdown voltage ( input /power supply )

- snap back voltage of the pull down ( output )

# Lateral NPN as the ESD device

Reverse biased collector junction collects minority carriers

- Collector junction avalanches holes are injected in the substrate. Avalanche is the process in which highly energized particles cause the formation of holes electron pairs.

- Excess holes forward bias the emitter junction because of the potential increase in the substrate. Current begins to flow in the base region.

- Electrons flow from forward biased junction to depletion region. Holes flow in the opposite direction.

• Positive feedback quickly focuses current into the base region; device is now operating as a bipolar.

#### Advantages of NPN as ESD device

- Triggering and sustaining voltage higher than power supply and lower than oxide breakdown

- high impedence when the device is ON in operating conditions

- low impedence when the device is OFF and ESD is applied

- Low dynamic resistance (~10 Ohms range )

- Structure consistent with the CMOS process.

### Drawback of NPN as ESD device

- Bipolar action is induced by the collector avalanche. The mechanism is a potential cause of failure

- Large size is required to reduce ESD current density below the 2<sup>nd</sup> breakdown threshold

- Uniform current distribution is necessary but not easily obtained

- Not suitable for very fast ESD models (CDM)\*.

- \*CDM Charge Device Model

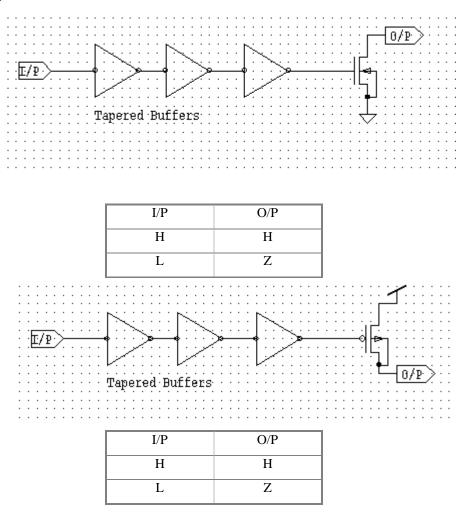

# 3.1.5 Output Pad buffers

CMOS output pad Buffers are used to drive large capacitive loads which arise from long global interconnect lines such as clock distribution networks, high capacitance fan out and high off chip loads. The drive capability of such a buffer should be such as to achieve the requisite rise and fall times into a given capacitive load. Normally the drive capability of I/O buffers as high as 24mA [1] and as low as 0.8mA is available. Conventionally a XmA buffer would mean to source or sink XmA while fulfilling the worst case CMOS/TTL dc levels at the output of the sourcing/sinking transistor. The following section would help explain the meaning of an XmA buffer and gives the analytical design equations for designing such an output transistor drivers.

### **Design of a XmA Buffer:**

Consider a push pull stage at the output of the buffer where both p and n transistors are driven by different set of controlled signals through a chain of inverters. The p transistor would apparently source the current while n would sink the current. All the simulations are performed at the worst conditions. This considers the inductive voltage drop in the power pads (due to the packaging lead inductance). Typically a drop of 0.4 V is used for the equations and eldo simulations here.

Figure 3.5(a) - PMOS sourcing current in X mA Buffer

$I_{DS} = \beta[(V_{GS}-VTP)VDS-V_{DS}^{2}/2] 2]....1(a)$

where  $\beta$  is given as

$\beta = \mu p \epsilon / tox. (W/L)p$  .....1(b)

$(W/L)_p = [X . 10 - 3]. [(-4.1 + |Vtp|)0.4 - 0.08]^{-1} [tox/\infty p.\Sigma].....2$

tox is the oxide thickness  $\infty_p$  the hole mobility and  $\Sigma$  the relative permittivity of the Silicon dioxide.

The aspect  $ratio(W/L)_p$  of the pMOS driver is designed such that IDS=XmA.Thus for a CMOS output buffer (W/L) of the p driver for a XmA Buffer is given as in equation in 2.

With appropriate value of  $\propto_p$  the hole mobility which is a highly sensitive parameter, aspect ratio values of the driver close to that obtained by ELDO simulations are obtained. The normal procedure for finding the driver sizes still is by performing ELDO / SPICE simulation on an isolated transistor under requisite dc levels and worst case supply voltages.

Figure 3.5(b) - NMOS sinking XmA of current

#### XmA=µn\*e/t<sub>ox</sub> (W/L)n [(5-Vtn)\*4-0.08]

Where  $\mu n$ =electron mobility

Similarly the n transistor figure 3.5(b) will sink current while meeting CMOS / TTL output dc conditions. A rise fall time of 12 ns is achieved for the all buffers while driving a maximum load of 25 pf (determined conventionally) under nominal conditions.

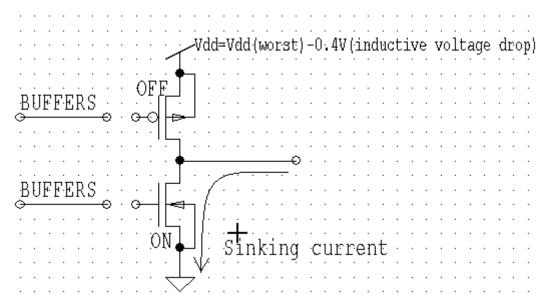

#### **Tapering of Buffers**

Frequently the output stage transistors are preceded by a string of scaled inverters typically three in stage to scale the internal on chip gate signal to a drive level capable of quickly switching the large external capacitance. This prevents the degradation of signal paths by placing too large a capacitive load on previous stages.

The optimization to be achieved in such scaling is to minimize the delay between the input and output while maintaining the area and the power dissipation. A basic derivation of tapering factor in [2] has shown the factor to vary between 3 to 10.A series of advanced works has appeared recently in journals. The work in [3] gives an accurate expression of this factor taking into account the short circuit current power consumption. Design of tapered buffers for gate arrays and standard cell circuits is presented in [4].

While a variable stage ratio approach as a means of reducing the area of cascoded inverters in Buffers is presented in [5].

Undoubtedly the tapering of buffers for optimization to meet constraints such as area, power and speed has come to occupy a degree of importance in Buffer design. An extensive deal on this topic is certainly out of scope of the present work

#### **Different output stages**

Often a plain inverter stage at the output of buffers is avoided. The miller capacitance formed between the gates and the source-drain diffusion [2] of p and n transistors can result in oscillations at the output in series with the lead inductance. Also the self-bootstrapping causes additional delays. The short circuit power dissipation is highly possible in such a configuration. These limitations have given rise to several types of output stages. Below is explained some of the widely used configurations with their relative merits.

#### **PUSH-PULL STAGE:**

A push pull stage consists of p and n transistors at the output pad for sourcing and sinking respectively, where each of the gates of transistors is controlled through a different chain of tapered inverters fed after buffering (as shown in figure 3.6). Such a stage has the advantage of doing away with the miller capacitance and hence bootstrapping (by avoiding direct gate contacts of the two output driver transistors.). Also static and short circuit power dissipation can be avoided by bifurcating the inverter chain in a way such that while sourcing current at the output pad, NMOS driver is made OFF before PMOS is on and vice versa. This prevents a short path at any moment of operation.

Figure 3.6- Push pull output stage

#### **OPEN DRAIN OUTPUT STAGE:**

An open drain stage is superior to push pull stage in that it has just one driver transistor. Such a configuration obviously avoids even the source -drain diffusion capacitance apart from doing away with miller capacitance. Thus open drain is faster than a push pull stage pad. The limitation of such a driver is that it can either source or sink current at a time. The two possible configurations are shown below in figure 3.7. The output state of the pad can also be driven to tristate and can be connected to buses where high impedance state is required for data transfer.

Figure 3.7 - Open Drain output stage

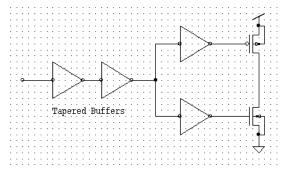

#### TRISTATE PADS:

A high impedance state, which is the state when no current flows at the output, is required when data is to be transferred from the bus [14]. This state is achieved when both the p and n output transistors go into cutoff region of operation. A simple logic for enabling such a state with a particular dc level at an input pin is shown in the figure 3.8(a) and figure 3.8(b). Thus when input pin EN is high, both p and n transistors at the output is OFF and tristate is achieved. Open Drain output stages can also be tristated by appropriate signal at the input.

Figure 3.8(a) - Tri stated pads Using NAND gate

EN - Active Low

EN – H, Z – Tristated

Figure 3.8(b) - Tri stated pads Using NAND and NOR gate

EN - Active Low

EN-H, Z-Tristated

#### **PULL UP/DOWN STAGES:**

Often the tristated output is put to a particular logic level instead of letting the bus float [22]. Either logic low or high can be made at the output using the pull up or pull down transistors. Normally the NMOS is used for pulling down and PMOS is used for pull up, configured as shown in Fig 3.9. The design specifications [6] for the pull up /down stages specify the equivalent resistance and the pull up/down current allowed. The design of such transistors is such as to allow the least static power consumption though quickly pulling up/down the tristated bus to the required logic. The pull up/down stages can also

Figure 3.9- Output/Input pull-up pull-down transistors

Be used at the input of input buffers to keep them from floating.

### 3.2 Slew Rate Control

A fast transition of the signal at the output pad tends to introduce frequencies in UHF range into the off chip load being fed. Sometimes this becomes undesirable in applications such as if the signal is fed to a Television chip, cellular phones, radios etc. The signals in the UHF range then appear as noise. Thus many a time's controlled switching of current signal at the output pad is required, achieved by slew rate control circuits. A controlled switching also results in reduced dI/dt power supply noise. The source of this noise is the inductive voltage drop V = L (dI/dt) at the power rails where inductance is introduced by the package pins.

Other methods to reduce this noise would be to use the lowest inductance package pins (usually the center pins) for power and ground or reducing the off chip load being driven. Slew rate control circuits thus artificially limit the rate of current switching thereby limiting the UHF interference. A very basic work on what exactly slew control would mean has been presented by Parthasarthy in [7].

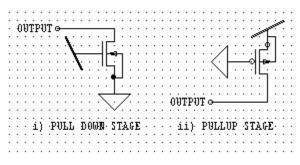

The basic approach for achieving slew rate is to break the output driving transistors in different parallel transistors and switch the stages sequentially one after the other with some delay. Below is explained the working of a Slew rate controlled circuit used with Pad limited I/O design. The slew rate action is basically achieved through the circuit shown in figure 3.10(a).

A predriver consisting of inverters is designed in such a way so that the signal at NIN rises faster than PIN while signal at PIN falls faster than NIN (simple jugglery with W/L of predriver inverter can achieve this.). The signals are shown in figure 3.10(b). For illustration sake let the signal at NIN and PIN fall. (Which is when the input signal goes low). Since PIN goes low first, the output of all the NAND gates PD1 -PD4 go high at the same time This results in all the output p transistor, shown in figure 3.10(d) go OFF at the same time. While NIN goes low from high state later than the PIN, the output of the first NOR gate ND1 switches to high later. Further ND2, ND3 and ND4 would switch high sequentially as the signal is propagated through the NOR-NOT set of gates. The switching of ND1-ND4 is as shown in figure 3.10(c).Thereby a controlled switching at the output is apparently concluded by applying the signals ND1-ND4 to the output driver n -transistors stages [15]. A reverse case of output going high, while sourcing current is explained as above with faster transition at NIN than PIN.

Figure 3.10(a) - Slew rate control circuit

The rate of switching is controlled by the amount of delay offered to the propagation of signals by the set of NAND-NOT and NOR-NOT set of gates. Greater is the delay offered to a particular transition of switching, more controlled is the current switching and hence more is the slew rate control. A set of modifications can be made to the basic

circuit of slew rate control to have a balance of slew rate control, area and power constraints.

Figure 3.10(b) - Signals from Pre-Driver stages

Figure 3.10(c) - Switched signal at the NMOS driver I/P

Figure 3.10(d) - Multi stage O/P driver

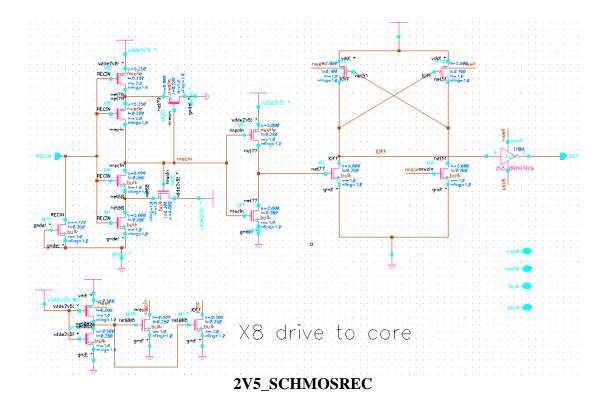

### 3.2.1 Active Slew Rate Control

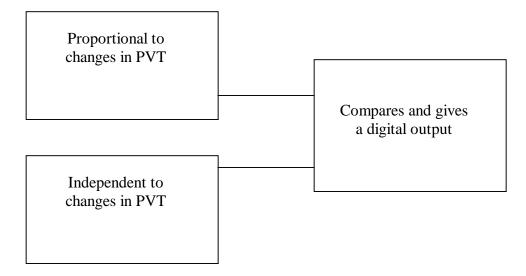

Although, Active slew rate control and design of compensation Block is beyond the scope of the current work, but to understand I/O's as a whole, it is necessary to have a brief overview of the compensation block. The necessity of the slew rate control has been explained in the earlier part of the work.

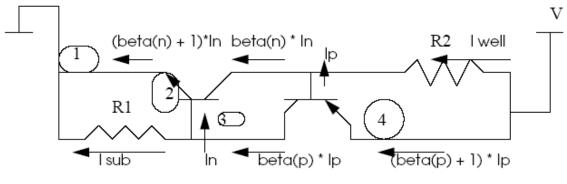

#### What is active slew rate control?