## "MULTILEVEL INVERTER"

## A Major Project Report

Submitted in Partial Fulfillment of the Requirements for Degree of

## MASTER OF TECHNOLOGY IN ELECTRICAL ENGINEERING

## (POWER APPARATUS & SYSTEMS)

By

Rachit Shah (04MEE014)

Department of Electrical Engineering INSTITUTE OF TECHNOLOGY NIRMA UNIVERSITY OF SCIENCE & TECHNOLOGY, AHMEDABAD 382 481

May 2006

### **Certificate**

This certify that the is to Major Project Report entitled "MULTILEVEL INVERTER" submitted by Mr. Rachit Shah (04MEE014), towards the partial fulfillment of the requirements for Degree of Master of Technology (Electrical Engineering) in the field of Power Apparatus & Systems of Nirma University of Science and Technology is the record of work carried out by him under our supervision and guidance. The work submitted has in our opinion reached a level required for being accepted for examination. The results embodied in this major project work to the best of our knowledge have not been submitted to any other University or Institution for award of any degree or diploma.

Date:

#### Industrial Guide: Mr.VINOD PATEL (Dy.Manager-R&D) AMTECH ELECTRONICS (I) LTD GANDHINAGAR

#### **Institute Guide:**

Mr. D.B. DAVE Professor Electrical Engg Dept INSTITUTE OF TECHNOLOGY NIRMA UNIVERSITY Mr. Tejas Panchal Lecturer Electrical Engg Dept INSTITUTEOFTECHNOLOGY NIRMA UNIVERSITY

HOD

Director

Electrical Engineering dept Institute of Technology NIRMA UNIVERSITY Institute of Technology NIRMA UNIVERSITY

### ACKNOWLEDGEMENT

First of all, I would like to thank **AMTECH Electronics** (I) Ltd., Gandhinagar, for giving me an opportunity to perform the project under its premises and give me the industrial exposure.

I wish to express my sincere gratitude to **Mr. Vinod Patel**, Dy. Manager, R&D, AMTECH Electronics (I) Ltd., Gandhinagar, for his guidance and support. His perfectionism has made me improve many details of my work. He challenged me to find technical solutions to realistic problems; many of them are included in this dissertation. He always helped me and encouraged me throughout the period we have worked together.

I would like to thank Mr. Bharat Pandya, Chief Engineer - Design for his support and advice. His extensive knowledge and helpful attitude gains my sincere admiration. I wish to thank all the employees of the AMTECH Electronics (I) Ltd., for making it easier for me to spend the span of six months.

I am thankful to **Prof.U.A.Patel**, Section Head & **Prof.B.B.Kadam**, M.Tech cocoordinator, Electrical Engineering Dept, Nirma University for allowing me to do my project work at AMTECH Electronics (I) Ltd., Gandhinagar.

I wish to express my deep gratitude to **Prof. D.B. Dave,** for his guidance and advice. I am grateful to him for giving me a correct guidance throughout my project and curriculum.

I am grateful to **Mr. Tejas Panchal**, who was always eager to help me through my project and who always felt me as his friend.

I would like to express my appreciation to **Prof. K, Gopakumar,** CEDT Bangalore, for giving me his valuable knowledge. He always encouraged me and provide me his precious guidance.

I would like to honestly thank **Prof. P.N. Tekwani**, who is pursuing his doctorate in Multilevel Inverter in IISC Bangalore, for helping me through my project work and guide me throughout me work.

Thanks to my parents and family members for their continuous support and encouragement to strive for my goals.

Finally, I would like to thank all my friends who were always beside me. THANKS TO ALL OF THEM.

Rachit Shah.

### **Abstract**

For high power applications, voltages and currents must be pushed up. Hence, maximum ratings of power semiconductors become a real handicap. Multilevel Inverter can overcome this limitation.

The report covers and gives an idea of different topologies available in Multilevel Inverters. Main two modulation topologies - Sinusoidal PWM and Space Vector PWM, used in Multilevel Inverter are also explained in this report.

To get the deep-through to Three-Level Diode-Clamped Inverter topology, firstly the Sinusoidal PWM topology is explained. The SPWM topology clearly explains the switching used in Three-Level Diode-clamped Inverter and its basics.

This report also provides one with a new and simple algorithm for Space-Vector PWM. This algorithm takes the advantage of symmetry in the space-vector diagram in order to reduce the switching losses of the IGBT's. The biggest problem of diodeclamped inverter of neutral point voltage unbalanced is overcome by the use of the effective space-vector algorithm. Simulation results are provided to validate the effectiveness of the algorithm, for different reference speeds.

The H-Bridge Inverter topology is also studied in deep and the simulation results for Nine-Level Inverter are also provided. The simulation result comparison shows that the H-Bridge Inverter is quit simple and advantageous in comparison with Diode-Clamped Inverter topology, because of simple switching techniques and improved quality of the output voltage and current and improved source current. The THD of the source current is 5-6% and output phase voltage THD is 8-9%. Other advantage of H-Bridge Inverter is easy commercialization and easy to increase the number of CELLS and hence voltage levels.

The simulation results are supported with the experimental results. For preparing the prototype, different PCB's are prepared. The gate pulses are generated by the use of DSP 'TMS320F2811', which are then further given to the IGBT driver board via multilevel interface board.

A single-phase 3-level prototype model for CELL is also prepared. The experimental results are also shown.

v

## List of Figures

| Half-bridge configuration                                                          | 02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Full-bridge configuration                                                          | 02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Output waveform of Half-Bridge configuration                                       | 02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Output waveform of Full-Bridge configuration                                       | 02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Three-level diode-clamped inverter topology                                        | 05                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Four-level diode-clamped inverter topology                                         | 05                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Three-level flying capacitor topology                                              | 08                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Four-level flying capacitor topology                                               | 08                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Two-cell Cascaded H-bridge topology                                                | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Parallel phase inverter topology                                                   | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SPWM for Six-level inverter topology                                               | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SPWM for Even number of output voltage levels                                      | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SPWM for Odd number of output voltage levels                                       | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Variable Frequency Carrier Band (SPWM)                                             | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

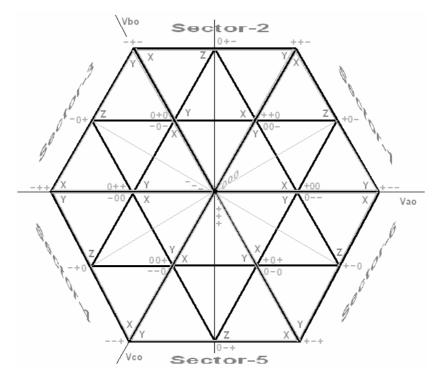

| Space - Vector Diagram for Three-Level Inverter                                    | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

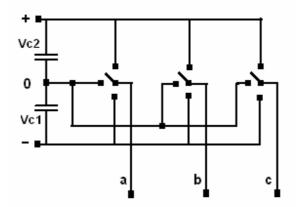

| Simplified Model of Three-Level Diode Clamped Inverter                             | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

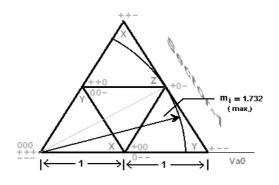

| Max. length of the normalized reference vector in steady-state conditions.         | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

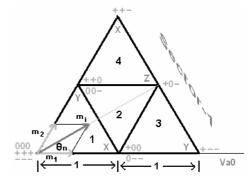

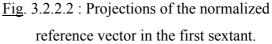

| Projections of the normalized reference vector in the first sextant                | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

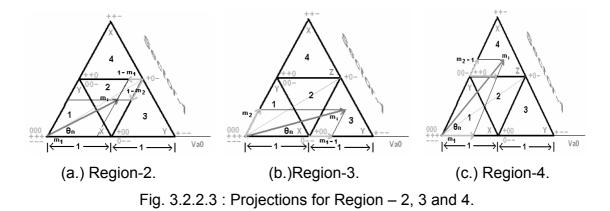

| Projections for (a.) Region - 2, (b.) Region - 3 and (c.) Region - 4               | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

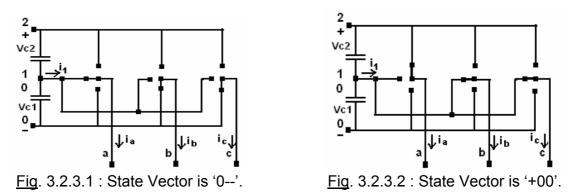

| State Vector is '0'                                                                | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| State Vector is '+00'                                                              | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

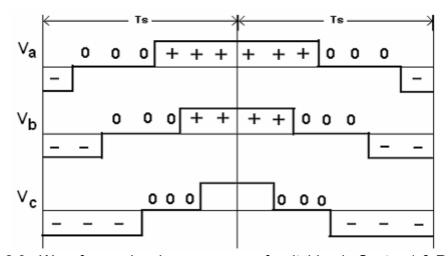

| Waveforms showing sequence of switching in Sector-1 and Region-1                   | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Three-level diode-clamped inverter with Sinusoidal PWM with two dc                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| sources                                                                            | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Output waveforms for (a.) $m_a = 1$ , (b.) $m_a = 0.8$ , (c.) $m_a = 0.4$ (R-Load, |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| with phase-disposition)                                                            | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Output waveforms for (a.) $m_a = 1$ , (b.) $m_a = 0.4$ (R & L-Load, with           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| phase-disposition)                                                                 | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Output waveforms for $m_a = 1$ (R-Load, without phase-disposition)                 | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Output waveforms for (a.) $m_a = 1$ , (b.) $m_a = 0.4$ (R & L-Load, without        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| phase-disposition)                                                                 | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Three-level diode-clamped inverter with Sinusoidal PWM with single                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| dc source                                                                          | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Output waveforms for (a.) $m_a = 1$ , (b.) $m_a = 0.4$ (R & L-Load, with           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| phase-disposition)                                                                 | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                    | sources.<br>Output waveforms for (a.) $m_a = 1$ , (b.) $m_a = 0.8$ , (c.) $m_a = 0.4$ (R-Load,<br>with phase-disposition).<br>Output waveforms for (a.) $m_a = 1$ , (b.) $m_a = 0.4$ (R & L-Load, with<br>phase-disposition).<br>Output waveforms for $m_a = 1$ (R-Load, without phase-disposition).<br>Output waveforms for (a.) $m_a = 1$ , (b.) $m_a = 0.4$ (R & L-Load, without<br>phase-disposition).<br>Three-level diode-clamped inverter with Sinusoidal PWM with single<br>dc source. |

| Fig. 4.2.2.     | Output waveforms for (a.) $m_a = 1$ , (b.) $m_a = 0.4$ (R & L-Load, without |      |

|-----------------|-----------------------------------------------------------------------------|------|

|                 | phase-disposition)                                                          | 29   |

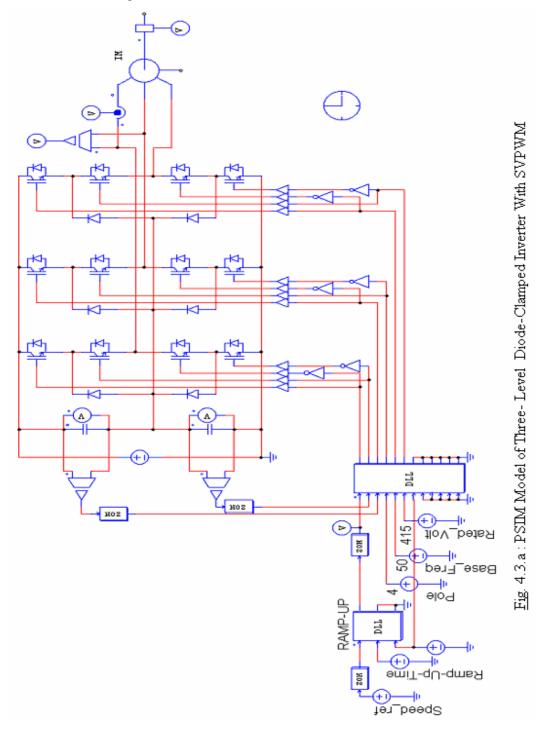

| Fig.4.3.a.      | PSIM model of three-level diode clamped inverter with SVPWM                 | 31   |

| Fig. 4.3.b.     | Flowchart of the proposed model                                             | . 32 |

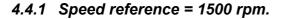

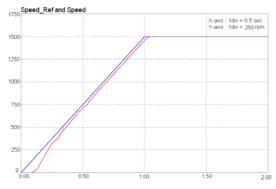

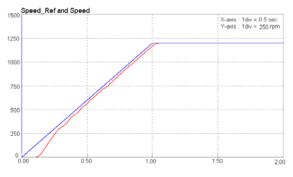

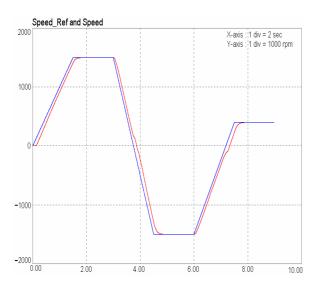

| Fig. 4.4.1.1.   | (a.) Speed Reference (1500 rpm) and Motor Speed, (b.) Expanded View         | . 33 |

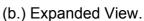

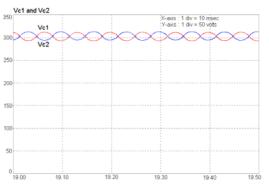

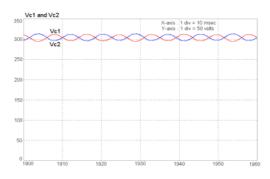

| Fig. 4.4.1.2.   | Capacitor Voltages (Ref_Speed = 1500 rpm)                                   | 33   |

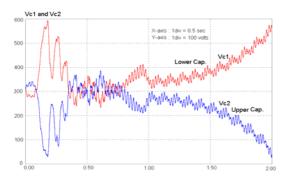

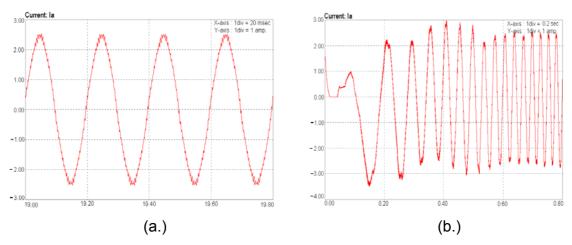

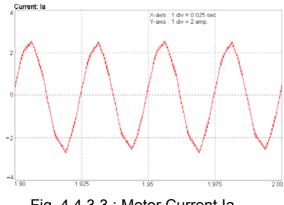

| Fig. 4.4.1.3.   | Motor Current (Ref_Speed = 1500 rpm)                                        | 33   |

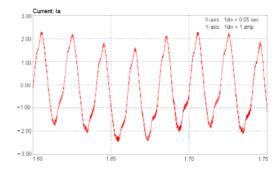

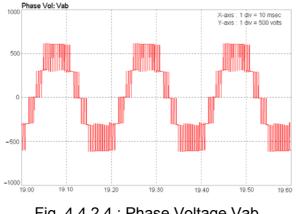

| Fig. 4.4.1.4.   | Phase Voltage Vab (Ref_Speed = 1500 rpm)                                    | 33   |

| Fig. 4.4.2.1.   | Speed ref. & Motor speed (Ref_Speed = 1500 rpm)                             | 34   |

| Fig. 4.4.2.2.   | Capacitor Voltages (Ref_Speed = 1500 rpm)                                   | 34   |

| Fig. 4.4.2.3.   | Motor Current Ia (a.) Ref. speed and (b.) Starting (Ref_Speed = 1500 rpm).  | 34   |

| Fig. 4.4.2.4.   | Phase Voltage Vab (Ref_Speed = 1500 rpm)                                    | 34   |

| Fig. 4.4.3.1.   | Speed ref. & Motor speed (Ref_Speed = 1200 rpm)                             | 35   |

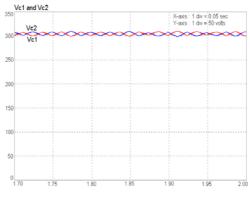

| Fig. 4.4.3.2.   | Capacitor Voltages (Ref_Speed = 1200 rpm)                                   | 35   |

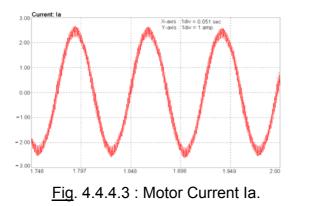

| Fig. 4.4.3.3.   | Motor Current Ia (Ref_Speed = 1200 rpm)                                     | 35   |

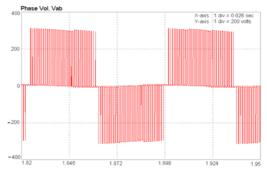

| Fig. 4.4.3.4.   | Phase Voltage Vab (Ref_Speed = 1200 rpm)                                    | 35   |

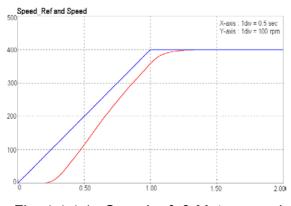

| Fig. 4.4.4.1.   | Speed ref. & Motor speed (Ref_Speed = 400 rpm)                              | 35   |

| Fig. 4.4.4.2.   | Capacitor Voltages (Ref_Speed = 400 rpm)                                    | 35   |

| Fig. 4.4.4.3.   | Motor Current Ia (Ref_Speed = 400 rpm)                                      | 36   |

| Fig. 4.4.4.4.   | Phase Voltage Vab (Ref_Speed = 400 rpm)                                     | 36   |

| Fig. 4.4.5.1.   | Speed ref. & Motor speed (Ref_Speed = 1500~-1500~400 rpm)                   | 36   |

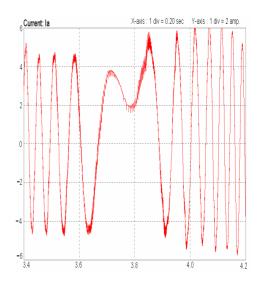

| Fig. 4.4.5.2.   | Motor Current (Ia) (Ref_Speed = 1500~-1500~400 rpm)                         | 36   |

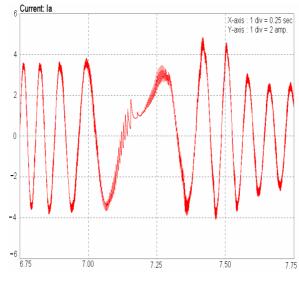

| Fig. 4.4.5.3.   | Motor Current (Ia) (Ref_Speed = 1500~-1500~400 rpm)                         | 36   |

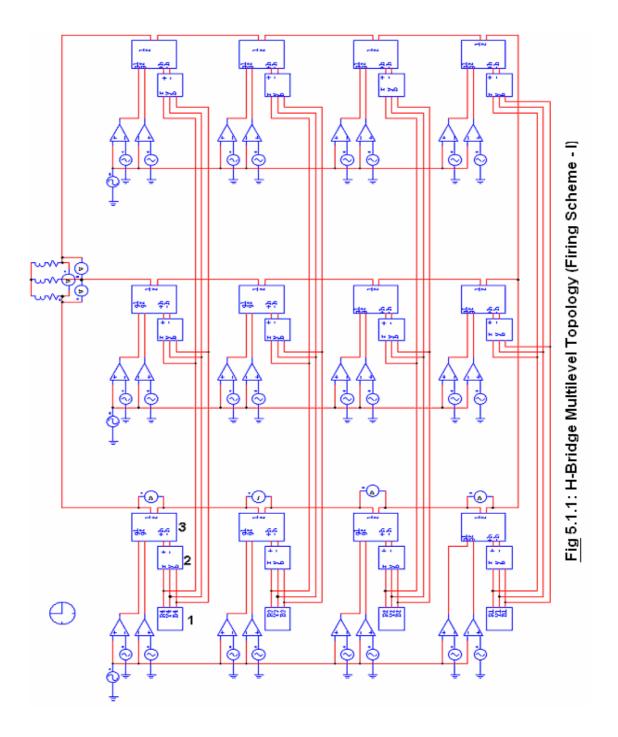

| Fig. 5.1.1.     | H-Bridge Multilevel Topology (Firing Scheme-I)                              | 38   |

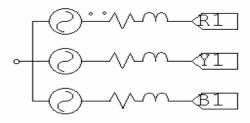

| Fig. 5.1.2.     | Three-Phase Source (Block-1)                                                | 39   |

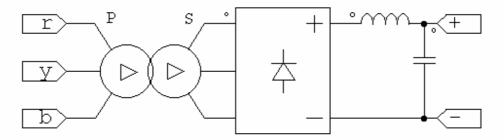

| Fig. 5.1.3.     | Transformer & Rectifier With DC-Choke and DC-Link Cap. (Block-2)            | 39   |

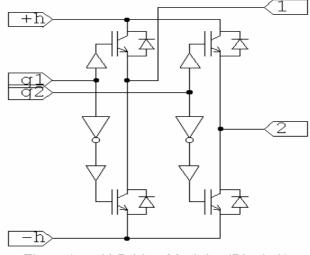

| Fig. 5.1.4.     | H-Bridge Module (Block-)                                                    | 39   |

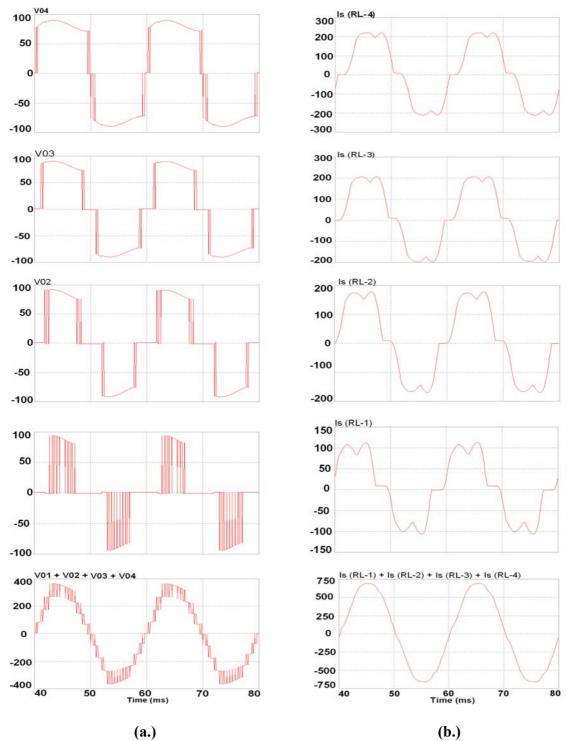

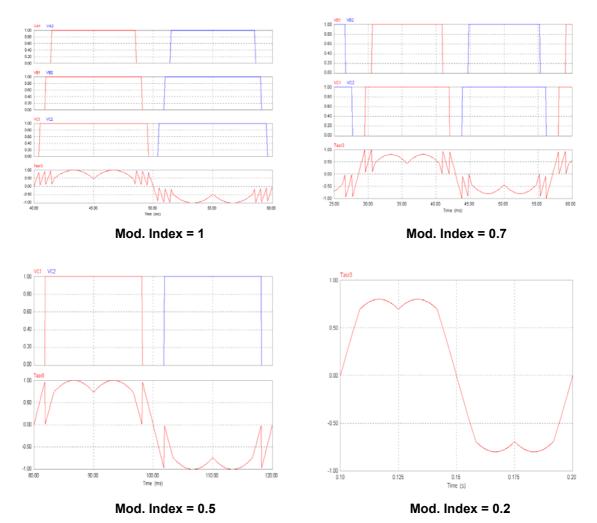

| Fig. 5.1.1.(a.) | Top to bottom, Voltages across Cells from top to bottom & bottom-most       |      |

|                 | Phase-Voltage                                                               | 40   |

| (b.)            | Current in Transformers of R-Phase & total source current                   | 40   |

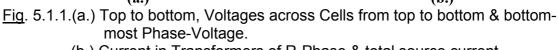

| Fig. 5.1.1.1.   | Sine-Triangular Comparison                                                  | 41   |

| Fig. 5.1.1.2 .  | Line Voltage (416 Volts RMS.)                                               | 41   |

| Fig. 5.1.1.3.   | Line Voltage FFT                                                            | 41   |

| Fig. 5.1.1.4.   | Load Current (98 Amps RMS.)                                                 | 41   |

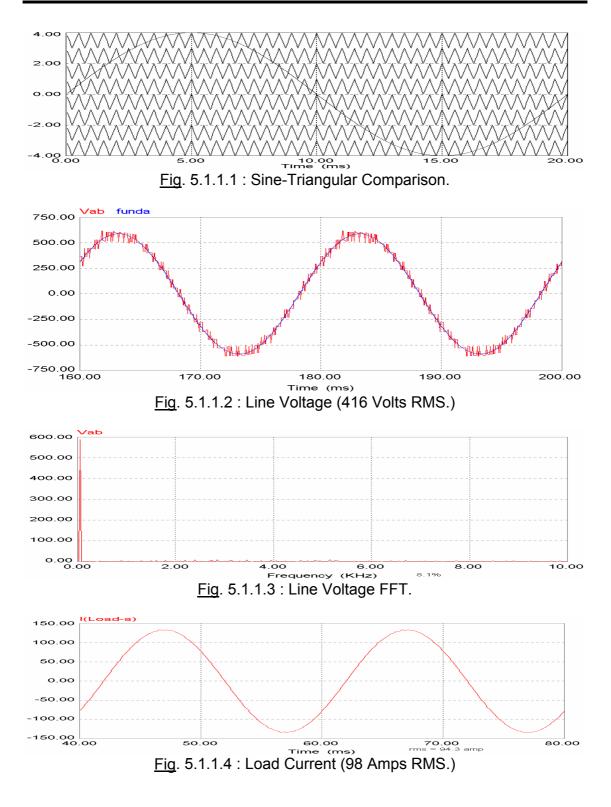

| Fig. 5.2.1.     | 9-Level H-Bridge Inverter Topology (Firing Scheme-II)                       | . 42 |

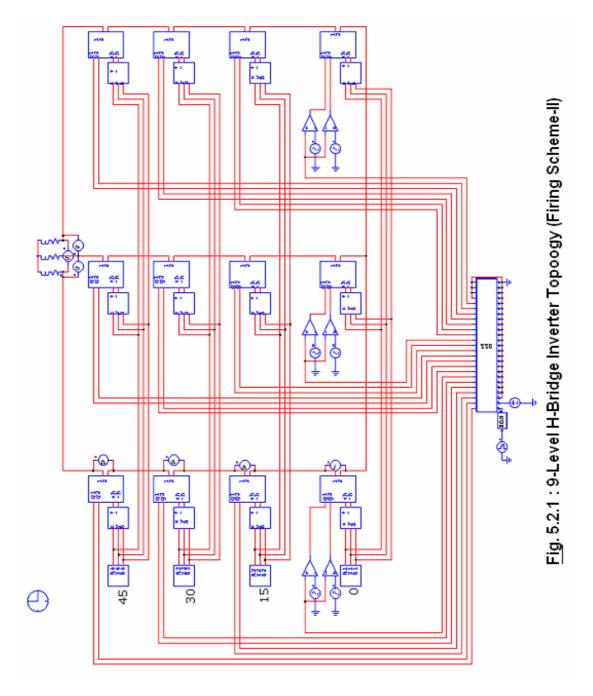

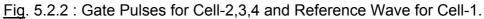

| Fig. 5.2.2.     | Gate Pulses for Cell-2,3,4 and Reference Wave for Cell-1                    | 43   |

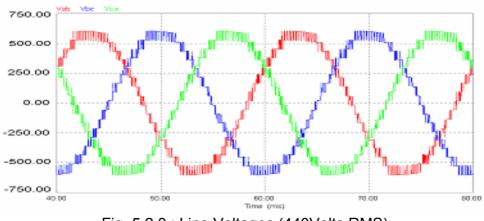

| Fig. 5.2.3.     | Phase Voltages (440Volts RMS)                                               | 43   |

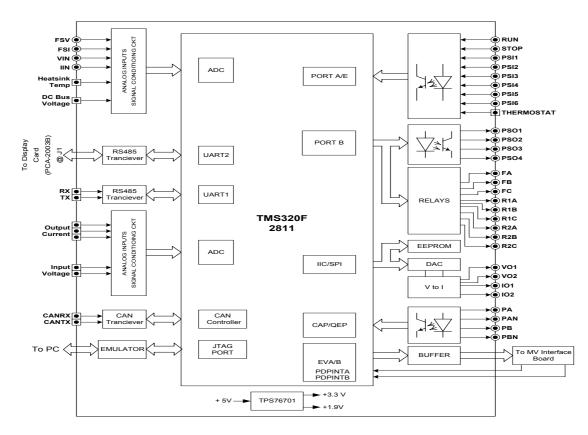

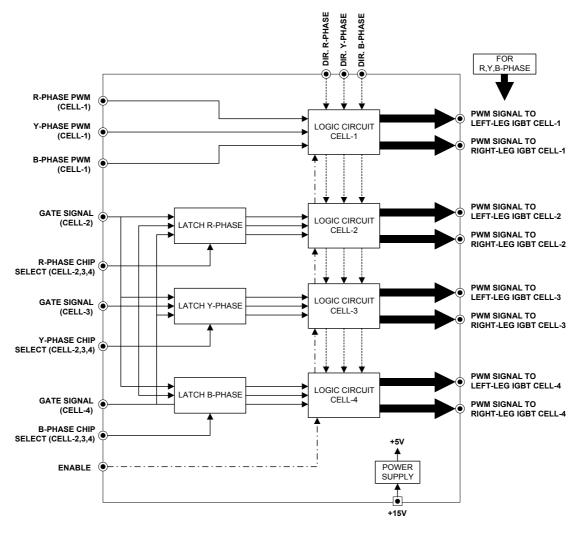

| Fig. 6.1.2.  | Block Diagram Representation of Control Signal Board             | 45   |

|--------------|------------------------------------------------------------------|------|

| Fig. 6.1.3.  | Block Diagram Representation of Multi-Level Interface Board      | 46   |

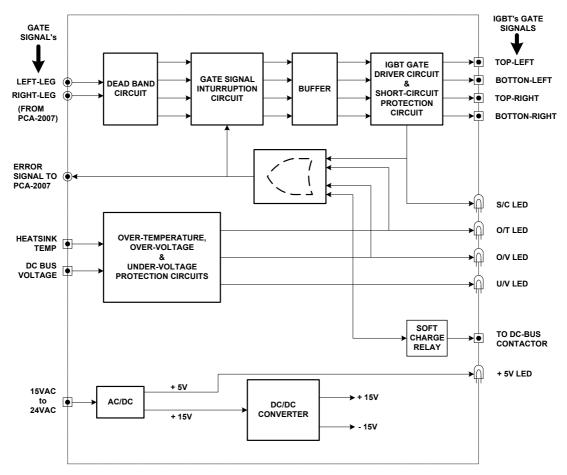

| Fig. 6.1.4.  | Block Diagram Representation of MV Driver Board                  | 48   |

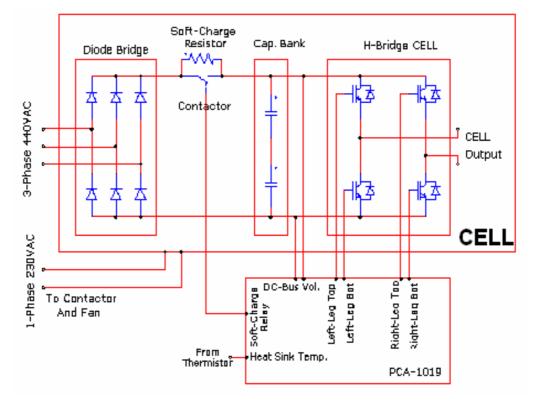

| Fig. 6.2.    | Representable View of Single CELL Structure                      | 53   |

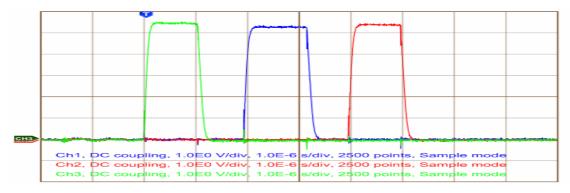

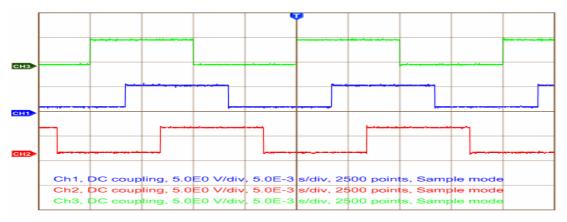

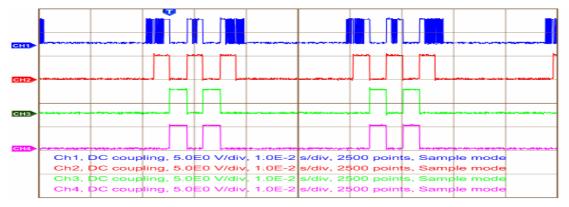

| Fig. 7.1.1.  | Chip-Select Signal For R-Phase, Y-Phase and B-Phase              | 54   |

| Fig. 7.1.2.  | Direction Signals For R-Phase, Y-Phase and B-Phase               | 54   |

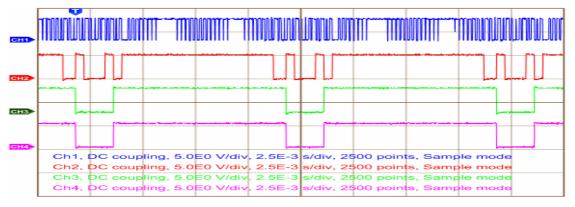

| Fig. 7.2.1.  | Signals Generated At Output of Latch & PWM (R-Phase)             | . 55 |

| Fig. 7.2.2.  | Signals Generated At Output of Logic Circuit @ 50 Hz (R-Phase)   | 55   |

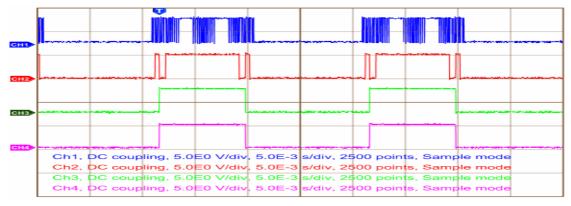

| Fig. 7.2.3.  | Signals Generated At Output of Logic Circuit @ 40 Hz (R-Phase)   | 55   |

| Fig. 7.2.4.  | Signals Generated At Output of Logic Circuit @ 26 Hz (R-Phase)   | 56   |

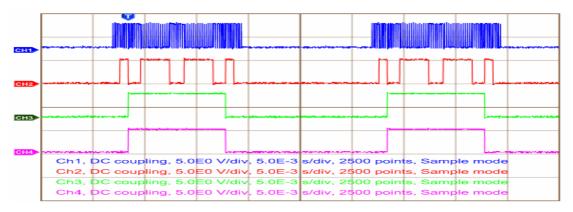

| Fig. 7.2.5.  | Signals Generated At Output of Logic Circuit @ 25 Hz (R-Phase)   | 56   |

| Fig. 7.2.6.  | Signals Generated At Output of Logic Circuit @ 12.6 Hz (R-Phase) | . 56 |

| Fig. 7.2.7.  | Signals Generated At Output of Logic Circuit @ 12.5 Hz (R-Phase) | . 57 |

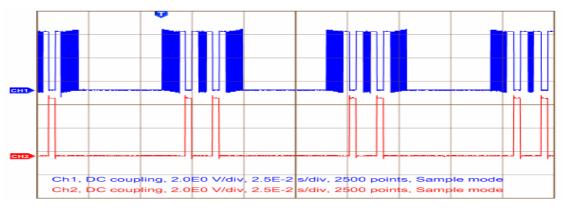

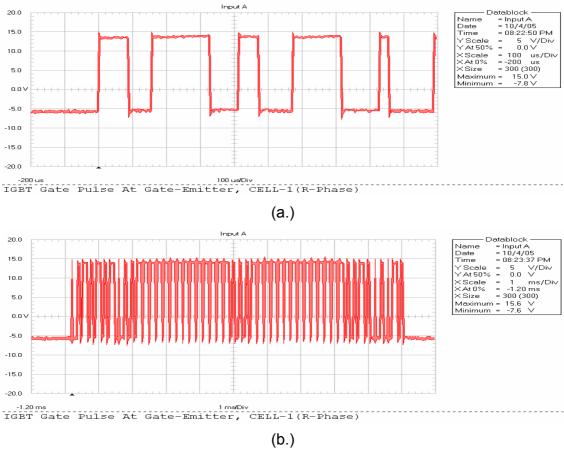

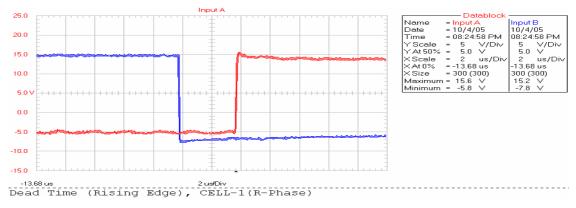

| Fig. 7.3.1.  | IGBT Gate Pulse At Gate-Emitter, CELL-1 (R-Phase)                | . 57 |

| Fig. 7.3.2.  | Dead-Time (Rising Edge), CELL-1 (R-Phase)                        | . 58 |

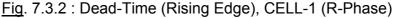

| Fig. 7.3.3.  | Dead-Time (Falling Edge), CELL-1 (R-Phase)                       | . 58 |

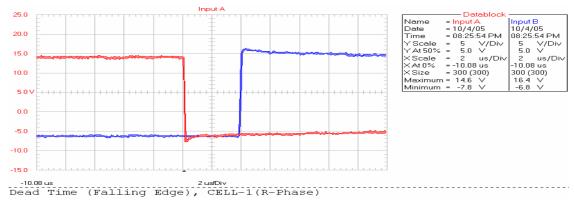

| Fig. 7.3.4.  | IGBT Gate Pulse At Gate-Emitter, CELL-2 (R-Phase)                | . 58 |

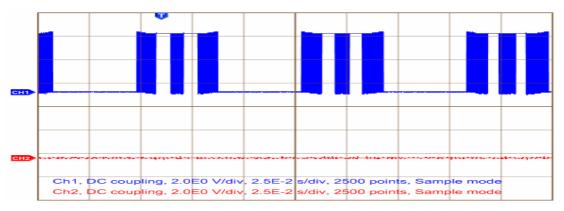

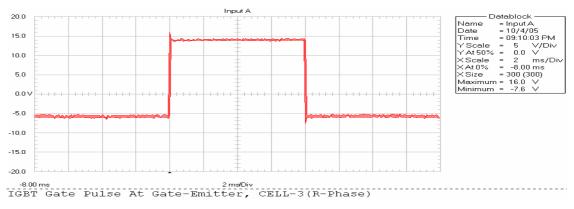

| Fig. 7.3.5.  | IGBT Gate Pulse At Gate-Emitter, CELL-3 (R-Phase)                | . 59 |

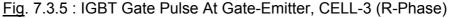

| Fig. 7.3.6.  | IGBT Gate Pulse At Gate-Emitter, CELL-4 (R-Phase)                | . 59 |

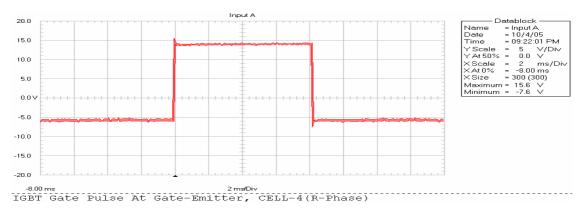

| Fig. 7.3.7.  | Voltage Waveform At Drain of Q2                                  | 59   |

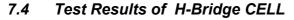

| Fig. 7.4.1.  | Soft-Charge Voltage Across Capacitor-Bank                        | . 60 |

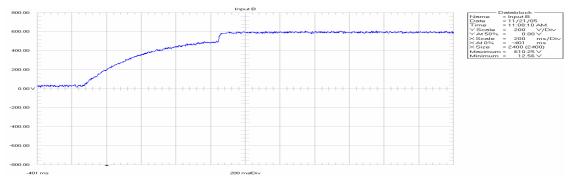

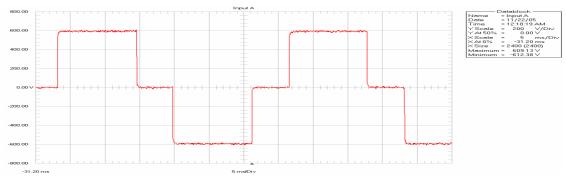

| Fig. 7.4.2.  | CELL-1 Output Voltage @ 50Hz                                     | 60   |

| Fig. 7.4.3.  | CELL-2 Output Voltage @ 50Hz                                     | 60   |

| Fig. 7.4.4.  | CELL-3 & 4 Output Voltage @ 50Hz                                 | 60   |

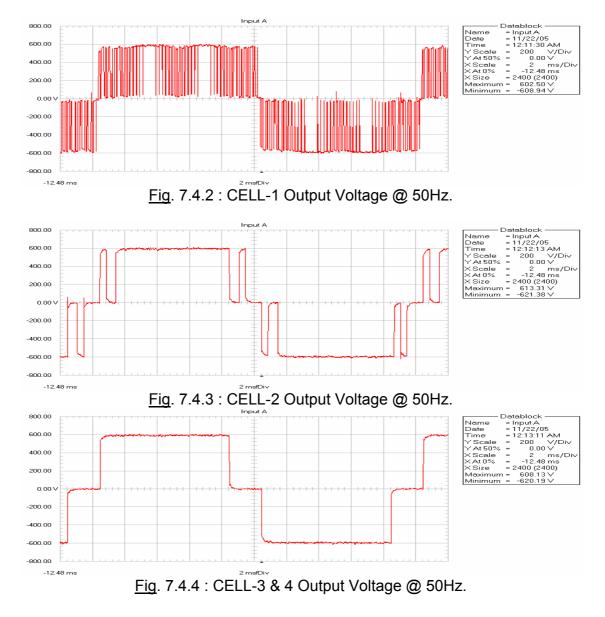

| Fig. 7.4.5.  | CELL-1 Output Voltage @ 35Hz                                     | 60   |

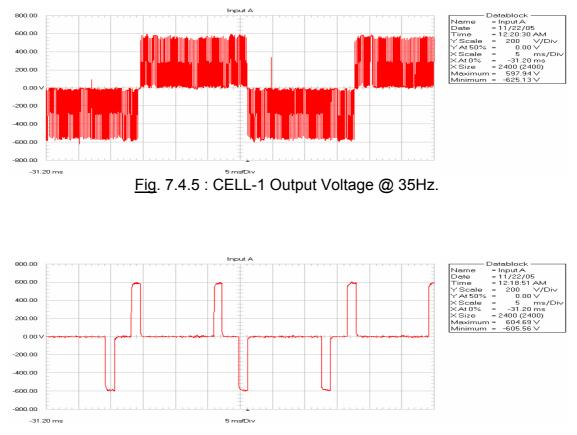

| Fig. 7.4.6.  | CELL-2 Output Voltage @ 35Hz                                     | 60   |

| Fig. 7.4.7.  | CELL-3 & 4 Output Voltage @ 35Hz                                 | 60   |

| Fig. 7.4.5.  | CELL-1 Output Voltage @ 35Hz                                     | 61   |

| Fig. 7.4.6.  | CELL-2 Output Voltage @ 35Hz                                     | 61   |

| Fig. 7.4.7.  | CELL-3 & 4 Output Voltage @ 35Hz                                 | 61   |

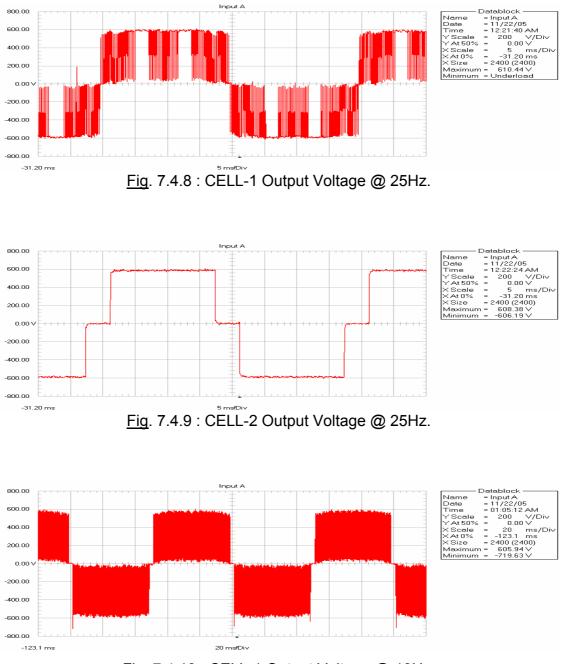

| Fig. 7.4.8.  | CELL-1 Output Voltage @ 25Hz                                     | 62   |

| Fig. 7.4.9.  | CELL-2 Output Voltage @ 25Hz                                     | 62   |

| Fig. 7.4.10. | CELL-1 Output Voltage @ 10Hz                                     | 62   |

## List of Tables

| Table – 2.1.1. | Three-level inverter relationships                | 06   |

|----------------|---------------------------------------------------|------|

| Table – 2.1.2. | Four-level inverter relationships                 | .06  |

| Table – 2.2.1. | Three-level flying capacitor relationships        | 09   |

| Table – 2.2.2. | Four-level flying capacitor relationships         | 09   |

| Table – 2.3.1. | H-bridge cell relationships                       | 11   |

| Table – 2.3.2. | Parallel inverter relationships                   | 12   |

| Table – 2.4.   | Comparison of topologies for multilevel inverters | . 14 |

| Table – 3.2.1. | Summary of information for the SVPWM              | 22   |

| Table – 3.2.2. | Sequence of switching in Sector-1                 | .23  |

| Table – 6.1.   | DSP Pins Usage For Signal Generation              | .45  |

# **CONTENTS**

| Project Title   | (i)   |

|-----------------|-------|

| Certificate     | (ii)  |

| Acknowledgement | (iii) |

| Abstract        | (v)   |

| List of Figures | (vi)  |

| List of Tables  | (ix)  |

| Chapte | er 1 : Introduction                                            | . 1 |

|--------|----------------------------------------------------------------|-----|

| 1.1.   | Harmonics in Electrical Systems                                | . 1 |

| 1.2.   | Conventional Two-Level and Three-Level Voltage Source Inverter | . 2 |

| 1.3.   | Multilevel Voltage Source Inverter                             | . 3 |

| Chapter | 2:     | Multilevel Inverter Topologies      | 4  |

|---------|--------|-------------------------------------|----|

| 2.1.    | Diode  | -Clamped Multilevel Inverter        | 4  |

| 2.2.    | Flying | Capacitor Multilevel Inverter       | 8  |

| 2.3.    | H-Bria | lge Inverters                       | 11 |

|         | 2.3.1. | Cascaded H-Bridge Inverters         | 11 |

|         | 2.3.2. | Parallel H-Bridge Inverter Topology | 11 |

|         | 2.3.3. | Modified H-Bridge Inverter Topology | 12 |

|         |        |                                     |    |

| Chapter | 3:     | Modulation Topologies For Multilevel Inverter             | 15 |

|---------|--------|-----------------------------------------------------------|----|

| 3.1.    | Sinuso | oidal Pulse Width Modulation (SPWM)                       | 15 |

| 3.2.    | Space  | Vector Pulse Width Modulation (SVPWM)                     | 17 |

|         | 3.2.1. | Space Vector PWM For a Three-Level Diode Clamped Inverter | 18 |

|         | 3.2.2. | Simplified Calculation of Duty Cycles                     | 21 |

|         | 3.2.3. | Symmetric Modulation                                      | 23 |

| Chapter | 4:     | Simulation Model Of Three-Level Diode Clamped          |    |

|---------|--------|--------------------------------------------------------|----|

|         |        | Inverter                                               | 24 |

| 4.1.    | Sinusc | idal PWM With Two DC Source                            | 24 |

|         | 4.1.1. | Simulation Results For Triangular Waves With Phase-    |    |

|         |        | Disposition                                            | 25 |

|         | 4.1.2. | Simulation Results For Triangular Waves With No Phase- |    |

|         | Di     | sposition                                              | 27 |

| 4.2.    | Sinus  | oidal PWM With Two Capacitors & Single DC Source       | 28 |

|         | 4.2.1. | Simulation Results For Triangular Waves With Phase-    |    |

|         |        | Disposition                                            | 29 |

|         | 4.2.2. | Simulation Results For Triangular Waves With No Phase- |    |

|         |        | Disposition                                            | 29 |

| 4.3.    | Simula | ation Model With Space-Vector PWM                      | 31 |

| 4.4.    | Simula | ation Results of SVPWM                                 | 33 |

|         | 4.4.1. | Speed reference = 1500 rpm                             | 33 |

|         | 4.4.2. | Speed reference = 1500 rpm                             | 34 |

|         | 4.4.3. | Speed reference = 1200 rpm                             | 35 |

|         | 4.4.4. | Speed reference = 400 rpm                              | 35 |

|         | 4.4.5. | Speed reference = 1500 rpm to -1500rpm to 400 rpm      | 36 |

| Chapter | 5:     | Simulation Model Of Nine-Level H-Bridge Inverter.      | 38 |

| 5.1.    | Firing | Topology-I                                             | 38 |

|         | 5.1.1. | Simulation Results For Firing Topology-I               | 40 |

| 5.2.    | Firing | Topology-II                                            | 42 |

|         | 5.2.1. | Simulation Results For Firing Topology-II              | 43 |

| Chapter | 6:     | Hardware Description                                   | 44 |

| 6.1.    | Contro | ol Circuit & Driver Circuit                            | 44 |

|         | 6.1.1. | Display/Keypad Card                                    | 44 |

|         | 6.1.2. | Control Signal Board                                   | 44 |

|         | 6.1.3. Multi-Level Interface Board | 46   |

|---------|------------------------------------|------|

|         | 6.1.4. MV Driver Board             |      |

| 6.2.    | H-Bridge CELL                      | 52   |

| Chapte  | r 7 : Test Results                 | 54   |

| 7.1.    | Test Results for PCA-2004A         |      |

| 7.2.    | Test Results for PCA-2007          |      |

|         | Test Results for PCA-1019          |      |

| 7.4.    | Test Results of H-Bridge CELL      | 59   |

| Chapte  | r 8 : Conclusion & Future Work     | 63   |

| Referer | 1Ces                               | 64   |

| Append  | dix                                | 66   |

|         |                                    | •••• |

### 1. INTRODUCTION

#### 1.1 Harmonics in Electrical Systems

One of the biggest problems in power quality aspects is the harmonic contents in the electrical system. Generally, harmonics may be divided into two types:

1) Voltage harmonics, and

2) Current harmonics.

Current harmonics is usually generated by harmonics contained in voltage supply and depends on the type of load such as resistive load, capacitive load, and inductive load. Both harmonics can be generated by either the source or the load side. Harmonics generated by load are caused by nonlinear operation of devices, including power converters, arc-furnaces, gas discharge lighting devices, etc. Load harmonics can cause the overheating of the magnetic cores of transformer and motors. On the other hand, source harmonics are mainly generated by power supply with non-sinusoidal voltage waveform. Voltage and current source harmonics imply power losses, Electromagnetic Interference (EMI) and pulsating torque in AC motor drives. Any periodic waveform can be shown to be the superposition of a fundamental and a set of harmonic components. By applying Fourier transformation, these components can be extracted. The frequency of each harmonic component is an integral multiple of its fundamental. The method used to determine harmonic content commonly used is Total Harmonic Distortion (THD), which is defined in terms of the amplitudes of the harmonics, Hn, at frequency  $n\omega o$ , where  $\omega o$  is frequency of the fundamental component whose amplitude of H1 and n is integer. The THD is mathematically given by

$$THD = \frac{\sqrt{\sum_{n=2}^{\infty} H_{(n)}^{2}}}{H_{1}}$$

#### 1.2 Conventional Two-Level and Three-Level Voltage Source Inverter

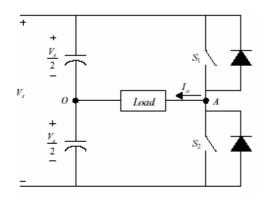

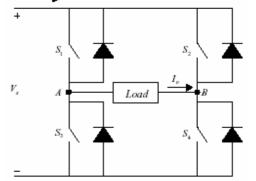

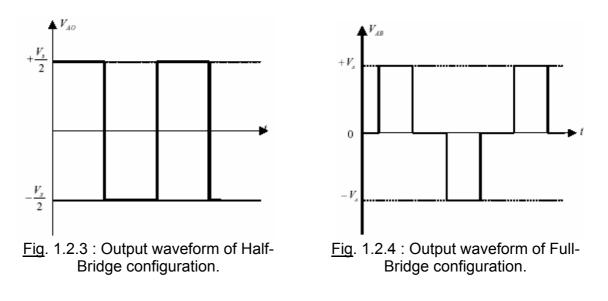

Switch-mode dc-to-ac inverters used in ac power supplies and ac motor drives where the objective is to produce a sinusoidal ac output whose magnitude and frequency can both be controlled. Practically, we use an inverter in both single-phase and three-phase ac systems. A half-bridge is the simplest topology, which is used to produce a two-level square-wave output waveform. The full-bridge topology is used to synthesize a three-level square-wave output waveform. The half-bridge and full-bridge configurations of the single-phase voltage source inverter are shown in Fig.1.2.1 and 1.2.2, respectively.

Fig. 1.2.1 : Half-bridge configuration.

Fig. 1.2.2 : Full-bridge configuration.

Fig. 1.2.3 and 1.2.4 respectively shows the output waveform of a Half-bridge and Fullbridge configuration.

#### 1.3 Multilevel Voltage Source Inverter

For high power applications, voltages and currents must be pushed up. Hence, maximum ratings of power semiconductors become a real handicap. Paralleling devices, subsystems or systems leads to higher current levels. On the other hand, given a chain of devices connected in series, achieving static and dynamic voltage sharing among switches becomes a problem. The best method for stabilizing voltages applied to the devices is by clamping those using DC voltage sources; or large capacitors, which transitorily behave as voltage sources. Multilevel topologies are based on this principle, and therefore, the voltages applied to the devices can be controlled and limited.

Advantages offered by the multilevel approach compared to two-level topology include:

- ► Good power quality, due to greater availability of voltage levels,

- ► Good electromagnetic compatibility (EMC),

- ► Low switching losses, as switching frequencies of the devices can be reduced,

- ► Filters with smaller reactive components,

- ► Ratings of the components used reduces.

These all benefits, together with the ability to deal with high voltage levels, confer on multilevel converters a very important role in the field of high power applications.

In 1980, early interest in multilevel power conversion technology was triggered by the work of Nabae, et al., who introduced the neutral-point-clamped (NPC) inverter topology. It was immediately realized that this new inverter had many advantages over the more conventional two-level inverter. Subsequently, in the early nineties the concept of the three-level inverter was extended further and some new multilevel topologies were proposed.

### 2. MULTILEVEL INVERTER TOPOLOGIES

At the present time, the majority of research and development effort seems to concentrate on the development of four classes of inverters:

- 1. The diode-clamped (neutral-point-clamped) multilevel inverter.

- 2. The flying capacitor inverter.

- 3. The multilevel inverter with cascaded and parallel H-bridge inverters.

- 4. Modified H-bridge inverters.

#### 2.1 Diode-Clamped Multilevel Inverter

The diode-clamped inverter provides multiple voltage levels through connection of the phases to a series bank of capacitors. According to the original invention, the concept can be extended to any number of levels by increasing the number of capacitors. Early descriptions of this topology were limited to three-levels where two capacitors are connected across the dc bus resulting in one additional level. The additional level was the neutral point of the dc bus, so the terminology neutral point clamped (NPC) inverter was introduced. Due to capacitor voltage balancing issues, the diode-clamped inverter implementation has been mostly limited to the three-level. Because of industrial developments over the past several years, the three-level inverter is now used extensively in industry applications. Although most applications are medium-voltage, a three-level inverter for 480V is also in the market.

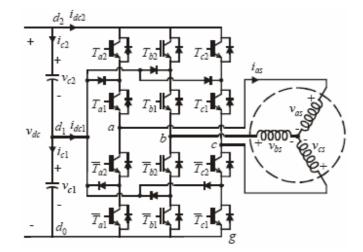

Fig. 2.1.1 shows the topology of the three-level diode-clamped inverter. Although the structure is more complicated than the two-level inverter, the operation is straightforward. Each phase node (a, b or c) can be connected to any node in the capacitor bank  $(d_0, d_1 \text{ or } d_2)$ . Connection of the *a*-phase to junctions  $d_0$  and  $d_2$  can be accomplished by switching transistors  $T_{a1}$  and  $T_{a2}$  both OFF or both ON respectively. These states are the same as the two-level inverter yielding a line-to-ground voltage of zero or the dc voltage. Connection to the junction  $d_1$  is accomplished by gating  $T_{a1}$  OFF and  $T_{a2}$  ON. In this representation, the labels  $T_{a1}$  and  $T_{a2}$  are used to identify the transistors as well as the transistor logic (1=ON and 0=OFF). Since the transistors are always switched in pairs, the complement are labeled  $\overline{T}_{a1}$  and  $\overline{T}_{a2}$  accordingly. In a practical implementation, some dead time is

Fig. 2.1.1 : Three-level diode-clamped inverter topology.

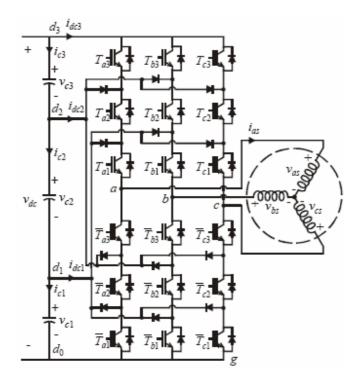

Fig. 2.1.2 : Four-level diode-clamped inverter topology.

inserted between the transistor signals and their complements meaning that both transistors in a complementary pair may be switched off for a small amount of time during a transition. From Fig. 2.1.1, it can be seen that, with this switching state, the *a*-phase current  $i_{as}$  will flow into the junction through diode  $D_{a1}$  if it is negative or out of

the junction through diode  $D_{a2}$  if the current is positive. According to this description, the inverter relationships for the *a*-phase are presented in Table -2.1.1.

| Sa | T <sub>a2</sub> | T <sub>a1</sub> | v <sub>ag</sub>   | i <sub>adc1</sub> | i <sub>adc2</sub> |

|----|-----------------|-----------------|-------------------|-------------------|-------------------|

| 0  | 0               | 0               | 0                 | 0                 | 0                 |

| 1  | 0               | 1               | v <sub>c1</sub>   | i <sub>as</sub>   | 0                 |

| 2  | 1               | 1               | $v_{c1} + v_{c2}$ | 0                 | i <sub>as</sub>   |

Table – 2.1.1. Three-level inverter relationships.

The dc currents  $i_{adc1}$  and  $i_{adc2}$  are the *a*-phase components to the junction currents  $i_{dc1}$  and  $i_{dc2}$  in Fig. 2.1.1 respectively.

Extending the diode-clamped concept to four levels results in the topology shown in Fig. 2.1.2. A pair of diodes is added in each phase for each of the two junctions. The operation is similar to the three-level inverter with the relationships described in Table -2.1.2.

Table – 2.1.2. Four-level inverter relationships.

| Sa | $T_{a3}$ | T <sub>a2</sub> | T <sub>a1</sub> | $v_{ag}$                   | <i>i</i> <sub>adc1</sub> | i <sub>adc2</sub> | i <sub>adc3</sub> |

|----|----------|-----------------|-----------------|----------------------------|--------------------------|-------------------|-------------------|

| 0  | 0        | 0               | 0               | 0                          | 0                        | 0                 | 0                 |

| 1  | 0        | 0               | 1               | v <sub>c1</sub>            | <i>i</i> as              | 0                 | 0                 |

| 2  | 0        | 1               | 1               | $v_{c1} + v_{c2}$          | 0                        | <i>i</i> as       | 0                 |

| 3  | 1        | 1               | 1               | $v_{c1} + v_{c2} + v_{c3}$ | 0                        | 0                 | i <sub>as</sub>   |

The advantages of diode-clamped multilevel inverter are:

- Voltages across the switches are only half of the dc-link voltage.

- The first group of voltage harmonics is centered around twice the switching frequency.

- This topology can be generalized, and the principles used in the basic three-level topology can be extended for use in topologies with any number of levels.

However, practical experience with this topology revealed several **technical difficulties** that complicate its application for-high power inverters. These are as follows:

- This topology requires high speed clamping diodes that must be able to carry full load current and are subject to severe reverse recovery stress.

- For topologies with more than three levels the clamping diodes are subject to increased voltage stress equal to V<sub>pn</sub>.(n-1)/n. Therefore, series connection of diodes might be required. This complicates the design and raises reliability and cost concerns.

- The issue of maintaining the charge balance of the capacitors is still an open issue for NPC topologies with more than three-levels. Although the three-level NPC topology works well with high power factor loads, NPC topologies with more than three levels are mostly used for Static VAR Compensation circuits.

#### 2.2 Flying Capacitor Multilevel Inverter

Another fundamental multilevel topology, the flying capacitor, involves series connection of capacitor clamped switching cells. This topology has several unique and attractive features when compared to the diode-clamped inverter. One feature is that added clamping diodes are not needed. Furthermore, the flying capacitor inverter has switching redundancy within the phase which can be used to balance the flying capacitors so that only one dc source is needed.

Fig. 2.2.1 : Three-level flying capacitor topology.

Fig. 2.2.2 : Four-level flying capacitor topology.

Fig. 2.2.1 shows the three-level flying capacitor inverter. The general concept of operation is that each flying capacitor is charged to one-half of the dc voltage and can be connected in series with the phase to add or subtract this voltage. Table -2.2.1 shows the relationships for the *a*-phase.

In comparison to the three-level diode-clamped inverter, an extra switching state is possible. In particular, there are two transistor states which make up the level  $S_a = 1$ . Considering the direction of the *a*-phase flying capacitor current  $i_{ac1}$  for the redundant states, a decision can be made to charge or discharge the capacitor and therefore, the capacitor voltage can be regulated to its desired value by switching within the phase. In

Table-2.2.1, the current  $i_{adc}$  is the *a*-phase component of the dc current. The total dc current can be calculated by summing the components for all phases.

| Sa | T <sub>a2</sub> | $T_{a1}$ | v <sub>ag</sub>              | i <sub>ac1</sub> | <i>i</i> <sub>adc</sub> |

|----|-----------------|----------|------------------------------|------------------|-------------------------|

| 0  | 0               | 0        | 0                            | 0                | 0                       |

|    | 0               | 1        | v <sub>ac1</sub>             | -i <sub>as</sub> | 0                       |

| 1  | 1               | 0        | $v_{\rm dc}$ - $v_{\rm ac1}$ | i <sub>as</sub>  | i <sub>as</sub>         |

| 2  | 1               | 1        | v <sub>dc</sub>              | 0                | i <sub>as</sub>         |

Table – 2.2.1. Three-level flying capacitor relationships.

Fig.2.2.2 shows the structure for the *a*-phase of the four-level flying capacitor inverter. For this inverter, the capacitors  $v_{ac1}$  and  $v_{ac2}$  are ideally charged to one-third and twothirds of the dc voltage respectively. The four voltage levels are obtained by the relationships shown in Table -2.2.2.

| Sa | T <sub>a2</sub> | $T_{a2}$ | T <sub>a1</sub> | $v_{ m ag}$                        | <i>i</i> <sub>ac1</sub> | i <sub>ac2</sub> | <i>i</i> <sub>adc</sub> |

|----|-----------------|----------|-----------------|------------------------------------|-------------------------|------------------|-------------------------|

| 0  | 0               | 0        | 0               | 0                                  | 0                       | 0                | 0                       |

|    | 0               | 0        | 1               | $v_{ac1}$                          | -i <sub>as</sub>        | 0                | 0                       |

| 1  | 0               | 1        | 0               | $v_{ac2}$ - $v_{ac1}$              | i <sub>as</sub>         | -i <sub>as</sub> | 0                       |

| 1  | 1               | 0        | 0               | $v_{\rm dc}$ - $v_{\rm ac2}$       | 0                       | <i>i</i> as      | <i>i</i> as             |

|    | 0               | 1        | 1               | $v_{ac2}$                          | 0                       | -i <sub>as</sub> | 0                       |

|    | 1               | 1        | 0               | $v_{\rm dc}$ - $v_{\rm ac1}$       | i <sub>as</sub>         | 0                | <i>i</i> as             |

| 2  | 1               | 0        | 1               | $v_{dc}$ - $v_{ac2+}$<br>$v_{ac1}$ | -i <sub>as</sub>        | i <sub>as</sub>  | i <sub>as</sub>         |

| 3  | 1               | 1        | 1               | v <sub>d</sub>                     | 0                       | 0                | <i>i</i> as             |

Table – 2.2.2. Four-level flying capacitor relationships.

The advantages of Flying Capacitor topology are :

- This topology naturally limits the dV/dt stress across the devices.

- Introduces additional switching states that can be used to help maintain the charge balance in the capacitors.

At the present time it seems that this topology has few **disadvantages**.

- The dc-link capacitor charge controller adds complexity to the control of the whole circuit.

- The flying capacitor topology might require more capacitance than the equivalent diode clamped topology. In addition, it is obvious that rather large RMS currents will flow through these capacitors.

#### 2.3 H-Bridge Inverters

#### 2.3.1 Cascaded H-Bridge Inverters

The series H-bridge inverter appeared in 1975, and several patents have been obtained for this topology. Since this topology consist of series power conversion cells, the voltage and power level may be easily scaled. One of the earlier applications of this topology was for plasma stabilization; it was then extended for three-phase applications.

A two-cell series H-bridge inverter is shown in Fig. 2.3.1. The inverter consist of familiar H-bridge (sometimes referred to as full-bridge) cells in a cascade connection. Since each cell can provide three voltage levels (zero, positive dc voltage, and negative dc voltage), the cells are themselves multilevel inverters. Taking the *a*-phase for example, the relationship for a particular cell can be expressed as in Table -2.3.1.

| S <sub>aHi</sub> | T <sub>aLi</sub> | T <sub>aRi</sub> | v <sub>agi</sub>   | <i>i</i> <sub>adci</sub> |

|------------------|------------------|------------------|--------------------|--------------------------|

| -1               | 0                | 1                | -v <sub>adci</sub> | -i <sub>as</sub>         |

|                  | 0                | 0                | 0                  | 0                        |

| 0                | 1                | 1                | 0                  | 0                        |

| 1                | 1                | 0                | V <sub>adci</sub>  | i <sub>as</sub>          |

Table – 2.3.1. H-bridge cell relationships.

\* Where i = No. of Cell. *i.e.* i<sup>th</sup> Cell.

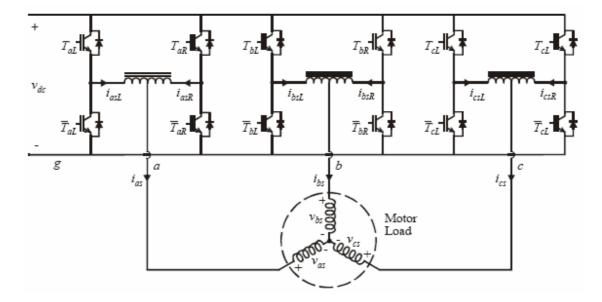

#### 2.3.2 Parallel H-Bridge Inverter Topology

Since nearly all multilevel inverters involve effective series connection of transistor devices, parallel connection of inverter poles through inter-phase reactors is sometimes overlooked or not recognized as a multilevel solution. However, the multilevel features and redundancy were noted by researchers some time ago. One advantage of parallel connection is that the devices share current and this topology is good for high current loads.

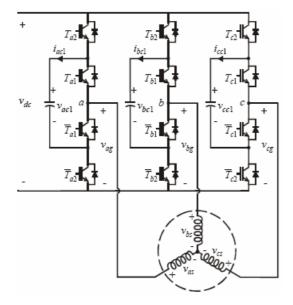

Fig.2.3.2 shows a three-phase three-level inverter made from parallel two-level poles. The inter-phase reactor is similar to a typical transformer with the exception that an airgap exists in the core to ensure linearity and the windings are such that the resistance and leakage inductances are small. With these assumptions, the reactor will have equal

voltages on each half meaning that the line-to-ground voltage is the average of that of each of the two-level poles. Then the general relationships for the *a*-phase can be listed as in Table -2.3.2.

| Sa | $T_{aL}$ | $T_{aR}$ | v <sub>ag</sub>     | i <sub>adc</sub> |

|----|----------|----------|---------------------|------------------|

| 0  | 0        | 1        | 0                   | 0                |

|    | 0        | 1        | <sub>vdc</sub> / 2  | <i>i</i> asR     |

| 1  | 1        | 0        | v <sub>dc</sub> / 2 | i <sub>asL</sub> |

| 2  | 1        | 1        | v <sub>dc</sub>     | i <sub>as</sub>  |

Table – 2.3.2. Parallel inverter relationships.

A primary **advantage** of H-bridge topology is that it provides the flexibility to increase the number of levels without introducing complexity into the power stage. Also, this topology requires the same number of primary switches as the diode-clamped topology, but does not require the clamping diode.

The H-bridge **configuration uses** multiple dedicated dc-busses and often a complicated and expensive line transformer, which makes this a rather expensive solution. However, the cells can be supplied by phase-shifted transformers in medium-voltage systems in order to provide high power quality at the utility connection.

#### 2.3.3 Modified H-Bridge Inverter Topology

The conventional H-bridge topology for n-cells connected in series gives 2n+1 output waveform levels. While in case of modified H-bridge topology for n cells connected in series we get  $2^{n+1}$ -1 level of output waveform. In case of conventional topology the DC voltage at each cell are equal and in case of modified topology the DC voltage at each cell increases in binary pattern *i.e.*, in  $2^{n-1}$  format. For example, 2Vdc, 4Vdc, 8Vdc ....  $2^{n-1}$ .

Fig. 2.3.1 : The Two-cell Cascaded H-bridge drive.

Fig. 2.3.2 : Parallel phase inverter.

| Topology                 | Level           | a                | b               | c                                       | d                                       | e              |

|--------------------------|-----------------|------------------|-----------------|-----------------------------------------|-----------------------------------------|----------------|

| Diode<br>Clamped         | п               | 6( <i>n</i> -1)  | 6( <i>n</i> -1) | <i>n</i> – 1                            | <i>n</i> – 1                            | 2 <i>n</i> -1  |

| Flying<br>Capacitor      | п               | 6( <i>n</i> -1)  | 0               | 3 <i>n</i> – 5                          | $(n-1)^2 + 3\sum_{i=1}^{n-2} i^2$       | 2 <i>n</i> – 1 |

| Conventional<br>H-bridge | п               | 6( <i>n</i> -1)  | 0               | (Even) $3n/2 - 1.5$<br>(Odd) $3n/2 - 2$ | (Even) $3n/2 - 1.5$<br>(Odd) $3n/2 - 2$ | 2 <i>n</i> -1  |

| Modified<br>H-bridge     | $m = 2^{n} - 1$ | 12( <i>n</i> -1) | 0               | (Odd) $3n/2+1.5$<br>(Even) $3n/2+3$     | (Odd) $3n/2 + 1.5$<br>(Even) $3n/2 + 3$ | 2 <i>m</i> -1  |

Table – 2.4. Comparison of Topologies For Multilevel Inverters.

a : switches (with free-wheeling diodes).

b : independent diodes (with different reverse voltages possible).

c : capacitors (with different voltages possible).

d : real number of capacitors (series and parallel connections for the same voltage distribution and capacitance).

e : line-to-line output voltage levels.

## 3. MODULATION TOPOLOGIES FOR MULTILEVEL INVERTER

It is generally accepted that the performance of an inverter, with any switching strategies, can be related to the harmonic contents of its output voltage. Power electronics researchers have always studied many novel control techniques to reduce harmonics in such waveforms. In multilevel technology, the well-known modulation topologies are as follows:

- 1) Sinusoidal Pulse Width Modulation (SPWM).

- 2) Space Vector Pulse Width Modulation (SVPWM).

#### 3.1 Sinusoidal Pulse Width Modulation (SPWM)

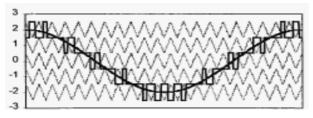

Sinusoidal pulse width modulation is one of the primitive techniques, which are used to suppress harmonics presented in the quasi-square wave. These methods have been extensively studied and are among the most popular in industrial applications. These methods involve a comparison of the reference signal with a triangular carrier waveform and the detection of cross-over instances to determine switching events. The variations of these methods are essentially in the polarity and shape of the carrier waveforms.

Fig. 3.1.1 : 6 – Level Inverter SPWM

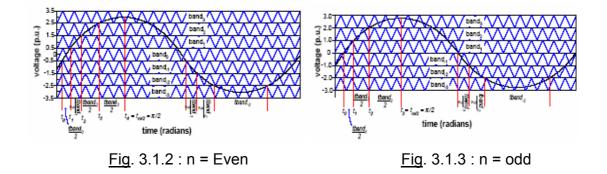

For an n-level inverter, n-1 carriers with the same frequency  $f_c$  and same peak-to-peak amplitude  $A_c$  are used. The reference, or modulation, waveform has peak-to-peak amplitude  $A_m$  and frequency  $f_m$ , and it is centered in the middle of the carrier set. The three cases of triangular wave disposition are :

- 1) Alternative phase opposition disposition, where each carrier band is shifted by  $180^{\circ}$  from the adjacent bands,

- Phase opposition disposition, where the carriers above the zero reference are in phase, but shifted by 180° from those carriers below the zero reference and

- 3) In-phase disposition, where all the carriers are in phase.

Fig. 3.1.2 and 3.1.3 shows the SPWM for number of output levels even and odd respectively.

Variable frequency carrier band is another topology used in multilevel sinusoidal PWM. In this topology, as shown in Fig. 3.1.4, the frequency of the carrier band decreases as we go from zero-level to upper bands and lower bands.

Fig. 3.1.4 Variable Frequency Carrier Band.

#### 3.2 Space Vector Pulse Width Modulation (SVPWM)

The space-vector PWM method is an advanced, computation-intensive PWM method and is possibly the best among all the PWM techniques for variable-frequency drive applications still known. Because of its superior performance characteristics, it has been finding widespread application in recent years.

It can be shown that the space vector  $\overline{V}$  with magnitude  $V_m$  rotates in a circular orbit at angular velocity  $\omega$ , where the direction of rotation depends on the phase sequence of the voltages. With the sinusoidal three-phase command voltages, composite PWM fabrication at the inverter output should be such that the average voltages follow these command voltages with a minimum amount of harmonic distortion.

The space vector modulation uses averaging technique, as it uses the voltage vector such that their average value is equal to the instantaneous output voltage required. For averaging the value, the first step is identifying the nearest three voltage vectors and using the redundancy. After identification the next step is to estimate the on-time period for each voltage vector. The final step is to determine the sequence of switching of each voltage vector. The SVM can be implemented by the help of fast DSP's.

#### 3.2.1 Space Vector PWM For a Three-Level Diode Clamped Inverter

In case of a two-level inverter there are total of 8-vectors (6-non zero vectors and 2-zero vectors). The number of vectors for a n-level inverter is given by

No. of space vector =  $n^3$

Hence in case of a three-level inverter there are 27 vectors and among them, there are 3zero vectors and 24-non zero vectors. Similarly, five-level inverter shall have 125 vectors. Each switching state, or combination of phase-leg switches, produces a defined set of three-phase voltages, which can be represented in a hexagon form as shown in figure 3.2.1.1.

Fig. 3.2.1.1 : Space - Vector Diagram for Three-Level Inverter.

Suitable vectors from the space-vector (SV) diagram should be chosen for each modulation cycle in order to generate the reference vector  $(m_i)$ . The vectors nearest to  $m_i$  are the most appropriate selections in terms of their ability to minimize the switching frequencies of the power devices, improve the quality of the output voltage spectra, and the electromagnetic interference (EMI).

In figure 3.2.1.1, the SV diagram of the three-level inverter is divided into six sextants, and each sextant is then divided into four triangular regions in order to show the vectors nearest to the reference.

Figure 3.2.1.2 represents the simplified model of the three-level diode clamped inverter, where Vc1 and Vc2 are the voltages across the lower and the upper capacitors voltages respectively.

Fig. 3.1.1.2 : Simplified Model of Three-Level Diode Clamped Inverter.

Each leg has the following three-states, which are utilized to generate the required voltage :

State '+': Upper switches ON.

State '0' : Auxiliary switches ON.

State '-' : Lower switches ON.

Four groups of vectors can be distinguished in this SV diagram, as described in the following:

- (1) The "large vectors" ('+--', '++-', '-+-', '-++', '--+' and '+-+') assign the output voltages of the inverter to either the highest or the lowest DC voltages levels. As they do not connect any output to the NP, they do not affect the voltage balance of the capacitors. These vectors can generate the highest AC voltage amplitudes because they have the greatest lengths. In fact, these six vectors are equivalent to the active ones of the two-level inverter.

- (2) The "medium vectors" ('+0-', '0+-', '-+0', '-0+', '0-+' and '+-0') connect each output to a different DC-link voltage level. Under balanced conditions, their tip end in the middle of the segments that join two consecutive large vectors. The

length of the medium vectors defines the maximum amplitude of the reference vector for linear modulation and steady-state conditions, which is  $\sqrt{3}/2$  the length of the large vectors. Since one output is always connected to the NP, the corresponding output current will define the NP current. This connection produces voltage imbalances in the capacitors, and these must be compensated.

- (3) The "short vectors" ('0--/+00', '00-/++0', '-0-/0+0', '-00/0++', '--0/00+' and '0-0/+0+') connect the AC outputs to two consecutive DC-link voltage levels. Their length is half the length of the large vectors. They are double vectors, which means that two states of the converter can generate the same voltage vector. As they affect the NP current in opposite ways, proper utilization of these vectors will help the NP voltage to achieve balance.

- (4) The "zero vectors" ('---', '000' and '+++') are in the origin of the diagram. They connect all of the outputs of the converter to the same DC-link voltage level, and therefore, they do not produce any current in the DC side.

#### 3.2.2 Simplified Calculation of Duty Cycles

Taking into account the symmetry of all the sextants, it is interesting to reflect the reference vector into the first sextant in order to reduce the number of relevant regions. Also, the amplitude of the reference vector must be normalized to fit into a diagram in which the triangular regions have unity lengths.

The theoretical maximum length of the normalized reference vector  $(m_i)$  is the two-unity value. However, in steady-state conditions, its length is limited to  $\sqrt{3}$  due to the fact that longer lengths of this vector will be outside of the vector-diagram hexagon (figure 3.2.2.1), and thus cannot be generated by modulation. Over modulation is produced if the normalized reference vector assumes lengths longer than  $\sqrt{3}$  for some positions of this vector, but it can never be outside of the hexagon.

Fig. 3.2.2.1 : Max. length of the normalized reference vector in steady-state conditions.

In figure 3.2.2.2, the normalized reference vector is decomposed into the axes located at zero and sixty degrees, obtaining projections  $m_1$  and  $m_2$ , respectively.

The lengths of the new vectors are determined as follows :

$$m_1 = (\sqrt{3}) * \left[ \cos \theta_n - \frac{\sin \theta_n}{\sqrt{3}} \right]$$

and  $m_2 = 2 * \sqrt{3} * \frac{\sin \theta_n}{\sqrt{3}}$

In general, these values are the direct duty ratios of the vectors, as in the following :

$$d_{0--/+00} = m_1$$

,

$d_{00-/++0} = m_2$  and

$d_{+++/000/---} = 1 - m_1 - m_2$ .

The cases for which the normalized reference vector is located in Regions 2, 3 and 4 are shown in figure 3.2.2.3-(a,b,c).

Table-3.2.1 summarizes the information needed to ascertain the region where the reference vector lies and the duty cycles of the nearest vectors in the first sextant.

| Case                      | Region | Duty Cycles                    |

|---------------------------|--------|--------------------------------|

| $m_1 \leq 1$              |        | $d_{0/+00} = m_1$              |

| $m_2 \leq 1$              | 1      | $d_{00-/++0} = m_2$            |

| $m_1 + m_2 \le 1$         |        | $d_{+++/000/} = 1 - m_{1-}m_2$ |

| $m_1 \leq 1$              |        | $d_{0/+00} = 1 - m_2$          |

| $m_2 \leq 1$              | 2      | $d_{00-/++0} = 1 - m_1$        |

| $m_1 + m_2 > 1$           |        | $d_{+0-} = m_1 + m_2 - 1$      |

|                           | 3      | $d_{+} = m_1 - 1$              |

| $m_1 > 1$                 |        | $d_{+0-} = m_2$                |

|                           |        | $d_{0/+00} = 2 - m_1 - m_2$    |

|                           | 4      | $d_{+0-} = m_1$                |

| <i>m</i> <sub>2</sub> > 1 |        | $d_{++-} = m_2 - 1$            |

|                           |        | $d_{00-/++0} = 2 - m_1 - m_2$  |

Table-3.2.1: Summary of information for the SVPWM.

For all cases, it is assumed that the sum of  $m_1$  and  $m_2$  is not greater than 2; otherwise, the reference vector would be outside of the hexagon, and thus could not be reproduced by modulation.

#### 3.2.3 Symmetric Modulation

In this method the nearest vectors in the given sextant are used for getting the required output voltage. The vectors must be selected such that the DC-link capacitors voltages are balanced. The NP current must be positive in order to discharge the lower capacitor, and must be negative to charge it. For example, vector '0--' will discharge the lower capacitor  $(i_1 = i_a > 0)$ , and vector '+00' will charge it  $(i_1 = i_b + i_c = -i_a < 0)$ .

The switching sequence used in first sector and its different regions is as shown in Table-3.2.2.

Table-3.2.2: Sequence of switching in Sector-1.

| Sector |                           | Region - 1     | Region - 2 | Region - 3 | Region - 4 |

|--------|---------------------------|----------------|------------|------------|------------|

|        | Va                        | -000+++        | 0+++       | 0 0 + + +  | 0+++       |

| 1      | $\mathbf{V}_{\mathbf{b}}$ | <b>00</b> 0 ++ | 0 0        | - 000+     | 00++       |

|        | Vc                        | 0 0 0 +        | 0          | 0 0        | 0          |

Fig. 3.2.2.3 : Waveforms showing sequence of switching in Sector-1 & Region-1.

## 4. SIMULATION MODEL OF THREE-LEVEL DIODE CLAMPED INVERTER

#### 4.1 Sinusoidal PWM With Two DC Source

The simulation of the proposed scheme is done by the help of the PSIM v 6.0 Simulation package.

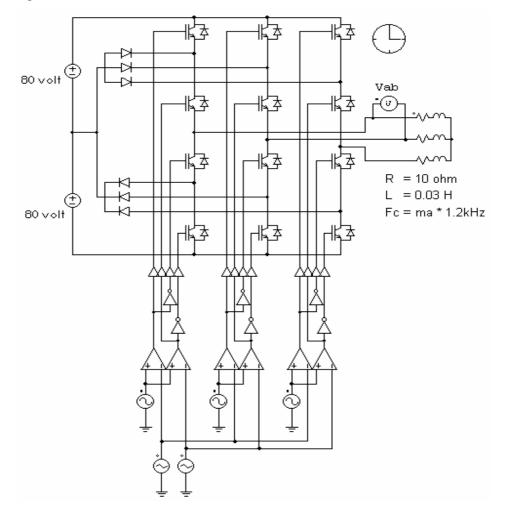

**Figure – 4.1** shows the model of a Three-Level Diode-Clamped Inverter with DC sources, in PSIM v 6.0. For initial understanding of the topology proposed, two DC sources of 80 Volts and Resistive and Inductive load with value 10 ohm and 0.03 Henry respectively are used. Twelve IGBT's (with anti-parallel diodes) are used as the switching devices.

<u>Fig</u>. 4.1 : Three-Level Diode-Clamped Inverter With Sinusoidal PWM With Two DC Source.

#### 4.1.1 Simulation Results For Triangular Waves With Phase-Disposition

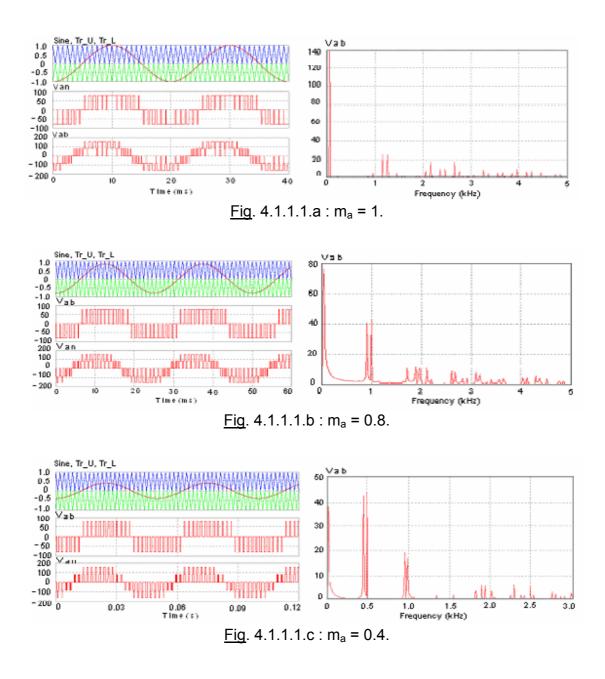

In this case the carrier triangular waves (upper wave and lower wave) are phase disposed by  $180^{\circ}$ . The load used over here is resistive load of value R = 10 ohms. The simulation is done over here is with modulation index  $m_a = 1$ ,  $m_a = 0.8$  and  $m_a = 0.4$ . The frequency of carrier waves used is Fc =  $m_a * 1.2$  kHz. The figures below shows the output phase voltage V<sub>ab</sub>, phase voltage V<sub>an</sub> and the fast fourier transform of voltage V<sub>ab</sub>.

The simulation shown below is for the load R = 10 ohms and L = 0.03H with  $m_a = 1$  and  $m_a = 0.4$ .

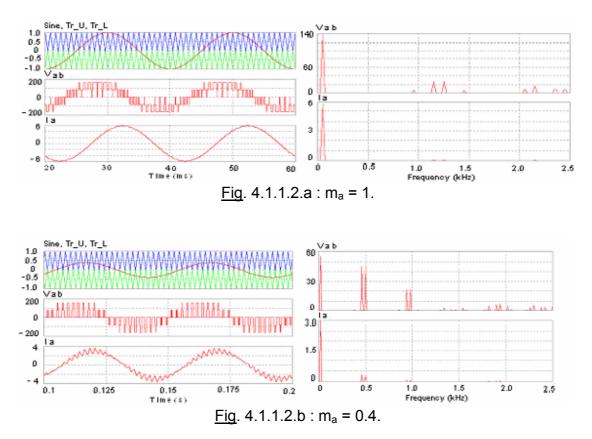

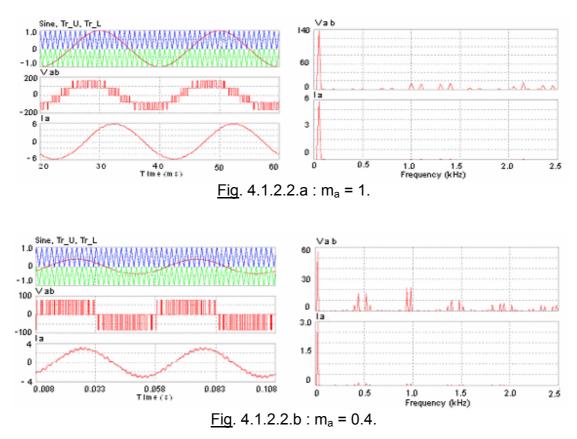

#### 4.1.2 Simulation Results For Triangular Waves With No Phase-Disposition

The simulation shown below is for the load R = 10 ohms and  $m_a = 1$ . Here the upper and lower carrier waves have  $0^\circ$  phase shift as shown in figure 4.1.2.1.

The simulation shown below is for the load R = 10 ohms and L = 0.03H.

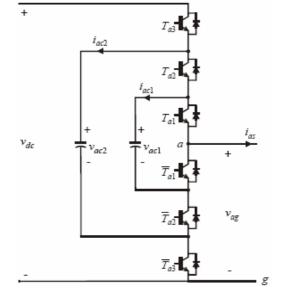

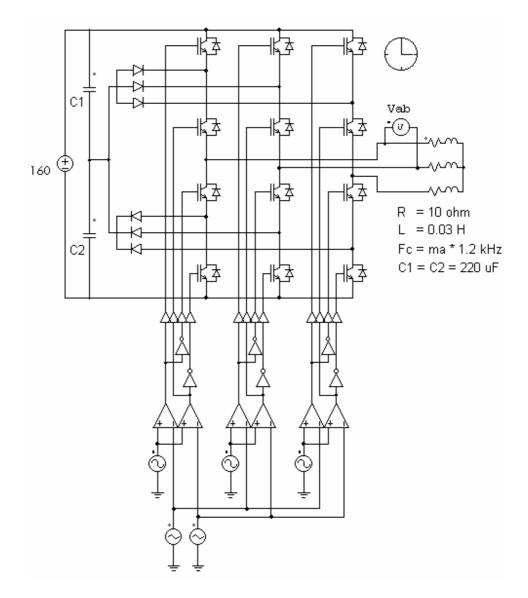

#### 4.2 Sinusoidal PWM With Two Capacitors & Single DC Source

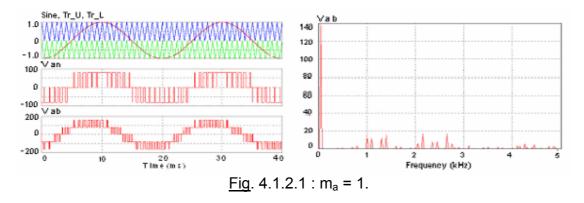

**Figure** – **4.2** shows the model of a Three-Level Diode-Clamped Inverter with DC source, in PSIM. Here single DC source with 160 Volts and two series capacitor with  $C = 220 \mu$  and Resistive and Inductive load with value 10 ohm and 0.03 Henry respectively are used.

Fig. 4.2 : Three-Level Diode-Clamped Inverter With Sinusoidal PWM With Single DC Source.

The value of the capacitor is selected on the basis of the thumb rule used in industries, i.e., for 1 ampere rms output current (at rated condition) 40uF to 60uF capacitance is selected.

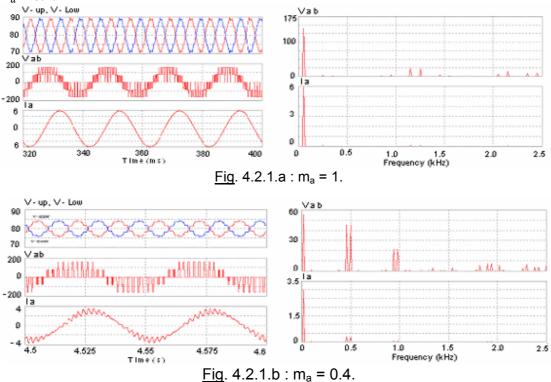

#### 4.2.1 Simulation Results For Triangular Waves With Phase-Disposition

The simulation shown below is for the load R = 10 ohms and L = 0.03H with  $m_a = 1$  and  $m_a = 0.4$ .

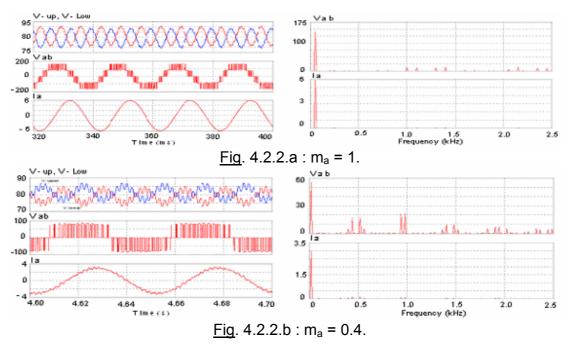

4.2.2 Simulation Results For Triangular Waves With No Phase-Disposition

The first set of output line voltage harmonics are centered around the switching frequency of the carrier wave, as it can be seen from the fast fourier transform analysis of the output line voltage. The other set of harmonics are centered around the multiple of the switching frequency of the carrier wave as seen above. The total harmonic distortion is considerably low in case of the topology with carrier waves in no phase disposition state. The main problem in case of SPWM is the use of the redundant switching states, which are used in a proper manner in case of SVPWM to balance the average neutral point current to zero and balance the neutral point voltage with upper and lower capacitor voltages equal.

#### 4.3 Simulation Model With Space-Vector PWM

Simulation of the proposed model in done in the PSIM v 6.0 package. The programming for the sector identification, time calculations and all other calculations are done in the Visual Basic v 6.0. Figure 4.3.a shows the PSIM model.

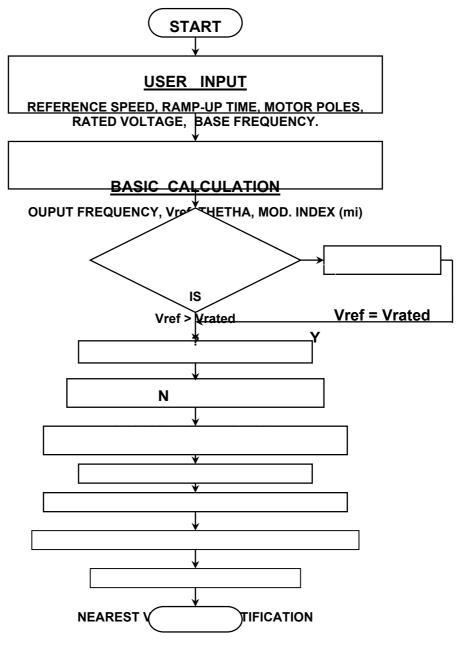

Flowchart of The Program:

ASSIGNMENT OF DUTY RATIO TO VECTORS

SIGNALS OUT TO IGBT's

Fig. 4.3.b : Flowchart of the proposed model.

#### 4.4 Simulation Results of SVPWM.

Fig. 4.4.1.2 : Capacitor Voltages.

Fig. 4.4.1.3 : Motor Current.

Fig. 4.4.1.4 : Phase Voltage Vab.

The problem in Diode-Clamped Inverter is the voltage unbalance in the upper and lower capacitors, which can be seen from the Figure 4.4.1.2. This problem needs to be overcome.

The problem of the unbalanced capacitor voltages is overcome by adjusting the counter value according to the change in reference speed value and the ramp-up. The simulation results are shown in the following section with different speed references.

Fig. 4.4.2.1 : Speed ref. & Motor speed.

Fig. 4.4.2.2 : Capacitor Voltages.

Fig. 4.4.2.3 : Motor Current Ia (a.) Ref. speed and (b.) Starting.

Fig. 4.4.2.4 : Phase Voltage Vab.

#### 4.4.3 Speed reference = 1200 rpm.

Fig. 4.4.3.1 : Speed ref. & Motor speed.

Fig. 4.4.3.2 : Capacitor Voltages.

Fig. 4.4.3.3 : Motor Current Ia.

## 4.4.4 Speed reference = 400 rpm.

Fig. 4.4.4.1 : Speed ref. & Motor speed.

Fig. 4.4.3.4 : Phase Voltage Vab.

Fig. 4.4.4.2 : Capacitor Voltages.

#### 4.4.5 Speed reference = 1500rpm to -1500rpm to 400 rpm.

Fig. 4.4.5.1 : Speed ref. & Motor speed.

Fig. 4.4.5.2 : Motor Current (la).

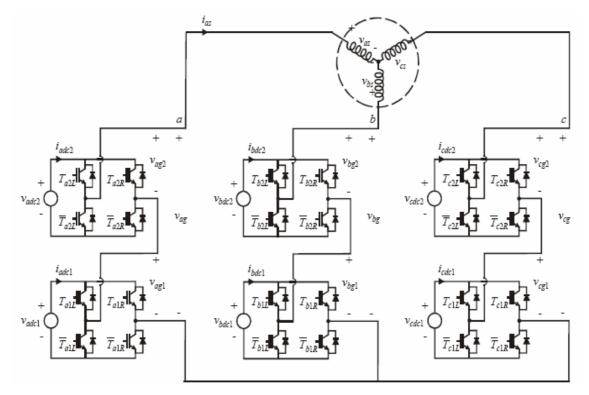

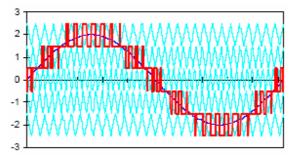

Fig. 4.4.5.3 : Motor Current (la).