## Artificial Intelligence Based Test Data Compression Techniques

**Major Project**

Submitted in partial fulfillment of the requirements

For the degree of

Master of Technology in Electronics and Communication Engineering (VLSI DESIGN)

By

Harikrishna Parmar 09MEC014

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING AHMEDABAD-382481 May 2011

## Artificial Intelligence Based Test Data Compression Techniques

**Major Project**

Submitted in partial fulfillment of the requirements

For the degree of

Master of Technology in Electronics and Communication Engineering (VLSI DESIGN)

By

Harikrishna Parmar 09MEC014

Guided by Prof. Usha Mehta

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING AHMEDABAD-382481 May 2011

## Declaration

This is to certify that

- i) The thesis comprises my original work towards the degree of Master of Technology in Information and Communication Technology at Nirma University and has not been submitted elsewhere for a degree.

- ii) Due acknowledgement has been made in the text to all other material used.

Harikrishna Parmar

## Certificate

This is to certify that the Major Project entitled "Artificial Intelligence Based Test Data Compression Techniques" submitted by Your Name (09MEC014), towards the partial fulfillment of the requirements for the degree of Master of Technology in Electronics and Communication Engineering of Nirma University of Science and Technology, Ahmedabad is the record of work carried out by him under my supervision and guidance. In my opinion, the submitted work has reached a level required for being accepted for examination. The results embodied in this major project, to the best of my knowledge, haven't been submitted to any other university or institution for award of any degree or diploma.

Usha.S Mehta Guide, Professor, PG VLSI Design, Institute of Technology, Nirma University, Ahmedabad Dr. N.M DevashrayeeP.G.Coordinator,PG VLSI Design,Institute of Technology,Nirma University, Ahmedabad

Prof. A. S. RanadeHead of Dept, Professor,Institute of Technology,Nirma University, Ahmedabad

Dr. K.Kotecha Director, Professor, Institute of Technology, Nirma University, Ahmedabad

### Abstract

The circuit consumes more power during test mode compared to functional mode. So test power has been major big concern in large System-on-Chip designs from last decade. In the first part of report, the state-of-the-art in low power testing is presented. The first part contains the detailed survey on various power reduction techniques proposed for both the aspects of testing i.e. external testing as well as Built-In-Self-Test. The advances in DFT techniques emphasizing low power is also included in this part.

In the second part novel methods are presented which aims at minimizing the total power consumption during testing. This is achieved by minimizing the switching activity in the circuit by reducing the Hamming Distance between successive test vectors. In this method the test vectors are reordered for minimum total hamming distance and the same vector set is used for testing. Artificial intelligence is another approach that is described to reduce switching activity. Also Test power has become a serious problem with scan-based testing. It can lead to prohibitive test power in the process of test application. During the process of scan shifting, the states of the flip-flops are changing continually, which causes excessive switching activities. Test vector reordering for reducing scan in scan out power is one of the general goal of low power testing. WTM based reordering technique have proposed here to reorder the test vectors in an optimal manner to minimize switching activity during testing.

In the third part it is shown that MT Fill algorithm is preferable when power is a big concern. Frequency directed bit filling approach is preferable when compression is a major goal. But the proposed approach that is a combination of MT fill and frequency directed bit filling is preferable when one wants to achieve moderate power and compression.

The final part addresses error-resilience that is the capability to tolerate bit-flips in a compressed test data stream (which is transferred from an Automatic Test Equipment

(ATE) to the Device-Under-Test (DUT)). In an ATE, bit-flips may occur in either the electronics components of the loadboard, or the high speed serial communication links (between the user interface workstation and the head). It is shown that errors caused by bit-flips can seriously degrade the test quality (as measured by coverage) of the compressed data streams. The effects of bit-flips on compression are analyzed and various test data compression techniques are evaluated.

### Acknowledgements

No Project work is ever the outcome of efforts or talent of single individual. This is no exception. Many teachers, friends, well-wishers have contributed to this work directly or indirectly and made it possible for me to present it in its present shape. Although it is not possible for me to name and thank them all individually, I must make special mention some of the personalities and acknowledge my sincere indebtedness to them and preserve gratitude to many others in my heart.

"You can even do right things you want and you can even do it for the right reasons you want. But if you don't have the right and proper guidance, you can never hit a right target." For that I express my deep and sincere gratitude to P.G.Coordinator Dr. N. M. Devashrayee for his constant encouragement, valuable guidance and constructive suggestions during all the stages of the Project work. He has been great source of inspiration and help me during my whole course by providing me the necessary guidance in every way to build the better future.

I am deeply indebted to my guide Prof. Usha Mehta for her constant guidance and motivation. she has devoted significant amount of his valuable time to plan whole project work. Without her experience and insights, it would have been very difficult to do quality work.

I am also thankful to Prof. N. P. Gajjar, Prof. Amisha P. Naik and all the faculty members of Department of Electronics & Communchication Engineering, Institute of Technology, Nirma University, Ahmedabad, for providing me all the necessary guidance through out the term which provides lots of help in course of my Project work. I also gratefully acknowledge Ms. Niti Avasthi for providing me the full laboratory support at PG-VLSI Design Lab.

> - Harikrishna Parmar 09MEC014

# Contents

| D            | eclar               | ation ii                                     | ii            |

|--------------|---------------------|----------------------------------------------|---------------|

| $\mathbf{C}$ | ertifi              | cate                                         | v             |

| A            | bstra               | nct                                          | v             |

| A            | ckno                | wledgements vi                               | ii            |

| Li           | ist of              | Tables x                                     | i             |

| Li           | ist of              | Figures xi                                   | ii            |

| 1            | <b>Int</b> r<br>1.1 |                                              | <b>2</b><br>2 |

| <b>2</b>     | Lite                | erature Survey                               | 5             |

|              | 2.1                 | Terminology                                  | 5             |

|              | 2.2                 |                                              | 6             |

|              | 2.3                 |                                              | 8             |

|              |                     | 0 i                                          | 8             |

|              |                     | 2.3.2 Ordering Techniques                    | 9             |

|              |                     | 2.3.3 Input Control                          | 0             |

|              |                     | 2.3.4 Vector Compaction and Data Compression | 0             |

|              |                     | 2.3.5 Scan Chain Transformation              | 1             |

|              |                     | 2.3.6 Clock Scheme Modification              | 2             |

|              | 2.4                 | Low Power BIST Techniques                    | 2             |

|              |                     | 2.4.1 Low Power Test Pattern Generators      | 3             |

|              |                     | 2.4.2 LFSR Tunning                           | 4             |

|              |                     | 2.4.3 Vector Filtering BIST                  | 5             |

|              |                     | 2.4.4 Circuit Partitioning                   | 6             |

|              |                     | 2.4.5 Low Power RAM Testing                  | 6             |

|              | 2.5                 | Low Power DFT Techniques                     | 7             |

| 3        | Rec                                             | ordering Techniques                                                                                                   | 18       |  |  |  |  |  |

|----------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|----------|--|--|--|--|--|

|          | 3.1 Hamming Distance based Reordering technique |                                                                                                                       |          |  |  |  |  |  |

|          |                                                 | 3.1.1 Problem formulation                                                                                             | 21       |  |  |  |  |  |

|          |                                                 | 3.1.2 Total Hamming Distance(THD)                                                                                     | 21       |  |  |  |  |  |

|          |                                                 | 3.1.3 Reordering Algorithm:                                                                                           | 22       |  |  |  |  |  |

|          | 3.2                                             | Artificial Intelligence approach                                                                                      | 24       |  |  |  |  |  |

|          |                                                 | 3.2.1 Brief overview                                                                                                  | 24       |  |  |  |  |  |

|          |                                                 | 3.2.2 Prior Work                                                                                                      | 25       |  |  |  |  |  |

|          |                                                 | 3.2.3 Motivation of the work and problem formulation                                                                  | 28       |  |  |  |  |  |

|          |                                                 | 3.2.4 An A <sup>*</sup> based method for dynamic power minimization by test                                           |          |  |  |  |  |  |

|          |                                                 | 0                                                                                                                     | 29       |  |  |  |  |  |

|          |                                                 | 3.2.5 Cost function $g(n)$                                                                                            | 30       |  |  |  |  |  |

|          |                                                 | 3.2.6 Computing lower bound of switching activity: Heuristic func-                                                    |          |  |  |  |  |  |

|          |                                                 | tion $h(n)$ )                                                                                                         | 31       |  |  |  |  |  |

|          |                                                 | 3.2.7 The A <sup>*</sup> based algorithm: AITVR $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                 | 32       |  |  |  |  |  |

|          |                                                 |                                                                                                                       | 33       |  |  |  |  |  |

|          |                                                 | 3.2.9 Empirical Observation                                                                                           | 33       |  |  |  |  |  |

|          | 3.3                                             | WTM based Reordering of Combine Test Vector and Output Response                                                       | 35       |  |  |  |  |  |

|          |                                                 | 3.3.1 Problem formulation                                                                                             | 35       |  |  |  |  |  |

|          |                                                 | 3.3.2 Cost Function $g(n)$                                                                                            | 35       |  |  |  |  |  |

|          |                                                 | 3.3.3 Empirical observation $\ldots$ | 37       |  |  |  |  |  |

| 4        | D!4                                             |                                                                                                                       | ഹ        |  |  |  |  |  |

| 4        |                                                 | 8 8                                                                                                                   | 39<br>20 |  |  |  |  |  |

|          | 4.1                                             | 0                                                                                                                     | 39       |  |  |  |  |  |

|          | 4.2                                             | 1 0 0                                                                                                                 | 40<br>41 |  |  |  |  |  |

|          |                                                 | 1 1                                                                                                                   | 41<br>43 |  |  |  |  |  |

|          | 19                                              | 0                                                                                                                     |          |  |  |  |  |  |

|          | 4.3                                             | Mixed approach : Frequency directed + MT Fill                                                                         | 46       |  |  |  |  |  |

| <b>5</b> | Cor                                             | npression Algorithm                                                                                                   | 50       |  |  |  |  |  |

|          |                                                 |                                                                                                                       | 52       |  |  |  |  |  |

|          | 5.2                                             | Code-Based Schemes                                                                                                    | 53       |  |  |  |  |  |

|          |                                                 | 5.2.1 Dictionary Code (Fixed-to-Fixed)                                                                                | 54       |  |  |  |  |  |

|          |                                                 | 5.2.2 Huffman Code (Fixed-to-Variable)                                                                                | 55       |  |  |  |  |  |

|          |                                                 | 5.2.3 Run-Length Code (Variable-to-Fixed)                                                                             | 58       |  |  |  |  |  |

|          |                                                 | 5.2.4 Golomb Code (Variable-to-Variable)                                                                              | 59       |  |  |  |  |  |

| ~        | -                                               |                                                                                                                       | ~ .      |  |  |  |  |  |

| 6        |                                                 |                                                                                                                       | 64       |  |  |  |  |  |

|          | 6.1                                             | Brief Overview                                                                                                        | 64       |  |  |  |  |  |

|          |                                                 | 6.1.1 Previous Work done                                                                                              | 65       |  |  |  |  |  |

|          | 6.0                                             | 1                                                                                                                     | 66       |  |  |  |  |  |

|          | 6.2                                             | Analysis                                                                                                              | 75       |  |  |  |  |  |

|          |                                                 | 6.2.1 Propagation and Shifts                                                                                          | 76       |  |  |  |  |  |

| 7 Henry in a Code board to shui and                          |                   |

|--------------------------------------------------------------|-------------------|

| 7 Hamming Code based technique<br>7.0.2 Generating Algorithm | <b>80</b><br>. 81 |

| 8 Cyclic redundancy check (CRC)<br>8.0.3 Computation of CRC  | <b>89</b><br>. 90 |

| 9 Two dimensional Parity check Code                          | 93                |

| 10 Conclusion and Future Scope         10.1 Conclusion       |                   |

| References                                                   | 100               |

| List of Publication                                          | 105               |

# List of Tables

| Ι    | Comparison of Switching activity in Hamming and AI           | 38       |

|------|--------------------------------------------------------------|----------|

| Ι    | Test data set for frequency directed bit filling             | 41       |

| II   | Comparison of Switching activity in different ISCAS Circuits | 48       |

| III  | Comparison of Compression in different ISCAS Circuits        | 49       |

|      |                                                              |          |

| Ι    | Bit Flip without Compression                                 | 68       |

| II   | Bit Flip after Compression for Huffman Coding                | 69       |

| III  | Bit Flip after Compression for Selective Huffman Coding      | 70       |

| IV   | Bit Flip after Compression for FDR Coding                    | 71       |

| V    | Bit Flip after Compression for EFDR Coding                   | 72       |

| VI   | Bit Flip after Compression for SAFDR Coding                  | 73       |

| VII  | Bit Flip after Compression for GOLOMB Coding                 | 74       |

| VIII | Bit Flip after Compression for VIHC Coding                   | 75       |

| т    |                                                              | 05       |

| I    | Area Overhead with Huffman Code                              | 85       |

| II   | Area Overhead with selective Huffman Code                    | 86       |

| III  | Area Overhead with FDR Code                                  | 86       |

| IV   | Area Overhead with EFDR Code                                 | 87       |

| V    | Area Overhead with SAFDR Code                                | 87       |

| VI   | Area Overhead with GOLOMB Code                               | 88       |

| VII  | Area Overhead with VIHC Code                                 | 88       |

| I    | Bits Overhead with Huffman Code                              | 94       |

| II   | Bits Overhead with Selective Huffman Code                    | 95       |

| III  | Bits Overhead with FDR Code                                  | 95       |

| IV   | Bits Overhead with EFDR Code                                 | 96       |

| V    | Bits Overhead with SAFDR Code                                | 96       |

| VI   | Bits Overhead with GOLOMB Code                               | 97       |

| VI   | Bits Overhead with VIHC Code                                 | 97<br>97 |

| V II |                                                              | 91       |

# List of Figures

| 3.1  | a.)<br>Test Vectors for Full adder circuit b.) Switching matrix<br>$\mathrm{hd}[\mathbf{n}][\mathbf{n}]$ .<br>. 23                                                       |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.2  | Test Vectors of C17                                                                                                                                                      |

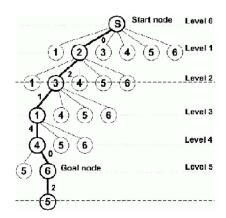

| 3.3  | Transition graph of C17 $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 30$                                                                       |

| 3.4  | Finding optimal path from informed search space                                                                                                                          |

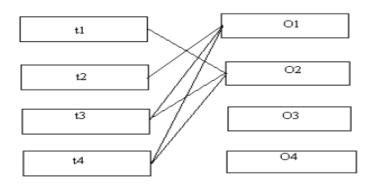

| 3.5  | a.) Test Vector b.)Output Response                                                                                                                                       |

| 3.6  | Test Vector passing through Output Response                                                                                                                              |

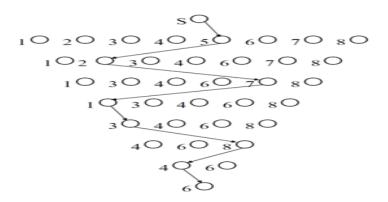

| 3.7  | Finding optimal path in informed search space                                                                                                                            |

| 4.1  | Test Vector Sequence                                                                                                                                                     |

| 4.2  | Transitions in case of Opposite Bit Filling 44                                                                                                                           |

| 4.3  | Transitions in case of Same Bit Filling 45                                                                                                                               |

| 4.4  | Test Vectors                                                                                                                                                             |

| 4.5  | Part of data for a.) Frequency Directed b.MT Fill) 47                                                                                                                    |

| 4.6  | MT Filled data is mapped in above fig                                                                                                                                    |

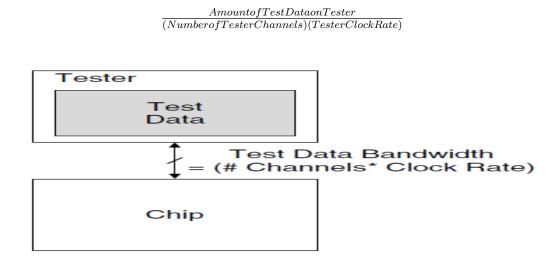

| 5.1  | Block diagram illustrating test data bandwidth                                                                                                                           |

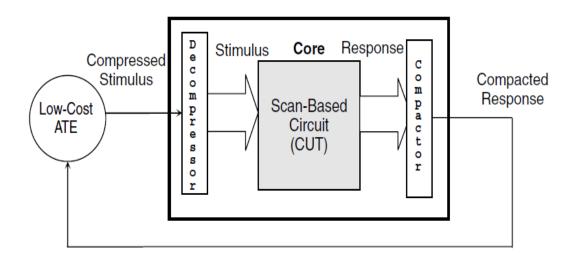

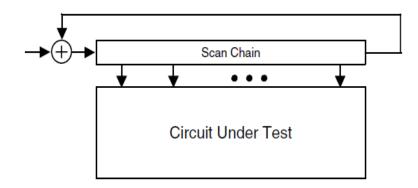

| 5.2  | Architecture for test compression $\ldots \ldots \ldots$ |

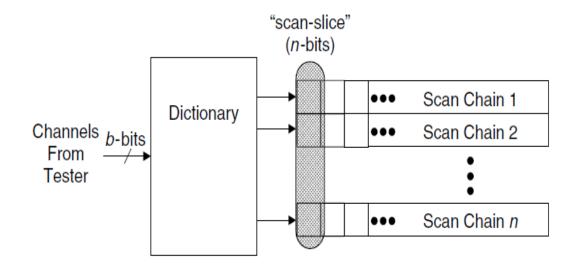

| 5.3  | Test compression using a complete dictionary                                                                                                                             |

| 5.4  | Statistical Coding based on symbole frequencies                                                                                                                          |

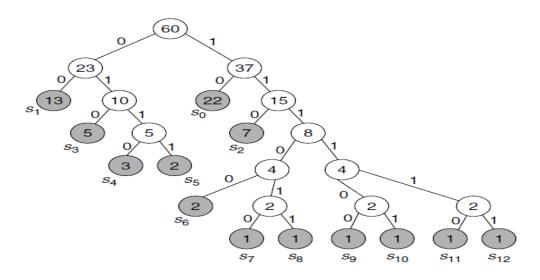

| 5.5  | Example of test set divided into 4 bit block                                                                                                                             |

| 5.6  | Huffman Tree                                                                                                                                                             |

| 5.7  | 3 Bit runlength code                                                                                                                                                     |

| 5.8  | Cyclical scan architecture for applying difference vectors                                                                                                               |

| 5.9  | GOLOMB Code                                                                                                                                                              |

| 5.10 | FDR Code                                                                                                                                                                 |

| 5.11 | EFDR Code                                                                                                                                                                |

| 5.12 | SAFDR Code                                                                                                                                                               |

| 5.13 | VIHC Code                                                                                                                                                                |

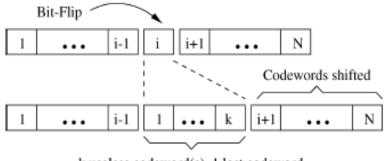

| 6.1  | Conceptual view of the shift effect due to a bit-flip                                                                                                                    |

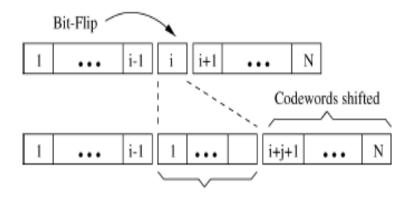

| 6.2  | Conceptual view of the propagation effect due to a bit-flip 77                                                                                                           |

| 7.1  | Hamming code example                                                                                                                                                     |

#### LIST OF FIGURES

| $8.2 \\ 8.3$ | Padded bits with CRC                | 91<br>91 |

|--------------|-------------------------------------|----------|

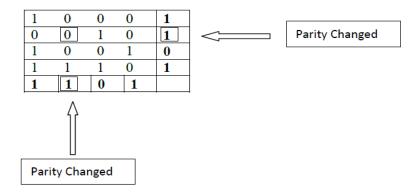

| 9.1          | Two dimensional Parity check Matrix | 93       |

## Chapter 1

## Introduction

THE SYSTEM-ON-A-CHIP (SoC) revolution challenges both design and test engineers, especially in the area of power dissipation. Generally, a circuit or system consumes more power in test mode than in normal mode. This extra power consumption can give rise to severe hazards in circuit reliability or, in some cases, can provoke instant circuit damage. Moreover, it can create problems such as increased product cost, difficulty in performance verification, reduced autonomy of portable systems, and decrease of overall yield. Low power dissipation during test application is becoming increasingly important in todays VLSI systems design and is a major goal in the future development of VLSI design.

### 1.1 The challenge to test

Modern chip design has greatly advanced with recent silicon manufacturing technology improvements that escalate transistor counts, increasing a chips complexity while maintaining its size. This phenomenon will continue, resulting in at least 10 of todays microprocessors fitting onto a single chip by 2005. Consequently, design and test of complex digital circuits imposes extreme challenges to current tools and methodologies. VLSI circuit designers are excited by the prospect of addressing these challenges efficiently, but these challenges are becoming increasingly hard to overcome. Test currently ranks among the most expensive and problematic aspects in a circuit design cycle, revealing the ceaseless need for innovative, test-related solutions. As a result, researchers have developed several techniques that enhance a designs testability through DFT modifications and improve the test generation and application processes. Traditionally, test engineers evaluated these techniques according to various parameters: area overhead, fault coverage, test application time, test development effort, and so forth. But now, the recent development of complex, highperformance, low-power devices implemented in deep-submicron technologies creates a new class of more sophisticated electronic products, such as laptops, cellular telephones, audio- and video-based multimedia products, energyefficient desktops, and so forth. This new class of systems makes power management a critical parameter that test engineers cannot ignore during test development. Test or DFT engineers find their main motivation in considering power consumption during test in a circuits consumption of more power in test mode than during normal operation. IT IS shown that the test power (the power consumed during test) could be twice as high as the power consumed during the normal mode. Several reasons cause this increased power usage. First, test efficiency correlates with toggle rate; therefore, in the test mode the switching activity of all nodes is often several times higher than during normal operation. Second, test engineers use parallel testing in SoCs to reduce the test application time, which might result in excessive energy and power dissipation. Third, the DFT circuitry designed to reduce the test complexity is often idle during normal operation but might be intensively used in the test mode. Fourth, successive functional input vectors applied to a given circuit during system mode have a significant correlation. In contrast, the correlation between consecutive test patterns can be low. For example, in a signal-processing circuit for speech recognition, the input vectors behave predictably, with the least-significant bits more likely to change than the most-significant bits. Similarly, in high-speed circuits that process digital audio and video signals, the inputs to most of those modules change relatively slowly. In fact, designers of low-power circuits take advantage of this consistent behavior

#### CHAPTER 1. INTRODUCTION

when they determine a circuits thermal and electrical limits, and system packaging requirements. In contrast, there is no definite correlation between the successive test patterns generated by an automatic test-pattern generator for external testing or the patterns produced by a linear feedback shift register (LFSR) for built-in selftest (BIST). This lack of correlation can result in significantly greater switching activity in the circuit during test than during normal operation. Because power dissipation in CMOS circuits is proportional to switching activity, tests excessive switching activity can cause catastrophic problems, as detailed later. Although academic research on low-power design remains nearly independent of that for test, industrial practice requires ad hoc solutions for considering power consumption during test application[7]. Practiced solutions include

1. oversizing power supply, package, and cooling to withstand the increased current during testing (test engineers insert breaks into the test process to avoid hot spots);

- 2. testing with reduced operating frequency; and

- 3. system-under-test partitioning and appropriate test planning.

The first solution increases both hardware costs and test time. Although the second proposal uses less hardware, the reduced frequency increases test time and might lead to a loss of defect coverage because the reduced frequency can mask dynamic faults. Moreover, this solution reduces power consumption but lengthens test time, so it does not reduce the total energy consumed during test. The third solution of test partitioning and test planning detects dynamic faults, but increases hardware costs and test time. To provide an adequate response to these industrial needs, various researchers have proposed solutions for power problems encountered during test. I classify these solutions into those applicable for external testing and the qualities of power under test, as defined in the Terminology sidebar (next page) and the next two sections.

## Chapter 2

## Literature Survey

To provide an adequate response to the industrial needs, various researchers have proposed solutions for power problems encountered during test. These solutions are classified into those applicable for external testing and those applicable for BIST. But first, test engineers and designers need to understand the qualities of power under test, as defined in the Terminology.

### 2.1 Terminology

As discussed earlier, one of the current concerns, which may turn into a major engineering problem in the future of SOC development, is test power. These concerns involve energy, average power, peak power, instantaneous power and thermal overload. Below are some definitions of these parameter. Energy: the total switching activity generated during test application. Energy has impact on the battery lifetime during power up or periodic self-test of battery operated devices. Average Power: the total distribution of power over a time period, which is generally the amount of power consumed during the application of a test. The average power is given by the ratio between the energy and the test time. Elevated average power adds to the thermal load that must be vented away from the device under test. It may cause structural damage to the silicon (hot spots), to bonding wires or to the package. Peak Power: the highest value of power at any given instant. The peak power determines the thermal and electrical limits of components and the system packaging requirements. If the peak power exceeds a certain limit, the correct functioning of the entire circuit is no longer guaranteed. - In fact, the time window for the definition of the peak power is related to the thermal capacity of the chip, and forcing this window to one clock period is sometimes just a simplifying assumption. For example, Test and the circuit has a peak power consumption during only one cycle but it has power consumption within the limit of thermal capacity of the chip for all other cycles, the circuit will not be damaged because the energy consumed, which corresponds to the peak power consumption times one cycle, will not be enough to elevate chip temperature over the limit of thermal capacity of the chip (unless the peak power consumption is far higher than normal power consumption). In order to damage the chip, high (not only highest) power consumption should last for several cycles to consume enough energy that can elevate chip temperature over the limit [6].

### 2.2 Energy and Power Modelling

Power consumption in CMOS circuits can be classified into static and dynamic. Static power dissipation is due to leakage current or other current drawn continuously from the power supply. Dynamic dissipation is due to (i) short circuit current and (ii) charging and discharging of load capacitance during output switching.

For the current CMOS technology, dynamic power is the dominant source of power consumption, although this may change for future developments of high scaled integration. The average energy consumed at node *i* per switching is 1/2CiV<sup>2</sup>DD where Ci is the equivalent output capacitance and VDD the power supply voltage. Therefore, a good approximation of the energy consumed in a period is 1/2CisiV<sup>2</sup><sub>D</sub>D, where si is the number of switching during the period. Nodes connected to more than one gate are nodes with higher parasitic capacitance. Based on this fact, and in a first approximation, capacitance Ci, is assumed to be proportional to the fanout of the node Fi. Therefore, an estimation of the energy Ei consumed at node i during one clock period is:

$$E_i = \frac{1}{2} s_i \cdot F_i \cdot C_0 \cdot V_{DD}^2 \tag{2.1}$$

where  $C_0$  is the minimum size parasitic capacitance of the circuit. According to this expression, the estimation of the energy consumption at the logic level requires the calculation of the fanout  $F_i$  and the number of switching on node i,  $s_i$ . The fanout of the nodes is defined by circuit topology, and the switching can be estimated by a logic simulator (note that in a CMOS circuit, the number of switching is calculated from the moment the input vector is changed until the moment the internal nodes reach the new stable state, including the hazard switching). The product  $s_i F_i$  is named Weighted Switching Activity (WSA) of node *i* and represents the only variable part in the energy consumed at node *i* during test application. According to the above formulation, the energy consumed in the circuit after application of a pair of successive input vectors ( $V_{k-1}$ ,  $V_k$ ) can be expressed by:

$$E_{V_K} = \frac{1}{2} \cdot C_0 \cdot V_{DD}^2 \sum_i s(i,k) \cdot F_i$$

(2.2)

where *i* ranges all the nodes of the circuits and s(i,k) number of switching provoked, by  $V_k$  at node *i*. Consider now a pseudo-random test sequence of Lendthtest, the test length required to achieve the targeted fault coverage, the total energy consumed in the circuit during application of the complete test sequence is:

$$E_{total} = \frac{1}{2} \cdot C_0 \cdot V_{DD}^2 \cdot \sum_k \cdot \sum_i s(i,k) \cdot F_i$$

(2.3)

Let us denote the clock period. as T. By definition, the instantaneous power is the power consumed during one clock period. Therefore we can express the instantaneous power consumed in the circuit after application of vectors  $(V_{k-1}, V_k)$

as  $P_{inst}(V_k) = E_{vk}/T$  The peak power consumption corresponds to the maximum of

the instantaneous power consumed during the test session. It therefore corresponds to the highest energy consumed during one clock period, divided by T. More formally, it can be expressed by:

$$P_{peak} = max_k[P_{inst}(V_k)] = \frac{max_k(E_{vk})}{T}$$

(2.4)

Finally, the average power consumed during the test session is the total energy divided by the test time, and is given as follows:

$$P_{ave} = \frac{E_{total}}{\left[\left(Length_{test}\right).T\right]} \tag{2.5}$$

According to the above expressions of the power and energy consumption, and assuming a given CMOS technology and supply voltage for the circuit design, the number of switching, of a node i in the circuit is the only parameter that has impact on both the energy, the peak power and the average power consumption. Similarly, the clock frequency used during testing has impact on both the peak power and the average power. Finally, the test length the number of test patterns applied to the CUT, has impact only on the total energy consumption. Consequently, when deriving a solution for power and/or energy minimization during test, a designer or a test engineer has to have these relationships in mind [2].

## 2.3 Low Power External Testing Techniques

Various techniques described in literature to ensure non destructive external testing of an SoC using ATE are categorized in following subsections.

#### 2.3.1 Low Power ATPG Algorithm

The basic goal of automatic test pattern generation (ATPG) was to decide the test pattern for given design under Test (DUT) which gives maximum fault coverage. The current research in this field focuses on ATPG algorithm which not only gives maximum fault coverage but also ensures the maximum fault coverage at lowest possible power dissipation. In this category first of all Podem algorithm proposed by Wang and Gupta and the method of exploiting the redundancy by fault dropping proposed by Corno et al. has been covered in previous survey paper by P.Girard [2]. Few other methods are is also researched in this area. Polian I. et al [32]. propose a heuristic method to generate test sequences which create worst-case power drop by accumulating the high and low-frequency effects. The generated patterns need to be sequential even for scan designs. They employ a dynamically constrained version of the classical D-algorithm for test generation, i.e., the algorithm generates new constraints on-the-fly depending on previous assignments. In an another approach Ho Fai Ko, Nicolici N [14] suggested that scan chain division has been successfully used to control shift power by enabling mutually exclusive flip-flops at different times during the scan cycle. However, to control capture power without losing transition fault coverage during at-speed scan test, the existing automatic test pattern generation (ATPG) flows need to be modified. He presented a novel scan chain division algorithm that analyzes the signal dependencies and creates the circuit partitions such that both shift and capture power can be reduced when using the existing ATPG flows. Whereas Sying-Jyan Wang et al. [41] present a low capture power ATPG and a power-aware test compaction method. Two goals are achieved by the proposed ATPG. (1) The growth of test pattern count is lower than the detection number n. (2) The peak power becomes smaller as the detection number n increases. The test compaction algorithm further reduces the number of test patterns as well as the average capture power.

#### 2.3.2 Ordering Techniques

The researches have widely explored the test vector reordering techniques to reduce the switching power. The earlier method based on Hamming distance based reordering proposed by P Girard and Debholkar are described in survey paper [27]. Girard's approach of vector ordering is enhanced by Paramasivam K, Gunavathi K, Sathishkumar P They have shown that the switching activity can be reduced up to 35 %[31]. In another method Roy S, Sen Gupta I, Pal A [34] proposed an AI-based approach to order the test vectors in an optimal manner to minimize switching activity during testing.

#### 2.3.3 Input Control

Here the idea is to identify an input control pattern such that by applying the pattern to the primary inputs of the circuit during the scan operation, the switching activity in the combinational part can be minimized or even eliminated. Huang and Lee's basic idea of input control technique with existing vector- or latch-ordering techniques that reduces the power consumption has been covered in previous survey paper by P. Girard [27]. In the same area ElShoukry. M et al.[9] presented a technique of gating partial set of scan cells. The subset of scan cells is selected to give maximum reduction in test power within a given area constraint. An alternate formulation of the problem is to treat maximum permitted test power and area overhead as constraints and achieve a test power that is within these limits using the fewest number of gated scan cells, thereby leading to least impact in area overhead. The area overhead is predictable and closely corresponds to the average power reduction.

#### 2.3.4 Vector Compaction and Data Compression

ATPG generated uncompacted test data contains a large number of don't care bits. There are number of test data compression techniques which explores the don't care filling options to optimize the compression of test data. The next generation compression scheme does not only aims to maximum compression but also explores the don't care bit filling to give minimum switching activity and hence power reduction. Static compaction techniques to control scan vector power dissipation proposed

by R. Sankaralingam et al. and a technique of Combining Low-Power Scan Testing and Test Data Compression for System-on-a-Chip proposed by A. Chandra and K. Chakrabarty has been covered in previous survey paper by P Girard [27]. Few other methods are also suggested after that, for Vector Compaction which are based on Don't care filling. Among them Sying-Jyan Wang et al. [40] proposed an automatic test pattern generation (ATPG) scheme for low power launch-off-capture (LOC) transition test. Two techniques are explored in the proposed ATPG. A bidirectional X-filling and vector replacement scheme. Whereas Kundu S, Chattopadhyay S [19] have used a Genetic Algorithm based heuristic to fill the don't cares. Their approach produces an average percentage improvement in dynamic power and leakage power over 0- fill, 1-fill, and Minimum transition fill (MT-fill) algorithms for don't care filling. In an another approach Z. Chen et al. [8] proposed segment-based X-filling to reduce test power and keep the defect coverage. The scan chain configuration tries to cluster the scan flip-flops with common successors into one scan chain, in order to distribute the specified bits per pattern over a minimum number of chains. Based on the operation of a state machine, Jing-Ling Yang and Qiang Xu [17] elucidates a comprehensive frame for probability-based primary-input dominated X-filling methods to minimize the total weighted switching activity (WSA) during the scan capture operation. Experimental results demonstrate that the proposed approach significantly reduces both average and peak WSAs. Whereas Tapas M and Santanu C [22] describe the effect of don't care filling of the patterns generated via automated test pattern generators, to make the patterns consume lesser power. It presents a trade-off in the dynamic and static power consumption. The effect is expected to be more prominent for technologies beyond 100 nm.

#### 2.3.5 Scan Chain Transformation

Here the scan architecture is designed in such a way that it maintains the test time, enables reuse of the conventional scan architecture's test patterns, and avoids decreasing the scan clock rate. Previously L. Whetsel's approach of , Adapting Scan Architectures for Low Power Operation and K.J.Lee's approach of Peak-Power Reduction for Multiple-Scan Circuits during Test Application has been covered in previous survey paper by P Girard [27]. In addition to that Sinanoglu, O, Orailoglu A [37] proposed a scan chain modification methodology that transforms the stimuli to be inserted to the scan chain through logic gate insertion between scan cells, reducing scan chain transitions . Based on this analysis, they developed an algorithms for transforming a set of test vectors into power optimal test stimuli through cost-effective scan chain modifications.

#### 2.3.6 Clock Scheme Modification

Giving a clock to a whole circuit will give some unnecessary transition, which affects on power and energy consumption. Here the techniques are described which manages the clock distribution in such a way that overall it consumes less power. Previously Pouya and Crouch's ideas on optimization trade-offs for vector volume and test power , Sankaralingam et al approach on reducing power dissipation during test using Scan chain disable, Bonhomme et al's approach based on a gated clock scheme for low power scan testing of logic ics or embedded cores have are covered in previous survey paper by P Girard [27]. It is found that many STUMPS architectures found in current chip designs allow disabling of individual scan chains for debug and diagnosis, such feature can be used for reducing the power consumption during test. Here Imhof M.E et al. [16] presented an automated generation of a test plan that keeps fault coverage as well as test time, while significantly reducing the amount of wasted energy by disabling of individual scan chains for debug and diagnosis .

### 2.4 Low Power BIST Techniques

Various authors reported on techniques to cope with power problems during BIST. In the following, these techniques for low power BIST are presented.

#### 2.4.1 Low Power Test Pattern Generators

In this category the BIST architecture is designed in such a way that it decreases the circuits overall activity so that power consumption reduces significantly. Previously BIST strategy, called dual-speed LFSR was suggested by Wang and Gupta, based on two different speed LFSRs. Also Corno et al proposed an approach on low power BIST via non-linear hybrid cellular automata. Then a modified clock scheme for a low power BIST test pattern generator was proposed by P Girard, In addition to that Zhang et al suggested a POWERTEST tool, which is a Tool for Energy Conscious Weighted Random Pattern Testing. Whereas Wang and Gupta proposed LT-RTPG: A New Test-Per-Scan BIST TPG for Low Heat Dissipation. These all have been covered in previous survey paper by P Girard [27]. After that Ahmed N et al. [2]. presented a new low power test pattern generator using a linear feedback shift register (LFSR), called LP-TPG, which inserts intermediate patterns between the random patterns to reduce the transitional activities of primary inputs which eventually reduces the switching activities inside the circuit under test, and hence, power consumption. Hirevren and Levent [18] proposed a polynomial-time algorithm that converts the test pattern generation problem into combinatorial problem called Minimum Set Covering. Solutions to that give the low-power design topology for the test pattern sequence. Youbean K et al. [46] presents a new low power BIST TPG scheme. It uses a transition monitoring window (TMW) that comprised of a TMW block and a MUX. The proposed technique represses transitions of patterns using the k-value which is a standard that is obtained from the distribution of TMW to observe over transitive patterns causing high power dissipation in a scan chain. K.Gunavathil et al. [11] proposed TPG based on Read Only Memory (ROM) which is carefully designed to store the test vectors with minimum area over the conventional ROM. This reduces the number of CMOS transistors significantly when compared to that of LFSR/Counter TPG. Bin Z. et al [5] proposed approach to reconfigure the CUT's partial-acting-inputs into a short ring counter (RC), and keep the CUT's

partial-freezing-inputs unchanged during testing. S.Wang [44] presents a low hardware overhead test pattern generator (TPG) for scan-based built-in self-test (BIST) that can reduce switching activity in circuits under test (CUTs) during BIST and also achieve very high fault coverage with reasonable lengths of test sequences. The proposed BIST TPG decreases transitions that occur at scan inputs during scan shift operations and hence reduces switching activity in the CUT. M.Nourani et al. [26] proposed low-transition linear feedback shift register (LT-LFSR) technique. Transitions are reduced in two dimensions: 1) between consecutive patterns and 2.) between consecutive bits. The proposed architecture increases the correlation among the patterns generated by LT-LFSR with negligible impact on test length. Bei Cao et al. [43] presented an efficient algorithm to synthesize a built-in TPG from low power deterministic test patterns without inserting any redundancy test vectors. The structure of TPG is based on the non-uniform cellular automata (CA). And the algorithm is based on the nearest neighborhood model, which can find an optimal non-uniform CA topology to generate given low power test patterns. Li-gang Hou et al. [10] proposed a low power dynamic LFSR (LDLFSR) circuit which achieves comparable performance with less power consumption. Typical LFSR, a DFLSR[I], a LDLFSR are compared on randomness property and inviolability property. Multi-layer perceptron neural networks are used to test these LFSRs' inviolability property. H.-T. Lin J.C.-M. Li. [20] presented ATPG technique, which simultaneously reduces capture and shift power during scan testing. This ATPG performs power reduction during dynamic test compaction so the test length overhead is very small. This method implements several novel techniques, such as parity back trace, confined propagation, dynamic controllability and post-fill test regeneration T.

#### 2.4.2 LFSR Tunning

Here this category mainly emphasized on reduction energy consumption without modifying the fault coverage. Various BIST techniques are described here. Earlier Girard et al. address the problem of energy minimization during test application for BIST enabled circuits[27]. In a random testing environment, a significant amount of energy is wasted in the LFSR and in the CUT by useless patterns that do not contribute to fault dropping. In this work, a new built-in self-test scheme for scan-based circuits is proposed by Bhattacherya B.B. et al. [3] for reducing such energy consumption. A mapping logic is designed which modifies the state transitions of the LFSR such that only the useful vectors are generated according to a desired sequence. Experimental results on ISCAS-89 benchmark circuits reveal a significant amount of energy savings in the LFSR during random testing.

#### 2.4.3 Vector Filtering BIST

Here main idea is to filter out some non detecting sequences so that over all switching can be reduced and hence power consumption. Previously Girard et al. proposed a test-vector-inhibiting technique to filter out some non detecting subsequences of a pseudorandom test set generated by an LFSR. His work was extended by Manich et al. by the filtering action to all the nondetecting subsequences. The authors use a decoding logic to store the first and last vectors of the nondetecting subsequences to be filtered and the same idea was implemented by Gerstendrfer and Wunderlich. These authors combine a pattern-filtering technique with Hertwig and Wunderlich's technique to avoid scan-path activity during scan shifting. These all have been covered in previous survey paper by P Girard [27]. After that S. Hatami et al. [13] proposed a scan cell architecture that decreases power consumption and the total consumed energy. In the method which is based on the data compression, the test vector set is divided into two repeated and unrepeated partitions. The repeated part, which is common among some of the vectors, is not changed during the new scan path where new test vector will be filled. As a result, the test vector is applied to the circuit under test in a fewer number of clock cycle, leading to a lower switching activity in the scan-path during test mode.

#### 2.4.4 Circuit Partitioning

Main goal here is to partition the circuit in to sub circuit so that parallel testing can be achieved . Girard et al. propose a novel low-power BIST strategy based on circuit partitioning. This strategy partitions the original circuit into two structural sub circuits so that two different BIST sessions can successively test each sub circuit. This idea has been covered in previous survey paper by P Girard [27]. To address the power in the scan chain, Swarup B et al [4] propose an efficient scan partitioning technique that reduces both average and peak power in the scan chain during shift and functional cycles. Whereas Qiang Xu et al. [33] proposed a novel low-power virtual test partitioning technique where faults in the glue logic between subcircuits can be detected by patterns with low power dissipation that are applied at the entire circuit level, while the patterns with high power dissipation can be applied within a partitioned subcircuit without loss of fault coverage. Experimental results show that the proposed technique is very effective in reducing test power.

#### 2.4.5 Low Power RAM Testing

Various RAM trasition reduction technique by reordering read and write access are described for low power consumption. Cheung and Gupta propose a methodology for low-power test of RAMs. The authors base their strategy on RAM transition reduction by reordering the read and write accesses and the address counting scheme. These measures decrease the energy consumption and keep test time the same, so they also minimize the average power[2]. The idea has been covered in previous survey paper by P Girard [27] A row bank-based precharge technique based on the divided wordline (DWL) architecture is proposed by Shyue-Kung Lu et al. [21] for lowpower testing of embedded SRAMs. In low-power test mode, instead of precharging the entire memory array, only the current accessed row bank is precharged. This will result in significant power saving for the precharge circuitry. With the ever increasing number of memories embedded in a system-on-chip (SoC), power dissipation due to test has become a serious concern. Here Yuejian Wu et al. [47] proposed a novel low power memory BIST. Its effectiveness is evaluated on memories in 130 and 90 nm technologies. A significant power reduction can be achieved with virtually zero hardware overhead.

## 2.5 Low Power DFT Techniques

Apart from internal and external techniques here DFT techniques are described for low power testing. Here main goal is to reduce switching activity by adding some hardware during test. Xiaoming Yu and Miron Abramovici [45] introduce two designfor-testability (DFT) techniques based on clock partitioning and clock freezing to ease the test generation process for sequential circuits. In the first DFT technique, a circuit is mapped into overlapping pipelines by selectively freezing different sets of registers so that all feedback loops are temporarily cut. An opportunistic algorithm takes advantage of the pipeline structures and detects most faults using combinational techniques. This technique is feasible to circuits with no or only a few self-loops. In the second DFT technique, they use selective clock freezing to temporarily cut only the global feedback loops. These DFT techniques do not introduce any delay penalty into the data path, have small area overhead, allow for at-speed application of tests, and have low power consumption. Min-Hao Chiu Li, J.C.-M [23] presents a Jump scan technique (or J-scan) for low power testing. The J-scan shifts two bits of scan data per clock cycle so the scan clock frequency is halved without increasing the test time. The experimental data show that the proposed technique effectively reduces the test power by two thirds compared with the traditional MUX scan. The presented technique requires very few changes in the existing MUX-scan design for testability methodology and needs no extra computation. The penalties are area overhead and speed degradation.

## Chapter 3

# **Reordering Techniques**

Test power has become a serious problem with switching activity as well as in scanbased testing. It can lead to prohibitive test power in the process of test application. During the process of scan shifting, the states of the flip-flops are changing continually, which causes excessive switching activities. Test vector reordering for reducing switching power is one of the general goal of low power testing. Here two techniques Hamming distance based and AI-based approach is proposed to order the test vectors in an optimal manner to minimize switching activity during testing.

## 3.1 Hamming Distance based Reordering technique

Very Large Scale Integration (VLSI) design plays a significant role in the fabrication of modern Integrated Circuits(ICs) with smaller in size and with more features for any electronics systems. Energy consumption and power dissipation are the major concern in the VLSI design. Several factors have contributed to this trend. With the advent of portable devices, for example low energy consumption has become one of the major design goals in order to prolong battery life. Moreover the amount of energy a circuit consumes is directly reflected in its heat dissipation, however requires expensive packaging and cooling techniques which in turn increases system cost [1]. In addition, as power consumption increases, circuit reliability gets affected adversely due to electro-migration. This is applicable for both Design power and testing power. Testing is a process of checking the fabricated ICs for any incorrect behavior due to faults like logical fault, delay fault, fabrication faults<sup>[2]</sup>, etc. Testing is done by generating and applying a set of binary vectors called test vectors to the input of the circuit. Fault is detected by verifying the output for the given test vector with stored responses. Testing has to be done for all possible faults in the circuit. Hence more test vectors may be required to test all the faults in complete circuit. Single test vector may detect more than one fault and more than one test vectors can be generated for a single fault. A set of test vectors<sup>[4]</sup> must be generated such that more faults are covered with minimum number of test vectors. Testing is not only done after the fabrication of ICs but also required when ICs are in usage. This is called periodic testing which is required for all type of systems like PC, Laptop, cell phones etc. The main problem under testing environment is that it results in considerably higher circuit activity rate compared to normal mode operation, hence causing above normal power dissipation. However if test vector sets are not optimized for power[10], low power circuits dissipate two fold power under test as they do at normal operating condition[2]. When the circuit is tested with pseudo-random patterns, consecutive input test vectors are statistically independent which results in increased switching activity in the circuit under test. Since in CMOS circuits energy is primarily consumed by signal transition, the average power consumption during testing is significantly higher than normal mode of operation. The Relationship between hamming distance [6] and the average power of a circuit plays a significant role to optimize the test power. In order to optimize, the hamming distance between successive test vectors is used to arrange the test vectors in specific order so that Total Hamming Distance(THD) is minimum. A test vector set with least hamming distance is obtained by optimization technique. The test power obtained by applying test patterns in the optimal order is regarded as the optimized test power. In order to guarantee the proper operating conditions during test, the total power consumption must not exceed the maximum power allowance for the circuit under test |2|. Another

problem is that even if the average power dissipation over a sequence of test vectors is small, the peak (or instantaneous) power dissipation may be sufficiently high to destroy the CUT. In practice, destruction really occurs when the instantaneous power exceeds the maximum power allowance during several successive test vectors. For this reason, it is essential to take care of both average and peak power dissipation during test application.

Many low power design techniques have been proposed at all levels of the design hierarchy. However, all these techniques focus on low power dissipation during system mode or standby mode, and during test mode. The simplest way to ensure nondestructive testing of a CUT is to use ordering of test vectors, which causes switching activity that is comparable to that during normal circuit operation. Several categories of techniques can be found in the literature related to the low power testing. The first category consists of ATPG (Automatic Test Pattern Generator) techniques[5], in which new ATPGs are proposed with the intent of generating test patterns that can reduce the power dissipated during test application in addition to the normal ATPG objectives. The second category consists of ordering techniques in which the switching activity is reduced by modifying the order in which test vectors of a given test sequence are applied to the CUT. The paper [14] discussed about two methods used for reordering of test vectors in order to reduce the dynamic power dissipation during testing of combinational circuits. Two search methods 2-opt heuristic and a genetic algorithm based approach have applied and results obtained for combinational circuits. These techniques can be applied during external testing or deterministic BIST (Built-In Self Test). In this paper we present a novel method, which aims at minimizing switching activity during testing of combinational circuit. The test vectors are reordered based on the hamming distance between successive test vectors. Graph theory based reordering algorithm is proposed to solve the problem. Since this problem is NP complete, the algorithm is developed through heuristic approach which gives better optimum solution for such problems. Random heuristics are used in previous approaches that may or may not give better solution. In this proposed

algorithm structured heuristic is used to obtain better results than random heuristics.

#### 3.1.1 Problem formulation

The power dissipation during testing [2] is minimized by reducing the number of transition in the circuit. This is achieved by reducing the hamming distance between successive test vectors. Usually test vectors are in random and hence it is necessary to rearrange the order of occurrence of test vectors so that the hamming distance between successive test vectors is minimum. In general the total switching power in the whole circuit is proportional to the hamming distance of input test vectors. Therefore the reordered test vector set with minimum hamming distance is used for testing the CUT to reduce the switching power. The problem of minimizing switching power is solved by graph theory using Hamiltonian path [3] technique. Graph G(V,E)is defined with V nodes and E edges. The problem is formulated by considering the test vector as node and hamming distance between them as edge cost of the graph. Here the Hamiltonian path is a path with all nodes and minimum total edge cost. Graph Theory based Reordering algorithm [12] is used to construct the Hamiltonian path, which is resultant reordered test vector set whose total hamming distance is minimum. Now the path developed by the algorithm is reordered test vector sequence which offers less number of transitions at the input which in turn results in reduced power dissipation in the circuit under test during testing [3]. Heuristic approach is used in the algorithm to find more suboptimal sequences.

#### 3.1.2 Total Hamming Distance(THD)

Total hamming distance is defined as Sum of hamming distance between successive test vectors in the sequence.

Let hamming distance d[ti, tj] be the total number of changes between i thth and j test vector. The Total Hamming Distance(THD) for the whole test vector set is calculated by the following relation.

$$THD = \sum_{i=1}^{N} d[t_i, t_{i+1}]$$

(3.1)

where n represents total number of test vectors in the whole set. The overall procedure to minimize the switching activity during testing is as follows.

- a. Consider a digital circuit with p inputs and q outputs.

- b. Generate all the test vectors to detect all the single stuck at faults[4] of the circuit. Let the number of test vectors be n.

- c. Find the hamming distance between each and every test vector and load the same in array hd of size n x n. Let hd[i][j] be the array elements which gives hamming distance between  $i^{th}$  and  $j^{th}$  test vectors.

- d. Apply reordering algorithm to find the reordered test vector sequence with minimum total hamming distance.

- e. Perform fault simulation[4] with reordered test vector set which gives minimum number of transition and hence less power dissipation.

- f. Since Heuristic based algorithm generates more sub-optional sequences, select the best sequence with least total switch activity.

The reordering algorithm used in step d is discussed in the next sub-section.

#### 3.1.3 Reordering Algorithm:

The various parameters used in the algorithms are as follows: t1, t2,....tn be n test vectors with m bits each.  $T = \{1, 2, ...., k, ..., n\}$  where k represents  $k^{th}$  position in the vector set generated by ATPG.

R is a set to store ordered test vector sequence.

Q is a set to store T-R.

Step 1: Select a test vector x such that swa\_init[x] is minimum in the array swa\_init[]. Add x to set R.

Step 2: Select a test vector y such that  $hd[x][y_{min}]$  is minimum in the array.

Step 3: Add  $y_{min}$  to R; Q $\leftarrow$ T-R;  $x_{min} \leftarrow y_{min}$ .

Step 4: From the array  $hd[x_{min}][j]$  when j varies as in Q, find y so that  $hd[x][y_{min}]$  is the smallest value. Go to step 3.

Step 5: In the step 4, if  $hd[x_{min}][j]$  has more than one smallest value, then such number of reordered sequence will be generated for every  $x_{min}$ . These sequences are called as sub-optimal sequences.

Finally the set R will have reordered test vector sequence with minimum hamming distance which results in minimum switching activity during testing.

| Test vector | No.            |

|-------------|----------------|

| set (n=7)   |                |

| 000         | t <sub>1</sub> |

| 111         | t <sub>2</sub> |

| 001         | t3             |

| 010         | t <sub>4</sub> |

| 101         | t <sub>5</sub> |

| 011         | t <sub>6</sub> |

| 100         | t <sub>7</sub> |

| $\int 0$    | 3 | 1 | 1 | 2 | 2 | 1  |

|-------------|---|---|---|---|---|----|

| 3           | 0 | 2 | 2 | 1 | 1 | 2  |

| 1           | 2 | 0 | 2 | 2 | 1 | 2  |

| 1           | 2 | 2 | 0 | 3 | 1 | 2  |

| 2           | 1 | 2 | 3 | 0 | 2 | 1  |

| 2           | 1 | 1 | 1 | 2 | 0 | 3  |

| $\lfloor 1$ | 2 | 2 | 2 | 1 | 3 | ر٥ |

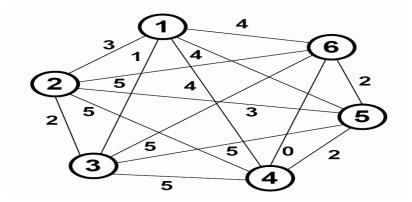

Figure 3.1: a.) Test Vectors for Full adder circuit b.) Switching matrix hd[n][n]

The above procedure is illustrated with simple full adder circuit with 3 inputs and 2 outputs. The test vector set that used to detect the entire single stuck at faults is given in Table I. The set consists of 7 vectors with total hamming distance as 15. The vectors are represented by the order of occurrence for the sake of convenience. The hamming distance array hd[][] of order n X n is constructed. This is given as in fig 3.1. It is known that the number of bit changes between t1 and t2 test vectors

in the table is three. Similarly between t2 and t3 test vectors is two. This is shown in the array as hd[1][2]=3 and hd[2][3]=2 respectively. The hamming distance array hd[][] is developed in this method.

On application of reordering algorithm to this matrix hd[][], the reordered test vectors are generated with minimum hamming distance.

The solution and the THD are given as follows:

Unordered sequence : t1 t2 t3 t4 t5 t6-t7 THD : 15

Ordered sequence : t3 t1 t4 t6 t2 t5 t7 THD : 6

The total hamming distance for the resultant ordered sequence is 6 which shows that 60 % of total hamming distance is reduced when compared with that of unordered sequence. This reduces the switching activity and hence the power dissipation in the circuit.

## 3.2 Artificial Intelligence approach

#### 3.2.1 Brief overview

Advancements in semiconductor fabrication technology has helped the design engineers to accommodate more number of transistors in a VLSI chip. With the proliferation of mobile battery-powered devices, reduction of power in the embedded VLSI chips has become an active area of research. During the last decade, power reduction techniques have been proposed at all levels of the design hierarchy - from system to device levels. For the development of complex, high performance, low power devices implemented in deep submicron technology, power management is a critical parameter and it cannot be ignored even during testing. With the increase in the density of the chips, the problem of testing has also increased manifold.

A related problem is to achieve power reduction during the actual testing of a chip [25]. Power consumption in test mode is considerably higher than the normal functional mode of a chip. The reason is that test patterns cause as many nodes switching as possible, while a power saving system mode only activates a few modules at a time. Thus, during testing switching activity in all the internal lines of a chip is often several times higher than during normal operation. Sometimes parallel testing is used in SoCs to reduce test application time, which results in excessive power dissipation. Again, successive functional input vectors applied to a given circuit during system mode have a significant correlation, while the correlation between consecutive test patterns can be very low. Usually, there is no definite correlation between the successive test patterns generated by an ATPG (for external testing) or by an LFSR (for BIST) for testing of a circuit. This can cause significantly larger switching activity in the circuit during testing than that during its normal operation. Abnormal power consumption during testing leads to adverse effects on the chip and the testing process such as, (a) this may give rise to severe hazards to the circuit reliability and lead to long or shortterm malfunction, (b) it can cause chip destruction due to excessive heat in absence of proper heat dissipation mechanism, (c) it can increase the packaging and cooling costs, (d) it can cause the chip to falsely fail the test due to noise problems such as, IR and Ldi/ dt drops, which may be a source of yield loss and increase in production cost, (e) it may make it difficult to obtain a carefully tested bare die to be used in multichip modules (MCM) or what is called the Known Good Die problem (KGD) and (f) it can dramatically shorten the battery life when on-line testing is considered. For all these reasons, various techniques have been proposed to reduce the impact of high power consumption during test application. Low power dissipation during test application is becoming an equally important figure of merit in today's VLSI circuits design with BIST and is expected to become one of the major objectives in the near future.

### 3.2.2 Prior Work

A survey on low power testing of VLSI circuits has been given in [27]. There are several techniques for low power testing of VLSI circuits such as, test vector reordering, scan chain ordering, power-constrained test scheduling, use of multiple scan chains, low power test pattern generation, vector compaction, etc. Test vector reordering is a very well-known technique to reduce dynamic power dissipation during combinational circuit testing through switching activity minimization in the circuit. Test vector reordering is an essential task in testing VLSI systems because it affects from two perspectives: power consumption and correlation among data used for test data compression. The problem of test vector reordering can be mapped into finding Hamiltonian cycle in a complete weighted graph, which is known to be NP-hard. So, there is no polynomial time solvable algorithm for the problem. Therefore, it is essential to find a good heuristic-based solution for the problem. Existing approaches have used several heuristics for solving this problem. In [19], the problem of test vector reordering has been mapped into finding the Hamiltonian path in a fully-connected weighted graph which is similar to the traveling salesman problem (TSP). As there exists no polynomial time algorithm for TSP, approximation methods of solution have been used. Solutions for three cases have been given: (i) reordering for maximal or minimal activity, (ii) reordering of test vectors with a desired circuit activity across the VLSI chip while achieving a high coverage for stuck-at faults, and (iii) reordering for localized switching activities to maximize it in one part and minimize at other part of the circuit. In another work [30], proposed greedy algorithm has guaranteed decrease in power consumption without modifying the initial fault coverage. A second technique based on Simulated Annealing (SA) has been proposed in which the greedy solution is used as initial solution and it shows a considerable average power reduction during test application. Here, only Hamming distance between test vectors has been used to avoid simulation of the circuit and providing a solution (an Hamiltonian path of minimum cost in the Hamming distance graph) in a short computation time. It has been shown that there is a correlation between the Hamming distance and the transition activity. But, if signal transitions in the internal line be considered, then obviously optimal solution can be found.

Another work [28] has also considered the Hamming distance minimization be-

tween adjacent vectors to reduce the dynamic power dissipation during testing. In [42], reduction of power dissipation during test application has been studied both for scan designs and for combinational circuits tested using built-in self-test (BIST). They have shown that heuristics with good performance bounds can be derived for combinational circuits tested using BIST and a post ATPG phase has been proposed for reducing power dissipation during test application in full-scan circuits and for pure combinational circuits. They have shown that scan-latch ordering along with test-vector reordering can give considerable improvement in power dissipation and considerable savings can be obtained by repeating some of the test vectors. In [12], an evaluation of different heuristic approaches has been done in terms of execution time and quality. Here, it has been shown that the Multi-Fragment heuristic performs better than Christofides and Lin-Kernighan heuristics in terms of time. It also outperforms the Christofides heuristic in terms of quality and achieves performance very close to Lin-Kernighan. They recommended reordering algorithms to use the Multi-Fragment heuristic for near-minimal ordered sets of vectors that result in both reduced power consumption and enhanced data compression ratio. Recently, some works have formulated test vector reordering problem as TSP and Genetic Algorithm (GA) has been used to generate low power test patterns.

Chattapadhyay and Choudhary have shown proposed a GA-based formulation to solve the problem of generating a test pattern set such that it has high fault coverage and low power consumption has been proposed in [2]. They have shown a method of selecting a subset of test vectors generated by an ATPG tool to reduce power dissipation by sacri?cing a small amount of fault coverage. In [1], authors have studied two well known search methods (2-opt heuristic and a GA-based approach) with reduction in fault coverage. They have also combined those two methods for power reduction.