Test Data Compression Techniques for IP Core Based SoC: Time, Power and Area Optimization

> A THESIS SUBMITTED TO NIRMA UNIVERSITY FOR THE DEGREE OF

# **Doctor of Philosophy**

IN TECHNOLOGY AND ENGINEERING

> BY Usha Sandeep Mehta

INSTITUTE OF TECHNOLOGY, NIRMA UNIVERSITY, SARKHEJ-GANDHINAGAR HIGHWAY, AHMEDABAD-382 481 GUJARAT, INDIA

May 2011

Test Data Compression Techniques for IP Core Based SoC: Time, Power and Area Optimization

A Thesis

Submitted for the Degree of

Doctor of Philosophy in

**Technology and Engineering**

By

Usha Sandeep Mehta

Under the guidance of

Dr. K. S. Dasgupta

Director, IIST, Thiruvananthapuram, Kerala

&

Dr. N. M. Devashrayee PG-VLSI Coordinator, Nirma University, Ahmedabad

DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING AHMEDABAD-382481 May 2011

### **CERTIFICATE**

This is to certify that Ms. **Usha Sandeep Mehta** is registered as a student under Registration No.**07EXTPHDE17** for Doctoral programme under the Faculty of Nirma University and have fulfilled the requirement of **R.PH.D 6.4** to attend the Department for the work and coursework (for 90 days) as required.

Dr. N. M. Devashrayee Name & Signature of Co-Guide

Dr. K. S. Dasgupta Name & Signature of Guide

### **CERTIFICATE**

This is to certify that I, **Usha Sandeep Mehta**, am registered as a student under Registration No. **07EXTPHDE017** for Doctoral programme under the Institute of Technology under the Nirma University. I have completed the research work and also the presynopsis seminar as prescribed under the regulation No. 3.5 for the Ph.D. study.

It is further certified that the work embodied in this thesis is original and contains the independent investigations carried out by me. The research is leading to **\*the discovery of** new facts / **techniques** / correlation of scientific facts already known.

\* (Please tick whichever is applicable)

Date :

Forwarded by guide :

Signature of the student

Guide

Co-Guide

| 5.0                   |                                                 |  |  |

|-----------------------|-------------------------------------------------|--|--|

| Remarks of Head of    | Remarks of Head of the Department (if any) :    |  |  |

| Date :                | Signature :                                     |  |  |

| Remarks of Dean Fa    | culty Concerned :                               |  |  |

| Date :                | Signature:                                      |  |  |

| Remarks of Dean Fa    | culty of Doctoral Studies & Research (if any) : |  |  |

| Date :                | Signature :                                     |  |  |

| To,                   |                                                 |  |  |

| The Executive Registr | ar                                              |  |  |

Nirma University

## **CERTIFICATE**

This is to certify that the contents of this thesis entitled **"Test Data Compression Techniques for IP Core Based SoC: Time, Power and Area Optimization"** is the original research work of **Ms. Usha Sandeep Mehta** carried out under my supervision.

I further certify that the work has not been submitted either partly or fully to any other university or body – in quest of a degree, diploma or any other kind of academic award.

Date : Place :

Name of Co-Guide: Full Designation: Name of Institute:

Dr. N. M. Devashrayee Co-ordinator, PG-VLSI Design Institute of Technology, Nirma University, Ahmedabad, Gujarat

Place :

Name of Guide: Full Designation: Name of Institute: Dr. K. S. Dasgupta Director, Indian Institute of Space Science and Technology, Thiruvananthapuram, Kerala

### Candidate's Statement

The work included in this thesis entitled **"Test Data Compression Techniques for IP Core Based SoC: Time, Power and Area Optimization"** is an independent investigation carried out by me under the guidance and supervision of **Dr. K. S. Dasgupta** and **Dr. N. M. Devashrayee**. In the thesis, references of the work done by others which have been used are cited at appropriate places.

I hereby declare that the work incorporated in the present thesis is original and has not been submitted to any other university or body – in quest of a degree, diploma or any other kind of academic award.

Date : Place :

> Name of Student: Usha Sandeep Mehta Reg. No.: 07EXTEPHDE017

#### **ACKNOWLEDGEMENTS**

No work is ever the outcome of efforts or talent of single individual. This work is no exception. Many teachers, friends, well-wishers have contributed to this thesis work directly or indirectly and made it possible for me to present it in its current shape. Although it is not possible for me to name and thank them all individually, I must specially mention some of the personalities and acknowledge my sincere indebtedness to them and preserve gratitude to many others in my heart.

First and foremost, I express my deep and sincere gratitude to my guide Dr. K. S. Dasgupta for all his guidance, support, inspiration and seemingly endless patience. I also direct a special gratitude to my co-guide Dr. N. M. Devashrayee. Together with Dr. Dasgupta, he made a great team of advisors and has provided excellent guidance in how to obtain and present research results.

I am deeply indebted to Prof. Virendra Singh and Dr. D. J. Shah who have taken a lots of pain for regularly evaluating my work and provide very precise inputs which made the progress of this research work very fast. My thanks are also due to Prof. Nur Touba for providing technical help.

I am also thankful to Dr Ketan Kotecha, Prof. A. S. Ranade, my faculty friends and project students at Nirma University for their inspiration, support, help and contributions.

Any thanks or regards can not be enough for my mother who is the first and foremost teacher of my life. I don't have enough words to describe the sacrifices of my father who made me able in all adverse conditions of his life. I dedicate this work to both of them. The credit goes to my children Riddhi-Vandeet and in-laws for their patience, support and encouragement. Last but not least, thank you Sandeep for all the love and support you give to me. Thank you for being you.

> - Usha Sandeep Mehta April 2011

#### ABSTRACT

To handle design complexity and short time-to-market, it is increasingly common to use modular design approach in SoC. Such IP cores with hidden architecture have further exaggerated the two burning issues for fabrication testing of SoC: the test cost and test power. The cost of test is strongly related to the increasing test-data volumes which lead to longer test application times and larger tester memory requirement. The solution to this is test data compression.

The increasing test power leads to system reliability issues. The dynamic power during scan operations plays a major role in overall test power. This dynamic scan power is directly related to the number of transitions during scan-in and scan-out. Here, the 'test data compression' and 'switching activity reduction' issues in context of 'hidden structure of IP cores' are addressed.

In this thesis, various test data compression techniques are surveyed and it was observed that for ATPG generated binary data which contains large number of don't care bits, 'run length code' and 'statistical code' based methods are most suitable in context of IP cores. Similarly, the switching activity reduction methods for external testing are suitable to IP cores for power reduction.

It was inferred that if the 'don't care bit filling' and 'reordering' techniques are used in synergy to pre-process the test data, the compression can be increased and test power can be reduced without much on-chip area overhead.

In this thesis, mostly all existing run-length and statistical code methods are implemented and analyzed for compression, power and area overhead.

Using the 'don't care bit filling' and 'reordering' concepts, the test data processing techniques are proposed to further increase compression and reduce test power. The proposed 'Run Based Don't Care Bit Filling', 'HDR-CBF-DV', '2-D Reordering' and 'WTR-CBF-DV' test data processing techniques are used to improve the run length based test data compression codes. The same way proposed 'FDBAF' test data processing technique improves the results for statistical codes. To improve the overall test application time, the 'Modified Selective Huffman code' is proposed. Its effectiveness in increasing compression and reducing test application time without any extra area overhead is proved mathematically and also demonstrated with large amount of simulation results.

# **TABLE OF CONTENTS**

| ACK  | NOWLE    | DGEMENTS                                    | i   |

|------|----------|---------------------------------------------|-----|

| ABS  | TRACT    |                                             | ii  |

| LIST | г ог та  | BLES                                        | vii |

| LIST | r of fic | GURES                                       | ix  |

| ABB  | REVIAT   | NONS                                        | xi  |

| 1.   | INTR     | ODUCTION                                    | 1   |

|      | 1.1      | Test Flow                                   | 2   |

|      | 1.2      | Test Cost                                   | 6   |

|      |          | 1.2.1 Test Time                             | 7   |

|      |          | 1.2.2 Test Data Volume                      | 7   |

|      |          | 1.2.3 Test Data Compression                 | 10  |

|      | 1.3      | Test Power                                  | 11  |

|      | 1.4      | Issues Related to IP Core SoC               | 12  |

|      | 1.5      | Objective                                   | 13  |

|      | 1.6      | Adopted Methodology                         | 14  |

|      | 1.7      | Thesis Organization                         | 15  |

| 2.   | LITEI    | RATURE SURVEY                               | 18  |

|      | 2.1      | Test Data Compression                       | 18  |

|      | 2.2      | Test Data Compression Methods               | 19  |

|      | 2.3      | Compression Methods for IP Cores            | 22  |

|      | 2.4      | Test Data Compression Environment           | 23  |

|      | 2.5      | Code Based Test Data Compression Methods    | 26  |

|      |          | 2.5.1 Statistical Code Based Methods        | 26  |

|      |          | 2.5.2 Run Length Code Based Methods         | 28  |

|      |          | 2.5.3 Dictionary Code Based Methods         | 30  |

|      |          | 2.5.4 Constructive Code Based Methods       | 31  |

|      | 2.6      | Code Based Methods for IP Cores             | 31  |

|      | 2.7      | Test Power                                  | 32  |

|      | 2.8      | Switching Activity Reduction Methods        | 37  |

|      |          | 2.8.1 SAR Techniques for Built-In-Self-Test | 37  |

|    |        | 2.8.2    | SAR Techniques for Design-For-Test             | 40       |

|----|--------|----------|------------------------------------------------|----------|

|    |        | 2.8.3    | SAR Techniques for External Testing            | 41       |

|    | 2.9    | SAR Te   | chniques for IP Cores                          | 41       |

|    | 2.10   | SAR Te   | chniques for External Testing                  | 42       |

|    |        | 2.10.1   | Low Power ATPG Algorithm                       | 42       |

|    |        | 2.10.2   | Input Control                                  | 42       |

|    |        | 2.10.3   | Ordering Technique                             | 43       |

|    |        | 2.10.4   | Don't Care Bit Filling                         | 44       |

|    | 2.11   | Externa  | al Testing SAR Techniques for IP Cores         | 45       |

|    | 2.12   | Method   | ology for Experiments                          | 46       |

|    |        | 2.12.1   | Results for Proposed Methods in This<br>Thesis | 46       |

|    |        | 2.12.2   | Contemporary Profession Tool                   | 48       |

|    | 2.13   | Inferen  | ces                                            | 49       |

| 3. | Run Le | ength Co | de Based Test Data Compression                 | 50       |

|    | 3.1    | Existing | g Run Length Codes                             | 50       |

|    |        | 3.1.1    | Overview of Existing Run Length Codes          | 50       |

|    |        | 3.1.2    | Analysis of Existing Run Length Codes          | 58       |

|    | 3.2    | The Pro  | posed Run Based Bit Filling Method             | 59       |

|    |        | 3.2.1    | Problem Formulation                            | 59       |

|    |        | 3.2.2    | Entropy Based Maximum Compression              |          |

|    |        |          | Limit                                          | 62       |

|    |        | 3.2.3    | Experimental Results                           | 64       |

|    |        | 3.2.4    | Observations and Analysis                      | 66       |

|    | 3.3    | The Pro  | posed HDR-CBF-DV Method                        | 67       |

|    |        | 3.3.1    | Problem Formulation                            | 68       |

|    |        | 3.3.2    | Hamming Distance Based Reordering              | 68       |

|    |        | 3.3.3    | Columnwise Bit Filling                         | 73       |

|    |        | 3.3.4    | Difference vector                              | 73       |

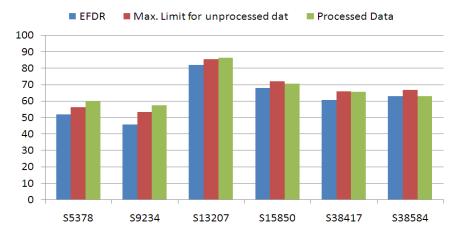

|    |        | 3.3.5    | On-Chip Decoder                                | 74       |

|    |        | 3.3.6    | Experimental Results                           | 75       |

|    | _      | 3.3.7    | Observations and Analysis                      | 77       |

|    | 3.4    |          | posed 2-D Reordering Method                    | 78       |

|    |        | 3.4.1    | Problem Formulation                            | 78       |

|    |        | 3.4.2    | Rowwise First Reordering                       | 78       |

|    |        | 3.4.3    | Columnwise Second Reordering                   | 79<br>70 |

|    |        | 3.4.4    | Power Efficient Bit Filling                    | 79       |

|    |        | 3.4.5      | On-Chip Decoder                               | 80  |

|----|--------|------------|-----------------------------------------------|-----|

|    |        | 3.4.6      | Experimental Results                          | 81  |

|    |        | 3.4.7      | Observations and Analysis                     | 85  |

|    | 3.5    | The Pr     | oposed WTR-CBF-DV Method                      | 86  |

|    |        | 3.5.1      | Problem Formulation                           | 86  |

|    |        | 3.5.2      | Weighted Transition Based Reordering          | 86  |

|    |        | 3.5.3      | Difference vector                             | 88  |

|    |        | 3.5.4      | Run Length Code for Compression               | 88  |

|    |        | 3.5.5      | Algorithm for WTR-CBF-DV                      | 88  |

|    |        | 3.5.6      | Motivational Example                          | 89  |

|    |        | 3.5.7      | On-Chip Decoder                               | 93  |

|    |        | 3.5.8      | Experimental Results                          | 93  |

|    |        | 3.5.9      | Observations                                  | 95  |

|    | 3.6    | Inferen    | lces                                          | 95  |

| 4. | Statis | stical Cod | le Based Test Data Compression                | 97  |

|    | 4.1    | Existin    | g Statistical Codes                           | 97  |

|    |        | 4.1.1      | <b>Overview of Existing Statistical Codes</b> | 97  |

|    |        | 4.1.2      | Analysis of Existing Statistical Codes        | 101 |

|    |        | 4.1.3      | Observations                                  | 108 |

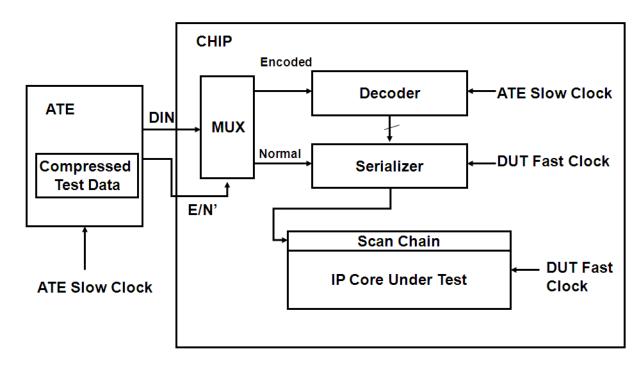

|    | 4.2    | The Pr     | oposed MS-Huffman Code                        | 109 |

|    |        | 4.2.1      | Problem Formulation                           | 110 |

|    |        | 4.2.2      | The Modified Selective Huffman Code           | 111 |

|    |        | 4.2.3      | Mathematical Analysis                         | 113 |

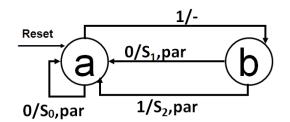

|    |        | 4.2.4      | On-Chip Decoder                               | 116 |

|    |        | 4.2.5      | Test Application Time                         | 118 |

|    |        | 4.2.6      | Experimental Results                          | 121 |

|    |        | 4.2.7      | Observations                                  | 124 |

|    | 4.3    | The Ex     | isting Bit Filling Methods                    | 124 |

|    | 4.4    | The Pr     | oposed FDBAF Method                           | 126 |

|    |        | 4.4.1      | Problem Formulation                           | 126 |

|    |        | 4.4.2      | The FDBAF Algorithm                           | 127 |

|    |        | 4.4.3      | On-Chip Decoder                               | 129 |

|    |        | 4.4.4      | Experimental Results                          | 131 |

|    |        | 4.4.5      | Observations                                  | 131 |

|    | 4.5    | Inferen    | ices                                          | 131 |

| 5  | Conc   | lusion and | d Future Work                                 | 133 |

|    | 5.1    | Conclu     | sion                                          | 133 |

| 5.2                                    | Future Work | 137 |

|----------------------------------------|-------------|-----|

| References                             | 5           | 139 |

| List of Publications Related to Thesis |             | 146 |

| Annexure                               |             | 149 |

## LIST OF TABLES

| 2.1  | Details of MINTEST Generated Test Sets for ISCAS'89         | . – |  |

|------|-------------------------------------------------------------|-----|--|

|      | Circuits                                                    | 47  |  |

| 2.2  | Details of TestKompress Generated Test Set for ISCAS'89     | 48  |  |

| 0.1  | Circuits                                                    |     |  |

| 3.1  | Modified 3-Bit Run Length Code                              | 51  |  |

| 3.2  | Golomb Code for m=4                                         | 52  |  |

| 3.3  | Frequency Directed Run Length Code                          | 53  |  |

| 3.4  | Extended Frequency Directed Run Length Code                 | 54  |  |

| 3.5  | Shifted Alternating Frequency Directed Run Length           |     |  |

|      | Code                                                        | 55  |  |

| 3.6  | Modified Frequency Directed Run length Code                 | 57  |  |

| 3.7  | Fixed Plus Variable Run Length Code                         | 58  |  |

| 3.8  | Comparison of % Compression for Run Length Based Code       | 59  |  |

| 3.9  | Comparison of On-Chip Decoder Area for Run Length Codes.    | 59  |  |

| 3.10 | % Compression for Proposed Bit Filling Method               | 64  |  |

| 3.11 | Total # of Symbols for Proposed Bit Filling Method          | 65  |  |

| 3.12 | Total # of Distinct Symbols for Proposed Bit Filling Method | 65  |  |

| 3.13 | Entropy for Proposed Bit Filling Method                     | 65  |  |

| 3.14 | Scan-In Power for Proposed Bit Filling Method               |     |  |

| 3.15 | Relative % Improvement in % Compression with Different      |     |  |

|      | Run Based Bit Filling Methods                               | 66  |  |

| 3.16 | Compatibility of Bits                                       | 69  |  |

| 3.17 | % Compression of FDR, Golomb, MFDR and Proposed HDR-        |     |  |

|      | CBF-DV                                                      | 75  |  |

| 3.18 | % Compression of EFDR, SAFDR and Proposed HDR-CBF-          |     |  |

|      | DV                                                          | 76  |  |

| 3.19 | Relative % Improvement in % Compression with HDR-CBF-       |     |  |

|      | DV Method                                                   | 77  |  |

| 3.20 | % Compression of EFDR with Proposed 2-D Method              | 81  |  |

| 3.21 | % Compression of SAFDR with Proposed 2-D Method             | 81  |  |

| 3.22 | Comparison of Peak Power                                    | 83  |  |

| 3.23 | Comparison of Average Power                                 | 83  |  |

| 3.24 | Relative % Improvement in % Comparison and Power in case    |     |  |

|      | of the Proposed 2-D Reordering Method                       | 85  |  |

| 3.25 | Comparison of Test Data Processing Methods Applied with     |     |  |

|      | FDR Coding                                                  | 93  |  |

| 3.26 | % Compression for WTR-CBF-DV Method with FDR Coding         | 94  |  |

| 3.27 | Average Power for WTR-CBF-DV Method                          | 94  |  |

|------|--------------------------------------------------------------|-----|--|

| 3.28 | Peak Power for WTR-CBF-DV Method                             |     |  |

| 4.1  | Selective and Optimal Selective Huffman Codes                | 99  |  |

| 4.2  | RL-Huffman Codes for Given Example                           | 100 |  |

| 4.3  | % Compression for VIHC (Group Size= 4)                       | 101 |  |

| 4.4  | Split-VIHC for Test Set –I                                   | 102 |  |

| 4.5  | Split-VIHC for Test Set –II                                  | 102 |  |

| 4.6  | % Compression for Various Huffman Code                       | 103 |  |

| 4.7  | Modified Selective Huffman Code                              | 112 |  |

| 4.8  | % Compression for Selective, Optimal Selective and MS-       |     |  |

|      | Huffman Code (N=8)                                           | 121 |  |

| 4.9  | % Compression for Selective, Optimal Selective and MS-       |     |  |

|      | Huffman Code (N=16)                                          | 121 |  |

| 4.10 | Area Overhead for Selective, Optimal Selective and MS-       |     |  |

|      | Huffman Code                                                 | 122 |  |

| 4.11 | Test Application Time for Selective, Optimal Selective and   |     |  |

|      | MS-Huffman Code                                              | 123 |  |

| 4.12 | TAT for Selective, Optimal Selective and MS-Huffman Code     |     |  |

|      | Block Size = 32                                              | 123 |  |

| 4.13 | TAT for Selective, Optimal Selective and MS-Huffman Code for |     |  |

|      | Size = 08                                                    | 123 |  |

| 4.14 | Test Application Time for Various Compression Methods        | 123 |  |

| 4.15 | Relation between % Compression and # Bits/Symbol for         |     |  |

|      | FDBAF Method                                                 | 128 |  |

| 4.16 | % Compression for Proposed FDBAF Method                      | 131 |  |

# LIST OF FIGURES

| 1.1  | Scan Chain                                            | 4  |

|------|-------------------------------------------------------|----|

| 1.2  | Scan Test Application                                 | 5  |

| 1.3  | Manufacturing Cost versus Test Cost                   | 6  |

| 1.4  | Test Data Volume                                      | 8  |

| 1.5  | Test Data Compression                                 | 10 |

| 1.6  | Power Density versus Channel Length                   | 11 |

| 1.7  | Motivation of the Thesis                              | 14 |

| 1.8  | Goal of the Thesis                                    | 14 |

| 2.1  | Shift and Capture Power during Scan Tests             | 34 |

| 2.2  | Weighted Transitions during Scan In                   | 35 |

| 2.3  | Weighted Transitions during Scan Out                  | 36 |

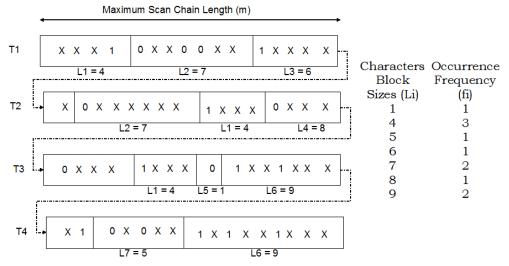

| 3.1  | Example of Simple Run Length Coding                   | 51 |

| 3.2  | Example of Golomb Coding                              | 52 |

| 3.3  | Example of Frequency Directed Run Length Coding       | 53 |

| 3.4  | Example of Extended FDR Coding                        | 54 |

| 3.5  | Example of Alternate FDR Coding                       | 55 |

| 3.6  | Example of Shifted Alternate Coding                   | 56 |

| 3.7  | On-Chip Decoder for Difference Vector                 | 74 |

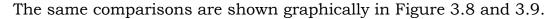

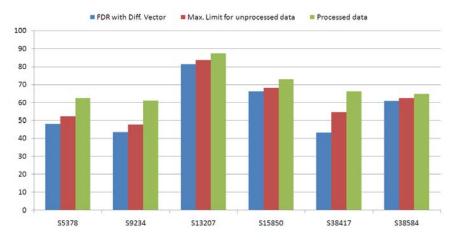

| 3.8  | Improvement in % Compression in FDR by Proposed HDR-  |    |

|      | CBF-DV                                                | 76 |

| 3.9  | Improvement in % Compression in EFDR by Proposed HDR- |    |

|      | CBF-DV                                                | 76 |

| 3.10 | On-Chip Decoder Architecture for 2-D Method           | 80 |

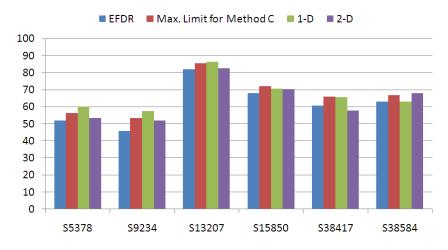

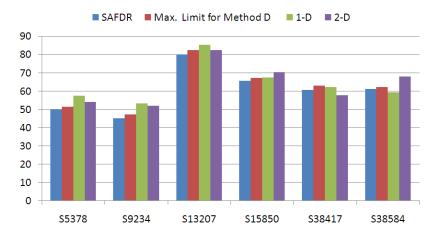

| 3.11 | % Compression for EFDR, Max. Limit ( C ), HDR-CBF-DV  |    |

|      | and 2-D                                               | 82 |

| 3.12 | % Compression for SAFDR, Max. Limit ( D ), HDR-CBF-DV |    |

|      | and 2-D                                               | 82 |

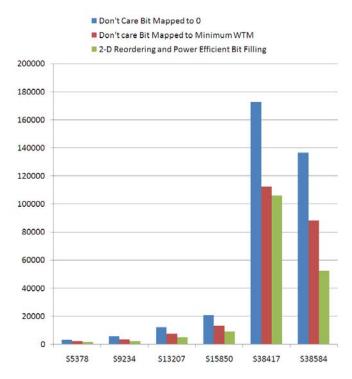

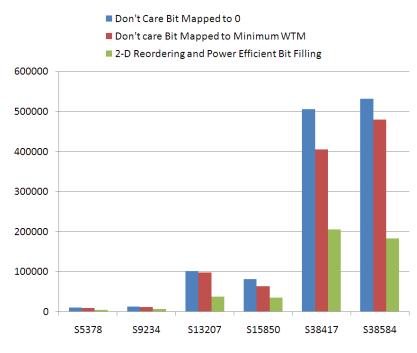

| 3.13 | Comparison of Average Power for 2-D Method            | 84 |

| 3.14 | Comparison of Peak Power for 2-D Method              | 84  |

|------|------------------------------------------------------|-----|

| 4.1  | Example of RL-Huffman Code                           | 100 |

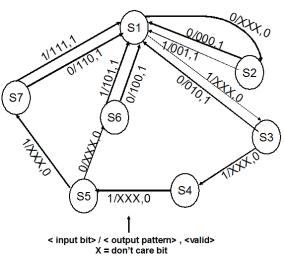

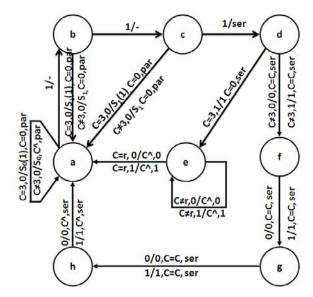

| 4.2  | FSM for Huffman Decoder                              | 104 |

| 4.3  | FSM Decoder for Selective Huffman Code               | 104 |

| 4.4  | FSM Decoder for Optimal Selective Huffman Code       | 105 |

| 4.5  | VIHC Decoder                                         | 106 |

| 4.6  | FSM for VIHC Decoder                                 | 106 |

| 4.7  | CGU for VIHC Decoder                                 | 107 |

| 4.8  | FSM for Split – VIHC Decoder                         | 108 |

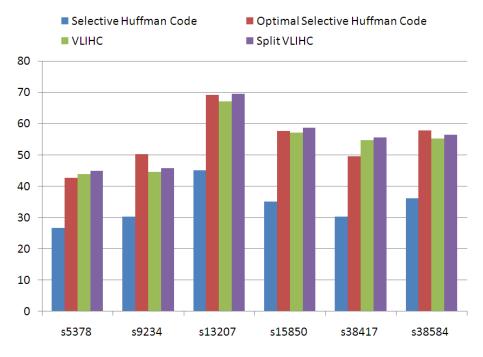

| 4.9  | % Compression for various Statistical Codes          | 109 |

| 4.10 | % Area Overhead for various Statistical Codes        | 109 |

| 4.11 | Architecture for On-Chip Decoder for MS-Huffman Code | 116 |

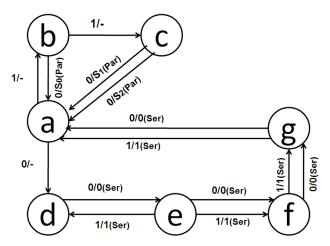

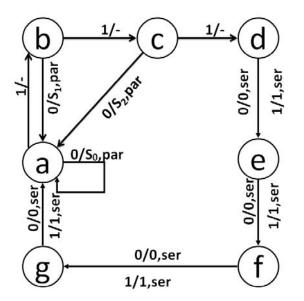

| 4.12 | FSM Decoder for MS-Huffman Code                      | 118 |

| 4.13 | FSM Decoder for FDBAF Algorithm                      | 129 |

## **ABBREVIATIONS**

| AFDR       | Alternate Frequency Directed Run Length Code        |

|------------|-----------------------------------------------------|

| AI         | Artificial Intelligence                             |

| ASIC       | Application Specific Integrated Circuits            |

| ATE        | Automatic Test Equipment                            |

| ATPG       | Automatic Test Pattern Generation                   |

| BIST       | Built In Self Test                                  |

| CUT        | Circuit Under Test                                  |

| DUT        | Design Under Test                                   |

| EFDR       | Extended Frequency Directed Run Length Code         |

| FDR        | Frequency Directed Run Length Code                  |

| FDBAF      | Frequency Directed Bit Appending and Filling        |

| FPVL       | Fixed Plus Variable Length Run length code          |

| GA         | Genetic Algorithm                                   |

| HDR-CBF-DV | Hamming Distance Based Reordering - Column wise     |

|            | Bit Filling – Difference Vector                     |

| IC         | Integrated Circuit                                  |

| IP         | Intellectual Property                               |

| ITRS       | International Technology Roadmap for Semiconductors |

| MFDR       | Modified Frequency Directed Run Length Code         |

| MS-Huffman | Modified Selective Huffman Code                     |

| MT Fill    | Minimum Transition Fill                             |

| SA         | Simulated Annealing                                 |

| SAFDR      | Sifted Alternate Frequency Directed Run length code |

| SAR        | Switching Activity Reduction                        |

| SoB        | System-on-Board                                     |

| SoC        | System-On-Chip                                      |

| ТАТ        | Test Application Time                               |

| TDCE       | Test Data Compression Environment                   |

|            |                                                     |

| THD   | Total Hamming Distance                   |

|-------|------------------------------------------|

| TTM   | Time To Market                           |

| VIHC  | Variable Length Input Huffman Code       |

| SVIHC | Split Variable Length Input Huffman Code |

| VLSI  | Very Large Scale Integration             |

| WSA   | Weighted Switching Activity              |

| WT    | Weighted Transition                      |

| WTM   | Weighted Transition Matrix               |

# Chapter 1 Introduction

From the day in 1947, when Bardeen, Shockley and Brattain at Bell Lab completed their noble prize winning research on bipolar transistor, the use of transistor in terms of integrated circuits (ICs) has been increased at a very rapid rate. The first IC which contained only one transistor, three resistors and one capacitor available commercially was produced by Fairchild Semiconductor Corp. in 1961. From then, the everlasting improvements in semiconductor fabrication technology have led to ICs with billions of transistors. The VLSI industry annual survey shows that total 10<sup>18</sup> transistors were manufactured in 2003. It means that 100 million transistors in form of integrated circuits were manufactured for each of the human on planet Earth during 2003. The ICs, informally known as chips are embedded nowadays in a wide range of products and systems, from consumer electronics and medical equipment to automotive and aviation systems which usually require high reliability and where the cost of failures can be immense.

The technology development in VLSI industry has made it possible to pack millions of transistor on a single chip. The earlier day's System-On-Board (SoB) which contained components like processors and peripheral devices including data transformation engines, data ports, controllers etc, can be now integrated on one single chip referred as System-On-Chip (SoC) [1]. The VLSI design and fabrication flow is extremely complex and time consuming. Addition to that, as described by Moore's law, the technology window for VLSI changes every two years which forces reduction in timeto-market (TTM). In order to meet short TTM requirements, the readymade modules are preferred at system level design rather to design each block of system individually. Such ready-made i.e. pre-designed and preverified blocks of logic, generally called Intellectual Property (IP) cores are largely used in SoCs. The cores can be designed in-house or bought from core vendors; however, it is the task of the system integrator to integrate them into a system.

Even though the IC design is verified thoroughly and it is assured that the design meets all its intended requirements, because of the possible imperfection in fabrication process due to various physical reasons, many defects such as shorts to power or ground, opens, misaligned materials, extra materials, etc. may appear as faults and cause failures. Therefore, each manufactured IC needs to be tested individually [2]. This process is named as fabrication test. The same is applicable to SoC. The aim of fabrication test is to ensure that each fabricated SoC moving to customer is free from manufacturing defects. During the fabrication test, in general, the test stimuli are applied to Device-Under-Test (DUT) and the produced responses are compared against the expected (golden) ones.

# 1.1 Test Flow

The test process is divided into the two stages, the test generation and the test application (fabrication test). The physical defects like extra or missing material caused by dust particles on the mask, wafer surface or processing chemicals, can be detected by its resultant electrical (circuit) level failure modes, such as opens, shorts, and parameter degradations. Fault models are used to represent the effect of a failure. The effect of a failure will, at the logical level, appear as incorrect signal values. One of the earliest and most popular fault models today, is the stuck-at fault model. According to the stuck-at fault model, a defect will cause the line in the design to permanently be stuck at logic value 0 (stuck-at 0) or 1 (stuck-at 1). A stuck-at 0 fault, present at a given fault location, is detected when the stimulus data applied is a 1. The produced response will be a 0 (since the fault location is stuck at 0), which will be different from the expected response which is a 1, hence the fault is detected.

During test generation, an automatic test pattern generator (ATPG) is usually used to generate test-data for the design, including test stimuli and expected responses. The netlist (layout) of the design is given as an input to the ATPG tool which uses sophisticated algorithms to analyze the design and generate test patterns for it. Examples of such test pattern generation algorithms are the D-algorithm and PODEM.

During test application (fabrication test), it is required that the test stimuli can be applied to any given location from the inputs and that the produced responses can be propagated from any given location to the outputs. Hence, two of the most important properties of test are the observability and the controllability. The controllability is the ability of controlling the logic value at a specific location in the IC design. The observability is the ability to observe a logical value at any part of the IC. The controllability is high for the locations close to the inputs while it is low for the locations close to the outputs.

To test an IC is a complex task, even for small ICs. In order to reduce this complexity, the controllability and observability of an IC can be increased during the design stages by adding testability features. This process is called DFT and is, usually, automatically performed using specialized design tools. During the test pattern generation stage, the test-data used to test the fabricated IC is developed. A fault simulator is used to verify the test patterns and to measure the fault coverage. If the fault coverage is low, DFT is repeated until acceptable fault coverage has been achieved. The general aim of DFT is to increase the testability of an IC. Usually, DFT introduces a certain area and performance overhead. For example, it is possible to increase the observability and the controllability by inserting a direct connection, a so-called test point, between the hard-to-test fault location and an I/O pin. The test point DFT approach is straightforward, however, it does not scale as the number of hard-to-test fault locations is increased. A more scalable DFTtechnique is to use scan chain insertion, which is a widely adopted DFTtechnique. To make a design scanable, the FFs in the design are modified with one additional scan input, one additional scan output, and one scan enable input. The scan-modified FFs are then connected in shift registers which is known as scan chains.

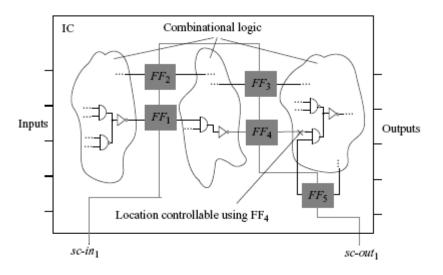

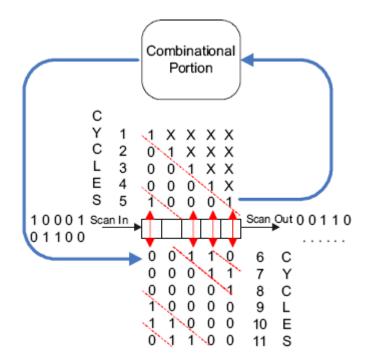

Figure 1.1: Scan Chain

In Figure 1.1, the 5 FFs in the design have been scan-modified and connected into one scan chain. (The scan enable is not illustrated for reasons of readability.) Two additional I/O pins, sc-in<sub>1</sub> and sc-out<sub>1</sub>, are added for the test stimuli shift-in and the produced responses shift-out, respectively. Scan chain testing implies that the design has two modes: functional mode and test mode. The flow of a scan cycle is as follows:

1. Assert test mode, shift in test stimuli (scan-in phase) and set up the desired inputs.

- 2. Assert functional mode and apply one clock cycle. The produced responses are now captured in the FFs and at the outputs.

- 3. Assert test mode and shift out the produced responses (scan-out phase).

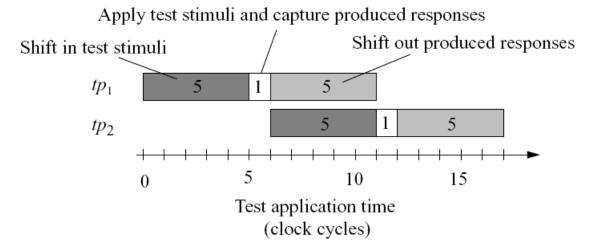

The test-data corresponding to the bits required for a full test stimuli shift-in, apply and capture, and shift-out of the produced responses is called a test pattern. For efficient test application, the test stimuli of the following test pattern are shifted in while the produced responses from the current test pattern are shifted out, that is, a concurrent scan-in and scan-out phase is performed. The scan test application is applied in Figure 1.2 using two test patterns, tp<sub>1</sub> and tp<sub>2</sub>, which are applied to the IC design. The test application time for the two test patterns is 17 clock cycles. The test application time  $TAT_{sc}$  (number of clock cycles) for a test T used to test an IC with sc scan chains is as follows:

$$TAT_{sc} = (1 + ff) * l + ff$$

.....(1.1)

where l is the number of test patterns that are applied and ff is the length of the longest scan chain among the SC scan chains. The rate at which the test-data is shifted is given by the scan frequency,  $f_{scan}$ .

Figure 1.2: Scan Test Application

Fabrication test is usually performed using automatic test equipment (ATE). The test stimuli and expected responses are stored in the ATE memory. Testing is performed by applying test stimuli to the device under test, and by comparing the produced responses to the expected ones. A difference between the expected response and the produced ones indicates that a fault is present and that the device under test should be discarded. The rate at which the test-data is applied is given by the operating frequency of the ATE,  $f_{ATE}$ .

## 1.2 Test Cost

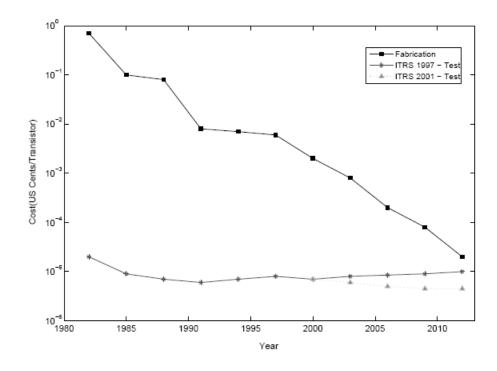

Figure 1.3: Manufacturing Cost versus Test Cost [Courtesy: ITRS]

The importance of reducing the cost of test is motivated by comparing the test cost with the fabrication cost. With the advances in fabrication process for IC, the fabrication cost has reduced drastically and now the testing cost is becoming a dominating part of the overall manufacturing cost of an IC. Figure 1.3 adapted from International Technology Roadmap for Semiconductors (ITRS) 1999 [3] and ITRS 2001 [4] shows how the relative cost of test per transistor grows compared to the fabrication cost per transistor. It shows that the actual cost of test is almost constant while the cost of fabrication has been dramatically reduced over the years. Today, the overall manufacturing cost includes the cost of design, fabrication and test all together and the cost of test is a significant part of this overall manufacturing cost.

#### 1.2.1 Test Time

As each IC is tested individually, the test cost per IC is directly proportional to the test application time per IC. Conventional external testing involves storing all test vectors and test response on an external tester-that is, Automatic Test Equipment (ATE). The overall test application time, in such case, involves time for transferring the test stimuli from tester, response generation time, time for transferring the generated response to tester and time for comparison of generated response with expected response. As per the ITRS 2009, the test application time per SoC will be increased 209.34 times in 2024 compared to it is today in 2009 [5].

#### 1.2.2 Test Data Volume

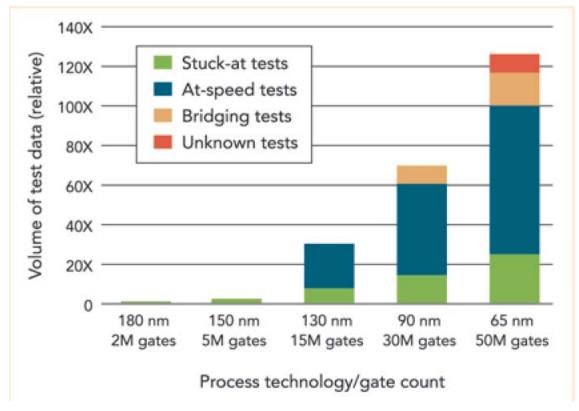

As a result of the emergence of new fabrication technologies and design complexities, the number of tests and corresponding data volume and test time increase with each new fabrication process technology. As per the ITRS 2009, the test data volume which is 19Gb today, will be 488 times larger in 2024 [5]. The Figure 1.4 [6] shows the volume of test data with corresponding technology.

Just to maintain test quality requirements, new tests require: greater than 2X the test time to handle devices that double in gate count while maintaining the same number of scan channels, 3X to 5X the number of patterns to support at-speed scan testing for the growing population of timing defects at 130-nm and smaller fabrication processes, and 5X the number of patterns to handle multiple-detect and new DFM-based fault models.

Figure 1.4: Test Data Volume [Courtesy: www.tmworld.com]

The ATEs have limited speed, memory, and I/O channels. The test data bandwidth between the tester and the chip is relatively small; in fact, it is often the bottleneck determining how fast you can test the chip.

$$test time \geq \frac{amount \ of \ test \ data \ on \ tester}{number \ of \ tester \ channels \ X \ tester \ clock \ rate} \dots (1.2)$$

Testing cannot proceed any faster than the amount of time required to transfer the test data So it can be said that the test time is directly proportional to test data volume (in bits). The test data volume contains test stimuli and expected response. In addition to that, larger test data demands large tester memory.

Three general approaches help to reduce the test time required by ATE per chip [7] are as following:

#### A. Stand-alone Built-In-Self-Test

Traditional stand-alone BIST involves using on-chip hardware to perform all test pattern generation and output response analysis. Stand-alone BIST eliminates the need for tester storage. This is very useful for performing self-test in the field when there is no access to a tester. However, achieving high fault coverage with stand-alone BIST generally requires considerable overhead because of random-pattern-resistant (RPR) faults, which have low detection probabilities. Detecting such faults requires either test points or deterministic-pattern-embedding logic. Other issues with BIST include the need for a BIST-ready design, a way to handle false and multicycle paths, and the need to keep nondeterministic values from corrupting the final signature.

#### B. Hybrid Built-In-Self-Test

If a particular chip design uses BIST only for manufacturing test, then hybrid BIST can be more cost-effective than stand-alone BIST. Hybrid BIST involves storing some data on the tester to help detect RPR faults. The simplest approach is to perform ATPG for RPR faults not detected by pseudorandom BIST to obtain a set of deterministic test patterns that "top up" the fault coverage to the desired level, and then store those patterns directly on the tester. More efficient hybrid BIST schemes store the deterministic top-up patterns on the tester in a compressed form, then use the existing BIST hardware to decompress these patterns. Some schemes embed deterministic patterns by using compressed weight sets or by perturbing the pseudorandom sequence in some manner.

#### C. Test Data Compression

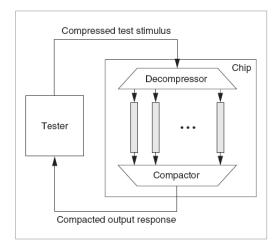

Test data compression Test data compression involves adding some additional on-chip hardware before and after the scan chains. This additional hardware decompresses the test stimulus coming from the tester; and also compacts the response after the scan chains and before it goes to the tester. This permits storing the test data in a compressed form on the tester. With test data compression, the tester still applies a precise deterministic (ATPG-generated) test set to the circuit under test (CUT).

#### 1.2.3 Test Data Compression

Figure 1.5: Test Data Compression

Considering above three methods, the stand alone BIST and hybrid BIST can be incorporated by the IP core designer however these schemes are not in the scope of system integrator as he cannot look into or modify the internal architecture of any IP core. The remaining method, test data compression, is further explored for test time reduction in case of IP core based SoC in this thesis.

As shown in Figure 1.5, test-data compression will allow less numbers of bits to be transferred from ATE to DUT which in turn will require less data transfer time. Another advantage is that it offers is less test data storage requirement on ATE. The resurgence of interest in test data compression has also led to new commercial tools like OPMISR and SmartBIST tools from IBM [8] and the TestKompress tool from Mentor Graphics [9]. Even if, it is assumed that the size of ATE vector memory is assumed to increase as fast as DRAM bit size increases, the test data volume compression ratio required for today's SoC is 80 and it is further predicted that the requirement of this ratio will be as high as 104000 in 2024 [5]. So it is inferred that for test cost reduction, the test data compression techniques should be further explored.

## 1.3 Test Power

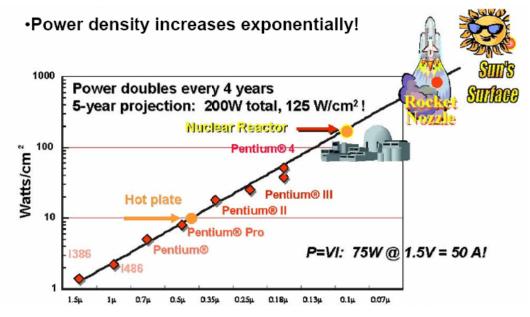

Figure 1.6: Power Density versus Channel Length [Courtesy: INTEL Corp.]

From last two decades, approach of VLSI industry has been to lower voltage and smaller geometry with each generation of IC process. As the result of lower voltage and shrunk geometry, the leakage current and energy increases contributing to higher power. As shown in Figure 1.6, the power density doubles every four year. The problem of power dissipation extends to power delivery, distribution and reliability issues [10]. Hence, low power VLSI design techniques are the major concern for current VLSI industry. Generally, a circuit in test mode may consume the power as high as twice the power consumed in the normal mode. The reasons are as follows. The switching activity of all nodes is often several times higher than the activity during normal operations. Parallel testing strategy adds to power consumption. While testing, the DFT circuits in addition to normal circuit will also consume power. These all reasons can cause significantly larger switching activity in the circuit during test than that during its normal operation. Since dynamic power dissipation in CMOS circuits is proportional to switching activity, this excessive switching activity during test may be responsible for cost, reliability, performance verification, autonomy and technology related problems [11].

The dynamic power has been the major part of overall power dissipation in CMOS circuits. Since this dynamic power is directly proportional to switching activity, the problem of test power reduction can be considered as problem of 'Switching Reduction'.

# 1.4 Issues Related to IP Core Based SoC

As discussed in section 1.2 and 1.3, the existing fabrication testing method faces two major problems: test cost and test power. As stated there, test cost problem can be addressed using test data compression and test power problem can be addressed using switching activity reduction. However, the current research on test data compression and switching power reduction cannot be directly applied to the IP core based SoC.

The structure of IP cores are often hidden from system integrator. For this reason, neither any modification to its internal scan chain nor any DFT insertion is possible for IP cores. Further, any testing tools like Automatic Test Pattern Generator (ATPG) or fault simulation cannot be applied to it. Such cores are coming with ready to use test data. This test data is used to test the core when it is in isolation as well as when it is as a part of system after being integrated into system. It is usually assumed that the core is directly accessible and it becomes the task of the system integrator to ensure that the logic surrounding the core allows the test stimuli to be applied and the produced responses to be transported for evaluation.

In this scenario, only those test data compression and switching reduction schemes which do not require any modification in scan chain or internal structure are suitable to this application. Further, these schemes should not demand the help of any testing tool like ATPG or fault simulation and must be applicable to any kind of test data i.e. partially specified or fully specified.

# 1.5 Objective

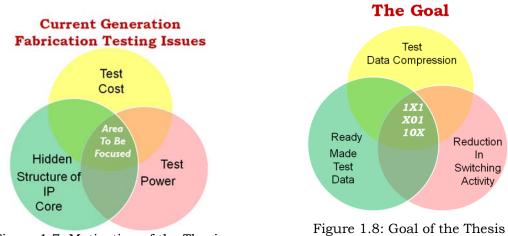

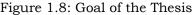

The motivation here is to solve the issues like test cost and test power in context of hidden structure of IP core. The goal decided is to use test data compression for test cost, switching activity reduction for test power and ready-made test data in context of IP core based SoC. Figure 1.7 and 1.8 shows the motivation of the thesis and goal of the thesis respectively.

Figure 1.7: Motivation of the Thesis

The objective of the thesis is defined as:

To design a test data processing or/and compression method specifically for IP core based SoC which

- 1. does not require any insertion or modification in internal structure of IP core

- 2. does not require any test development tools like ATPG or fault simulation

- 3. increases the compression

- 4. reduces the overall test application time (TAT)

- 5. reduces the switching activity during scan operation

- 6. does not increase the on-chip area overhead

compared to existing methods.

# 1.6 Adopted Methodology

In this thesis work, the methodology adopted is:

- 1. The need or issues related to current generation testing is studied.

- 2. The existing solutions for that issue are surveyed.

- 3. From the available solutions, the possible solutions for IP core based SoC are separated.

- 4. These solutions are implemented and analyzed.

- 5. The existing solutions are optimized.

- 6. For further improvement, new methods are proposed and proved mathematically supported by sufficient amount of experimental results.

# 1.7 Thesis Organization

The rest of the thesis work is divided into four chapters. The detail and publications related to each chapter is as follows:

#### Chapter 2 Literature Survey

In this chapter, the need and parameters related to test data compression is discussed in brief. The various test data compression schemes like linear decompression based schemes, broad cast scan based scheme and code based scheme with their suitability to IP cores is reviewed. After the survey on all four classifications of code based scheme, i.e. run-length based code, statistical code, dictionary codes and constructive code, the classifications suitable to IP core, `run length based code' and `statistical code' is explained in detail.

This chapter also includes the complete survey on various classifications of switching activity reduction methods in case of external testing, DFT and BIST techniques with criteria of the suitability to IP core. The selected external low power testing technique is further explored and 'don't care bit filling method' as well as 'test vector reordering method' is described in detail.

[Publications Related to This Chapter: Ref. J-3, C-1, C-8, C-9]

#### Chapter 3 Run Length Code Based Test Data Compression

This chapter contains the overview and analysis through implementation and simulation of existing run length based test data compression techniques like simple run length coding, Golomb coding, Frequency Directed Run length coding (FDR), extended FDR, modified FDR, alternating FDR, shifted alternating FDR, etc. The analysis of area overhead for various on-chip decoders is included. The proposed `Run Based Bit Filling' depending upon the classification of run types is described with necessary motivational example. The upper limit of compression based on entropy is estimated for the proposed 'Run Based Bit Filling'. The test data processing method "Hamming Distance Based Reordering and Columnwise Bit Filling with Difference Vector (HDR-CBF-DV)" is included in this chapter. This chapter also contains the power efficient test data processing technique "2-D Reordering" and the power efficient 'Weighted Transition Based Reordering (WTR)'. The effectiveness for each scheme is demonstrated with sufficient simulation results.

[Publications Related to This Chapter: Ref. J-1, J-5, C-3, C-4, C-5, C-6]

#### Chapter 4 Statistical Code Based Test Data Compression

This chapter includes overview and analysis through implementation and simulation of existing statistical test data compression methods like Huffman code, selective Huffman code, optimal selective Huffman code, variable length input Huffman code (VIHC), Split VIHC, fixed plus variable length coding, RL-Huffman code, multilevel Huffman code etc. A test data compression code `Modified Selective Huffman Code (MS-Huffman Code)' with necessary decoder architecture is proposed. The improvement in compression and overall test application time compared to existing method without any extra area overhead is proved mathematically as well as demonstrated with necessary simulation results. This chapter includes the test data processing technique `Frequency Dependant Bit Appending and Filling (FDBAF)'.

[Publications Related to This Chapter: Ref. J-2, J-4, C-2, C-7]

#### Chapter 5 Conclusion and Future Work

This chapter presents the conclusion of the thesis. It also uncovers the scope of future work in the same direction.

# Chapter 2 Literature Survey

Because of the development in fabrication and design technology, IP Core based SoC has come up as the current state of art for VLSI design. While test cost and test power remain burning issues for testing, the hidden structure of IP core has further exaggerated the problem.

The test cost is directly proportional to test application time which is directly related to amount of test data. Hence it can be said that test cost problem can be converted in to test data compression problem.

Similar way, the dynamic power plays the significant role in overall test power consumption. The dynamic power is directly proportional to switching activity during test. It means that the overall test power can be directly controlled by reducing the switching activity during test.

The detailed survey on test data compression and switching activity reduction methods follows in subsequent sections.

# 2.1 Test Data Compression

The advantage of test data compression is that it generates the complete set of patterns applied to the CUT with ATPG, and this set of test patterns can be optimized with respect to the desired fault coverage. Test data compression is also easier to adopt in industry because it's compatible with the conventional design rules and test generation flows for scan testing. Test data compression has two advantages. The most important is it can reduce the test time for a given test data bandwidth. The second advantage is it reduces the amount of data stored on the tester, which can extend the life of older testers that have limited memory.

Test data compression involves two methodologies: 1. for the single scan chain testing, it reduces the number of bits to be transferred from ATE to DUT and thus reduces the test data transfer time. At DUT, there is one on-chip decoder to expand the code word again in original form. This decoding time may further affect the overall reduction in test application time. 2. for multiple scan chain testing, the decompressor expand the data from n tester channels to fill greater than n scan chains. Increasing the number of scan chains shortens each scan chain, in turn reducing the number of clock cycles needed to shift in each test vector.

Test data compression must compress the test vectors lossless (i.e. it must reproduce all the care bits after decompression) to preserve fault coverage. Test vectors are highly compressible because typically only 1% to 5% of their bits are specified (care) bits. The rest are don't-cares, which can take on any value with no impact on the fault coverage. A test cube is a deterministic test vector in which the bits that ATPG does not assign are left as don't-cares (i.e. the ATPG does not randomly fill the don't-cares). In addition to containing a very high percentage of don'tcares, test cubes also tend to be highly correlated because faults are structurally related in the circuit. Both of these factors are exploitable to achieve high amounts of compression.

## 2.2 Test Data Compression Methods

There is variety of data compression algorithms available in literature used for multimedia, communication and such other applications which compresses the data either lossy or lossless. These algorithms can compress any type of data i.e. fully specified (without any don't care bits) or partially specified (with don't care bits). From all these methods, only those methods which compress data lossless can be applied for compression of test vectors so that the fault coverage is retained.

The ATPG uncompacted test-data consists a large number of unspecified bits, so-called don't-care bits which, together with regularities in the testdata can be explored during the compression, such that a minimal amount of test-data needs to be stored in the tester memory [12]. The test application time can be reduced if decoders are placed on-chip, since the amount of test-data to be applied through the chip I/O pins is reduced [13].

The quality factors of test data compression techniques are:

- 1. The amount of compression possible

- 2. The area overhead because of decoding architecture. The on-chip decompression circuitry must be small so that it does not add significant area overhead. The properties of the code are chosen such that the decoder has a very small area.

- 3. The reduction in test time. Transferring compressed test vectors takes less time than transferring the full vectors at a given bandwidth. However, in order to guarantee a reduction in the overall test time, the decompression process should not add much delay (which would subtract from the time saved in transferring the test data). The properties of the code are chosen is guaranteed to be able to decode the test data as fast as the tester can transfer it.

- 4. The scalability of compression (does the compression technique work with various design sizes, with few or many scan channels, and with different types of designs?)

- 5. Power dissipation is an important factor in today's chip design.

- 6. The robustness in the presence of X states (can the design maintain compression while handling X states without losing coverage?)

- 7. The ability to perform diagnostics of failures when applying compressed patterns

- 8. Type of Decoder: data-independent decoder or data dependant decoder. In the former category, the on-chip decoder or decompression program is universal, i.e., it is reusable for any test set. In contrast, the decoder of a data-dependent technique can only decompress a specific test vector. They have difficulties in terms of size and organization for improved compression and often require large on-chip memory. Hence, data-independency is a preferable property

Various methods described in literature to compress specifically VLSI test data can be classified in following subsections.

### 1. Linear Decompression Based Test Data Compression Method

From a small number of bits (i.e. seed) stored on ATE, a large test data can be reproduce at DUT using only linear operations on seed with help of Linear Feedback Shift Register(LFSR) and XOR network. These schemes are called linear decompression based schemes. This methodology is effectively used in [14, 15, 16, 17, 18 and 19].

#### 2. Broadcast Scan Based Test Data Compression Method

The second classification of these techniques which is called broadcast scan based method, is based on the idea of broadcasting the same value to multiple scan chains (a single tester channel drives multiple scan chains). This is actually a special degenerate case of linear decompression in which the decompressor consists of only fan-out wires. This methodology is widely used in [20, 21, 22, 23] etc.

#### 3. Code Based Test Data Compression Method

The third classification is code based data compression method. It uses data compression codes to encode the test cubes. This involves partitioning the original data into symbols, and then replacing each symbol with a code word to form the compressed data. To perform decompression, a decoder simply converts each code word in the compressed data back into the corresponding symbol. Various code based data compression methods are evolved as described in next section of this chapter.

## 2.3 Compression Methods for IP Cores

The test data compression methods classified as above is widely accepted for ASIC testing. While considering its application for IP core based SoC testing, the suitability of such methods to IP must be analyzed.

From above three compression methods,

- Linear decompression method requires very simple controlling logic and is very efficient in compressing. The main drawback here is, it requires two stage ATPG. Also it is more convenient with partially specified test data only.

- The Broadcast scan methods are also efficient in compression and require a simple decoder. Like linear decompression, this method also requires one step ATPG and more suitable to partially specified test data with large amount of don't care bits.

- The code based test data compression method is not as efficient in exploiting don't care bits and requires a complex control logic. However it is suitable to any kind of test data and does not require any testing tool.

From above discussion, it can be inferred that the code based test data compression method is suitable to IP core based SoC. Hence, this method is selected as basic scheme for further consideration during this work. Before continuing the survey on code based compression methods, the parameters influencing the code based methods are discussed in the following section.

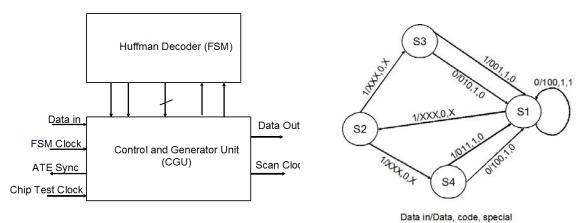

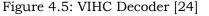

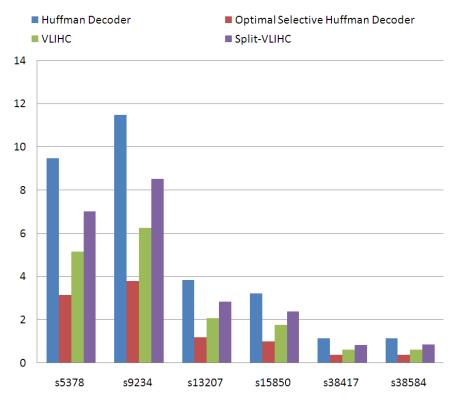

## 2.4 Test Data Compression Environment

Test data compression environment (TDCE) [24] comprising compression method and on-chip decoder, is defined and analyzed with respect to three TDCE parameters: compression ratio, area overhead and test application time. Testing in TDCE implies sending the compressed test data from the ATE to the on-chip decoder, decompressing the test data on-chip and sending the decompressed test data to the core under test (CUT). There are two main components in TDCE: the compression method, used to compress the test set off-chip, and the associated decompression method, based on an on-chip decoder, used to restore the initial test set on-chip. The on-chip decoder comprises two units: a unit to identify a compressed code and a unit to decompress it. If the two units can work independently (i.e., decompressing the current code and identifying a new code can be done simultaneously), then the decoder is called parallel. Otherwise, the decoder is referred to as serial.

Testing in TDCE is characterized by the following two parameters:

- Compression Ratio: which identifies the performance of the compression method and the memory & channel capacity requirements of the ATE

- 2. Area Overhead: imposed by the on-chip decoder (dedicated hardware or on-chip processor)

23

There are a number of factors which influence the above parameters:

- 1. The mapping and reordering algorithm, which prepares the test set for compression by mapping the 'don't cares' in the test set to '0's or '1's, and by reordering the test set.

- 2. The compression algorithm, which based on a coding scheme, compresses the initial test set.

- 3. The type of input patterns used as input by the coding scheme, which can be of fixed or variable lengths.

- 4. The length of the pattern which is the maximum allowed input pattern length used in the coding scheme.

- 5. The type of the on-chip decoder, i.e., the on-chip decoder can be serial or parallel.

#### **Compression Ratio**

Using patterns of various types and various lengths, the compression algorithms exploit different features of the test set. Mapping and reordering the initial test set emphasizes these features. Therefore, the compression ratio is influenced first by the mapping and reordering algorithm, and then by the type of input patterns and the length of the pattern, and finally by the compression algorithm.

As a quantitative measure of test data compression, the following two expressions can be used:

$$test \ data \ compression \ ratio = \frac{compressed \ test \ data \ (\# \ of \ bits)}{original \ test \ data \ (\# \ of \ bits)}$$

$$\dots \dots \dots \dots \dots (2.1)$$

#### Area Overhead

Area overhead depends upon the decoder type and input pattern. If the decoder is serial then the synchronization between the two units (code identification and decompression) is already at hand. However, if the decoder is parallel, then the two units have to synchronize, which can lead to increased control complexity and consequently to higher area overhead. Depending on the type of the input pattern different types of logic are required to generate the pattern on-chip. For example, if the coding scheme uses fixed-length input patterns, then a shift register is required to generate the patterns, however, if variable-length input patterns (runs of '0's for example) are used, then counters can be employed to generate the patterns. Since the length of the pattern impacts the size of the decoding logic, it also influences the area overhead.

Area Overhead in % =

$$\frac{\text{area of original circuit} - \text{area of decoder}}{\text{area of original circuit}} X 100$$

.....(2.3)

#### Test Application Time (TAT)

Test data compression will reduce the test time for transferring the data from ATE to DUT. However, the on-chip decoder will add decoding time to overall test application time. Hence, it should be taken care that the compression does not increase the overall test application time (TAT).

## 2.5 Code Based Test Data Compression Methods

The data compression codes are generally classified into four categories based on symbol size and codeword size. As the name suggests, in fixed to fixed coding schemes, the symbol size as well as codeword size is fixed. In fixed to variable coding schemes, the symbol size is fixed but codeword size is variable. In variable to fixed coding schemes, the symbol size is variable but codeword size is fixed. While in variable to variable coding schemes, the symbol as well as codeword size is variable. Based on the basic schemes and evolved variants, the code based compression methods are broadly divided into four different categories: Statistical Codes, Run-Length Codes, Dictionary Codes, and Constructive Codes.

All these categories are discussed in following subsections:

#### 2.5.1 Statistical Code Based Methods

Statistical coding partitions the original data into n bit symbols and assigns variable length code words based on each symbol's frequency of occurrence. It assigns shorter code words to symbols that occur more frequently, and longer code words to those that occur less frequently. This strategy minimizes the average length of a code word.

The Huffman code is very widely used code in all lossless data compression applications as the Huffman code is an optimal statistical code that is proven to provide the shortest average codeword length among all uniquely decodable variable length codes. The only disadvantage is that when the Huffman hardware decoder is placed in chip, it requires a large amount of area overhead because its size grows exponentially with symbol size [25]. The improved approach is a selective Huffman coding [26] for which a very simple decoder can be constructed. It only codes the most frequently occurring blocks in-stead of all blocks using code words with small numbers of bits.

The Selective Huffman encoding required extra bit with each codeword. This constant overhead, although minimum for the unencoded data blocks, can be relatively high for the most frequently occurring code words. An optimal selective Huffman code [27] uses an additional Huffman codeword in front of only the unencoded data blocks, relieving in this way the most frequently occurring codewords from the extra-bit over-head.

An arithmetic coding based compression method is proposed in [28, 29]. Given a test set in which all the test vectors are fully specified, some primary input values may be changed to opposite logic values without losing fault coverage [30]. This helps in reducing the number of distinct blocks which later coded with Huffman coding [31].

There are number of techniques proposed by researchers which explore the advantages of statistical codes in combinations of other coding techniques.

In RL-Huffman coding [32], the don't care bits in test vector are first filled with either '0' or '1' such that the overall run length of 1s or 0s has been increased. Such runs with variable size are coded using Huffman coding.

The Multilevel Huffman test data compression method [33, 34] is based on Huffman coding with a limited number of codewords. The test cubes of the CUT are compared against the pseudorandom sequences generated by various cells of an LFSR and if they match, the Huffman coded index for each selected LFSR cell is chosen for feeding the scan chain of the CUT.

As per variable-to-variable Huffman coding [35], densely specified regions are the main sources of unencoded data, and, therefore, their compression is favored by the usage of small distinct blocks. On the other hand, sparsely specified regions are more efficiently compressed using large distinct blocks, so to improve compression, the test sets should be partitioned into variable-length parts, which means that variable-length distinct blocks should be encoded. Apart from the variable-to-variable nature of the proposed approach, the generated codewords are reusable in the sense that they can encode compatible blocks of different sizes.

#### 2.5.2 Run Length Code Based Methods

The first data compression codes that researchers explored for compressing scan vectors were encoded by runs of repeated values of zeroes.

The simplest scheme based on run-length codes that encoded runs of 0s using fixed-length code words was proposed in [36]. To increase the prevalence of runs of 0s, this scheme uses cyclic scan architecture to allow the application of difference vectors.

A technique based on Golomb codes [37, 38] encodes runs of 0s with variable-length code words. The codewords are divided into groups of equal size m where m is any power of 2. The use of variable-length code words allows efficient encoding of longer runs, although it requires a synchronization mechanism between the tester and the chip.

A Frequency Directed Run length code (FDR) similar to Golomb code is proposed in [39, 40] but the difference is the variable group size. It is based on the observation that the frequency of runs of 0s with run length less than 20 is high and even within the range of 0 to 20, the frequency of runs decreases rapidly with increase in run length. So test data compression can be more efficient if the runs of 0s with shorter run length are mapped to shorter codewords.

The FDR code is very efficient for compressing data that has few 1s and long runs of 0s but inefficient for data streams that are composed of both runs of 0s and runs of 1s. Generally test vectors contain 0s and 1s in group i.e. there will be a run of 1s followed by run of 0s and vice versa. In an extension of FDR (EFDR) [41], the run of 0s followed by bit '1' and run of 1s followed by bit '0' are coded same way as FDR but adding an extra bit at beginning of FDR codeword.

Generally, the test set T is composed of alternating runs of zeros and run of ones. In alternating FDR coding (AFDR) style [42], instead of adding the extra bit to each run length code-word, only one bit will be added at beginning to indicate the type of first run length and then successive run length is automatically alternating type. So all run lengths are coded with normal FDR but at beginning, one bit will be added to indicate the first run type.

An evolution in alternating FDR is Shifted Alternating FDR (SAFDR) [43]. Here the runs are of either made of only ones or only zeroes. The both types of runs are placed alternating. So in such alternating FDR, no codeword is required for zero run length and each codeword will be shifted to one position higher run length. This helps in achieving higher compression compared to Alternating FDR.

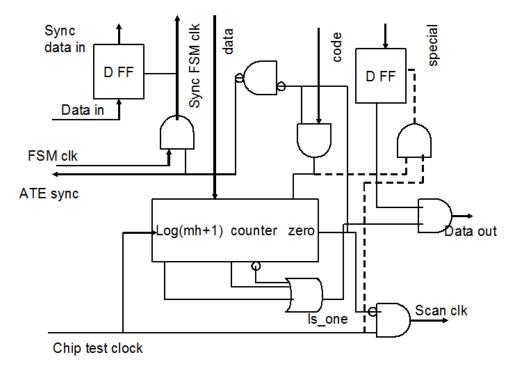

Regardless of the good compression ratios the area overhead of FDR is a disadvantage. So a mix of Huffman and FDR is proposed which instead of only patterns of fixed-length uses patterns of variable-length as input to the Huffman algorithm (VIHC) [24]. Here the compression ratio is retained because of FDR and the area overhead is reduced using selective Huffman Coding.

Spilt VIHC [44] approach demonstrates that before going to the VIHC, if the test file is divided in to two or more equal parts and the vectors are reordered in a specific way, the compression ratio can be still improved.

One more scheme based on probability of 0s and FDR is Modified Frequency-Directed Run-length (MFDR)[45]. In this scheme, the groups of FDR is further modified such a way to give better compression ratio than FDR if the probability of 0s in the test set is greater than 0.8565. A scheme based on selectively relaxing some bits of test vector before encoding it using FDR or Golomb code is proposed in [46]. Here by changing a specified bit with value 1 to a don't-care, two consecutive runs of 0s in the test sequence can be concatenated into a longer run of 0, thereby facilitating run-length coding. This procedure retains the fault coverage of the test set.

The data independent run length coding [47] explores the don't care bits in test patterns. It transmits the first segment of pattern as it is and then compares all other subsequent segments with first segment and decides either the next segment is same as first or complement of first segment.

Stuck at faults based test patterns can be reordered without any loss of fault coverage. The test patterns are reordered based on the minimum Hamming distance between them.

The run based reordering approach [48] is based on reordering the test patterns to give the bigger run lengths of 0s. The variable to fixed plus variable length coding [49] scheme divides code word into two parts: fixed length head section and variable-length tail section. Combined partial test vector reuse and FDR coding [50] finds such a vector, from which parts of each test vector from the different test sets can be sought. Based on this, a vector named overlapped vector which contains parts of each test vector and has shorter length than that of the sum of each test vector's length is decided.

#### 2.5.3 Dictionary Code Based Methods

The basic idea behind dictionary codes is to take advantage of a number of commonly occurring sequences. This scheme partitions the original data into n-bit symbols and uses a dictionary to store each unique symbol. This technique compresses data by encoding each *n*-bits using a *b*-bit code word that corresponds to the symbol's index in the dictionary (*b* is less than *n* when all possible symbols do not occur in the data). A scan vector compression scheme that uses a complete dictionary is proposed in [51]. The size of each index equals  $[log_2n]$ , where *n* is the number of distinct scan slices.

A partial-dictionary coding scheme [52] constrains the dictionary size based on the allocated area for the decompressor.

A method based on LZW, particularly LZ77 is proposed in [53, 54]. A partial dictionary along with a correction network that inputs bits to convert a dictionary entry into the desired scan slice is proposed in [55].

A hybrid test data compression method using scan chain compaction and dictionary based Scheme is proposed in [56].

#### 2.5.4 Constructive Code Based Methods

Constructive codes exploit the fact that each n-bit scan slice typically contains relatively few care bits. It is possible to construct the scan slice by incrementally specifying all the care bits using a sufficient number of code words.

A scheme to construct the current scan slice from the previous scan slice by flipping bits is proposed in [57]. A constructive code method [58] first sets all bits in a scan slice to either 0 or 1 (whichever matches the largest number of care bits), and then incrementally loads the care bits with opposite value using either a single-bit or a group-copy mode.

## 2.6 Code Based Method for IP Cores

The dictionary codes and constructive codes have reported high compression ratio, however, their results in terms of consistency to achieve a high compression ratio, cost of memory demanding decoder, and scan-in power due to high bit transitions are not favoring them for further use [32]. A drawback of using a complete dictionary is that the dictionary size can become very large, resulting in too much overhead for the decompressor. The drawback for constructive coding is very complex and data dependant decoder.

The remaining two methods: statistical coding and run length based coding are further selected for this thesis work on testing of IP core based SoC.

## 2.7 Test Power

Generally, a circuit in test mode may consume the power as high as three to four times the power consumed in the normal mode [10]. The main reasons of this extra power are parallel testing strategy and extra power drawn by DFT circuits in addition to normal circuit. This extra power consumption due to test application may give rise to severe hazards to the circuit reliability [11]. Moreover, it may be responsible for cost, performance verification as well as technology related problems. The terminology related to power issues [59] is as follows:

#### Energy

The total switching activity generated during test application. Energy has impact on the battery lifetime during power up or periodic self-test of battery operated devices.

#### Peak Power

The peak power is the highest value of power at any given instant. The peak power determines the thermal and electrical limits of components and the system packaging requirements. If the peak power exceeds a certain limit, the correct functioning of the entire circuit is no longer guaranteed [11].

The peak power consumption corresponds to the maximum of the instantaneous power consumed during the test session. It therefore