# Automatic conversion of source code for C to CUDA C

By

Parth R. Trivedi Roll No: 10MCEC25

#

# Automatic conversion of source code for C to CUDA C

## **Major Project**

Submitted in partial fulfillment of the requirements

For the degree of

Master of Technology in Computer Science and Engineering

By

Parth R. Trivedi Roll No: 10MCEC25

#

## Undertaking for Originality of the Work

I, Parth R. Trivedi, Roll. No. 10MCEC25, give undertaking that the Major Project entitled Automatic conversion of source code for C to CUDA C submitted by me, towards the partial fulfillment of the requirements for the degree of Master of Technology in Computer Science & Engineering of Nirma University, Ahmedabad, is the original work carried out by me and I give assurance that no attempt of plagiarism has been made. I understand that in the event of any similarity found subsequently with any published work or any dissertation work elsewhere; it will result in severe disciplinary action.

| Signature of Studen |

|---------------------|

| Date:               |

| Place:              |

## Certificate

This is to certify that the Major Project entitled "Automatic conversion of source code for C to CUDA C" submitted by Parth R. Trivedi (10MCEC025), towards the partial fulfillment of the requirements for the degree of Master of Technology in Computer Science and Engineering of Nirma University, Ahmedabad is the record of work carried out by him under my supervision and guidance. In my opinion, the submitted work has reached a level required for being accepted for examination. The results embodied in this major project, to the best of my knowledge, haven't been submitted to any other university or institution for award of any degree or diploma.

Dr. S.N. Pradhan

Guide, Professor,

Department Computer Engineering,

Institute of Technology,

Nirma University, Ahmedabad

Prof. D. J. Patel

Professor and Head,

Department of Computer Engineering,

Institute of Technology,

Nirma University, Ahmedabad

Dr. K. Kotecha

Director,

Institute of Technology,

Nirma University, Ahmedabad

## Acknowledgements

It gives me great pleasure in expressing thanks and profound gratitude to my guide Dr. S.N. Pradhan, Professor and M.Tech. Coordinator, Department of Computer Science and Engineering, Institute of Technology, Nirma University, Ahmedabad for his valuable guidance and continual encouragement throughout part one of the Major project. I am heartily thankful to him for his time to time suggestions and the clarity of the concepts of the topic that helped me a lot during this study.

I would like to extend my gratitude to Prof. D.J.Patel, H.O.D., Department of Computer Science and Engineering, Institute of Technology, Nirma University, Ahmedabad for fruitful discussions and valuable suggestions during meetings and for their encouragement.

I would like to thank Dr. Ketan Kotecha, Honorable Director, Institute of Technology, Nirma University, Ahmedabad for providing basic infrastructure and healthy research environment.

I would like to thank Prof. Samir Patel who gave me his precious time for discussions and evaluation of my project.

I would also thank my Institution, all my faculty members in Department of Computer Science and my colleagues without whom this project would have been a distant reality. Last, but not the least, no words are enough to acknowledge constant support and sacrifices of my family members because of whom I am able to complete my dissertation work successfully.

- Parth R. Trivedi 10MCEC25

## Abstract

As today in so many fields, computation is the main part of the algorithm and takes too much time in execution of the algorithm, it is necessary to parallelize the computation or reduce execution time. GPUs are widely used in (HPC) High Performance Computing. To achieve speedup, either we can increase clock frequency or multiple computation cores on the same chip. The clock speeds have reached the physical limit, so the use of many cores is the only way left to achieve speedup. As the GPU is growing demand of the Game Industry and large scientific computations, efforts have been made to take advantages to gain maximum utilization of the GPUs in computation. Though GPUs are widely used in Supercomputers today, they are not code transparent because one has to sit and code the algorithms in CUDA C to run them on GPU. So if we can have some middleware that converts the C programs to CUDA, the end user gets transparency.

I tried to develop a prototype compiler using ANTLR in visual studio that converts the C programs in CUDA C language. The thesis describes the literature survey in CUDA, different performance optimization strategies to reduce execution time, the Pattern approach to develop a translator for source code to source code translation on the basis of selection of codes using patterns, platforms to code such translator and platform comparison and choice and algorithm of translation. The Compiler Architecture and its implementation details are widely described in thesis. The thesis describes implementation of the complete C2CUDATranslator, testing and analysis of the developed compiler. The compiler takes input of C program and generates CUDA program. The thesis demonstrates the pattern approach for language to language translation and the compiler flow architecture. C2CUDAranslator covers a new way or a framework to implement new analysis algorithms to detect dependencies in the code. The thesis also covers neural network design for compiler learning and optimization of the translated code. The Neural Network helps compiler to take decision for selection of transformation and translation.

Finally, the thesis covers outcome of the compiler, converted programs list, evaluation using parboil benchmark suite, performance graph of converted programs. It is concluded that the C2CUDATranslator saves 95% of the development time in selected cases.

# Contents

| U            | nder                            | taking for Originality of the Work           | ii         |  |  |  |  |  |

|--------------|---------------------------------|----------------------------------------------|------------|--|--|--|--|--|

| $\mathbf{C}$ | Certificate<br>Acknowledgements |                                              |            |  |  |  |  |  |

| A            |                                 |                                              |            |  |  |  |  |  |

| A            | bstra                           | uct                                          | V          |  |  |  |  |  |

| $\mathbf{C}$ | onter                           | nts                                          | 3          |  |  |  |  |  |

| Li           | st of                           | Tables                                       | x          |  |  |  |  |  |

| Li           | st of                           | Figures                                      | xii        |  |  |  |  |  |

| A            | bbre                            | viations                                     | xiv        |  |  |  |  |  |

| 1            | Intr                            | roduction                                    | 1          |  |  |  |  |  |

|              | 1.1                             | Objective of the Work                        | 2          |  |  |  |  |  |

|              | 1.2                             | Scope of the Work                            | 2          |  |  |  |  |  |

|              | 1.3                             | Motivation of the Work                       | 2          |  |  |  |  |  |

|              | 1.4                             | Thesis Organization                          | 2          |  |  |  |  |  |

| 2            | Literature Survey               |                                              |            |  |  |  |  |  |

|              | 2.1                             | Design goal                                  | 5          |  |  |  |  |  |

|              |                                 | 2.1.1 Advantages                             | $\epsilon$ |  |  |  |  |  |

|              | 2.2                             | Limitation                                   | 7          |  |  |  |  |  |

|              | 2.3                             | CUDA Programming Model                       | 7          |  |  |  |  |  |

|              | 2.4                             | CUDA Memory Model                            | 6          |  |  |  |  |  |

|              | 2.5                             | Hardware Implementation: Memory Architecture | 11         |  |  |  |  |  |

|              | 2.6                             | Hardware Implementation: Execution Model     | 12         |  |  |  |  |  |

| 3            |                                 | Performance Optimization Strategies          |            |  |  |  |  |  |

|              | 3.1                             | Maximize Utilization                         | 14         |  |  |  |  |  |

|              |                                 | 3.1.1 Application Level                      | 14         |  |  |  |  |  |

|              |                                 | 3.1.2 Device Level                           | 14         |  |  |  |  |  |

|              |                                 | 3.1.3 Multiprocessor Level                   | 15         |  |  |  |  |  |

|              | 3.2                             | Maximize Memory Throughput                   | 16         |  |  |  |  |  |

| CONTENTS    | viii |

|-------------|------|

| 501(1E1(15) | VIII |

|   |                       | 3.2.1 Data Transfer between Host and Device | 16        |  |  |  |  |  |  |

|---|-----------------------|---------------------------------------------|-----------|--|--|--|--|--|--|

|   | 0.0                   | 3.2.2 Optimize Memory Access Patterns       | 19        |  |  |  |  |  |  |

|   | 3.3                   | Execution configuration optimization        | 21        |  |  |  |  |  |  |

|   | 9.4                   | 3.3.1 Occupancy                             | 22        |  |  |  |  |  |  |

|   | 3.4                   | Maximize Instruction Throughput             | 23        |  |  |  |  |  |  |

| 4 | Problem Definition 24 |                                             |           |  |  |  |  |  |  |

|   | 4.1                   | Part 1: C level Parallelization             | 24        |  |  |  |  |  |  |

|   |                       | 4.1.1 Loop interchange transformation       | 24        |  |  |  |  |  |  |

|   |                       | 4.1.2 Loop embedding transformation         | 25        |  |  |  |  |  |  |

|   |                       | 4.1.3 Pattern Structure                     | 26        |  |  |  |  |  |  |

|   |                       | 4.1.4 Condition Block                       | 28        |  |  |  |  |  |  |

|   |                       | 4.1.5 Result Block                          | 28        |  |  |  |  |  |  |

|   | 4.2                   | Part 2: C to CUDAC Transformation           | 30        |  |  |  |  |  |  |

|   | 4.4                   | 4.2.1 Examples                              | 30        |  |  |  |  |  |  |

|   |                       | *                                           |           |  |  |  |  |  |  |

|   |                       |                                             | 31        |  |  |  |  |  |  |

|   | 4.0                   | 4.2.3 Use of #pragma unroll                 | 34        |  |  |  |  |  |  |

|   | 4.3                   | Issues                                      | 34        |  |  |  |  |  |  |

|   | 4.4                   | Use of Patterns                             | 35        |  |  |  |  |  |  |

| 5 | Aut                   | Automatic code conversion Algorithm 37      |           |  |  |  |  |  |  |

| - | 5.1                   | The Algorithm                               | 37        |  |  |  |  |  |  |

|   | 0.1                   | 1110 1110011111111 1 1 1 1 1 1 1 1 1 1      | •         |  |  |  |  |  |  |

| 6 | Diff                  | Different Compiler Platforms 3              |           |  |  |  |  |  |  |

|   | 6.1                   | Introduction to ANTLR                       | 39        |  |  |  |  |  |  |

|   | 6.2                   | Introduction to Open64                      | 40        |  |  |  |  |  |  |

|   | 6.3                   | Introduction to SUIF                        | 41        |  |  |  |  |  |  |

| - | D1-4                  | tf Cil                                      | <b>42</b> |  |  |  |  |  |  |

| 7 |                       | Platform Comparison and reason of choice    |           |  |  |  |  |  |  |

|   | 7.1                   | What exactly does ANTLR 3 do?               | 42        |  |  |  |  |  |  |

|   |                       | 7.1.1 ANTLR 3                               | 44        |  |  |  |  |  |  |

|   |                       | 7.1.2 Target languages                      | 44        |  |  |  |  |  |  |

|   |                       | 7.1.3 Why should I use ANTLR 3?             | 44        |  |  |  |  |  |  |

| 8 | Con                   | npiler                                      | 45        |  |  |  |  |  |  |

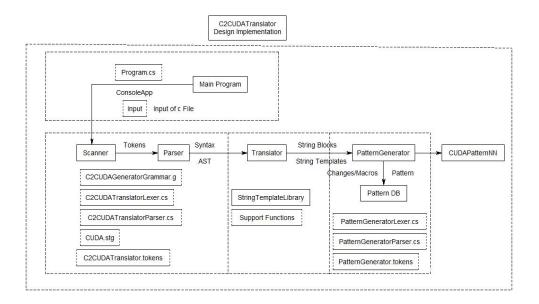

|   | 8.1                   | Compiler Modules                            | 46        |  |  |  |  |  |  |

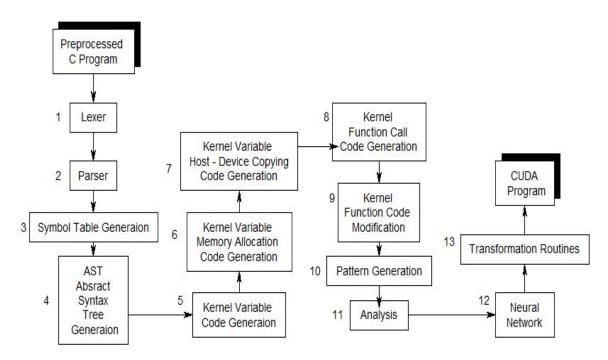

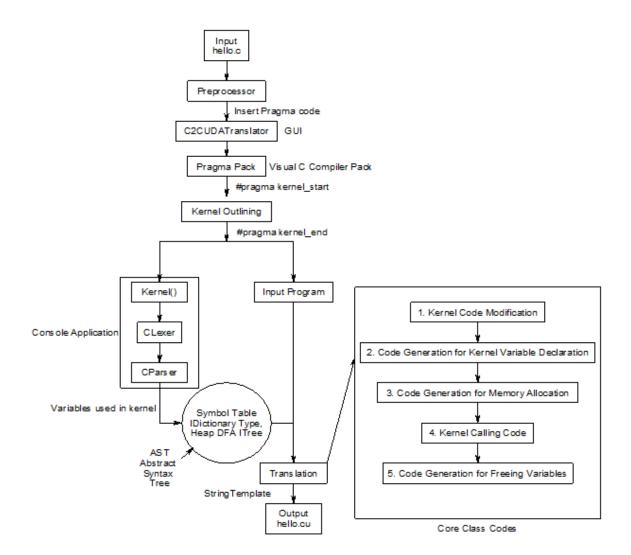

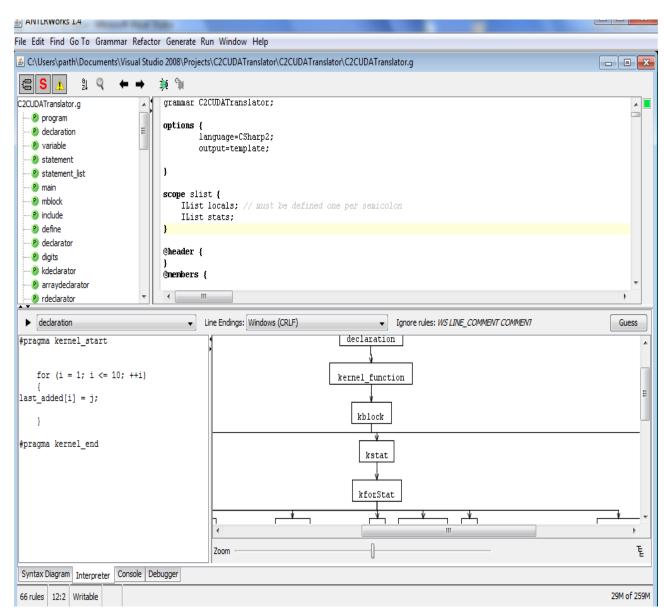

|   | 8.2                   | C2CUDATranslator Phases                     | 47        |  |  |  |  |  |  |

|   | 8.3                   | C2CUDATranslator Flow                       | 47        |  |  |  |  |  |  |

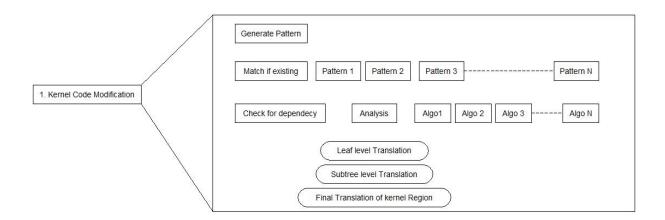

|   | 8.4                   |                                             | 49        |  |  |  |  |  |  |

|   |                       |                                             | 49        |  |  |  |  |  |  |

|   | 8.5                   | 0                                           |           |  |  |  |  |  |  |

|   | 8.6                   | Compiler Style                              | 50        |  |  |  |  |  |  |

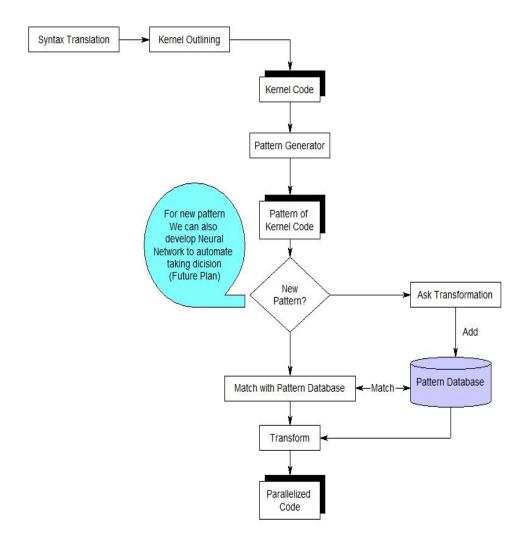

|   | 8.7                   | Pattern Learning                            | 51        |  |  |  |  |  |  |

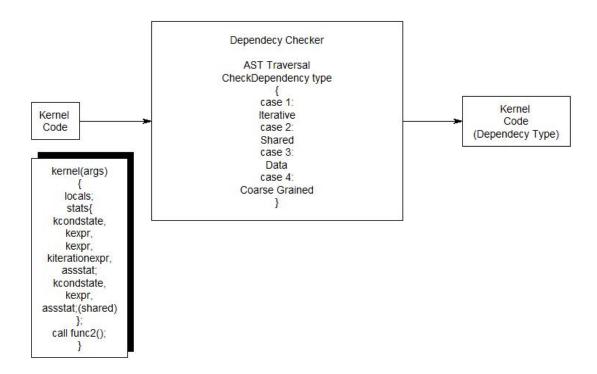

|   | 8.8                   | Dependency Checker                          | 53        |  |  |  |  |  |  |

|   |                       | 8.8.1 Dependency Analysis                   | 54        |  |  |  |  |  |  |

|   |                       | 8.8.2 Range Check                           | 56        |  |  |  |  |  |  |

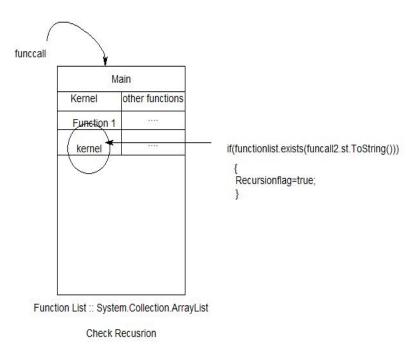

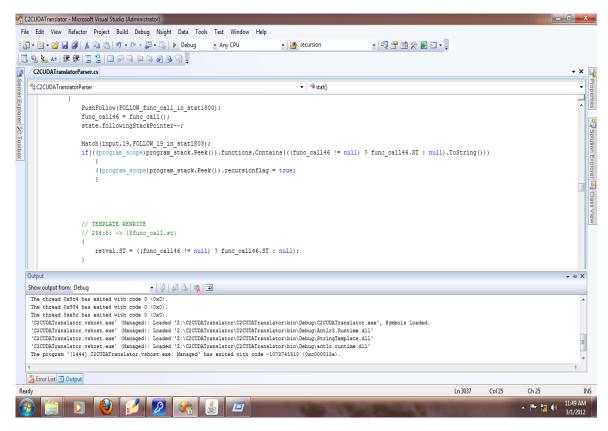

|   |                       | 8.8.3 Recursion Check                       | 56        |  |  |  |  |  |  |

|   | 8.9                   | Data Structures Used                        | 57        |  |  |  |  |  |  |

| ix |

|----|

|    |

|                                                | 8.11<br>8.12<br>8.13<br>8.14 | Interfaces used C2CUDATranslator Features Grammar Example Pattern Example Class Diagram Support Function Example | 58<br>58<br>59<br>62<br>63<br>65 |  |

|------------------------------------------------|------------------------------|------------------------------------------------------------------------------------------------------------------|----------------------------------|--|

| 9 Optimization 9.1 How to use Visual Profiler? |                              |                                                                                                                  |                                  |  |

|                                                | 9.1                          | 9.1.1 Getting started for optimization                                                                           | 66<br>66                         |  |

|                                                | 9.2                          | Maximize Memory Throughput                                                                                       | 67                               |  |

|                                                | 0.2                          | 9.2.1 Insertion of keywords for placing in memory                                                                | 67                               |  |

|                                                |                              | 9.2.2 Use of CUDAMemSet                                                                                          | 67                               |  |

|                                                |                              | 9.2.3 Asynchronous Transfers and Overlapping Transfers with Computation                                          | 67                               |  |

|                                                | 9.3                          | Decision Making                                                                                                  | 69                               |  |

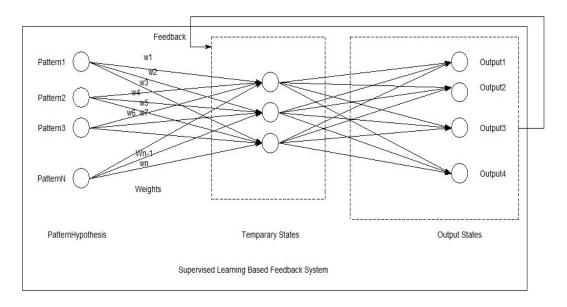

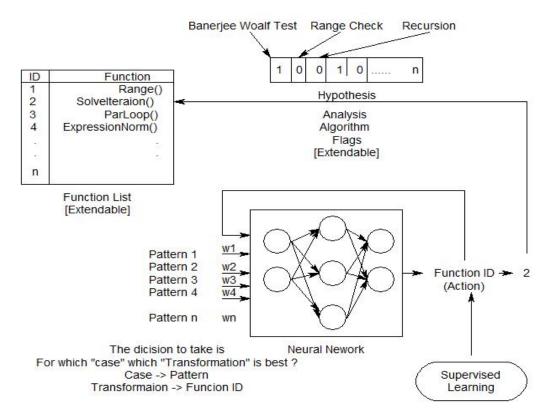

|                                                | 9.4                          | Artificial Neural Network                                                                                        | 69                               |  |

|                                                |                              | 9.4.1 Compiler Learning                                                                                          | 70                               |  |

| 10                                             | 04                           | come                                                                                                             | 71                               |  |

| 10                                             |                              | Input                                                                                                            | 71<br>72                         |  |

|                                                |                              | Output                                                                                                           | 74                               |  |

|                                                | 10.2                         | 10.2.1 Output Screenshot                                                                                         | 74                               |  |

|                                                |                              | 10.2.2 Output in words                                                                                           | 75                               |  |

|                                                |                              | 10.2.3 Parallelization Achieved                                                                                  | 78                               |  |

|                                                |                              | 10.2.4 Output of Converted Program (C2CUDATranslator)                                                            | 80                               |  |

|                                                |                              | 10.2.5 Output of Converted Program (Handwritten)                                                                 | 80                               |  |

| 11                                             | Fyol                         | luation                                                                                                          | 81                               |  |

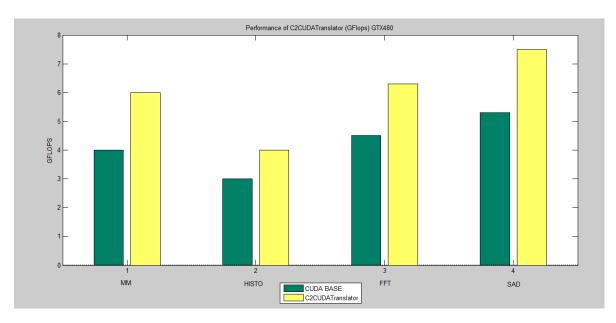

|                                                |                              | CUDA benchmarks for evaluating the C2CUDAranslator compiler                                                      | 81                               |  |

|                                                | 11.1                         | 11.1.1 Evaluation of C2CUDATranslator                                                                            | 82                               |  |

|                                                |                              |                                                                                                                  | Ŭ <b>-</b>                       |  |

| <b>12</b>                                      |                              | clusion                                                                                                          | 83                               |  |

|                                                | 12.1                         | Conclusion                                                                                                       | 83                               |  |

| 13                                             | Futi                         | ıre Scope                                                                                                        | 84                               |  |

|                                                |                              | Future Scope                                                                                                     | 84                               |  |

|                                                |                              | 13.1.1 Upcoming Features                                                                                         | 84                               |  |

|                                                |                              | 13.1.2 Pre-processor phase                                                                                       | 84                               |  |

|                                                |                              | 13.1.3 Parallelization/Analysis Phase                                                                            | 85                               |  |

|                                                |                              | 13.1.4 Compiler for OpenMP                                                                                       | 85                               |  |

|                                                |                              | 13.1.5 Compiler Learning                                                                                         | 85                               |  |

| W                                              | Web References 86            |                                                                                                                  |                                  |  |

| References                                     |                              |                                                                                                                  | 88                               |  |

| Tω                                             | Index                        |                                                                                                                  |                                  |  |

| T11(                                           | uex                          |                                                                                                                  | 89                               |  |

CONTENTS

| A Output Screenshots |                   |         | 90                                   |    |  |  |  |

|----------------------|-------------------|---------|--------------------------------------|----|--|--|--|

| В                    | User's Guide      |         |                                      |    |  |  |  |

|                      | B.1               | Getting | g Started                            | 91 |  |  |  |

|                      |                   | B.1.1   | Input and Output of C2CUDATranslator | 91 |  |  |  |

|                      | B.2               |         | DATranslator input Details           | 91 |  |  |  |

|                      |                   | B.2.1   | Kernel Outlining                     | 91 |  |  |  |

|                      |                   |         | Kernel Variables                     | 92 |  |  |  |

|                      |                   |         | Kernel local Variables               | 93 |  |  |  |

| $\mathbf{C}$         | Developer's Guide |         |                                      |    |  |  |  |

|                      | C.1               | Getting | g Started                            | 94 |  |  |  |

|                      |                   | C.1.1   | C2CUDATranslator Project Structure   | 94 |  |  |  |

|                      | C.2               |         | DATranslator development Details     | 95 |  |  |  |

|                      |                   |         | Analysis Framework                   | 95 |  |  |  |

|                      |                   |         | Translation Framework                | 95 |  |  |  |

|                      |                   |         | Use framework                        | 95 |  |  |  |

# List of Tables

| I | C2CUDA Translator Features                                  | 59 |

|---|-------------------------------------------------------------|----|

| I | CUDA benchmarks for evaluating the C2CUDAranslator compiler | 82 |

| Ι | Upcoming Features                                           | 84 |

# List of Figures

| 2.1  | CUDA Software Stack                              |

|------|--------------------------------------------------|

| 2.2  | CUDA programming model                           |

| 2.3  | CUDA Memory model                                |

| 2.4  | A set of SIMD processor with memory architecture |

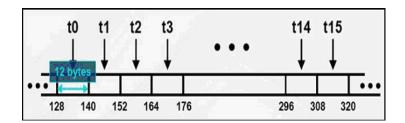

| 3.1  | A coalescing memory access                       |

| 3.2  | coalescing memory access: divergent warp         |

| 3.3  | Non- Sequential memory access                    |

| 3.4  | A coalescing memory access                       |

| 3.5  | A coalescing memory access                       |

| 3.6  | A coalescing memory access                       |

| 6.1  | ANTLRWORKS                                       |

| 6.2  | open64 Phases                                    |

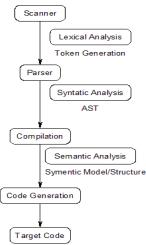

| 8.1  | General Compiler Phases                          |

| 8.2  | Compiler Modules                                 |

| 8.3  | Flow of the C2CUDA Translator                    |

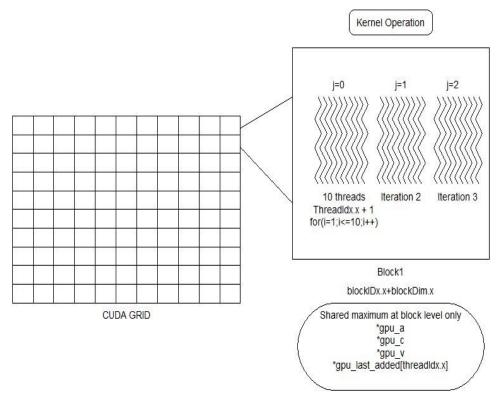

| 8.4  | Code Transformation in Kernel Region             |

| 8.5  | Compiler Style                                   |

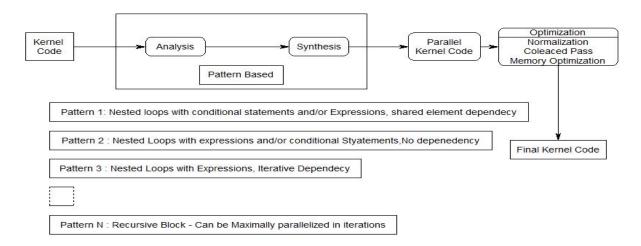

| 8.6  | Pattern Learning                                 |

| 8.7  | Dependency Checker                               |

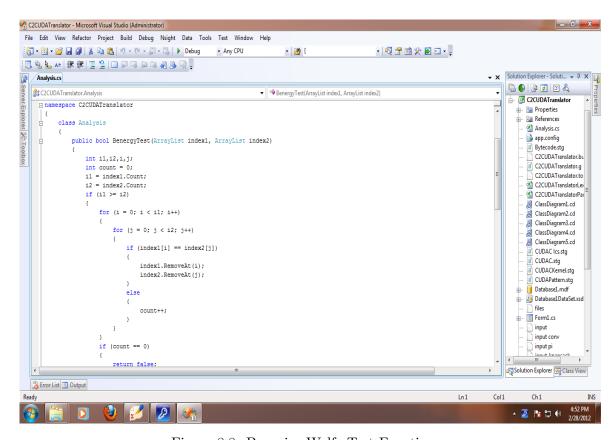

| 8.8  | Banerjee Wolfe Test Function                     |

| 8.9  | Recursion Check                                  |

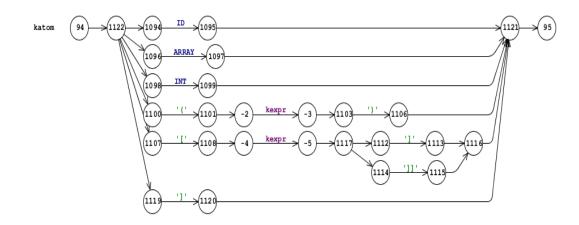

| 8.10 | Recursion Check Function                         |

|      | NFA Example                                      |

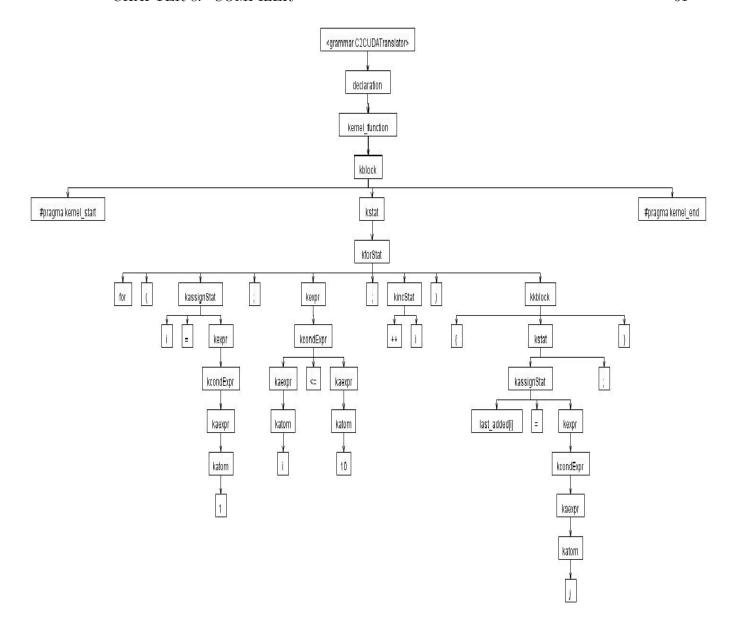

| 8.12 | Grammar Example                                  |

|      | Grammar Tree Example                             |

| 8.14 | Pattern Example                                  |

|      | Corresponding Pattern Example                    |

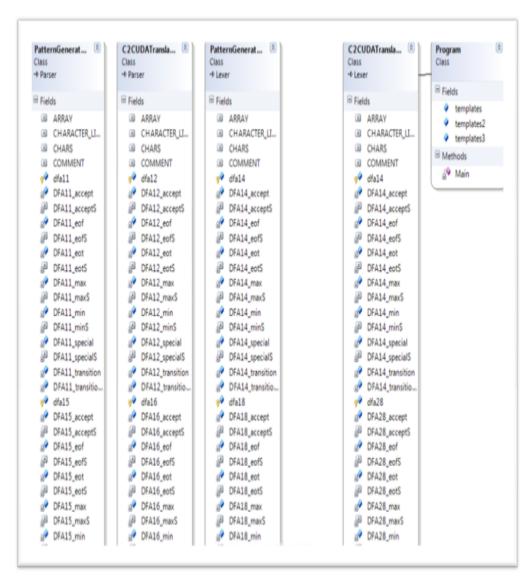

| 8.16 | Class Diagram 1                                  |

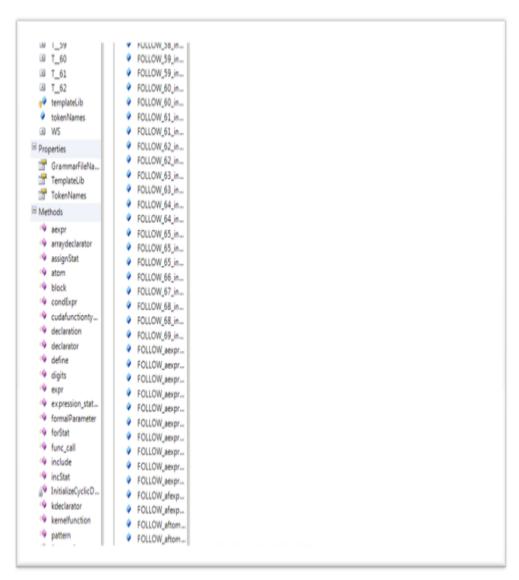

|      | Class Diagram 2                                  |

|      | Support Function Example                         |

| 9.1  | Pattern Neural Design                            |

| 9.2  | Compiler Learning                                |

| LIST O | F FIGURES                          | xiii |

|--------|------------------------------------|------|

| 10.1   | Output of C2CUDATranslator         | 74   |

| 10.2   | Knapsack Grid                      | 79   |

| 10.3   | Output of Converted Program        | 80   |

| 10.4   | Output of Handwritten Program      | 80   |

| 11.1   | Evaluation of C2CUDATranslator     | 82   |

| C.1    | C2CUDATranslator Project Structure | 95   |

# Abbreviations

ANSI American National Standards Institute

ANTLR ANother Tool for Language Recognition

AST Abstract Syntax Tree

CPU Central Processing Unit

CUDA Compute Unified Device Architecture

DARPA Defense Advanced Research Projects Agency

DFA Deterministic Finite Automaton

DRAM Dynamic Random Access Memory

FFT Fast Fourier Transform

GFLOP Giga FLoating-point OPeration

GPGPU General-Purpose computing on Graphics Processing Units

GPU Graphics Processing Unit

IEEE Institute of Electrical and Electronics Engineers

IR Intermediate Representation

LR Left to Right

MIPS Microprocessor without Interlocked Pipeline Stages

MPEG Moving Picture Experts Group

NaN Not a Number

NFA Nondeterministic Finite Automaton

NSF National Science Foundation

NVCC NVIDIA C Compiler

openMP Open Multi-Processing

PCCTS Purdue Compiler Construction Tool Set

SIMD Single Instruction Multiple Data

SUIF Stanford University Intermediate Format

# Chapter 1

# Introduction

Because of the demands of game industry, Graphics Processing Units (GPUs) have evolved from application-specific units for 3D scene rendering into highly parallel and programmable multi pipelined processors that can satisfy extremely high computational requirements at low cost. The fact that the performance of graphic processing units (GPUs) is much bigger than the central processing units (CPUs) of now-a-days [1] is hardly surprising. GPUs were formerly focused on such limited field of computing graphic scenes. Within the course of time, GPUs became very powerful and the area of use dramatically grew. So, we can come together on the term General Purpose GPU (GPGPU) denoting modern graphic accelerators. The driving force of rapid rising of the performance is computer games and the entertainment industry that evolves economic pressure on the developers of GPUs to perform a vast number of floating-point calculations within the unit of time. The research in the field of GPGPU started in late 70's [7]. Today's fastest GPUs can deliver a peak performance in the order of 500 GFLOPS [5], more than four times the performance of the fastest x86 quad-core processor. This thesis introduces a source to source transformation of c programs to CUDA Architecture. It also finds out dependencies and performs optimization for peak performance gain. Automatic evolution of kernels, independent code finding, Loop unrolling, Memory coalescing and thread scheduling are main part of concerns. IR level optimization and higher level optimizations patterns finding is important issue that may be covered by this thesis. Thesis describes parallelization patterns and CUDA C extensions from C to find out transformation rules. At least one can generate template using this transformation rules.

# 1.1 Objective of the Work

The objective of this research is to provide a better automation of the language translation of CUDA GPU to obtain better performance and to save manual efforts and time to learn the SDK and to prepare a program for CUDA environment.

## 1.2 Scope of the Work

The scope of this work is to make a translator that performs the language to language conversion for c program to CUDA C and reduces the development time.

#### 1.3 Motivation of the Work

To identify the independent computational tasks from the given C/C++ source code.

Increase the computation power by distributing the independent tasks to all the available processing elements. For this we have to parallelize the sequential code and break them in units so kernels can be made in CUDA.

# 1.4 Thesis Organization

The rest of the thesis is organized as follows.

- Chapter 2, Literature survey on CUDA, describes history of CUDA. It also describes CUDA Programming Model, Memory Architecture, and Hardware implementation.

- Chapter 3, Performance Optimization Strategies, describes various performance optimization strategies specific to CUDA, which are used to get the maximum utilization of available resources.

- **chapter 4**, Explanation of the Definition, methods for performance optimization, steps to be performed with the selected method, benefit of the software.

- **Chapter 5**, Automatic code conversion Algorithm, proposed algorithm and logic for code conversion and source to source translation.

- Chapter 6, Different Platforms, describes different platforms to develop.

- **Chapter 7**, *Platform Comparison and reason of choice*, describes comparisons of the platforms and platform choice for thesis.

- Chapter 8, Compiler Flow, describes the flow and architecture of the translator.

- **Chapter 9**, *Optimization*, describes the optimizations possible in translated program and decision taking neural design to make a decision.

- Chapter 10, Outcome, describes the inputs and outputs of the translator.

- Chapter 11, Evaluation, describes the evaluation of the translator based upon converted programs vs benchmark programs.

- Finally, in **chapter 12** concluding remarks and in **chapter 13** scope for future work is presented.

# Chapter 2

# Literature Survey

In November 2006, NVIDIA introduced CUDA(Compute Unified Device Architecture), a general purpose parallel computing architecture [5] - with a new parallel programming model and instruction set architecture - that leverages the parallel compute engine in NVIDIA GPUs to solve many complex computational problems in a more efficient way than on a CPU. NVIDIA GPUs with the new Tesla unified graphics and computing architecture run CUDA C programs and are widely available in laptops, PCs, workstations, and servers. The CUDA model is also applicable to other shared-memory parallel processing architectures, including multicore CPUs [8].

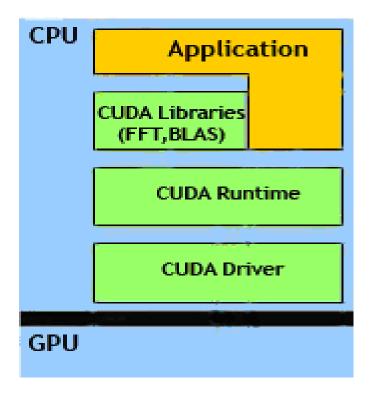

NVIDIA CUDA SDK has been designed for running parallel computations on the device hardware: it consist of a compiler, host and device runtime libraries and a driver API. CUDA software stack is composed of several layers: a hardware driver (CUDA Driver), an API and its runtime (CUDA Runtime), two higher-level mathematical libraries (CUDA Libraries) of common usage as shown in fig 2.1.

GPU performance is influenced by the architectural organization of the hardware platform. NVIDIA suggests that achieving the highest GPU occupancy and optimizing the use of the memory hierarchy are the two main factors behind GPU performance [2]. In fact, both of them are related since maximizing the occupancy can help to cover latency during global memory loads. Researchers represent several experiments aimed at analyzing their relative importance. Results indicate that code transformations that target efficient memory usage are the major determinant of actual performance. Overall, they ensure the best performance even if some resources remain underutilized. Therefore, maximizing occupancy should be examined at a later stage in the compilation process, once data related issues have been properly addressed. NVIDIA compiler NVCC can optimize code but the best optimized code is one should write at assembly level. But it looks very difficult in big algorithms and projects. So to find out occupancy is important issue.

Figure 2.1: CUDA Software Stack

# 2.1 Design goal

- Scale to 100's of cores, 1000's of parallel threads.

- Focus on the task of parallelization of the algorithms rather than spending time on their implementation.

- Support heterogeneous computation where applications use both the CPU and GPU. Serial portions of applications are run on the CPU, and parallel portions are run on

to the GPU.

- Enable heterogeneous systems (CPU + GPU) CPU and GPU are separate devices with separate DRAMs [2].

- Generate a template based on calculated occupancy.

- Conversion of C code in a way it fits in the CUDA C template.

- Optimize the source code and measure the performance GPU & CPU of the program [4].

## 2.1.1 Advantages

Advantages of CUDA over the traditional approach to GPGPU computing:

- More efficient data transfers between system and video memory.

- Faster downloads and read backs to and from the GPU.

- Scattered reads code can read from arbitrary addresses in memory.

- Shared memory CUDA exposes a fast shared memory region (16KB in size) that can be shared amongst threads. This can be used as a user-managed cache, enabling higher bandwidth than is possible using texture lookups.

- Full support for integer and bitwise operations.

- Support for integer texture lookups.

- Programming interface of CUDA applications is based on the standard C language with extensions, which facilitates the learning curve of CUDA operations.

- Support for integer texture lookups.

- Programming interface of CUDA applications is based on the standard C language with extensions, which facilitates the learning curve of CUDA.

#### 2.2 Limitation

- Threads should be running in groups of at least 32 for best performance, with total number of threads numbering in the thousands. Branches in the program code do not impact performance significantly, provided that each of 32 threads takes the same execution path; the SIMD execution model becomes a significant limitation for any inherently divergent task.

- Texture rendering is not supported.

- It uses a recursion-free, function-pointer-free subset of the C language, plus some simple extensions. However, a single process must run spread across multiple disjoint memory spaces, unlike other C language runtime environments.

- For double precision there are no deviations from the IEEE 754 standard. In single

precision, Denormals and signalling NaNs are not supported; only two IEEE rounding

modes are supported and those are specified on a per instruction basis rather than in

a control word and the precision of division square root are slightly lower than single

precision.

# 2.3 CUDA Programming Model

A CUDA program consists of one or more phases that are executed on either the host (CPU) or a device such as a GPU. The GPU is viewed as a compute device: that is a coprocessor to the CPU(host), has its own DRAM(device Memory), Runs many threads in parallel.[4] Data parallel portion of application are executed on the device as kernels which run in parallel on many threads. Difference between GPU and CPU thread [8] are:

- GPU threads are extremely lightweight and require very little creation overhead.

- GPU needs 1000s of threads for full efficiency where as multicore cpu needs only a

few.

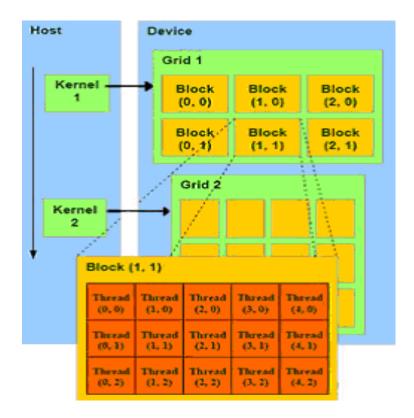

A kernel is executed as a grid of thread blocks. A thread block is a batch of thread that can cooperate with each other by efficiently sharing data through shared memory, and synchronizing there execution for hazard free shared memory accesses. There is a limit to the number of threads per block, since all threads of a block are expected

Figure 2.2: CUDA programming model

to reside on the same processor core and must share the limited memory resources of that core. Blocks are organized into a one-dimensional or two-dimensional grid of thread blocks as illustrated by Figure 2.2. The number of thread blocks in a grid is usually dictated by the size of the data being processed or the number of processors in the system. It must be possible to execute thread block in any order, in parallel or in series. This independence requirement allows thread blocks to be scheduled in any order across any number of cores, enabling programmers to write code that scales with the number of cores. For efficient cooperation, the shared memory is expected to be a low-latency memory near each processor core (much like an L1 cache) and thread synchronization is expected to be lightweight.

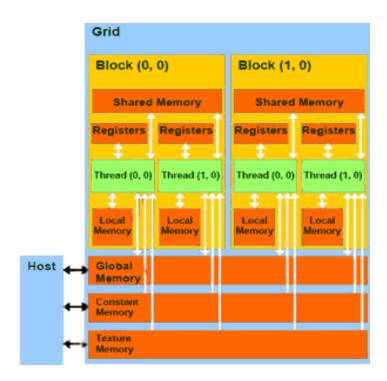

## 2.4 CUDA Memory Model

CUDA threads may access data from multiple memory spaces during their execution as illustrated by Figure 2.3. Each thread has private local memory. Each thread block has shared memory visible to all threads of the block and with the same lifetime as the block. All threads have access to the same global memory. There are also two additional read-only memory spaces accessible by

Figure 2.3: CUDA Memory model

all threads: the constant and texture memory spaces. The global, constant, and texture memory spaces are optimized for different memory usages Texture memory also offers different addressing modes, as well as data filtering, for some specific data formats. The global, constant, and texture memory spaces are persistent across kernel launches by the same application [5].

**Local Memory:** is small volume of memory, which can be accessed only by one streaming processor. The local memory space resides in device memory, so local memory accesses have same high latency and low bandwidth as global memory accesses.

Local memory accesses only occur for some automatic variables. Automatic variables that the compiler is likely to place in local memory are [8]:

- Arrays for which it cannot determine that they are indexed with constant quantities,

- Large structures or arrays that would consume too much register space,

- Any variable if the kernel uses more registers than available (this is also known as register spilling).

Global Memory: the largest volume of memory available to all multiprocessors in a GPU, from 256 MB to 1.5 GB in modern solutions (and up to 4 GB in Tesla). It offers high bandwidth, over 100 GB/s for top solutions from NVIDIA, but it suffers from very high latencies (several hundred cycles). Non-catchable supports general load and store instructions, and usual pointers to memory.

Global memory resides in device memory and device memory is accessed via 32-, 64-, or 128-byte memory transactions. These memory transactions must be naturally aligned: Only the 32-, 64-, or 128-byte segments of device memory that are aligned to their size (i.e. whose first address is a multiple of their size) can be read or written by memory transactions.

**Shared Memory:** is 16-KB memory shared between all streaming processors in a multiprocessor. Because it is on-chip, the shared memory space is much faster than the local and global memory spaces.

To achieve high bandwidth, shared memory is divided into equally-sized memory modules, called banks, which can be accessed simultaneously. Any memory read or write request made of n addresses that fall in n distinct memory banks can therefore be serviced simultaneously, yielding an overall bandwidth that is n times as high as the bandwidth of a single module.

Constant Memory: is a 64 KB, read only memory for all multiprocessors. It's cached by 8 KB for each multiprocessor. The constant memory space resides in device memory. A constant memory request for a warp is first split into two requests, one for each half-warp, that are issued independently. A request is then split into as many separate requests as there are different memory addresses in the initial request, decreasing throughput by a

factor equal to the number of separate requests. The resulting requests are then serviced at the throughput of the constant cache in case of a cache hit, or at the throughput of device memory otherwise. This memory is rather slow latencies of several hundred cycles, if there are no required data in cache.

Texture Memory: space resides in device memory and is cached in texture cache, so a texture fetch costs one memory read from device memory only on a cache miss, otherwise it just costs one read from texture cache. The texture cache is optimized for 2D spatial locality, so threads of the same warp that read texture addresses that are close together in 2D will achieve best performance. Also, it is designed for streaming fetches with a constant latency; a cache hit reduces DRAM bandwidth demand but not fetch latency.

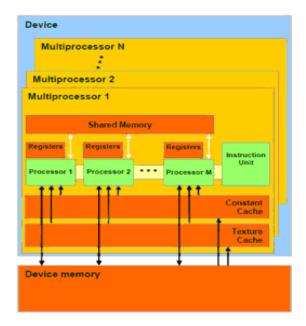

## 2.5 Hardware Implementation: Memory Architecture

The local, global, constant and texture spaces are regions of device memory. Each multiprocessor has following memory space as shown in fig 2.4

Figure 2.4: A set of SIMD processor with memory architecture

• A set of 32-bit registers per processor.

- On-chip shared memory where the shared memory space resides.

- A read-only constant cache to speed up access to the constant memory space.

- A read-only texture cache to speed up access to the texture memory space.

# 2.6 Hardware Implementation: Execution Model

- Each thread block of grid is split into warps that get executed by one multiprocessor, device processes only one grid at a time.

- Each thread block is executed by only one multiprocessor so that the shared memory space resides in the on chip shared memory and registers are allocated among the threads.

- A multiprocessor can execute several blocks concurrently. Shared memory and registers are allocated among the threads of all concurrent blocks. So, decreasing shared memory usage and register usage increases number of blocks that can run concurrently.

# Chapter 3

# Performance Optimization Strategies

Performance optimization revolves around four basic strategies:

- Maximize parallel execution to achieve maximum utilization;

- Optimize memory usage to achieve maximum memory throughput;

- Optimize Execution configuration;

- Optimize instruction usage to achieve maximum instruction throughput.

Which strategies will yield the best performance gain for a particular portion of an application depends on the performance limiters for that portion, optimizing instruction usage of a kernel that is mostly limited by memory accesses will not yield any significant performance gain. Optimization efforts should therefore be constantly directed by measuring and monitoring the performance limiters, for example using the CUDA profiler. Also, comparing the floating-point operation throughput or memory throughput - whichever makes more sense of a particular kernel to the corresponding peak theoretical throughput of the device indicates how much room for improvement there is for the kernel.

### 3.1 Maximize Utilization

To get the maximum utilization of the available resources, application should be parallelized in such a way that application keeps various components of the system busy most of the time.

### 3.1.1 Application Level

At a high level, the application should maximize parallel execution between the host, the devices, and the bus connecting the host to the devices, by using asynchronous functions calls and streams. It should assign to each processor the type of work it does best: serial workloads to the host; parallel workloads to the devices [11].

For parallel execution program is divided into threads, this threads need to share data with each other, there are two cases:

- If this threads belong to same block, they should use syncthreads() and share data through shared memory.

- If threads belong to different blocks, they must share data through global memory.

In this case two separate kernel invocations are required, one for writing to and one for reading from global memory.

The second case adds extra overhead of kernel invocations and also increases global memory traffic. Its occurrence should therefore be minimized by mapping the algorithm to the CUDA programming model in such a way that the computations that require inter-thread communication are performed within a single thread block as much as possible.

#### 3.1.2 Device Level

At a lower level, the application should maximize parallel execution between the multiprocessors of a device [13].

For devices of compute capability 1.x, only one kernel can execute on a device at one time,

so the kernel should be launched with at least as many thread blocks as there are multiprocessors in the device. For devices of compute capability 2.0, multiple kernels can execute concurrently on a device, so maximum utilization can also be achieved by using streams to enable enough kernels to execute concurrently.

#### 3.1.3 Multiprocessor Level

At an even lower level, the application should maximize parallel execution between the various functional units within a multiprocessor [13].

To maximize utilization, a GPU multiprocessor relies on thread-level parallelism. Utilization is therefore directly dependent on the number of resident warps. At every instruction issue time, a warp scheduler selects a warp that is ready to execute, if any, and issues the next instruction to the active threads of the warp. The number of clock cycles it takes for a warp to be ready to execute its next instruction is called latency, and full utilization is achieved when the warp scheduler always has some instruction to issue for some warp at every clock cycle during that latency period, or in other words, when the latency of each warp is completely hidden by other warps. How many instructions are required to hide latency depends on the instruction throughput.

If all input operands are registers, latency is caused by register dependencies. In the case of a back-to-back register dependency (i.e., some input operand is written by the previous instruction), the latency is equal to the execution time of the previous instruction and the warp scheduler must schedule instructions for different warps during that time. If warp is waiting at some memory fence or synchronization point at that time warp is not ready to execute its next instruction. A synchronization point can force the multiprocessor to idle as more and more warps wait for other warps in the same block to complete execution of instructions prior to the synchronization point. Having multiple resident blocks per multiprocessor can help reduce idling in this case, as warps from different blocks do not need to wait for each other at synchronization points.

The number of blocks and warps residing on each multiprocessor for a given kernel call depends on the execution configuration of the call, the memory resources of the multiprocessor, and the resource requirements of the kernel. To assist programmers in choosing

thread block size based on register and shared memory requirements, the CUDA Software Development Kit provides a spreadsheet, called the CUDA Occupancy Calculator, where occupancy is defined as the ratio of the number of resident warps to the maximum number of resident warps [13].

The performance of an application also depends on the kernel code. The number of threads per block should be chosen as a multiple of the warp size to avoid wasting of computing resources with under-populated warps as much as possible.

## 3.2 Maximize Memory Throughput

Memory optimizations are the most important area for performance. The goal is to maximize the use of the hardware by maximizing bandwidth. Bandwidth is the best served by using as much fast memory and as little slow-access memory as possible [14]. This section discusses best way to set up data items to use the memory effectively.

#### 3.2.1 Data Transfer between Host and Device

There are various ways to transfer data between host and device, which method provides best performance depend on the type of application and type of data, the application has to process.

#### Minimize data transfer between the host and the device.

Applications should be structure in such a way that minimizes data transfer between the host and the device. One way to accomplish this is to move more code from the host to the device, even if that means running kernels with low parallelism computations. Intermediate data structures may be created in device memory, operated on by the device, and destroyed without ever being mapped by the host or copied to host memory.

#### Group transfers

Also, because of the overhead associated with each transfer, batching many small transfers into a single large transfer always performs better than making each transfer separately.

#### Page-Locked Data Transfers

On systems with a front-side bus, higher performance for data transfers between host and device is achieved by using page-locked host. In addition, when using mapped page-locked memory, there is no need to allocate any device memory and explicitly copy data between device and host memory. Data transfers are implicitly performed each time the kernel accesses the mapped memory. For maximum performance, these memory accesses must be coalesced as with accesses to global memory. Assuming that they are and that the mapped memory is read or written only once, using mapped page-locked memory instead of explicit copies between device and host memory can be a win for performance.

On systems where device memory and host memory are physically the same, any copy between host and device memory is not required at that time mapped page-locked memory should be used. Applications can check whether a device is integrated or not by calling cudaGetDeviceProperties() and checking the integrated property or checking the CU DEVICE ATTRIBUTE INTEGRATED attribute using cuDeviceGetAttribute(). cudaMallocHost() allows allocation of page-locked ("pinned") host memory. Page-locked memory enable highest cudaMemcpy performance up to 3.2 GB/s on PCI-e x16 Gen1, and 5.2 GB/s on PCI-e X16 Gen2.

Allocating too much page-locked memory can reduce overall system performance, so we need to test our system and application to find their limits.

#### Asynchronous Transfers and Overlapping Transfers with Computation

We can transfer data between host and device using cudaMemcpy(), which is the blocking transfers, whereas cudaMemcpyAsync() provides non-blocking transfers in which control is returned immediately to the host thread. The asynchronous transfer requires pinned host memory and streamID (A stream is a sequence of operations that are performed in order on the device).

We can overlap data transfers and computation using asynchronous transfers. There are two ways to do this first, on all CUDA-enabled devices; it is possible to overlap host computation with asynchronous data transfers and with device computations. For example, Listing 3.1 demonstrates how host computation in the routine cpu Function() is performed while data is transferred to the device and a kernel using the device is executed.

The last argument to the cudaMemcpyAsync() function is the stream ID, which in this case uses the default stream, stream 0. The kernel also uses the default stream, and it will not

begin execution until the memory copy completes; therefore, no explicit synchronization is needed. Because the memory copy and the kernel both return control to the host immediately, the host function cpuFunction() overlaps their execution. In Listing 4.1, the memory copy and kernel execution occur sequentially.

```

cudaMemcpyAsync(a_d, a_h, size, cudaMemcpyHostToDevice, 0);

kernel<<<grid, block>>>(a_d);

cpuFunction();

```

Second, on devices that are capable of concurrent copy and execute, it is possible to overlap kernel execution on the device with data transfers between the host and the device. Whether a device has this capability is indicated by the deviceOverlap field of a cudaDeviceProp. On devices that have this capability, the overlap once again requires pinned host memory, and, in addition, the data transfer and kernel must use different, non-default streams (streams with non-zero stream IDs). Non-default streams are required for this overlap because memory copy, memory set functions, and kernel calls that use the default stream begin only after all preceding calls on the device (in any stream) have completed, and no operation on the device (in any stream) commences until they are finished. Listing 3.2 illustrates the basic technique.

```

cudaStreamCreate(&stream1); cudaStreamCreate(&stream2);

cudaMemcpyAsync(a_d, a_h, size, cudaMemcpyHostToDevice, stream1);

kernel<<<grid, block, 0, stream2>>>(otherData_d);

```

#### Listing 3.2 Concurrent copy and execute

In above listing, two streams are created and used in the data transfer and kernel executions as specified in the last arguments of the cudaMemcpyAsync call and the kernel's execution configuration. This technique could be used when the data dependency is such that the data can be broken into chunks and transferred in multiple stages, launching multiple kernels to operate on each chunk as it arrives.

#### Zero Copy

Zero copy is a feature that was added in version 2.2 of the CUDA Toolkit [14]. It allows GPU threads to directly access host memory. For this purpose, it requires mapped pinned (non-pageable) memory. On integrated GPUs, mapped pinned memory is always gives best

performance because it avoids redundant copies as integrated GPU and CPU memory are physically the same. Zero copy can be used in place of streams because kernel-originated data transfers automatically overlap kernel execution without the overhead of setting up and determining the optimal number of streams. The host code in Listing 3.3 shows how zero copy is typically set up.

```

float *a_h, *a_map; ....

cudaGetDeviceProperties(&prop, 0);

if(!prop.canMapHostMemory) exit(0); cudaSetDeviceFlags(cudaDeviceMapHost);

cudaHostAlloc((void)&a_h, nBytes, cudaHostAllocMapped);

cudaHostGetDevicePointer((void )&a_map, (void )a_h, 0);

kernel<<<gri>gridSize, blockSize>>>(a_map);

```

### Listing 3.3 Zero-copy host code

In above code, cudaGetDeviceProperties is used to check that device supports mapping host memory to the device's address space. cudaSetDeviceFlags() are used to map page-locked memory. cudaHostAlloc() is used to allocate page-locked mapped memory, and cudaHost-GetDevicePointer() is used to get the pointer to the mapped device address space.

#### 3.2.2 Optimize Memory Access Patterns

Performance of the system also depends on bandwidth. Bandwidth is one of the most important factor for performance. It goes on to calculate theoretical bandwidth which is in the order of hundreds of gigabytes per second. Where as Effective bandwidth can vary by an order of magnitude depending on access pattern, so need to optimize access patterns to get:

#### Coalesced global memory accesses

The simultaneous global memory accesses by each thread of a half-warp (16 threads on G80) during the execution of a single read or write instruction will be coalesced into a single access if:

- The size of the memory element accessed by each thread is either 4, 8, or 16 bytes.

- The elements form a contiguous block of memory.

- The Nth element is accessed by the Nth thread in the half-warp.

- The address of the first element is aligned to 16 times the element's size.

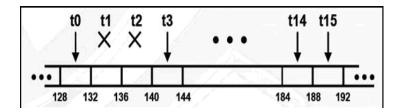

- Coalescing happens even if some threads do not access memory (divergent warp).

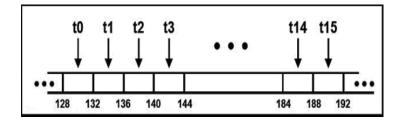

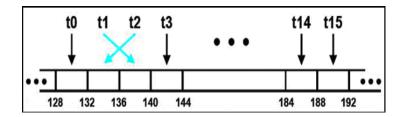

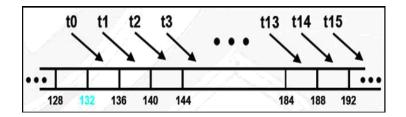

Figures 3.1 - 3.5 shows the different coalescing and Non-coalescing global memory access patterns.

Figure 3.1: A coalescing memory access

Figure 3.2: coalescing memory access: divergent warp

Figure 3.3: Non- Sequential memory access

We have to follow following guideline to avoid non-coalescing memory access.

- For irregular read patterns, texture fetches can be a better alternative to global memory reads.

- If all threads read the same location, use constant memory.

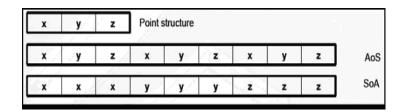

- For sequential access patterns, but a structure of size 4, 8, or 16 bytes:

Use a Structure of Array in stand of Array of Structures as shown in fig. 3.6.

Force structure alignment using align(X), where X=4, 8, or 16.

Use shared memory to achieve coalescing. (divergent warp).

Maximize the use of shared memory Because it is on-chip, shared memory is much faster than local and global memory. In fact, uncached shared memory latency is roughly 100x lower than global memory latency-provided there are no bank conflicts between the threads.

# 3.3 Execution configuration optimization

To get the maximum performance it is important to design the application to use threads and blocks in a way that get maximum utilization of available resources. A key concept in

Figure 3.4: A coalescing memory access

Figure 3.5: A coalescing memory access

this effort is occupancy, which is explained in the following sections.

# 3.3.1 Occupancy

Occupancy is the ratio of the number of active warps per multiprocessor to the maximum number of possible active warps. Another way to view occupancy is the percentage of the hardware's ability to process warps that is actively in use [11]. Higher occupancy does not always equate to higher performance - there is a point above which additional occupancy does not improve performance. However, low occupancy always interferes with the ability to hide memory latency, resulting in performance degradation.

Figure 3.6: A coalescing memory access

# 3.4 Maximize Instruction Throughput

If programmer knows, how instructions are executed then it is possible to apply low level optimizations that can be useful. It is good practices to apply lower level optimization after all higher-level optimization have been completed. To maximize instruction throughput the application should [13]:

- Minimize the use of arithmetic instructions with low throughput; this includes trading

precision for speed when it does not affect the end result, such as using intrinsic

instead of regular functions, single-precision instead of double precision, or flushing

the normalized numbers to zero.

- Minimize divergent warps caused by control flow instructions.

- Reduce the number of instructions, for example, by optimizing out synchronization points whenever possible or by using restricted pointers.

Here, throughput is given in number of operations per clock cycle per multiprocessor. For a warp size of 32, one instruction results in 32 operations. Therefore, if T is the number of operations per clock cycle, the instruction throughput is one instruction every 32/T clock cycles. All throughputs are for one multiprocessor. They must be multiplied by the number of multiprocessors in the device to get throughput for the whole device.

# Chapter 4

# Problem Definition

To optimize process we may like to make faster algorithm. But compiler on GPU NVCC may fail in converting proper optimized assembly code. To solve this one may write whole algorithm in assembly language. But it looks difficult for huge projects. We may prepare the tool that converts the C code in CUDA C but with proper optimization.

For .cu files we specify a header file, containing host functions in it. Then, include that header file in other .cu or .cpp files. The linker will do the rest. It is nothing different than having multiple plain .cpp files in project. It may possible to star with some example programs in c and to convert them in CUDA C and finding transformation rules.

# 4.1 Part 1: C level Parallelization

# 4.1.1 Loop interchange transformation

```

Before Parallelization: for ( i = 0 ; i < 200 ; i++ ) { for (j = 0 ; j <= 100 ; j++ ) { A[i][j] = A[i-1][j] + B[i][j]; }

```

```

After Parallelization: for ( j = 0 ; j <= 100 ; j++ )

{ for ( i =0 ; i < 200 ; i++ )

{ A[i][j] = A[i-1][j] + B[i][j];  }

}

```

# 4.1.2 Loop embedding transformation

```

Before Parallelization:

for (i=0;i<100;i++)

{

do_something();

}

....

void do_something()

{

procedure body

}

After Parallelization:

....

do_something2();

....

void do_something2()

{

int i;

for(i=0;i<100;i++)

{

procedure body

```

}

Both above transformations differ quite substantially, and therefore, using standard approaches, two separate programs would have to be written for each of them. This can be avoided if we properly organize the process of applying a transformation.

The translation is divided into 3 distinct stages:

- Code selection stage: In this stage the engine searches for code that has a strictly specified structure (that matches a specified pattern). Each fragment that matches this pattern is a candidate for the transformation.

- Conditions checking stage: Transformations can pose other (non-structural) restrictions on a matched code fragment. These restrictions include, but are not limited to, conditions on data dependencies and properties of index variables.

- Transformation stage: Code fragments that matched the specified structure and additional conditions are replaced by new code, which has the same semantics as the original code.

### 4.1.3 Pattern Structure

```

PATTERN

{

description of the code selection stage

}

CONDITIONS

{

additional constraints

}

RESULT

{

description of the new code

```

}

# Pattern block for the loop interchange transformation

```

PATTERN

{

VAR x, y;

for (x=EXPR(1);BOUND(1,x);STEP_EXPR(2,x))

{

for (y=EXPR(1);BOUND(2,y);STEP_EXPR(3,y))

{

STMTLIST(1);

}

}

```

# Pattern block for the loop embedding transformation

```

PATTERN

{

VAR x;

for (x=EXPR(1);BOUND(1,x);STEP_EXPR(2,x))

{

PROCCALL(1, p_pat);

}

void p_pat()

{

STMTLIST(1);

}

```

### 4.1.4 Condition Block

A conditions block contains additional conditions that are imposed on code that was elected in the previous stage. These conditions can be divided into 3 categories:

- Type properties: This category includes requirements such as "is this expression a constant?", "does this statement contain a procedure call?" or 'does this expression have side effects?".

- Structural properties: In case of some structural properties it is not desirable to have to specify them in the pattern block. Most importantly, if we had to specify the existence or absence of control transfer statements (break, continue and return statements) in the pattern block, we would severely restrict the generality of the descriptions of transformations. Therefore, extra conditions that test for these structural properties are necessary.

- Data dependencies:: Data dependencies are vital in testing for the legality of code transformations. Depending on the type of transformation we must be able to test or different following properties of data dependencies.

# Condition block for the loop interchange transformation

```

CONDITIONS

{

stmtlist_has_no_unsafe_jumps(1);

not(dep(* direction=(<,>)

between stmtlist 1 and stmtlist 10));

}

```

### 4.1.5 Result Block

The result block uses the same part of the transformation language as used in the pattern block. Also a number of the result block specific elements are allowed. These include for example support for creation of new variables in the transformed code. Also strict control over the data type of these newly created variables is possible. The examples below demonstrate the transformation block specification.

# Result block for the loop interchange transformation

```

RESULT

{

VAR x, y;

for (y=EXPR(1);BOUND(2,y);STEP_EXPR(3,y))

{

for (x=EXPR(1);BOUND(1,x);STEP_EXPR(2,x))

{

STMTLIST(1);

}

}

}

```

# Result block for the loop embedding transformation

```

RESULT

{

PROCCALL(1, p_transformation);

}

void p_transformation()

{

VAR x;

for (x=EXPR(1);BOUND(1,x);STEP_EXPR(2,x))

{

STMTLIST(1);

}

}

```

# 4.2 Part 2: C to CUDAC Transformation

# 4.2.1 Examples

# C Program structure

```

#include <stdio.h>

int add (int,int); /* function prototype for add */

void main() {

printf("\%d",add(3));

int add(int i, int j)

{

return i+j;

}

CUDA C Program structure #include <stdio.h>

#include <cuda.h>

\#define N 512

__global__ void add( int*a, int*b, int*c )

int main(void)

int *a, *b, *c; //host copies of a, b, c

int *dev_a, *dev_b, *dev_c; //device copies of a, b, c

int size = N * sizeof( int); //we need space for 512 integers

// allocate device copies of a, b, c

cudaMalloc( (void**)&dev_a, size );

cudaMalloc( (void**)&dev_b, size );

cudaMalloc( (void**)&dev_c, size );

a = (int^*) malloc(size);

b = (int^*)malloc(size);

c = (int^*) malloc(size);

random_ints(a, N);

```

```

random_ints(b, N);

// copy inputs to device

cudaMemcpy( dev_a, a, size, cudaMemcpyHostToDevice);

cudaMemcpy( dev_b, b, size, cudaMemcpyHostToDevice);

// launch add() kernel with N

add <<< N,N >>> (dev_a, dev_b, dev_c);

// copy device result back to host copy of c

cudaMemcpy( c, dev_c, size, cudaMemcpyDeviceToHost);

free(a);

free(b);

free(c);

cudaFree( dev_a);

cudaFree( dev_b);

cudaFree( dev_c);

return0;

__global__ void add( int*a, int*b, int*c )

int index = threadIdx.x + blockIdx.x * blockDim.x;

c[index] = a[index] + b[index];

}

```

This is sample program for adding two numbers.

# 4.2.2 Patterns

# **Program Structure**

# C Program

```

#include"stdio.h"

```

.... Function declarations .

```

void main()

{

int i;// var declarations

.... Function() ....

functions that run on CPU

CUDA C Program

#include"stdio.h"

#include"cuda.h"

\dots _host__Function declarations

__global__ kernel Function declarations

int void main()

int i;// var declarations ....

Function() ....

Kernel function <<>>() ....

return 0;

}

Functions that run on CPU

Kernel functions that run on GPU

```

# Declaration

```

a.> Variable Declaration C Program

int a, b;

CUDA C Program

int *a, *b, *c; //host copies of a, b, c

int *dev_a, *dev_b,*dev_c;//device copies of a, b, c

cudaMalloc( (void**)&dev_a, size );

cudaMalloc( (void**)&dev_b, size );

```

```

cudaMalloc( (void**)&dev_c, size );

a = (int*)malloc( size );

b = (int*)malloc( size );

c = (int*)malloc( size );

b.> Function Declaration

C Program

int add (int,int); /* function prototype for add */

CUDA C Program

__global__ void add( int *a, int *b, int *c );

```

### texture declaration

texture<Type, Dim, ReadMode> texRef;

- Type specifies the type of data that is returned when fetching the texture; Type is restricted to the basic integer and single-precision floating-point types and any of the 1-, 2-, and 4-component vector types;

- Dim specifies the dimensionality of the texture reference and is equal to 1, 2, or 3; Dim is an optional argument which defaults to 1;

- ReadMode is equal to cudaReadModeNormalizedFloat or cudaReadModeElement-Type; if it is cudaReadModeNormalizedFloat and Type is a 16-bit or 8-bit integer type, the value is actually returned as floating-point type and the full range of the integer type is mapped to [0.0, 1.0]

- For unsigned integer type and [-1.0, 1.0] for signed integer type; for example, an unsigned 8-bit texture element with the value 0xff reads as 1; if it is cudaReadModeElementType, no conversion is performed; ReadMode is an optional argument which defaults to cudaReadModeElementType.

# 4.2.3 Use of #pragma unroll

The #pragma unroll directive however can be used to control unrolling of any given loop. It must be placed immediately before the loop and only applies to that loop. It is optionally followed by a number that specifies how many times the loop must be unrolled.

```

#pragma unroll 5 for (int i = 0; i < n; ++i)

```

the loop will be unrolled 5 times. The compiler will also insert code to ensure correctness (in the example above, to ensure that there will only be n iterations if n is less than 5, for example). It is up to the programmer to make sure that the specified unroll number gives the best performance.

#pragma unroll 1 will prevent the compiler from ever unrolling a loop. If no number is specified after #pragma unroll, the loop is completely unrolled if its trip count is constant, otherwise it is not unrolled at all.

# 4.3 Issues

- a. One issue was that the CUDA compiler does not like long expressions. In initial tests, the evolved programs were written as a single expression. However, when the length of the expression was increased the compilation time increased dramatically. This is presumably because they are difficult to optimize.

- b. Another issue is that functions with many input variables will cause the compilation to fail, with the compiler complaining that it had been unable to allocated sufficient registers. In initial development, we had passed all the inputs in the training set to each individual regardless of if the expression used them. This worked well for small numbers of inputs, however the training set that was used to test the system contains 41 columns. The solution to this problem was to pass the function only the inputs that it used. However, this requires each function to be executed with a different parameter configuration. Conveniently, the CUDA.Net interface does allow this, as the function call can be generated dynamically at run time. The other issue here is that all/many inputs may be needed to solve a problem. It is hoped that this is a

compiler bug and that it will be resolved in future updates to CUDA.

### c. Restrictions

- (1) \_\_device\_\_ and \_\_global\_\_ functions do not support recursion.

- (2) \_\_device\_\_ and \_\_global\_\_ functions cannot declare static variables inside their body.

- (3) \_\_device\_\_ and \_\_global\_\_ functions cannot have a variable number of arguments.

- (4) \_\_device\_\_ functions cannot have their address taken; function pointers to \_\_global\_\_ functions, on the other hand, are supported.

- (5) The \_\_global\_\_ and \_\_host\_\_ qualifiers cannot be used together.

- (6) \_global\_ functions must have void return type.

- (7) Any call to a \_\_global\_\_ function must specify its execution configuration.

- (8) \_\_global\_\_ function is asynchronous, meaning it returns before the device has completed its execution.

- (9) A call to a \_\_global\_\_ function parameters are currently passed via shared memory to the device and limited to 256 bytes.

# 4.4 Use of Patterns

• Patterns help us describe expert solutions to parallel programming

- They give us a language to describe the architecture of parallel software.

- They provide a roadmap to the frameworks we need to support general purpose programmers.

- And they give us a way to systematically map programming languages onto of parallel algorithms thereby comparing their range of suitability.

# Chapter 5

# Automatic code conversion Algorithm

This algorithm is developed to convert a normal program written in C programming language which runs on a single CPU into a complete CUDA C program which can run properly on CUDA architecture and can get performance benefits of the architecture.

# 5.1 The Algorithm

The proposed algorithm is as bellow.

### **Algorithm 5.1** The Proposed Algorithm

- 1 Read C file of the input

- 2 Find out all the variables and kernel variables

- 3 Find out the global variables and included files

- 4 Create Symbol Table

- 5 Find out declared functions

- 6 If it is a main function Than

- Write it as main function

- 8 Else

- 9 Write it as it is

- 10 Find out functional dependence

- 11 If there is a inter functional dependence Than

- Write the function definition as device function

| 1 | 9  | 177  | 1   |

|---|----|------|-----|

| 1 | •• | - P/ | Ise |

- write the function as it is

- 15 Read main.cu file line by line

- Analyze code and calculate BlockGrid and BlockDim

- 17 Write appropriate CUDAMalloc and CUDAMemcpy code at respective place

- 18 Find out the function calls in the definition and insert them in function list

- 19 Find pragma kernel regions and convert them into kernel calls

- analysis with dependency checker

- 21 Based on dependency flags call transformation routines

- 22 Call appropriate kernel threads instead of function calls

- Include the header file to all the main.cu file.

- 24 Compile the main.cu file using nvcc compiler

- 25 Run the main file

# Chapter 6

# Different Compiler Platforms

Now, the translation process contains lots of complex processes like token generation, scanning, parsing, compilation, code generation, code modification, code analysis, dependency analysis, code optimization etc.

So it was impossible to make a compiler in c itself for c and do it all manually in one year by just only one student! So I better started for looking for compiler frameworks or compiler development environment that provides me some basic data structures like DFAs, NFAs or link list trees and interfaces to access those huge data structures to make my translator. I found some open source compiler platforms listed below:

# 6.1 Introduction to ANTLR

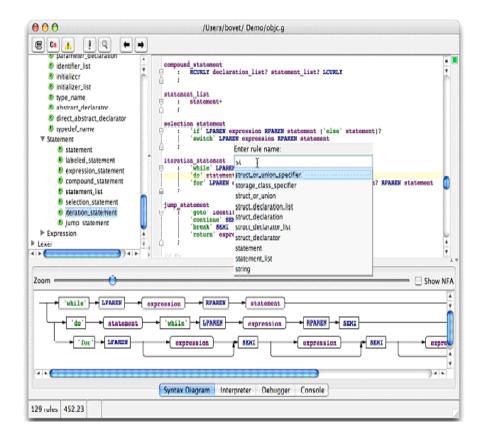

ANTLR, ANother Tool for Language Recognition, is a language tool that provides a framework for constructing recognizers, interpreters, compilers, and translators from grammatical descriptions containing actions in a variety of target languages. [21]

ANTLR has a sophisticated grammar development environment called ANTLRWorks.

Figure 6.1: ANTLRWORKS

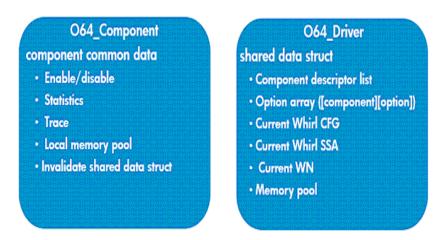

# 6.2 Introduction to Open64

Open64 has been well-recognized as an industrial-strength production compiler. It is the final result of research contributions from a number of compiler groups around the world. Formerly known as Pro64, Open64 was initially created by SGI from SGI's MIPSPro compiler. [24]