# "VERIFICATION OF SoC WITH ETHERNET INTERFACE"

A Major Project Report

Submitted in Partial Fulfillment of the Requirements for the Degree of

MASTER OF TECHNOLOGY

Ν

# ELECTRONICS & COMMUNICATION ENGG.

(VLSI Design)

By Manish Raizada (03MEC013)

Department of Electronics & Communication Engineering INSTITUTE OF TECHNOLOGY NIRMA UNIVERSITY OF SCIENCE & TECHNOLOGY, AHMEDABAD 382 481

MAY 2005

# CERTIFICATE

This is to certify that the Major Project Report (Part-I-II) entitled "Verification of SoC with Ethernet interface" submitted by Mr. Manish Raizada (Roll No.03MEC13) towards the partial fulfillment of the requirements for Semester III-IV of Master of Technology (Electronics & Communication Engg.) in the field of VLSI Design of Nirma University of Science and Technology is the record of work carried out by him under our supervision and guidance. The work submitted has in our opinion reached a level required for being accepted for examination. The results embodied in this major project work to the best of our knowledge have not been submitted to any other University or Institution for award of any degree or diploma.

Date:

Project Guide:

Facilitator at Institute:

Miss Mittal Patel ASIC Verification Dept. eInfochips Limited, Ahmedabad

Signature of Examiners:

Prof. Y. N. Trivedi Electronics & Comm. Engg. Dept. Institute Of Technology, Nirma University, Ahmedabad

| Dr. M. D. Desai                           | Dr. H. V. Trivedi           |

|-------------------------------------------|-----------------------------|

| HOD                                       | Director                    |

| Dept of Electronics & Comm. Engg.         | Institute of Technology     |

| Institute of Technology, Nirma University | Nirma University, Ahmedabad |

# ACKNOWLEDGEMENT

It gives me a great pleasure to take this opportunity to thank to **eInfochips Pvt. Ltd**. and **Mr. Nilesh Ranpura** for giving me such a great opportunity to do project in their esteemed organization. I deem it my privilege to have carried out this dissertation work under this well-known quality conscious organization.

I express my deep sense of gratitude to Mr. Pranav Tailor and Miss Mittal Patel for their personal involvement in every facet of this work and readiness to resolve any point of confusion by mutual discussion. I would also like to thank Mr. Vijay Patel and Mr. Dharmendra J. Patel for their co-operation and providing the necessary facilities for carrying out this work.

I would like to thank **Prof. Y. N. Trivedi** for his help, valuable suggestions and moral support. Finally, I would like to thank my parents for their constant love and support and for providing me with the opportunity and the encouragement to pursue my goals.

(Manish Raizada)

### **Confidentiality Notice**

The contents of this document constitute valuable proprietary and confidential property of Verisity Design, Inc. and its licensors, including eInfochips, Inc. No part of this information product may be reproduced, transmitted, or translated in any form or by any means, electronic, mechanical, manual, optical, or otherwise without prior written permission from Verisity Design, Inc.

Information in this product is subject to change without notice and does not represent a commitment on the part of Verisity. The information contained herein is the proprietary and confidential information of Verisity or its licensors, and is supplied subject to, and may be used only by Verisity's customers in accordance with, a written agreement between Verisity and its customers. Except as may be explicitly set forth in such agreement, Verisity does not make, and expressly disclaims, any representations or warranties as to the completeness, accuracy, or usefulness of the information contained in this document. Verisity does not warrant that use of such information will not infringe any third party rights, nor does Verisity assume any liability for damages or costs of any kind that may result from use of such information.

### **Restricted Rights Legend**

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraphs (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013.

## **Destination Control Statement**

All technical data contained in this product is subject to the export control laws of the United States of America. Disclosure to nationals of other countries contrary to United States law is prohibited. It is the reader's responsibility to determine the applicable regulations and to comply with them.

# Abstract

Verification is not a test bench, nor is it a series of test benches. Verification is a process used to demonstrate the functional correctness of a design. By saying functional correctness means the design to be verified has to adhere with some predefined rules or standard. In other words design under test should behave as per specified rules. We all perform verification processes throughout our daily lives: balancing a checkbook, tasting a simmering dish, associating landmarks with symbols on a map. These are all verification processes.

Today, in the era of multi-million gate ASICs, reusable Intellectual Property (IP), and System-on-Chip (SoC) designs, verification consumes about 70% of the design effort. Design teams, properly staffed to address the verification challenge, include engineers dedicated to verification. The number of verification engineers is usually twice the number of RTL designers. When design projects are completed, the code that implements the test benches makes up to 80% of the total volume. It is also the reason verification is currently the target of new tools and methodologies. These tools and methodologies attempt to reduce the overall verification time by enabling parallelism of effort, higher levels of abstraction and automation. Providing higher levels of abstraction enables you to work more efficiently without worrying about low-level details.

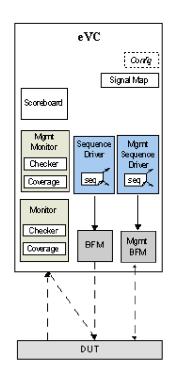

eVC consists of a complete set of elements for stimulating, checking and collecting coverage information on the device under test (DUT). The eVC expedites creation of a more efficient test bench for DUT. The eVC can work with both Verilog and VHDL devices and with all HDL simulators that are supported by Specman Elite. eVC can be used as full verification environment or can be added to existing environment. The eVC interface is viewable and thus can be the basis for user extensions.

This thesis report put some light on developing verification environment for the verification of Ethernet eVC (e Verification Component). Architecture of eVC has been discussed. eVC reduce verification time by atomizing the verification process. First few pages of report gives the answers of some fundamental questions like what is verification, why it is required and importance of verification. White Box approach has been used to verify eVC, and Coverage Driven Verification process used to verify functionality.

# Contents

|                                                      | Page No.     |

|------------------------------------------------------|--------------|

| List of Figures                                      | (            |

| List of Figures<br>List of Tables                    | (vii)        |

| Abbreviation                                         | (ix)         |

| Addreviation                                         | ( <b>x</b> ) |

| CHAPTER 1: Introduction                              | 1            |

| 1.1 Black Box Verification                           | 2            |

| 1.2 White Box Verification                           | 2            |

| 1.3 Grey Box Verification                            | 2<br>3       |

| 1.4 Levels of Verification                           |              |

| 1.5 Need of Verification languages                   | 5            |

| 1.6 History and advantages of 'e'                    | 7            |

| 1.7 Verification Reuse                               | 7            |

| 1.8 e Verification Component                         | 8            |

| 1.9 About Ethernet eVC                               | 10           |

| 1.10 Ethernet Basics                                 | 10           |

| 1.11 Verification for Ethernet eVC                   | 12           |

| CHAPTER 2 : Review Of Literature                     | 17           |

| 2.1 The IEEE 802.3 Logical relationship to the       |              |

| ISO Reference model                                  | 17           |

| 2.2 Ethernet MAC Sublayer                            | 18           |

| 2.3 Media Access Control Frame Structure             | 19           |

| 2.4 Half duplex transmission                         | 22           |

| 2.5 Full duplex transmission                         | 25           |

| 2.6 Ethernet PHY layer                               | 27           |

| 2.7 Encoding for signal transmission                 | 28           |

| 2.8 The IEEE 803.2 Physical Layer relationships to   |              |

| the ISO Reference Model                              | 30           |

| CHAPTER 3 : System Review (Basic Theory)             | 39           |

| 3.1 e Verification Component                         | 39           |

| 3.2 Ethernet eVC                                     | 39           |

| 3.3 Features of Ethernet eVC                         | 40           |

| 3.4 Ethernet traffic emulation                       | 40           |

| 3.5 Flow of data within the agents                   | 42           |

| 3.6 Agent architecture                               | 42           |

| 3.7 Monitor & BFM architecture                       | 44           |

| 3.8 Scoreboard architecture                          | 45           |

| 3.9 Scoreboard checking                              | 46           |

| 3.10 Topologies for verification at the module level | 47           |

| 3.11 Single port MAC dut for non-layered interfaces  | 48           |

| 3.12 Multi port MAC dut for non-layered interfaces   | 48           |

| 3.13 Single port PHY dut for non-layered interfaces  | 49           |

| 3.14 Multi port PHY dut for non-layered interfaces   | 49           |

| 3.15 Verification environment architecture           | 50           |

| 3.16 Is data collected correctly?                    | 52           |

| CHAPTER 4 : System Design                           | 54 |

|-----------------------------------------------------|----|

| 4.1 Structure of sequence                           | 54 |

| 4.2 Ethernet sequence structure                     | 55 |

| 4.3 Management sequence structure                   | 56 |

| 4.4 Injecting Ethernet packets with protocol errors | 58 |

| 4.5 Monitoring Coverage and checkers                | 61 |

| CHAPTER 5 : Coverage Driven Verification            | 63 |

| 5.1 Higher Abstraction                              | 64 |

| 5.2 Coverage requirements                           | 65 |

| 5.3 Steps for achieving regression                  | 67 |

| 5.4 Analyzing Bugs                                  | 74 |

| CHAPTER 6 : Results & Discussion                    | 80 |

| 6.1 Normal Scenario                                 | 80 |

| 6.2 Collision Scenario                              | 82 |

| 6.3 Zeroipg check Scenario                          | 85 |

| 6.4 Injecting RX_ER in ipg phase of packet          | 86 |

| 6.5 Results                                         | 87 |

| CHAPTER 7 : Conclusion & Future Scope               | 88 |

| 7.1 Conclusion                                      | 88 |

| 7.2 Future Scope                                    | 88 |

| REFERENCES | 89  |

|------------|-----|

| Appendix A | 90  |

| Appendix B | 109 |

# List of Figures

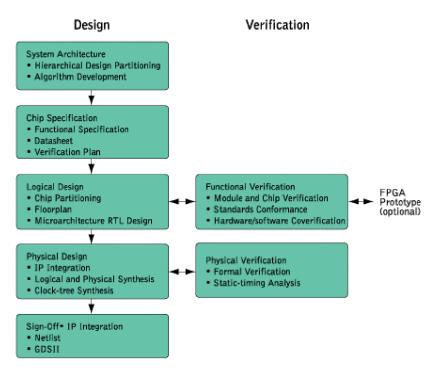

| Figure 1.1: Design and verification flow: A typical sequence of  |    |

|------------------------------------------------------------------|----|

| steps for logical                                                | 4  |

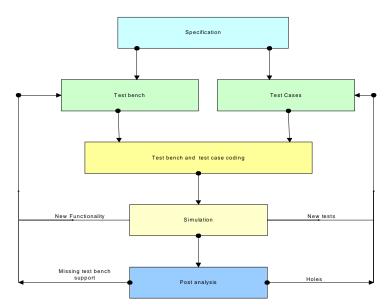

| Figure 1.2: Verification process flow                            | 4  |

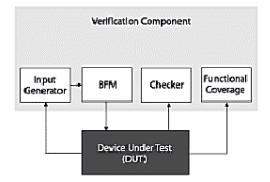

| Figure 1.3: Typical verification component                       | 9  |

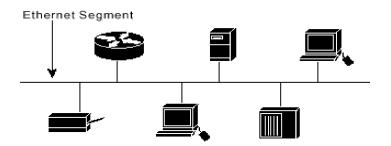

| Figure 1.4: An Ethernet network runs CSMA/CD over coaxial        |    |

| Cable                                                            | 10 |

| Figure 1.5: Example Point-to-Point Interconnection               | 11 |

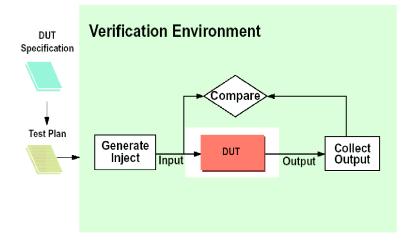

| Figure 1.6: Verification Environment                             | 16 |

| Figure 2.1: Ethernet's Logical Relationship to the ISO Reference |    |

| Model                                                            | 17 |

| Figure 2.2: MAC and Physical Layer Compatibility                 | 18 |

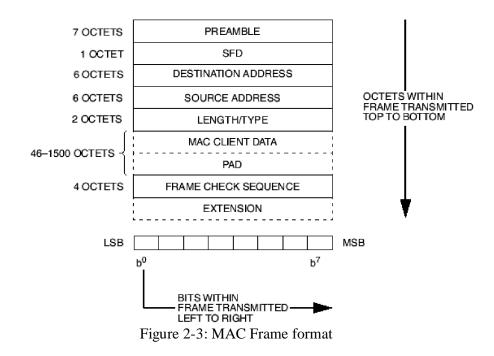

| Figure 2-3: MAC Frame format                                     | 19 |

| Figure 2.4: Address designation                                  | 20 |

| Figure 2.5: MAC Frame with Gigabit Carrier Extension             | 24 |

| Figure 2-6: A Gigabit Frame-Burst Sequence                       | 25 |

| Figure 2.7: Full Duplex Operation Allows Simultaneous Two-       |    |

| Way Transmission on the Same Link                                | 26 |

| Figure 2.8: An Overview of the IEEE 802.3 Flow Control           | 26 |

| Figure 2.9: A Concept Example of Baseline Wander                 |    |

| Sequence                                                         | 29 |

| Figure 2.10: Transition-Based Manchester Binary Encoding         | 29 |

| Figure 2.11: The Generic Ethernet Physical Layer Reference       |    |

| Model                                                            | 30 |

| Figure 2.12: Transmission between MAC & PHY                      | 32 |

| Figure 2.13: System level diagram of Reduced Gigabit Media       |    |

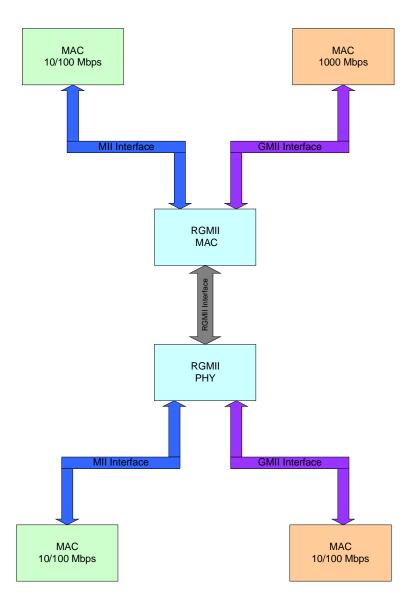

| Independent Interface (RGMII)                                    | 35 |

| Figure 3.1: Architecture of Ethernet eVC                         | 40 |

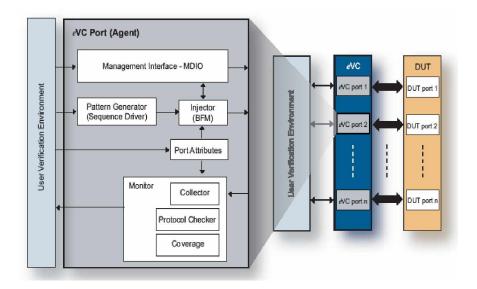

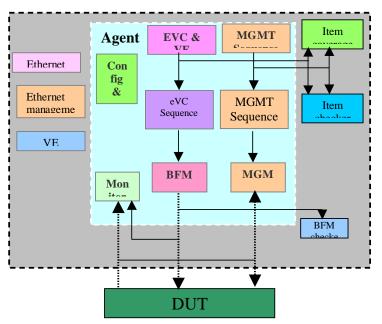

| Figure 3.2: Agent Architecture                                   | 43 |

| Figure 3.3: Agent Architecture for Layered Interfaces            | 44 |

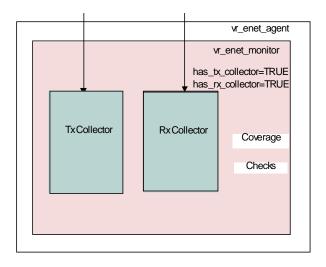

| Figure 3.4: Monitor and BFM architecture                         | 45 |

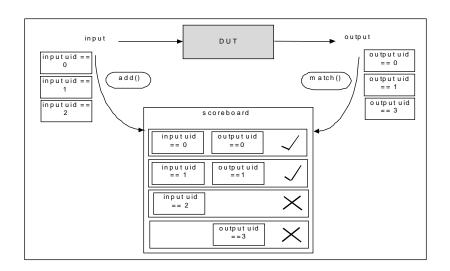

| Figure 3.5: Functioning of Scoreboard                            | 47 |

| Figure3.6: Ethernet eVC in user's verification environment   | 47 |  |  |  |

|--------------------------------------------------------------|----|--|--|--|

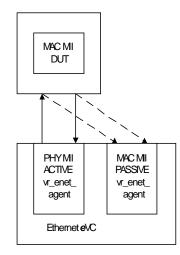

| Figure 3.7: Single Port MAC DUT                              | 48 |  |  |  |

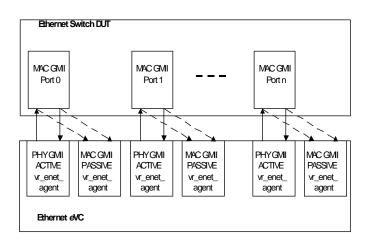

| Figure 3.8: Multi-Port MAC DUT                               | 48 |  |  |  |

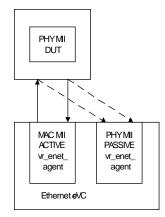

| Figure 3.9: Single Port PHY DUT                              | 49 |  |  |  |

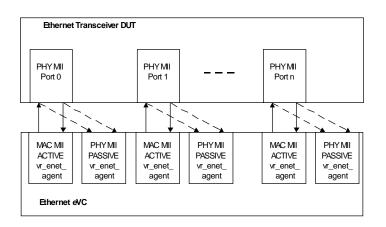

| Figure 3.10: Multi Port PHY DUT                              | 49 |  |  |  |

| Figure 3.11: Ethernet eVC VE functional block diagram        | 50 |  |  |  |

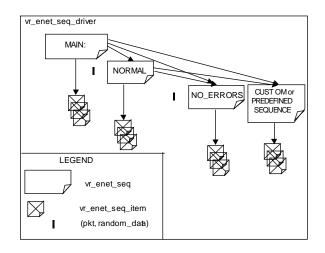

| Figure 4.1: Ethernet Sequence Structure                      | 55 |  |  |  |

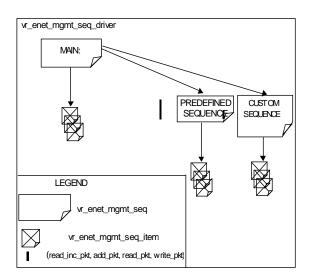

| Figure 4.2: Management Sequence Structure                    | 56 |  |  |  |

| Figure 5.1: Functional coverage serves multiple simulations  |    |  |  |  |

| Scenarios                                                    | 64 |  |  |  |

| Figure 5.2: Functional coverage of Ethernet Packet           | 66 |  |  |  |

| Figure 5.3: Functional coverage model for Ethernet eVC       | 69 |  |  |  |

| Figure 5.4: Illegal inter packet gap between two packets     |    |  |  |  |

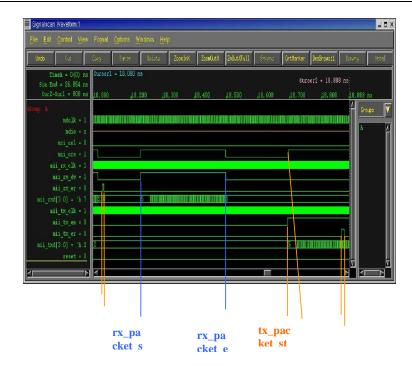

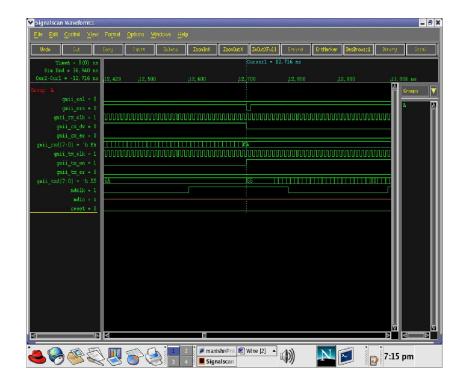

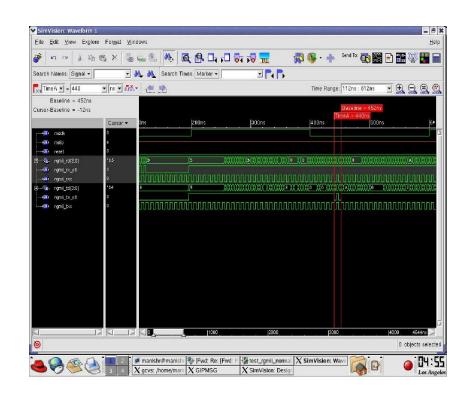

| Figure 6.1: Simulation of Normal Scenario                    | 80 |  |  |  |

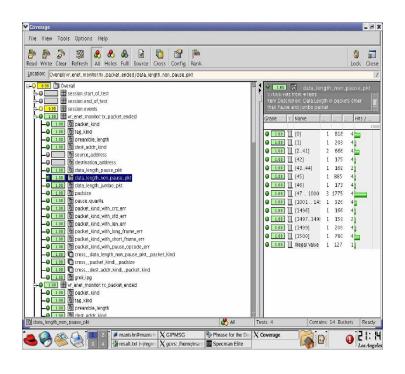

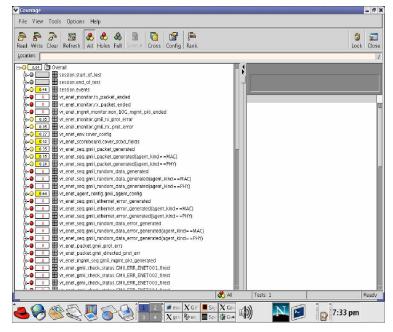

| Figure 6.2: Coverage of Normal Scenario                      | 81 |  |  |  |

| Figure 6.3: Simulation of Normal Packet scenario (RGMII      |    |  |  |  |

| interface)                                                   | 82 |  |  |  |

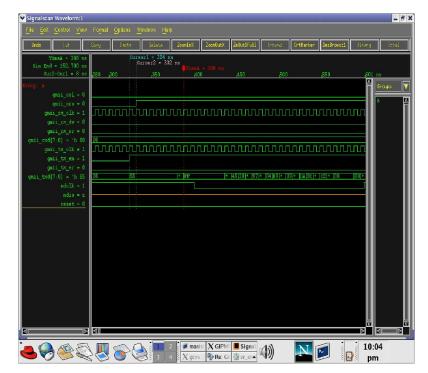

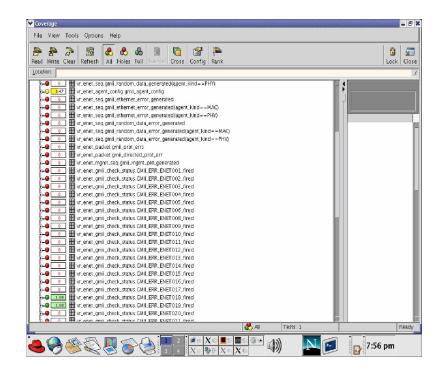

| Figure 6.4: Simulation of Collision Scenario                 | 83 |  |  |  |

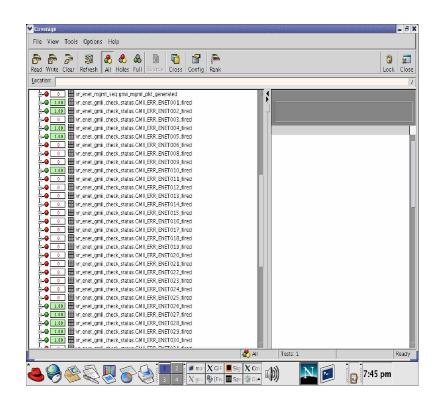

| Figure 6.5: Coverage of Collision Scenario (GMII Interface)  | 84 |  |  |  |

| Figure 6.6: Simulating collision scenario (RGMII Interface)  | 84 |  |  |  |

| Figure 6.7: Zeroipg check scenario (GMII Interface)          | 85 |  |  |  |

| Figure 6.8: Coverage of Zeroipg check Scenario               | 86 |  |  |  |

| Figure 6.9: TX_ER insertion in Data Phase of Ethernet Packet |    |  |  |  |

| (RGMII Interface)                                            | 86 |  |  |  |

| Figure 6.10: RX_ER insertion in IPG phase of Ethernet Packet |    |  |  |  |

| (RGMII Interface)                                            | 87 |  |  |  |

# List of Tables

| Table 2.1: Limits for Half-Duplex Operation                 | 24 |

|-------------------------------------------------------------|----|

| Table 2.2: Permissible encoding of TXD<7:0>, TX_ER, and     |    |

| TX_EN                                                       | 33 |

| Table 2.3: Permissible encoding of RXD<7:0>, RX_ER, and     |    |

| RX_DV                                                       | 34 |

| Table 2.4: Signal description of RGMII                      | 36 |

| Table 2.5: Signal coding for TXD, TXERR and TX_EN           | 37 |

| Table 2.6: Signal coding for RX_DV, RXERR and RX_ER         | 38 |

| Table 5.1: Correlation between functional coverage and code |    |

| Coverage                                                    | 65 |

| Table 5.2: Scenarios to be checked on various Ethernet      |    |

| Packets                                                     | 68 |

# Abbreviation

**VE:** Verification Environment, Aggregation of the eVC along with all other required verification components.

**eVC:** e Verification component, it represent complete verification environment for DUT.

**DUT:** Device Under Test, It is a device that is to be verified using eVC.

**eRM:** e Reusable Methodology, term used for eVC, to make eVC e Reusable in the sense it can be integrate with other eVC on Soc.

**Ethernet eVC:** Complete verification environment (eVC) of Ethernet protocol, it can be use to verify IEEE 802.3 Std, 2000 Edition compliant devices.

**CDV:** Coverage Driven Verification, ease the process of verification by focusing time and compute resources on simulations that are indicating coverage.

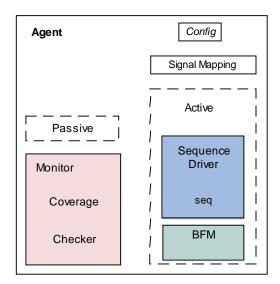

Agent: Top level agent, which contain active and passive agent.

Active Agent: Drives stimulus to DUT.

Passive Agent: Collect packets from DUT.

Monitor: A unit instance that passively monitors the DUT signal.

**BFM:** Bus Functional Model a unit instance that interacts with the DUT and drives or samples the DUT signals.

# Chapter 1 Introduction

As the project title explains, this project work is regarding verification of Ethernet eVC in which protocol adherence of Ethernet eVC has been checked for media independent interfaces GMII, SGMII, RGMII. As eVC has been written in 'e' language hence, understanding of language and Specman Elite (tool) are prerequisite for project work.

Before going in to the detail discussion of verification of Ethernet standard let us find answers of some basic questions like What is verification?, Why it is required?, What are the kinds and levels of verification and importance of verification? Starting with IEEE Definition about Verification, Verification means "Confirmation by examination and provisions of objective evidence that specified requirements have been fulfilled."

Verification is not a test bench, nor is it a series of test benches. Verification is a process used to demonstrate the functional correctness of a design. By saying functional correctness means the design to be verified has to adhere with some predefined rules or standard. In other words design under test should behave as per specified rules. We all perform verification processes throughout our daily lives: balancing a checkbook, tasting a simmering dish, associating landmarks with symbols on a map. These are all verification processes.

Today, in the era of multi-million gate ASICs, reusable Intellectual Property (IP), and System-on-Chip (SoC) designs, verification consumes about 70% of the design effort. Design teams, properly staffed to address the verification challenge, include engineers dedicated to verification. The number of verification engineers is usually twice the number of RTL designers. When design projects are completed, the code that implements the test benches makes up to 80% of the total volume. It is also the reason verification is currently the target of new tools and methodologies. These tools and methodologies attempt to reduce the overall verification time by enabling parallelism of effort, higher levels of abstraction and automation. Providing higher levels of abstraction enables you to work more efficiently without worrying about low-level details.

Automation tools helps in reducing time but they requires standard processes with welldefined inputs and outputs. Not all processes can be automated. It is possible to automate some portion of the verification process, especially when applied to a narrow application domain. Because of the variety of functions, interfaces, protocols, and transformations that must be verified, it is not possible to provide a general-purpose automation solution for verification.

The main purpose of functional verification is to ensure that a design implements intended functionality. Functional coverage reconciles a design with its specification. It is important to note that, unless a specification is written in a formal language with precise semantics, it is impossible to prove that a design meets the intent of its specification. Functional verification can be accomplished using three complementary but different approaches: black box, white-box, and grey-box.

#### **1.1 Black-Box Verification:**

With a black-box approach, the functional verification must be performed without any knowledge of the actual implementation of a design. All verification must be accomplished through the available interfaces, without direct access to the internal state of the design, without knowledge of its structure and implementation. This method suffers from an obvious lack of visibility and controllability. A black-box functional verification approach forms a true conformance verification that can be used to show that a particular design implements the intent of a specification regardless of its implementation. It is mostly used approach.

#### **1.2 White-Box Verification:**

As the name suggests, a white-box approach has full visibility and controllability of the internal structure and implementation of the design being verified. This method has the advantage of being able to quickly set up an interesting combination of states and inputs, or isolate a particular function. This approach is tightly integrated with a particular implementation and cannot be used on alternative implementations or future redesigns. It also requires detailed knowledge of the design implementation.

#### **1.3 Grey-Box Verification:**

Grey-box verification is a compromise between the aloofness of a black-box verification and the dependence on the implementation of white-box verification. Verification is a necessary evil. It always takes too long and costs too much. Verification does not generate a profit or make money: after all, it is the design being verified that will be sold and ultimately make money, not the verification. Yet verification is indispensable.

Verification is a process that is never truly complete. The objective of verification is to ensure that a design is error-free, yet one cannot prove that a design is error-free. Verification can only show the presence of errors, not their absence.

## **1.4 Levels of verification:**

There are four levels of verification:

**1.4.1 Component testing:** Testing conducted to verify the implementation of the design for one software element (unit, module) or a collection of software elements.

**1.4.2 Integration testing:** An orderly progression of testing in which various software elements and/or hardware elements are integrated together and tested. This testing proceeds until the entire system has been integrated.

**1.4.3 System testing:** The process of testing an integrated hardware and software system to verify that the system meets its specified requirements.

**1.4.4 Acceptance Testing:** Formal testing conducted to determine whether or not a system satisfies its acceptance criteria and to enable the customer to determine whether or not to accept the system.

# 1.4.5 Verification and design process flow:

Figure1.1: Design and verification flow: A typical sequence of steps for logical and physical design, and for verification.

# 1.4.6 Verification Process flow:

Below figure shows the verification flow.

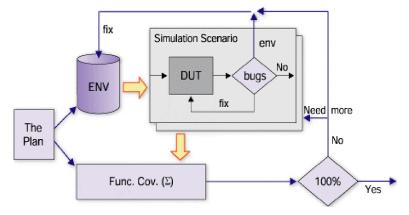

Figure 1.2: Verification process flow.

Verification flow starts with understanding specification of the chip/block under verification. Once the specification is understood, test cases document is prepared, which documents all the possible test cases. Once test case document is done to a level, where 70-80 percent functionality is covered, test bench architecture document is prepared. In the past, test bench architecture document is prepared first and test case document is prepared next. There is a draw back with this style, if test case document show a particular functionality to be verified and if test bench does not support as architecture document was prepared before test cases document. If we have test cases document to refer to, then writing architecture documented becomes much easier, as we know for sure what is expected from the test bench.

#### 1.4.6.1 Test Cases

Identify the test cases from the design specification a simple task for simple cases. Normally requirement in test cases becomes a test case. Anything that specification mentions, "Can do", "will have" becomes a test case. Corner test cases normally take lot of thinking to identify.

#### **1.5 Need of Verification Languages:**

Today, project teams build huge verification environments, where verification consumes 40-70% of the resources needed in a typical cycle. Because a verification environment typically contains concurrent mechanisms for controlling traffic streams to device input ports, and for checking outstanding transactions at the output ports, Verilog and VHDL have traditionally been used for building verification environments. Unfortunately, it is widely recognized that for more complex verification environments and problems, these languages do not contain the necessary constructs for modeling the verification environment efficiently.

As a result, many project teams have moved to using higher-level languages such as C and C++ to be more efficient in creating the verification environment. Unfortunately, these general-purpose languages do not have any built-in constructs for modeling hardware concepts such as concurrency, operating in simulation time, or manipulating vectors of various bit widths. Without these constructs, handling device-specific needs such as controlling synchronization between traffic streams, checking correct timing and formatting traffic data are extremely difficult and time-consuming. Project teams often use a mix of HDL

and C/C++ code to attack this verification problem, spending a good deal of time on the interface between the languages. With these problems in mind, what should a verification language look like? It should combine the best features of the most popular HDLs and general-purpose languages:

- Specifying the traffic and traffic parameters in the same terms as the device specification.

- Automatically generating these traffic streams with the ability to target corner cases of the design.

- Storing and checking outstanding transactions.

- Checking protocol adherence.

- Collecting functional feedback on the stimulus and the device under test.

- Automatically responding to feedback from the device during simulation.

With these features in place, verification engineers can focus much sooner on what needs to be verified rather than how to do it (implementing the environment infrastructure) One way to increase productivity is to raise the level of abstraction. High-level languages, such as C or Pascal, raised the level of abstraction from assembly-level, enabling engineers to become more productive. Similarly, computer languages specifically designed for verification are able to raise the level of abstraction compared to general-purpose simulation languages.

Verilog was designed with a focus on describing low-level hardware structures. It does not provide support for high-level data structures or object-oriented features. VHDL was designed for very large design teams. It strongly encapsulates all information and communicates strictly through well-defined interfaces. This creates an opportunity for verification languages designed to overcome the shortcomings of Verilog and VHDL.

Some popular verification languages Verisity, OpenVera from Synopsys and RAVE from Forte Design. Open-source solutions include the SystemC Verification Library (SCV) from Cadence and Jeda from Juniper Networks. There are also a plethora of homegrown solutions based on Perl, SystemC, C++ or TCL. Verification extensions to the Verilog language are also being added in SystemVerilog.

We have used "e/Specman" verification language for developing "Ethernet eVC" which is a ready made, highly configurable e verification environment suitable for verifying DUTs supporting Ethernet protocol.

# 1.6 History and advantages of e:

The e language was developed by Verisity as part of its Specman product as a tool for efficiently writing test benches. Like Vera, it is an imperative object-oriented language with concurrency; the ability to generate constrained random values, mechanisms for checking functional (variable value) coverage, and a way to check temporal properties (assertions). Books on e include Palnitkar [41] and Iman and Joshi [30]. The syntax of e is unusual. First, all code must be enclosed in < and > symbols; otherwise it is considered a comment. Unlike C, e declarations are written name: type. The syntax for fields in compound types (e.g., structs) includes particles such as % and !, which indicate when a field is to be driven on the device-under-test and not randomly computed respectively.

- Speeds up the design verification process:

- Automates manual processes

- Provides higher abstraction level than HDLs

- Supports modular, reusable, and extensible code

- Improves usability with graphical interface and debugger

- Improves design quality

- Supports all ranges of tests from directed to random

- Improves test base effectiveness with coverage analysis

- Supports both black box and white-box testing. (In black-box, connection to

- DUT's interface only. In white-box, looking into the DUT s internals also.)

# **1.7 Verification Reuse:**

"With verification consuming 60-80% of the manpower on complex chip projects, improving verification productivity is an economic necessity", said Moshe Gavrielov, Verisity CEO.Verification reuse directly addresses higher productivity, increased chip quality and overall verification investment. Reusable Methodology is the breakthrough technology required to create reusable verification environments and to ensure that all verification components effectively interoperate. Today's complex chips commonly incorporate many different protocols, interfaces and processors. Assembling appropriate verification

environments requires efficient integration of reusable, plug-and-play verification components.

Achieving reusability requires that all components be built and packaged uniformly. Reusability becomes even more challenging when design teams all over the world create verification components that need to fit together seamlessly. Every aspect of the component, including basic naming conventions and coding styles, debug message conventions, user interfaces, and interactions between components must be standardized in order to interoperability. assure World leader companies in the development faces many verification challenges Verification reuse is essential for our own productivity and to reduce time-to-market for these companies.

The capabilities introduced by Reusable methodology make a significant contribution to meeting these requirements by enabling a framework for reuse.

### **1.8 eVC (e Verification Component):**

One of the key factors for reusing code is arranging it as an independent and easy to use code package. When developing verification code in e, the reusable package is typically organized as an eVC (e Verification Component). An eVC is a verification component. It is ready-to-use configurable environment, typically focusing on a specific protocol or architecture.

Each eVC consists of a complete set of elements for simulating, checking and collecting coverage information for a protocol or architecture. eVC expedite creation of a most efficient test bench for design under test (DUT). They can work with both Verilog and VHDL devices and with all HDL simulators that are supported by Specman.

eVC can be used to create an environment. The eVC interface is viewable and hence can be the basis for user extensions. Maintaining the eVC in its original form facilitates possible upgrades.

eVC implementation is often partially encrypted, especially in commercial eVCs where authors want to protect their intellectual property. Most commercial eVC requires special feature license to enable them. Following is the list of possible kind of eVC:

- Bus-based eVCs (Such PCI and AHB)

- Data-communication eVCs (for example Ethernet, MAC, Data link)

- CPU/DSP eVCs

- Higher level protocol eVCs (TCP/IP, HTTP). These usually sit on top of other eVCs.

- Platform eVCs (that is, an eVC for a specific, reusable SoC platform, into which you plug eVCs of various cores).

- Compliance test-suite eVCs. These are tests (and perhaps coverage definitions and more) that demonstrate compliance to a protocol. For example, there could be a PCI compliance eVC in addition to the basic PCI eVC.

- HW/SW co-verification eVCs, such as an eVC dedicated to verifying a HW/SW environment using a particular RTOS/CPU combination.

A complete verification component handles all the facets involved in verifying a given protocol, interface or processor within the device under test (DUT). This minimally includes the following items (see Figure 1.3):

- Input traffic generator to create stimulus for the DUT (e.g. packets/frames, bus transactions, etc.)

- Bus functional models (BFMs) to drive that traffic, communicating directly with the DUT

- Monitors, scoreboards, and protocol checkers to examine the actual response of the DUT relative to the expected response

- Functional coverage to measure and report on whether the transactions and scenarios defined in the test plan have been covered or not

Figure 1.3: Typical verification component

# **1.9 About Ethernet eVC:**

The Ethernet eVC is a ready made highly configurable e Verification Component suitable for DUT supporting the Ethernet Protocol.

All eVC behavior complies with the IEEE Std 802.3, 2000, IEEE Draft P802.3ae/D4.0, SGMII and SMII specification by Cisco systems-1998 and RGMII specification by Hewlet Packard, version2.0. The Ethernet eVC is eRM compliant.

## **1.10 Ethernet Basics:**

The term Ethernet refers to the family of local area network (LAN) implementations that includes three principal categories.

• Ethernet and IEEE 802.3-LAN specifications that operate at 10 Mbps over coaxial cable.

• 100-Mbps Ethernet-A single LAN specifications, also known as Fast Ethernet, that operates at 100 Mbps over twisted-pair cable.

• 1000-Mbps Ethernet-A single LAN specifications, also known as Gigabit Ethernet, that operates at 1000 Mbps (1 Gbps) over fiber and twisted-pair cables.

Ethernet is a comprehensive international standard for Local Area Networks (LANs) employing CSMA/CD as the access method. This standard encompasses several media types and techniques for signal rates from 1 Mb/s to 1000 Mb/s. Ethernet is widely used LAN technology, which allows multiple end stations (such as computers, servers, printers, gateways, to other networks etc.) to exchange data among themselves within a single building or campus. It provides two distinct modes of operation: half duplex and full duplex. Figure 1-1 gives the view of Ethernet network.

Figure 1.4: An Ethernet network runs CSMA/CD over coaxial cable.

### 1.10.1 Half duplex operation:

In half duplex mode, the CSMA/CD media access method is the means by which two or more stations share a common transmission medium. To transmit, a station waits for a quiet period on the medium (that is, no other station is transmitting) and then sends intended message in bit-serial form. If after initiating a transmission, the message collides with that of another station then each transition station intentionally transmits for an additional predefined period to ensure the propagation of collision throughout the system. The station remains silent for a random amount of time (back off time) before attempting to transmit again. Half duplex operation can be used with all media and configurations allowed by this standard.

### 1.10.2 Full duplex operation:

Full duplex operation allows simultaneous communication between a pair of stations using point-to-point media (dedicated channel). Full duplex operation does not require that transmitter defer, nor they monitor or react to receive activity, as there are no contentions on shared medium in this mode. Full duplex mode can be used when all of the following are true: The physical medium is capable of supporting simultaneous transmission and reception without interference.

There are exactly two stations connected with a full duplex point-to-point link. Since there is no contention for use of a shared medium, the multiple access (i.e., CSMA/CD) algorithms are unnecessary.

Both the stations on the LAN are capable of, and have been configured to use, full duplex operation.

The most common configuration envisioned for full duplex operation consists of central bridge (also known as a switch) with a dedicated LAN connecting each bridge port to a single device. Figure 1-2 showing point-to-point link.

Figure 1.5: Example Point-to-Point Interconnection

# 1.10.3 Ethernet Network Elements:

Ethernet LANs consist of network nodes and interconnecting media. The network nodes fall into two major classes:

**1.10.3.1 Data terminal equipment (DTE):** Devices that are either the source or the destination of data frames. DTEs are typically devices such as PCs, workstations, file servers, or print servers that, as a group, are all often referred to as end stations.

**1.10.3.2 Data communication equipment (DCE):** Intermediate network devices that receive and forward frames across the network. DCEs may be either standalone devices such as repeaters, network switches, and routers, or communications interface units such as interface cards and modems.

The current Ethernet media options include two general types of copper cable: unshielded twisted-pair (UTP) and shielded twisted-pair (STP), plus several types of optical fiber cable.

# **1.11 Verification Environment for Ethernet eVC:**

# Steps for building verification environment:

For building verification environment, steps which are very common and applicable to any other verification environment as follows:

- Generating traffic streams

- Driving traffic into the design (stimuli)

- Checking these data streams

- Checking protocols and timing

- Tracking progress

- Modifying the environment due to spec changes or product derivatives

- Writing scenarios

#### Step 1: Generating traffic streams

When building a verification environment, the verification engineer often starts by modeling the device input stimulus. In Verilog, the designer is limited in how to model this traffic because of the lack of high-level data structures and the notion of dynamic lists. As a result, sequences of traffic items are often represented as a series of task calls to initialize the frame, build its header, and payload. This ?cut-and-paste? code is lengthy, hard to read and hard to maintain (if there is need to add another attribute passed to all task calls).

The verification engineer often needs constructs better suited for modeling and manipulating frame sequences. C provides some of these. However, it becomes apparent that C was not dev eloped with hardware in mind as soon as bit vectors need to be specified on non-four byte boundaries and manipulated. Unfortunately, the engineer still has to write the functions to manipulate the lists and, to use memory efficiently, now has to worry about correctly allocating and de-allocating memory and handling pointers. These memory problems can result in hours of chasing bus errors and segmentation faults.

The e language provides constructs for modeling traffic streams with built-in functions for generating them and automatically takes care of memory allocation and garbage collection (memory de-allocation). Also in e, there is no need to create generation functions for each struct. The generator is built-in, and once the structs are declared, meaningful stimuli can be generated. Defining a field ('frames' in the above example), which is a ?list of frames?, is enough to have a sequence of frames generated. The built in generator performs memory allocation dynamically, and a built-in garbage collection takes care of de-allocation.

#### Step 2: Driving stimuli into the device

With the data structures in place, the engineer has to consider how data will flow though the verification environment. Typically, a task or function will drive data into each of the device's input ports and a task or function will pull data from each of the device's output ports.

In Verilog, the device specific synchronization for that port is fairly easy because the engineer has direct control over the signals. However, many other functions are typically needed to synchronize the basic traffic flow, format the data at each end, and print the data structures for debugging and post-run checking.

C and C++ help with organizing and formatting data, but the benefit is eaten away because these general-purpose languages have no concept of simulation time or hardware signals. Special code must be written t o interface with the specific Verilog Programming Language Interface (PLI) to drive and sample simulation signals at the appropriate simulation time. Moreover, PLI-related code often needs to be tailored for different simulators. In addition, traffic structures built in C/C++ must be manually converted to the bit, byte or word format the device expects to receive and send.

The e language in this case combines the benefit of both worlds. It has the knowledge of simulation time, constructs for concurrency and built-in controllability, and observability of the simulation signals, regardless of the simulator. Further, each structure in the environment automatically has pre-defined pack and unpack functions for converting it to a bit stream, or vice versa, from bit stream into the data structure format and fields.

Step 3: Checking data streams

To check that the device works correctly, monitoring tasks or functions need to be written. In the case of an Ethernet device, such tasks would pull data from the output ports and compare it with the expected data. The expected data is often determined within a selfchecking environment by storing the outstanding transactions, or through a reference model of the device.

As with traffic streams, Verilog's lack of built-in lists makes it impossible to create dynamic scoreboards to verify the data integrity and routing of outstanding transactions. This inflexibility leads to built-in list sizes that use up memory and create assumptions in the code that are difficult to maintain if this code is to be portable.

Built-in lists and list functions, recursive data structure comparison, and automatic memory allocations are key features in the e verification language. These constructs make it much easier to implement data integrity checking

14

Step 4: Checking protocols and timing - using assertions

Because Verilog and VHDL are directly tied to the simulator, it is easy to interact with the device to get timing information. Unfortunately, most of the interesting timing checks are not straightforward and contain multiple edge dependencies. A timing check might be easy to specify in an English specification, but it is another story to write it in procedural code, be it Verilog, VHDL, C or C++. As a result, in the past few years, declarative assertions (in languages such as PSL/Sugar) have become an appealing approach.

The e language includes a built-in assertion language, similar in expressiveness to PSL/Sugar. Constructs to capture timing scenarios, automated capabilities to observe the device and checking constructs to relate timing scenarios are all built-in. Such an assertion language makes it easy to specify and combine complex timing scenarios that can be used for even the most difficult protocol checking.

Step 5: Tracking progress

A key requirement in verification is having a reliable metric that shows the progress towards hitting all the verification goals. Functional coverage, a metric that tracks which functionality of the device was verified, is being recognized as a highly reliable measure. Neither Verilog, VHDL nor C/C++ have the notion of functional coverage, causing many project teams to create elaborate combinations of log files, parsed by various scripts which then produce some summary reports. This enables very limited capabilities, and yet another maintenance burden on the implementers of the verification environment.

The e verification language has built-in functional coverage constructs, supporting simple value coverage, value-transition coverage and cross-coverage.

Step 6: Specification changes and product derivatives - extensibility

Once the environment is in place, the engineer might need to extend or modify it to accommodate changes or updates to the specification. Verilog, VHDL and C clearly fall short in this area because they provide no constructs to incorporate any changes: modifications need to be done within the original code. Changing the original code often results in bugs because the intent of the original code is not clearly known.

The e verification language offers the notion of extensibility, which is a key feature of an Aspect-Oriented Programming (AOP) language, and provides the constructs necessary to modify or change the functionality of the environment without having to change the original code in any form.

### Step 7: Writing scenarios

Once the verification environment is in place, the project team now needs to focus on writing scenarios to verify that the device behaves according to specification.

The problem with Verilog and C is that you have to write explicit randomization code for each attribute the designer wants to randomize. There is also often interest in mechanisms to weight particular attributes towards values that denote typical or corner case scenarios. Such mechanisms in Verilog and C are typically non-obvious, maintenance burdens.

'e' provides not only the built-in capability to randomly generate any data structure simple or complex - automatically with weighted distribution, but it also provides constructs for constraining the generated values within acceptable ranges. Additionally, e provides mechanisms to easily layer test-specific constraints for particular tests, and take run-time feedback from the device to focus this random test into hard-to-reach corner cases. Combining this generation capability with the temporal assertion language gives the verification engineer a powerful capability for identifying complex, internal corner case scenarios and generating specific traffic to create conflicts deep within the device.

Figure 1.6: Verification Environment

# Chapter 2 Review of Literature

## 2.1 The IEEE 802.3 Logical Relationship to the ISO Reference Model

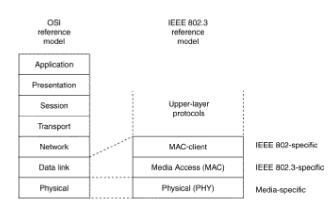

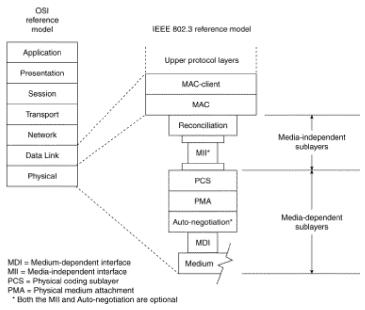

Figure 2-1 shows the IEEE 802.3 logical layers and their relationship to the OSI reference model. As with all IEEE 802 protocols, the ISO data link layer is divided into two IEEE 802 sub layers, the Media Access Control (MAC) sub layer and the MAC-client sub layer. The IEEE 802.3 physical layer corresponds to the ISO physical layer.

Figure 2.1: Ethernet's Logical Relationship to the ISO Reference Model

The MAC-client sub layer may be one of the following:

- Logical Link Control (LLC), if the unit is a DTE. This sublayer provides the interface between the Ethernet MAC and the upper layers in the protocol stack of the end station. The LLC sublayer is defined by IEEE 802.2 standards.

- Bridge entity, if the unit is a DCE. Bridge entities provide LAN-to-LAN interfaces between LANs that use the same protocol (for example, Ethernet to Ethernet) and also between different protocols (for example, Ethernet to Token Ring). Bridge entities are defined by IEEE 802.1 standards.

Because specifications for LLC and bridge entities are common for all IEEE 802 LAN protocols, network compatibility becomes the primary responsibility of the particular network protocol. Figure 2-2 shows different compatibility requirements imposed by the MAC and physical levels for basic data communication over an Ethernet link.

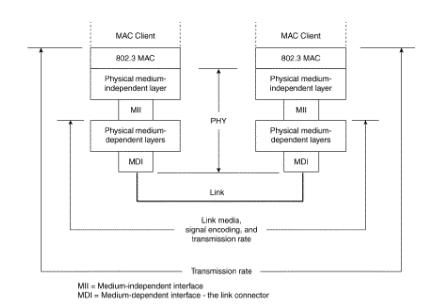

Figure 2.2: MAC and Physical Layer Compatibility Requirements for Basic Data Communication

The MAC layer controls the node's access to the network media and is specific to the individual protocol. All IEEE 802.3 MACs must meet the same basic set of logical requirements, regardless of whether they include one or more of the defined optional protocol extensions. The only requirement for basic communication (communication that does not require optional protocol extensions) between two network nodes is that both MACs must support the same transmission rate.

The 802.3 physical layer is specific to the transmission data rate, the signal encoding, and the type of media interconnecting the two nodes. Gigabit Ethernet, for example, is defined to operate over either twisted-pair or optical fiber cable, but each specific type of cable or signalencoding procedure requires a different physical layer implementation.

### 2.2 The Ethernet MAC Sublayer

The MAC sublayer has two primary responsibilities:

- Data encapsulation, including frame assembly before transmission, and frame parsing/error detection during and after reception

- Media access control, including initiation of frame transmission and recovery from transmission failure

# 2.3 Media Access Control frame structure:

This section gives the detail for the communication system using the CSMA/CD MAC. It defines the various components of MAC frame.

### 2.3.1 MAC frame format:

Figure 2-3 shows the nine fields of the frame: the preamble, SFD (start frame delimiter), the addresses of the frame's source and destination, length or type field to indicate the length or protocol type of the following field that contains the MAC client data, a field that contains padding if required, the frame check sequence field containing a cyclic redundancy check value to detects error in received frame, and the extension field if required (for 1000 Mb/s half duplex operation only). Of these nine fields all are of fixed size except for the data, pad and extension fields which may contain an integer number of octets between the minimum and maximum values that are determined by specific implementation of the CSMA/CD MAC for a particular interface.

### **2.3.2 MAC frame elements:**

### 2.3.2.1 Preamble field:

The preamble field is a 7-octate field that is used to achieve steady-state synchronization with received frame's timing.

#### 2.3.2.2 Start Frame Delimiter (SFD):

The SFD field is the sequence 10101011. It immediately follows the preamble pattern and indicates the start of frame.

#### 2.3.2.3 Address Fields:

Each MAC frame shall contain two address fields: the Destination address and the Source address field, in the order. The destination address field specifies the address(s) for which the frame is intended. The source address field identifies the station from which the frame was initiated. The representation of address field shall be as follows (see figure 2.4):

| I/G U/L 46-BIT ADDRESS |

|------------------------|

|------------------------|

I/G = 0 INDIVIDUAL ADDRESS I/G = 1 GROUP ADDRESS U/L = 0 GLOBALLY ADMINISTERED ADDRESS U/L = 1 LOCALLY ADMINISTERED ADDRESS

Figure 2.4: Address designation

**Note** Individual addresses are also known as unicast addresses because they refer to a single MAC and are assigned by the NIC manufacturer from a block of addresses allocated by the IEEE. Group addresses (multicast addresses) identify the end stations in a workgroup and are assigned by the network manager. A special group address (all 1 the broadcast address) indicates all stations on the network.

- **Destination address (DA):** Consists of 6 bytes. The DA field identifies which station(s) should receive the frame. The left-most bit in the DA field indicates whether the address is an individual address (indicated by a 0) or a group address (indicated by a 1). The second bit from the left indicates whether the DA is globally administered (indicated by a 0) or locally administered (indicated by a 1). The remaining 46 bits are a uniquely assigned value that identifies a single station, a defined group of stations, or all stations on the network.

- Source addresses (SA): Consists of 6 bytes. The SA field identifies the sending station. The SA is always an individual address and the left-most bit in the SA field is always 0.

- Length/Type: Consists of 4 bytes. This field indicates either the number of MACclient data bytes that are contained in the data field of the frame, or the frame type ID if the frame is assembled using an optional format. If the Length/Type field value is less than or equal to 1500, the number of LLC bytes in the Data field is equal to the Length/Type field value. If the Length/Type field value is greater than 1536, the frame is an optional type frame, and the Length/Type field value identifies the particular type of frame being sent or received.

- **Data:** Is a sequence of *n* bytes of any value, where *n* is less than or equal to 1500. If the length of the Data field is less than 46, the Data field must be extended by adding a filler (a pad) sufficient to bring the Data field length to 46 bytes.

- Frame check sequence (FCS): Consists of 4 bytes. This sequence contains a 32-bit cyclic redundancy check (CRC) value, which is created by the sending MAC and is recalculated by the receiving MAC to check for damaged frames. The FCS is generated over the DA, SA, Length/Type, and Data fields.

#### 2.3.4 Frame Transmission

Whenever an end station MAC receives a transmit-frame request with the accompanying address and data information from the LLC sublayer, the MAC begins the transmission sequence by transferring the LLC information into the MAC frame buffer.

- The preamble and start-of-frame delimiter are inserted in the PRE and SOF fields.

- The destination and source addresses are inserted into the address fields.

- The LLC data bytes are counted, and the number of bytes is inserted into the Length/Type field.

- The LLC data bytes are inserted into the Data field. If the number of LLC data bytes is less than 46, a pad is added to bring the Data field length up to 46.

- An FCS value is generated over the DA, SA, Length/Type, and Data fields and is appended to the end of the Data field.

After the frame is assembled, actual frame transmission will depend on whether the MAC is operating in half-duplex or full-duplex mode.

The IEEE 802.3 standard currently requires that all Ethernet MACs support half-duplex operation, in which the MAC can be either transmitting or receiving a frame, but it cannot be doing both simultaneously. Full-duplex operation is an optional MAC capability that allows the MAC to transmit and receive frames simultaneously.

#### 2.4 Half-Duplex Transmission: The CSMA/CD Access Method

The CSMA/CD protocol was originally developed as a means by which two or more stations could share a common media in a switch-less environment when the protocol does not require central arbitration, access tokens, or assigned time slots to indicate when a station will be allowed to transmit. Each Ethernet MAC determines for itself when it will be allowed to send a frame. The CSMA/CD access rules are summarized by the protocol's acronym:

- **Carrier sense:** Each station continuously listens for traffic on the medium to determine when gaps between frame transmissions occur.

- **Multiple access: S**tations may begin transmitting any time they detect that the network is quiet (there is no traffic).

- Collision detect: If two or more stations in the same CSMA/CD network (collision domain) begin transmitting at approximately the same time, the bit streams from the transmitting stations will interfere (collide) with each other, and both transmissions will be unreadable. If that happens, each transmitting station must be capable of detecting that a collision has occurred before it has finished sending its frame. Each must stop transmitting as soon as it has detected the collision and then must wait

a quasirandom length of time (determined by a back-off algorithm) before attempting to retransmit the frame.

The worst-case situation occurs when the two most-distant stations on the network both need to send a frame and when the second station does not begin transmitting until just before the frame from the first station arrives. The collision will be detected almost immediately by the second station, but it will not be detected by the first station until the corrupted signal has propagated all the way back to that station. The maximum time that is required to detect a collision (the collision window, or "slot time") is approximately equal to twice the signal propagation time between the two most-distant stations on the network.

This means that both the minimum frame length and the maximum collision diameter are directly related to the slot time. Longer minimum frame lengths translate to longer slot times and larger collision diameters; shorter minimum frame lengths correspond to shorter slot times and smaller collision diameters.

The trade-off was between the need to reduce the impact of collision recovery and the need for network diameters to be large enough to accommodate reasonable network sizes. The compromise was to choose a maximum network diameter (about 2500 meters) and then to set the minimum frame length long enough to ensure detection of all worst-case collisions.

The compromise worked well for 10 Mbps, but it was a problem for higher data-rate Ethernet developers. Fast Ethernet was required to provide backward compatibility with earlier Ethernet networks, including the existing IEEE 802.3 frame format and error-detection procedures, plus all applications and networking software running on the 10-Mbps networks.

Although signal propagation velocity is essentially constant for all transmission rates, the time required to transmit a frame is inversely related to the transmission rate.

At 100 Mbps, a minimum-length frame can be transmitted in approximately one-tenth of the defined slot time, and the transmitting stations would not likely detect any collision that occurred during the transmission. This, in turn, meant that the maximum network diameters specified for 10-Mbps networks could not be used for 100-Mbps networks. The solution for Fast Ethernet was to reduce the maximum network diameter by approximately a factor of 10 (to a little more than 200 meters).

The same problem also arose during specification development for Gigabit Ethernet, but decreasing network diameters by another factor of 10 (to approximately 20 meters) for 1000-Mbps operation was simply not practical. This time, the developers elected to maintain approximately the same maximum collision domain diameters as 100-Mbps networks and to increase the apparent minimum frame size by adding a variable-length nondata extension field to frames that are shorter than the minimum length (the extension field is removed during frame reception).

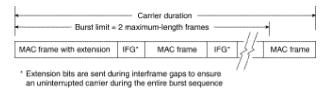

Figure 2.5 shows the MAC frame format with the gigabit extension field, and Table 2.1 shows the effect of the trade-off between the transmission data rate and the minimum frame size for 10-Mbps, 100-Mbps, and 1000-Mbps Ethernet.

| <b>4</b> |         |         |         |             | 416 bytes for 1000Base-X<br>520 bytes for 1000Base-T |     |     |            |

|----------|---------|---------|---------|-------------|------------------------------------------------------|-----|-----|------------|

| Preamble | SFD     | DA      | SA      | Length/type | Data                                                 | Pad | FCS | Extension* |

| * The e  | otensio | on fiel | d is au | tomatically |                                                      |     |     |            |

removed during frame reception

Figure 2.5: MAC Frame with Gigabit Carrier Extension

| Parameter                                   | 10 Mbps           | 100 Mbps                                                                  | 1000 Mbps                                           |

|---------------------------------------------|-------------------|---------------------------------------------------------------------------|-----------------------------------------------------|

| Minimum frame size                          | 64 bytes          | 64 bytes                                                                  | 520 bytes <sup>1</sup> (with extension field added) |

| Maximum collision diameter,<br>DTE to DTE   | 100 meters<br>UTP | <ul><li>100 meters</li><li>UTP</li><li>412 meters</li><li>fiber</li></ul> | 100 meters UTP<br>316 meters fiber                  |

| Maximum collision diameter with repeaters   | 2500 meters       | 205 meters                                                                | 200 meters                                          |

| Maximum number of repeaters in network path | 5                 | 2                                                                         | 1                                                   |

| Table 2.1: Limits for Half-Duplex Operation |

|---------------------------------------------|

|---------------------------------------------|

520 bytes apply to 1000Base-T implementations. The minimum frame size with extension field for 1000Base-X is reduced to 416 bytes because 1000Base-X encodes and transmits 10 bits for each byte.

Another change to the Ethernet CSMA/CD transmit specification was the addition of frame bursting for gigabit operation. Burst mode is a feature that allows a MAC to send a short sequence (a burst) of frames equal to approximately 5.4 maximum-length frames without having to relinquish control of the medium. The transmitting MAC fills each interframe interval with extension bits, as shown in Figure 2.6, so that other stations on the network will see that the network is busy and will not attempt transmission until after the burst is complete.

Figure 2-6: A Gigabit Frame-Burst Sequence

If the length of the first frame is less than the minimum frame length, an extension field is added to extend the frame length to the value indicated in Table 2-1. Subsequent frames in a frame-burst sequence do not need extension fields, and a frame burst may continue as long as the burst limit has not been reached. If the burst limit is reached after a frame transmission has begun, transmission is allowed to continue until that entire frame has been sent. Frame extension fields are not defined, and burst mode is not allowed for 10 Mbps and 100 Mbps transmission rates.

# 2.5 Full-Duplex Transmission: An Optional Approach to Higher Network Efficiency

Full-duplex operation is an optional MAC capability that allows simultaneous two-way transmission over point-to-point links. Full duplex transmission is functionally much simpler than half-duplex transmission because it involves no media contention, no collisions, no need to schedule retransmissions, and no need for extension bits on the end of short frames. The result is not only more time available for transmission, but also an effective doubling of the

link bandwidth because each link can now support full-rate, simultaneous, two-way transmission.

Transmission can usually begin as soon as frames are ready to send. The only restriction is that there must be a minimum-length inter frame gap between successive frames, as shown in Figure 2.7, and each frame must conform to Ethernet frame format standards.

Figure 2.7: Full Duplex Operation Allows Simultaneous Two-Way Transmission on the Same

#### Link

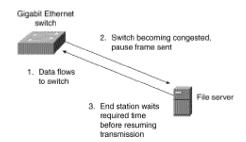

#### 2.5.1 Flow Control

Full-duplex operation requires concurrent implementation of the optional flow-control capability that allows a receiving node (such as a network switch port) that is becoming congested to request the sending node (such as a file server) to stop sending frames for a selected short period of time. Control is MAC-to-MAC through the use of a pause frame that is automatically generated by the receiving MAC. If the congestion is relieved before the requested wait has expired, a second pause frame with a zero time-to-wait value can be sent to request resumption of transmission. An overview of the flow control operation is shown in Figure 2.8.

Figure 2.8: An Overview of the IEEE 802.3 Flow Control Sequence

The full-duplex operation and its companion flow control capability are both options for all Ethernet MACs and all transmission rates. Both options are enabled on a link-by-link basis, assuming that the associated physical layers are also capable of supporting full-duplex operation. Pause frames are identified as MAC control frames by an exclusive assigned (reserved) length/type value. They are also assigned a reserved destination address value to ensure that an incoming pause frame is never forwarded to upper protocol layers or to other ports in a switch.

#### 2.5.2 Frame Reception

Frame reception is essentially the same for both half-duplex and full-duplex operations, except that full-duplex MACs must have separate frame buffers and data paths to allow for simultaneous frame transmission and reception.

Frame reception is the reverse of frame transmission. The destination address of the received frame is checked and matched against the station's address list (its MAC address, its group addresses, and the broadcast address) to determine whether the frame is destined for that station. If an address match is found, the frame length is checked and the received FCS is compared to the FCS that was generated during frame reception. If the frame length is okay and there is an FCS match, the frame type is determined by the contents of the Length/Type field. The frame is then parsed and forwarded to the appropriate upper layer.

#### 2.6 The Ethernet Physical Layers

Because Ethernet devices implement only the bottom two layers of the OSI protocol stack, they are typically implemented as network interface cards (NICs) that plug into the host device's motherboard. The different NICs are identified by a three-part product name that is based on the physical layer attributes.

The naming convention is a concatenation of three terms indicating the transmission rate, the transmission method, and the media type/signal encoding. For example, consider this:

- 10Base-T = 10 Mbps, baseband, over two twisted-pair cables

- 100Base-T2 = 100 Mbps, baseband, over two twisted-pair cables

- 100Base-T4 = 100 Mbps, baseband, over four-twisted pair cables

- 1000Base-LX = 100 Mbps, baseband, long wavelength over optical fiber cable

A question sometimes arises as to why the middle term always seems to be "Base." Early versions of the protocol also allowed for broadband transmission (for example, 10Broad), but broadband implementations were not successful in the marketplace. All current Ethernet implementations use baseband transmission.

#### 2.7 Encoding for Signal Transmission

In baseband transmission, the frame information is directly impressed upon the link as a sequence of pulses or data symbols that are typically attenuated (reduced in size) and distorted (changed in shape) before they reach the other end of the link. The receiver's task is to detect each pulse as it arrives and then to extract its correct value before transferring the reconstructed information to the receiving MAC.

- Filters and pulse-shaping circuits can help restore the size and shape of the received waveforms, but additional measures must be taken to ensure that the received signals are sampled at the correct time in the pulse period and at same rate as the transmit clock:

- The receive clock must be recovered from the incoming data stream to allow the receiving physical layer to synchronize with the incoming pulses.

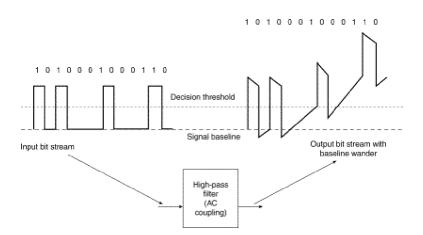

Compensating measures must be taken for a transmission effect known as baseline wander. Clock recovery requires level transitions in the incoming signal to identify and synchronize on pulse boundaries. The alternating 1s and 0s of the frame preamble were designed both to indicate that a frame was arriving and to aid in clock recovery. However, recovered clocks can drift and possibly lose synchronization if pulse levels remain constant and there are no transitions to detect (for example, during long strings of 0s).

Baseline wanders results because Ethernet links are AC-coupled to the transceivers and because AC coupling is incapable of maintaining voltage levels for more than a short time. As a result, transmitted pulses are distorted by a droop effect similar to the exaggerated example shown in Figure 2-9. In long strings of either 1s or 0s, the droop can become so severe that the voltage level passes through the decision threshold, resulting in erroneous sampled values for the affected pulses.

Figure 2.9: A Concept Example of Baseline Wander

Fortunately, encoding the outgoing signal before transmission can significantly reduce the effect of both these problems, as well as reduce the possibility of transmission errors. Early Ethernet implementations, up to and including 10Base-T, all used the Manchester encoding method, shown in Figure 2-10. Each pulse is clearly identified by the direction of the midpulse transition rather than by its sampled level value.

Figure 2.10: Transition-Based Manchester Binary Encoding

Unfortunately, Manchester encoding introduces some difficult frequency-related problems that make it unsuitable for use at higher data rates. Ethernet versions subsequent to 10Base- T all use different encoding procedures that include some or all of the following techniques:

- Using data scrambling: A procedure that scrambles the bits in each byte in an orderly (and recoverable) manner. Some 0s are changed to 1s, some 1s are changed to 0s, and some bits are left the same. The result is reduced run-length of same-value bits, increased transition density, and easier clock recovery.

- **Expanding the code space:** A technique that allows assignment of separate codes for data and control symbols (such as start-of-stream and end-of-stream delimiters, extension bits, and so on) and that assists in transmission error detection.

• Using forward error-correcting codes: An encoding in which redundant information is added to the transmitted data stream so that some types of transmission errors can be corrected during frame reception.

**Note** Forward error-correcting codes are used in 1000Base-T to achieve an effective reduction in the bit error rate. Ethernet protocol limits error handling to detection of bit errors in the received frame. Recovery of frames received with uncorrectable errors or missing frames is the responsibility of higher layers in the protocol stack.

### 2.8 The 802.3 Physical Layer Relationship to the ISO Reference Model

Although the specific logical model of the physical layer may vary from version to version, all Ethernet NICs generally conform to the generic model shown in Figure 2.11.

Figure 2.11: The Generic Ethernet Physical Layer Reference Model

The physical layer for each transmission rate is divided into sub layers that are independent of the particular media type and sub layers that are specific to the media type or signal encoding.

• The reconciliation sublayer and the optional media-independent interface (MII in 10-Mbps and 100-Mbps Ethernet, GMII in Gigabit Ethernet) provide the logical connection between the MAC and the different sets of media-dependent layers. The MII and GMII are defined with separate transmit and receive data paths that are bit-serial for 10-Mbps implementations, nibble-serial (4 bits wide) for 100-Mbps

implementations, and byte-serial (8 bits wide) for 1000-Mbps implementations. The media-independent interfaces and the reconciliation sublayer are common for their respective transmission rates and are configured for full-duplex operation in 10Base-T and all subsequent Ethernet versions.

• The media-dependent physical coding sublayer (PCS) provides the logic for encoding, multiplexing, and synchronization of the outgoing symbol streams as well symbol code alignment, demultiplexing, and decoding of the incoming data.

The physical medium attachment (PMA) sublayer contains the signal transmitters and receivers (transceivers), as well as the clock recovery logic for the received data streams.

- The medium-dependent interface (MDI) is the cable connector between the signal transceivers and the link.

- The Auto-negotiation sublayer allows the NICs at each end of the link to exchange information about their individual capabilities, and then to negotiate and select the most favorable operational mode that they both are capable of supporting. Auto-negotiation is optional in early Ethernet implementations and is mandatory in later versions.

- Depending on which type of signal encoding is used and how the links are configured, the PCS and PMA may or may not be capable of supporting full-duplex operation.

# **2.9 Ethernet Interfaces:**

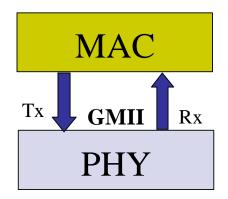

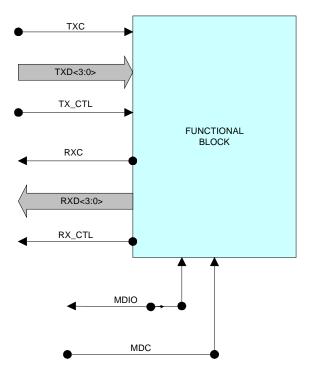

Ethernet Interfaces basically defines the logical and electrical characteristics for the data transmission between MAC and PHY layer. One such interface is Gigabit Media Independent Interface (GMII). (See Figure 2.12)

Gigabit Media Independent Interface (GMII):

This interface has following characteristics:

- It is capable of supporting 1000 Mb/s operation.

- Data and delimiters are synchronous to clock references.

- It provides independent eight-bit-wide transmit and receive data paths.

- It provides a simple management interface.

- It uses signal levels, compatible with common CMOS digital ASIC processes.

- It provides full and half duplex operation.

- Supports 1000 Mb/s speed and clock frequency is 125 MHz.

Figure 2.12: Transmission between MAC & PHY.

#### **2.9.1 Signal Description:**

#### 2.9.1.1 TX\_EN (transmit enable):

TX\_EN in combination with TX\_ER indicates the Reconciliation sublayer is presenting data on the GMII for transmission. It shall be asserted by the Reconciliation sublayer synchronously with the first octet of the preamble and shall remain asserted while all octets to be transmitted are presented to the GMII. TX\_EN shall be negated prior to the first rising edge of clock following the final data octet of a frame. TX\_EN is driven by the Reconciliation sublayer and shall transition synchronously with respect to the clock.

### 2.9.1.2 TXD (transmit data):

TXD is a bundle of eight data signals (TXD<7:0>) that are driven by the Reconciliation sublayer. TXD<7:0> shall transition synchronously with respect to the clock. For each clock period in which TX\_EN is asserted and TX\_ER is de-asserted, data are presented on TXD<7:0> to the PHY for transmission. TXD<0> is the lease significant bit. While TX\_EN and TX\_ER are both de-asserted, TXD<7:0> shall have no effect upon the PHY. Table 2.2 specifies the permissible encodings of TXD<7:0>, TX\_ER, and TX\_EN.

| TX_EN                                               | TX_ER | TXD<7:0>      | Description                |  |

|-----------------------------------------------------|-------|---------------|----------------------------|--|

| 0                                                   | 0     | 00 through FF | Normal inter-frame         |  |

| 0                                                   | 1     | 00 through 0E | Reserved                   |  |

| 0                                                   | 1     | 0F            | Carrier Extend             |  |

| 0                                                   | 1     | 10 through 1E | Reserved                   |  |

| 0                                                   | 1     | 1F            | Carrier Extend error       |  |

| 0                                                   | 1     | 20 through FF | Reserved                   |  |

| 1                                                   | 0     | 00 through FF | Normal data transmission   |  |

| 1                                                   | 1     | 00 through FF | Transmit error propagation |  |

| NOTE- Values in TXD<7:0> column are in hexadecimal. |       |               |                            |  |

Table 2.2: Permissible encoding of TXD<7:0>, TX\_ER, and TX\_EN

#### **2.9.1.3 TX\_ER** (transmit coding error):