# "Verification Of A Chip Block At Module And Board Bringup Level"

A Major Project Report

Submitted in Partial Fulfillment of the Requirements for the Degree of

# Master of Technology

IN

ELECTRONICS & COMMUNICATION ENGG. (VLSI Design)

By

Ms. Heena Shah

Department of Electronics & Communication Engineering Institute of Technology Nirma University of Science & Technology Ahmedabad-382481

# "Verification Of A Chip Block At Module And Board Bringup Level"

A Major Project Report

Submitted in Partial Fulfillment of the Requirements for the Degree of

## Master of Technology

IN

### ELECTRONICS & COMMUNICATION ENGG. (VLSI Design)

By

Ms. Heena Shah

Under the Guidance of

Mr. Darshan Sheth Project Leader - ASIC eInfochips, Ahmedabad. Mrs. Usha Mehta Asst. Professor – EC NIT, Nirma University, Ahmedabad.

Department of Electronics & Communication Engineering Institute of Technology Nirma University of Science & Technology Ahmedabad-382481

## Certificate

This is to certify that the Major Project entitled "Verification Of A Chip Block At Module And Board Bringup Level" submitted by Ms. Heena Shah (05MEC014), towards the partial fulfillment of the requirements for the Semester-III-IV of the degree of Master Of Technology in Electronics & Communication (VLSI Design) of Nirma University of Science & Technology is the record of work carried out by her under our supervision and guidance.

The work submitted has in our opinion reached a level required for being accepted for the examination. The results embodied in the major project work to the best of our knowledge have not been submitted to any other University or Institute for award of any degree or diploma.

> Prof. Usha Mehta E.C. Department Project Guide

Prof. A.S. Ranade H.O.D. E.C. Department Nirma University Ahmedabad Prof. A.B. Patel Director E.C. Department Nirma University Ahmedabad

## ACKNOWLEDGEMENT

### Sometimes our light goes out, but is blown into flame by another human being. I owe deepest thanks to those who have rekindled this light.

"Verification Of A Chip Block At Module And Board Bringup Level" is my Major Project for M.Tech (VLSI Design). I take this opportunity to express my gratitude to all those people who have been instrumental in making my project successful.

I am grateful to eInfochips, Ahmedabad for providing me the opportunity to do my *M*.*Tech Project in its premises.*

I extend my sincere thanks to Mr. Darshan Sheth, Project Leader – ASIC Division, eInfochips, Ahmedabad, for his constant guidance and encouragement in all possible ways.

I am grateful to Mr. Nilesh Ranpura, Project Manager - ASIC Division, eInfochips, Ahmedabad, for providing all necessary resources and his constant support.

I am thankful to Prof. Usha Mehta, Asst. Professor, EC Dept, NIT, Nirma University, Ahmedabad, for her guidance.

I extend my thanks to Prof. N.M. Devashrayee, Head and Course Coordinator – M.Tech (VLSI Design), NIT, Nirma University, Ahmedabad for his always unconditional support and encouragement.

Last but not the least, I am thankful to the almighty who blessed me with the zeal to work hard.

Heena Shah 05MEC014 M.Tech (VLSI Design)-!V NIT, Nirma University, Ahmedabad.

#### ABSTRACT

With gate counts and system complexity growing exponentially, engineers confront the most perplexing challenge in chip design cycle: Verification. Verification of the design RTL is done at various phases of the chip design flow at different abstraction levels. The Major Project "The Verification Of A Chip Block At Module and Board Bringup Level" concentrates on two types of Functional Verification at different stages in the Chip Design Flow. During Design phase, verification is done at low abstraction level, concentrating on the core functionality of the module. The inputs to the module are forced through the testbench and its interfaces are not looked upon. This is the functional verification of chip at module level and is done at the RTL design phase. After the RTL is been finalized after fixing all the bugs, it is send to the fabrication unit. The first chip that will tap out from the fabrication unit has to be tested on the operational board for it. The verification engineers work on the development of simulation platform for verifying each module of the chip for its functionality and dataflow within and external to the chip. The test cases developed for this, once pass on the bringup simulation platform, will be executed by the first chip on the board. The abstraction level is high and concentration is on the interfaces.

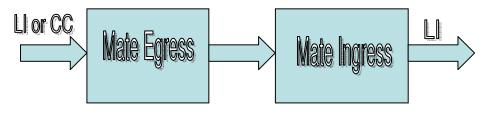

The modules called MI (Mate Ingress) and ME (Mate Egress) are verified for functional verification at module level. The Verification Environment Serving as Platform for simulation is developed with C++ and Verilog. The Test Bench is in Verilog and instantiates two modules Mate Ingress and Mate Egress that are interfaced internally. The module is thoroughly verified which different combinations of input streams generated by Standard SONET frame generator. The same Standard SONET frame analyzer is used to verify the output from the Design under Test. The test cases required to exercise the module for its core functionality are written and simulated as per the test plan. As the verification progressed, different issues related to Verification Environment, Test Bench, Test Case and RTL arouses. The RTL issues are filed as bugs and get resolved by the designers. This results in updation of all the verification components as per requirement. After passing all the test cases, the code coverage is done and based on it new test scenarios are added.

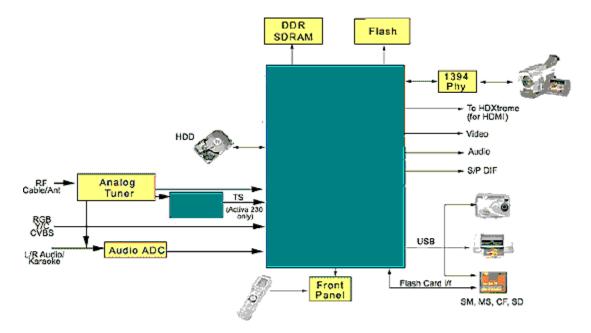

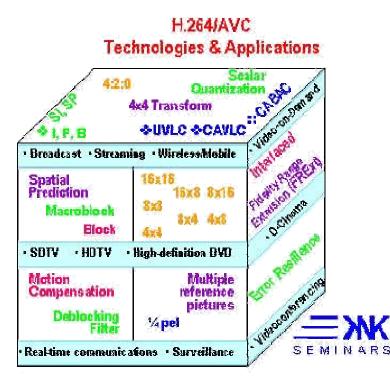

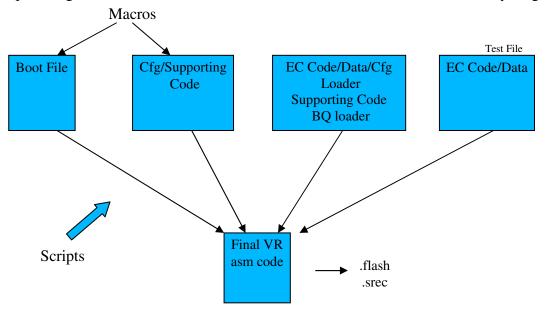

The module called EC (Enhanced Co-processor) is verified for functional verification at board bringup level. This module is a co-processor to a Video Processor and performs complex computational tasks for it. The flow starts with preparation of Test Plan for the bringup verification. The next step is to develop the bringup verification environment. This platform for simulation considers the complete data path for the module under test. It mimics the actual scenario the module will face when the chip is operational on the board. The development of test cases as per the test plan follows. Test cases are written to test each instruction in each operational mode along the complete data path. The chip on board exercises the pass test cases.

## LIST OF FIGURES

| Sr. No. | Fig. No. | Figure Title                               | Page No. |

|---------|----------|--------------------------------------------|----------|

| 1       | 1.1      | Functional Verification Reconvergent Model | 2        |

| 2       | 1.2      | The Chip On Board                          | 15       |

| 3       | 2.1      | Verification Flow                          | 22       |

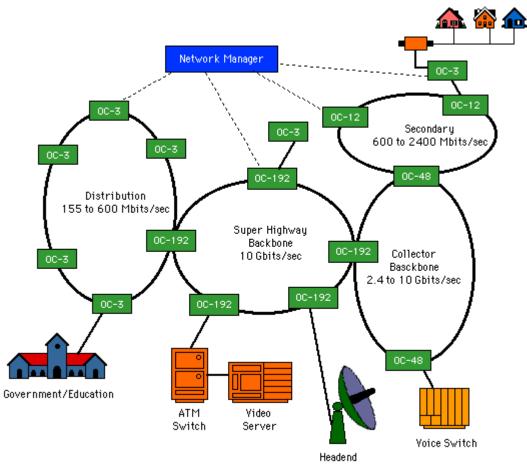

| 4       | 3.1      | Optical Network                            | 27       |

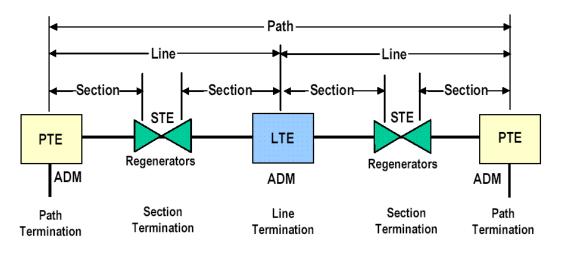

| 5       | 3.2      | SONET End To End Connection                | 28       |

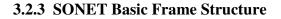

| 6       | 3.3      | Basic SONET frame                          | 28       |

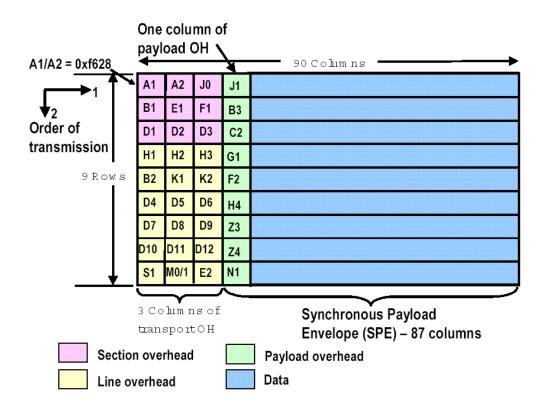

| 7       | 3.4      | SONET Multiplexing Structure               | 30       |

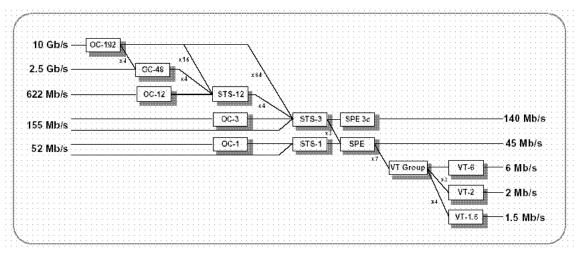

| 8       | 3.5      | SDH Multiplexing Structure                 | 31       |

| 9       | 4.1      | The C++ Environment                        | 33       |

| 10      | 4.2      | Complete VE For MIME Module                | 37       |

| 11      | 4.3      | The Simulation Flow                        | 39       |

| 12      | 5.1      | MIME TestBench Configuration               | 44       |

| 13      | 5.2      | Coverage Log's Snap Shot                   | 52       |

| 14      | 6.1      | Block Diagram Of Chip On Board             | 54       |

| 15      | 6.2      | H.264/AVC Technologies & Applications      | 56       |

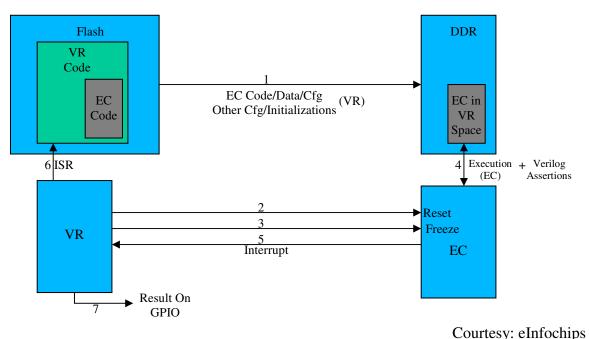

| 16      | 7.1      | Bringup Code Generation For EC             | 63       |

| 17      | 7.2      | Bringup Env Comp/Data/Control Flow         | 66       |

| 18      | 7.3      | Test Case Snap Shot                        | 73       |

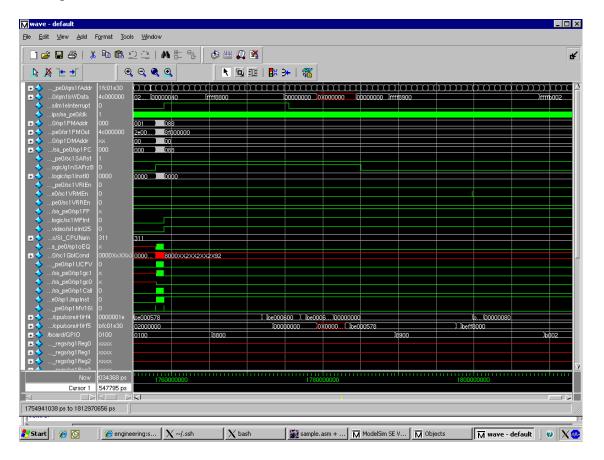

| 19      | 7.4      | Waveform Snap Shot                         | 77       |

## LIST OF TABLES

| Sr. No. | Fig. No. | Figure Title                                 | Page No. |

|---------|----------|----------------------------------------------|----------|

| 1       | 3.1      | SONET/SDH Digital Hierarchy                  | 30       |

| 2       | 5.1      | Features Of MIME Module With Identified Test | 46       |

|         |          | Cases                                        |          |

| 3       | 5.2      | Bugs Filed With Brief Summary                | 48       |

| 4       | 5.3      | New Test Cases identified after Coverage     | 49       |

| 5       | 8.1      | Test plan for the EC module                  | 69       |

| 6       | 8.2      | The EC Test Cases Executed                   | 71       |

| 7       | 9.1      | EVCD signal dump format                      | 91       |

| <b>CONTENTS</b> |

|-----------------|

|-----------------|

| Ch No. | Торіс                                        | Pg No. |

|--------|----------------------------------------------|--------|

| 1      | INTRODUCTION TO VERIFICATION                 | 1      |

| 1.1    | Introduction                                 | 1      |

| 1.2    | What is Verification?                        | 1      |

| 1.3    | Types Of Verification                        |        |

| 1.4    | Levels Of Verification                       | 4      |

| 1.5    | Verification Tools                           | 5      |

| 1.6    | Functional Verification                      | 12     |

| 1.7    | BUGS                                         | 14     |

| 1.8    | The Chip Bringup Verification                | 14     |

| 1.9    | The Verification Methodology                 | 16     |

| 1.10   | High Level Verification Languages            | 17     |

| 2      | THE VERIFICATION METHODOLOGY & FLOW          | 19     |

| 2.1    | Introduction                                 | 19     |

| 2.2    | The Verification Methodology                 | 19     |

| 2.3    | The Verification Flow                        | 20     |

| 2.4    | Designer – Verification Engineer Interaction | 25     |

|        |                                              |        |

| 3      | THE MIME MODULE FOR FUNCTIONAL VERIFICATION  | 26     |

| 3.1    | Introduction                                 | 26     |

| 3.2    | The Protocols/Standards                      | 26     |

| 3.3    | MIME Module                                  | 31     |

| 4      | THE MODULE LEVEL VERIFICATION ENVIRONMENT    | 33     |

| 4.1    | Introduction                                 | 33     |

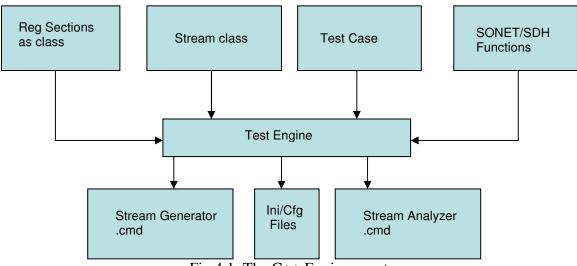

| 4.2    | The C++ Environment                          | 33     |

| 4.3    | The Verilog Environment                      | 34     |

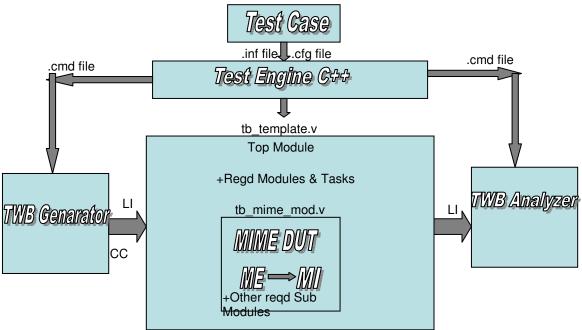

| 4.4    | The TestBench                                | 37     |

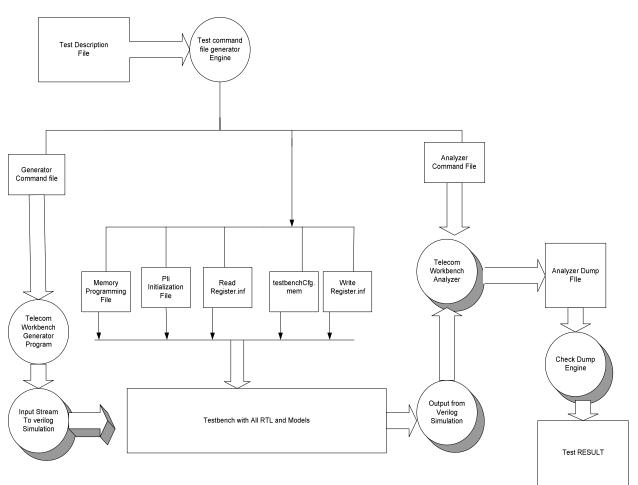

| 4.5    | The Simulation Flow                          | 38     |

| 5      | MODULE LEVEL VERIFICATION FLOW               | 41     |

| 5.1    | Introduction                                 | 41     |

| 5.2    | Languages Used                               | 41     |

| 5.3    | OS & S/W                                     | 42     |

| 5.4    | EDA Tools Used                               | 43     |

| 5.5    | Identification of features                   | 43     |

| 5.6    | Developing the test bench                    | 44     |

| 5.7    | Prioritization of features                   | 45     |

| 5.8    | Grouping of test cases                       | 46     |

| 5.9    | Environment settings                         | 46     |

| 5.10   | Debugging the test cases                     | 47     |

| 5.11 | Bug filing                                      | 47       |

|------|-------------------------------------------------|----------|

| 5.12 | Looping Structure                               | 48       |

| 5.13 | Regression                                      | 48       |

| 5.14 | Coverage                                        | 49       |

| 5.15 | Documentation                                   | 52       |

|      |                                                 |          |

| 6    | THE EC MODULE FOR BOARD BRINGUP<br>VERIFICATION | 53       |

| 6.1  | Introduction                                    | 53       |

| 6.2  | The Chip On Board                               | 53       |

| 6.3  | The Protocols/Standards                         | 55       |

| 6.4  | The Enhanced Co-processor Module                | 60       |

| 7    | THE BRINGUP VERIFICATION ENVIRONMENT            | 62       |

| 7.1  | Introduction                                    | 62       |

| 7.1  | Characteristics Of Bringup VE                   | 62       |

| 7.3  | The Bringup Code Generation for EC              | 63       |

| 7.4  | The Data/Control Flow in Bringup VE             | 65       |

| 7.5  | Critical Stages in Bringup VE development       | 67       |

| 7.6  | Verilog Assertions                              | 68       |

|      |                                                 |          |

| 8    | THE BRINGUP VERIFICATION FLOW                   | 69       |

| 8.1  | Introduction                                    | 69       |

| 8.2  | The Test Plan                                   | 69       |

| 8.3  | Bringup Verification Environment                | 71       |

| 8.4  | Simulating The Test Cases                       | 71       |

| 8.5  | Instruction Simulation                          | 75       |

| 8.6  | Debugging Test Cases                            | 77       |

| 8.7  | Executing Test Cases On Board                   | 78       |

| 8.8  | Executing Test Cases On Tester Board            | 79       |

| 9    | EDA TOOLS, S/W AND LANGUAGES                    | 80       |

| 9.1  | Introduction                                    | 80       |

| 9.2  | EDA Tools                                       | 80       |

| 9.3  | Application S/W                                 | 83       |

| 9.4  | Languages                                       | 86       |

| 9.5  | The Verilog Dump File                           | 89       |

|      |                                                 |          |

|      | Conclusion                                      | 93       |

|      | Future Scope                                    | 93       |

|      |                                                 |          |

|      | References       Abbreviations & Acronyms       | 94<br>95 |

1

### **INTRODUCTION TO VERIFICATION**

#### **1.1 Introduction**

With increase in the system complexity, the traditional capture and simulate methodology has changed to design simulate & synthesize. The logic, functionality and gate counts in a chip are increasing tremendously. With gate count and system complexity growing exponentially, engineers confronts the most perplexed challenge in the product design: functional verification. A bulk of time consumed in design of new ICs and systems is now spent on verification. Engineers are compelled to use the best verification and design tools available to shorten design cycle time. The true path to rapid and accurate system verification includes both tool and methodology innovation.

Today, in the era of multi-million gate ASICs, reusable Intellectual Property (IP), and System On Chip (SOC) designs, verification consumes about 70% of the design effort. The number of verification engineers is usually twice the number of design engineers. When design projects are completed, the code that implements the testbenches makes up to 80% of the total code volume. Verification of design is done at various levels of design phase. Different type of verification is done on the design. The foremost of them is the functional verification that verifies the functionality implemented by the design with respect to the specifications.

#### **1.2 What is Verification?**

I will start with the IEEE definition of Verification. IEEE defines Verification as *"Confirmation by examination and provisions of objective evidence that specified requirements have been fulfilled."* Lets first understand the definition. The design which is to be verified implements some specific functionality as per the requirements. Now the aim of verification is to examine that design implements these specified functionality. This is to be done by examination and not mere observation. It has to be supported by some objective evidences.

Verification can be done at various granularity levels. Depending on the features of the design to be verified, the abstraction level is decided. It follows methodology to accomplish it accurately and quickly. It is a parallel process with the design. Verification engineers and design engineers have to interact a lot to get a verified design at the end of the design cycle. Various EDA tools and languages are available for verification. I shall be going through the complete methodology in detail in the later chapters.

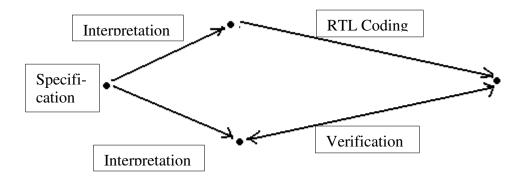

Verification Process is conceptually represented using a reconvergence model. It also illustrates what exactly is being verified. The purpose of verification is to ensure that the

result of some transformation is as intended or as expected. This is analogous to what we do daily in our life. e.g. confirming bank transactions with the available balance.

Fig1.1 Functional Verification Reconvergent Model

A design team interprets a written specification document and produces what they believe to be functionally correct synthesizable HDL code. If the same individual performs the verification of the RTL coding that initially required interpretation of a specification, then the common origin is that interpretation and not the specification. In this case, verification verifies designer's interpretation and not the specification. If that interpretation is wrong, then verification will not be able to highlight it. Hence, the process of verifications. Figure is for functional verification. Choosing the common origin and reconvergenence points determines what is being verified. For functional verification, it is the RTL coding verification against specifications.

Currently, verification is on critical path. It is on target of new tools and methodologies. These tools and methodologies attempt to reduce the overall verification time by enabling parallelism of effort, higher level of abstraction and automation. If effort can be parallelized, additional resources can be applied effectively to reduce the total verification time. For this, it is necessary to be able to write and debug testcases in parallel with each other as well as in parallel with the implementation of the design. Higher level of abstraction enables to work fast but this reduces control and hence should be used wisely. The verification process can be at higher level of abstraction by working at the transactions or bus cycle levels instead of dealing with lower level zeros and ones.

#### **1.3 Types Of Verification**

As explained earlier, in a reconvergence model, the points and path decides the type of verification. Different tools are used for different types of verification. Broadly, verification can be functional verification, formal verification, model checking and testbench generators.

#### **1.3.1 Functional verification**

Functional verification is to verify the functionality implemented by the design against the specification. This can be done at various granularity level. This depends on how much depth in verification is required based on the deadline. It can show that the design meets the intended specifications but cannot prove that design is free from any discrepancy. More explanation on this is in the later chapters.

#### **1.3.2** Formal verification

Establishing properties of hardware or software designs using logic, rather than just testing or informal arguments is formal verification. This involves formal specification of the requirement, formal modeling of the implementation, and precise rules of inference to prove, say, that the implementation satisfies the specification.

**Equivalence Checking** is a type of formal verification. This process mathematically proves that the origin and output are logically equivalent and that the transformation preserves its functionality. It compares two netlist to ensure that some netlist post processing such as scan chain insertion, clock tree synthesis or any manual modification, did not changed the functionality of the circuit. It is also used to verify that the netlist correctly implements the original RTL code. It can be used to see that the synthesizer tool is honest. It can also be used to verify that two RTL descriptions are logically equivalent. Equivalence checking is interested in comparing Boolean and sequential logic functions and not mapping these functions to a specific technology.

**Model Checking** is a recent application of formal verification. It is a method to algorithmically verify formal systems. This is achieved by verifying if the model satisfies a formal specification. The specification is often written as temporal logic formulas. A model-checking tool accepts system requirements or design (called models) and a property (called specification) that the final system is expected to satisfy. The tool then outputs yes if the given model satisfies given specifications and generates a counterexample otherwise. The decision process often uses some form of binary decision diagram (BDD). Here, assertions or characteristics of a design are formally proven or disproven. For example, all state machines in a design could be checked for unreachable or isolated states. Even deadlocks can be detected. The greatest obstacle to model checking is identifying, through interpretation of the design specification, which assertions to prove. Only a subset of identified assertions are feasible to prove.

#### **1.3.3** Testbench Generation

Here, there is no reconvergence point. The RTL code is the common origin. With the help of code coverage metrics and the source code under analysis, testbench generators generate testbenches to either increase code coverage or to exercise the design to violate a property.

#### **1.4 Levels Of Verification**

As per the Rule Of Ten for chip design, the cost of detecting a bug gets multiplied by \$10 as the design progresses through increasing abstraction level. It means that it is better to detect a bug at the initial stage of chip design. As the chip design progresses from component level to module level to system level and so on, the cost of detecting that bug increases with a multiple of \$10. Hence, Verification becomes most important to keep the cost of complete chip within the budget.

Chip Design is a long, complex and a precise process. The chip design goes through number of different stages where it is looked upon from different abstraction levels. It starts from specifications developed from market serve and ends when the chip is fully tested and reaches its final destination: market. At each step of design, verification follows. At each abstraction level, verification is performed rigorously on the design to confirm its corrective operation.

The verification of the functionality chip being design is normally done from bottom to top. The abstraction level goes on increasing. The level of granularity required for the verification effort is determined by the level of verification. The design is potentially composed of several levels. Verification proceeds with these partitions.

#### **1.4.1 Unit Level Verification**

This is the lowest level of verification. It works on logical partitions of the design units. They could be relatively small components like FIFO and state machines. They usually do not have an independent specification document to verify against either. This is basically an adhoc verification and designer can perform this himself. If the features to be verified at the unit level require interaction with other units, they have to be reverified at a higher level where the features are fully contained, to ensure that the integration correctly implements them.

#### **1.4.2 Module Level Verification**

Each chip is designed in terms of various functional modules. These modules are responsible for dedicated functionality of the chip and they interact internally to accomplish the ultimate functionality of the chip. Verification engineers starts with verification of chip RTL at module level. The test patterns applied are both random and deterministic. The module under test is verified from each angle of its functionality as per the specifications. Much of the work is done on the corner cases to identify the bugs in the RTL. This process is simultaneous to the design process and the designer keeps on fixing the bugs as the verification engineer identifies them. The input patterns applied are fired directly on the module only. This level does not verify the interfaces which the module has with other modules.

#### **1.4.3 Full Chip Level Verification**

Studied reports say that 25% to 40% of bugs are identified at full chip integration level verification. The chip is verified with all its modules integrated. The basic aim is to identify bugs related to the interactions of the modules inside the chip and system level interactions. The chip is verified against its complete specification which was used by the designer. Much of the effort deals with transactions, sequence and dependency of execution within the modules.

#### **1.4.4 Board Level Verification**

The designed chip is intended for use with other peripheral blocks. It interacts with these blocks to accomplish the application. At board level, the main aim is to concentrate on such system level interactions. This requires, obtaining suitable models for all such components. Third party models are used for this. The third party model is basically a non-synthesizable code, which has the functionality of the component. Hence, the chip is verified as if it is working in a real environment with all its peripheral components.

#### 1.4.5 Chip Bringup Verification

This is done to test that the chip was fabricated correctly. Tests are written and simulated to run on the actual chip when it taps out of the fab. These tests are basically to check the core functionality of the chip, its interactions with the peripheral blocks, dataflow within and external to chip and the application of the chip. The development and simulation of these test cases starts with the RTL tap out and deadline is governed by the data of first chip tap out.

#### **1.5 Verification Tools**

To improve the reliability and efficiency of a process, automation is required. I will be explaining the tools used in state-of-art functional verification environment. These tools aid the verification process and helps to achieve the deadline.

#### 1.5.1 Lint Tools

Lint tool identifies common mistakes programmers make. It allows finding the mistakes quickly and easily. It identifies real problems such as mismatched data types between arguments and function calls or mismatch in number of arguments. The source code that is syntactically correct and compiles without any error, may result in error at runtime. Lint tool is helpful here in identifying such problems prior to runtime. Diagnosing the problems at runtime would require a runtime debugger and would take several minutes. Lint tool is a static tool i.e. it does not require and stimulus or any description about the output expected. They perform checks that are entirely static in nature, with expectations built into the lint tool itself.

#### Lint tool for Verilog & VHDL

Verilog is a typeless language. Any value can be assigned to a reg or subprogram argument. This creates problem many times. Linting Verilog code ensures that all data is properly handled without accidentally dropping or adding to it. VHDL is a strong typing language. It does not need linting as much as Verilog. Still common problems in VHDL, like that created using std\_logic type can be resolved faster. Some Lint Tools are:

**Leda** : Leda is a code purification tool for designers using the Verilog and VHDL Hardware Description Language (HDL). Leda is uniquely qualified to analyze HDL code pre-synthesis and pre-simulation and is totally compatible with all popular synthesis and simulation tools and flows. By automating more than 500 design checks for language syntax, semantics and questionable synthesis/simulation constructs, Leda detects common as well as subtle and hard-to-find code defects, thus freeing designers to focus on the art of design.

HDLint : A power full linting tool for VHDL and Verilog.

**nLint** : nLint is a comprehensive HDL design rule checker fully integrated with the Debussy debugging system.

**SureLint** : Designers need tools to analyze and debug their designs before integrating with the rest of the project. SureLint offers finite state machine (FSM) analysis, race detection, and many additional checks the most complete lint tool on the market.

#### **1.5.2 Simulators**

Simulators are most common and familiar verification tools. They are named such because their role is limited to approximating reality. They attempt to create an artificial universe that mimics the future real designs. This lets the designers interact with the design before it is manufactured and correct flaws and problems earlier. Many physical characteristics are simplified to ease the simulation task. e.g. A digital simulator assumes that the only possible values for a signal are 0,1 unknown and high impedance. However, in reality, value of a signal is a continuous function of voltage and current across copper wire and can have infinite number of possible values. Within that simplified universe, simulator executes the description of the design.

Simulators are not static tools. They require a facsimile of the environment in which the design will find itself. This is a testbench and it needs to provide inputs, so that design can emulate the design's response based on its description. Simulators can be event driven or cycle driven. Event driven simulators executes the model only when there is any transition in the input provided. A cycle based simulator works on the simulator clock. Here, all timing and delay information is lost. They assume the design meets all the setup and hold requirements.

#### **Co-Simulators & Single Kernel Simulators**

Co-Simulators can provide simulation based on cycle and event, VHDL and Verilog, HDL and C or digital and analog. During co simulation, all simulators involved progress along the time axis in lock step. But now co-simulators which progress in time wrap synchronization have evolved where some simulators are allowed to move ahead of the others.

The biggest hurdle here is the communication overhead between simulators. Whenever a signal generated within a simulator is required as an input by another, the current value of that signal, as well as the timing information of any change in that value, must be communicated. This communication involves translation of event from one simulator into an equivalent event in another simulator.

**Modelsim** was the first to put the award winning Single Kernel Simulator (SKS) technology in the hands of design engineers, enabling transparent mixing of VHDL, Verilog and now SystemC in one design, with a common intuitive graphical interface for development and debug at any level, regardless of the language. Different languages are compiled into a single internal representation or machine code and the simulation is performed using a single simulation engine.

Some Simulators are:

**Verilog-XL** : This is the most standard simulator in the market, as this is the sign off simulator.

**NCVerilog** : This is the compiled simulator which works as fast as VCS, and still maintains the sign off capabilities of Verilog-XL. This simulator is good when it comes to gate level simulations.

**VCS** : This is worlds fastest simulator, this is also a compiled simulator like NCverilog. This simulator is faster when it comes to RTL simulation. Few more things about this simulator are direct C kernel interface, Covermeter code coverage embedded, better integration with VERA and other Synopsys tools.

**Finsim** : This is 100% compatible simulator with Verilog-XL, runs on Linux, Windows and Solaris. This is compiled simulator like VCS and NCVerilog, but slower then VCS and NCVerilog.

**Modelsim** : This is most popular simulator from Mentor Graphics. It has got very good debugger, it supports SystemC, Verilog, VHDL and SystemVerilog.

#### **1.5.3 Third Party Models**

In a board level design, along with your design, there will be some devices purchased from a third party. These can be PLDs, FPGAs, memories, etc. To ensure that the design will work functionally correct with these devices, it is necessary to include models for all the parts in the simulation. Models for these devices can be supplied from the vendor from whom you purchased the device or it can be from some third party. There are several service providers of models for standard SSI and LSI components. These models are non-synthesizable codes. Such models are generic and hence are verified to a greater degree of confidence. Hence, such models can be trusted well.

#### **Hardware Modelers**

When any design is very new or complex, it is difficult to find a model for it as no provider had time to develop it. For such conditions, Hardware Modeler is a solution. This is a small box that connects to your network. A real physical chip that needs to be simulated is plugged in. During simulation, the hardware modeler communicates with your simulators through special interface to supply inputs from the simulator to the device, and then sends the sampled output values from the device back to the simulation. This does not perform timing checks nor does it accurately reflect the output delays. But they greatly speed up the board and system level simulation as the execution occurs on real hardware that is most fastest.

#### **1.5.4 Waveform Viewers**

These are the most common verification tools used in conjunction with simulators. They let you visualize the transitions of multiple signals over time, and their relations with other transitions. Zooming of any particular time interval allows to measure time between two transitions. It can display data in various formats. They provide filters to filter out unwanted signals and see only the necessary signals in case of any complex design. You can locate time of any particular transition to locate any bug. They can be used interactively during the simulation, but more importantly offline, after the simulation has completed. They can playback the events that occurred during the simulation that were recorded in same trace file. Viewing waveforms as a post-processing step lets you quickly browse through a simulation that can take hours to run.

Some waveform viewers can compare two sets of waveforms. One set is presumed to be a golden reference, while other is verified for any discrepancy. The comparator visually flags or highlights any discrepancy found. Waveform viewers are advisable for debugging purpose. Do not use it to determine whether a test case passes or fails. Some Waveform Viewers are:

**nAnalyzer** : This is from Novas Software which provides a single environment for analysis and debugging critical design implementation issues.

**Dinotrace** : This is a free Verilog VCD waveform viewer for an X -11. It understands Verilog value change jump dumps, ASCII and other trace formats. It allows placing cursors, highlighting and searching signals.

**SimVision** : The SimVision analysis environment is a unified graphical debugging environment for Verilog-XL, NC-Verilog, NC-VHDL, and NC-Sim from Cadence. It can run in Simulation mode or Post processing mode.

#### 1.5.5 Code Coverage

For a complex design, the length of code goes in thousands. The logic is also very complex and involves much functionality. So, in is impossible to know with 100% certainty that the design being verified is indeed functionally correct. Code Coverage is a

tool used to find the coverage of the code by the test cases. The Coverage can be stated in many metrics. Depending on the feedback from this tool, verification engineers modify or write new test cases to covered the remaining statements or logic in code. Different metric of code coverage is calculated for all the test cases and finally the result is accumulated to get the complete picture which is analyzed further. It acts as an measure of the effort placed by verification engineer.

It works by instrumenting the source code. This is done by adding check points at strategic locations of source code to record whether particular construct has been exercised. This method varies from tool to tool. This instrumented code is then simulated normally using uninstrumented testbench. All results are collected in the database which generates various coverage metrics. Some popular reports are statement, path, expression, branch, toggle, fsm, etc.

#### **Statement Coverage**

Statement coverage is the most basic form of code coverage. A statement is covered if it is executed. Note that a statement does not necessarily correspond to a line of code. This type of coverage is relatively weak in that even with 100% statement coverage there may still be serious problems in a program which could be discovered through the use of other metrics. Even so, the first time that statement coverage is used in any reasonably sized development effort it is very likely to show up some bugs. It can be quite difficult to achieve 100% statement coverage. There may be sections of code designed to deal with error conditions, or rarely occurring events such as a signal received during a certain section of code. There may also be code that should never be executed:

if (\$param > 20)

{

die "This should never happen!";

}

It can be useful to mark such code in some way and flag an error if it is executed. Statement coverage, or something very similar, can also be called statement execution, line, block, basic block or segment coverage.

#### **Branch Coverage**

This type of coverage is relatively weak in that even with 100% statement coverage there may still be serious problems in a program which could be discovered through the use of other metrics. Even so, the first time that statement coverage is used in any reasonably sized development effort it is very likely to show up some bugs. It can be quite difficult to achieve 100% statement coverage. There may be sections of code designed to deal with error conditions, or rarely occurring events such as a signal received during a certain section of code. There may also be code that should never be executed:

```

if ($param > 20)

{

die "This should never happen!";

}

```

It can be useful to mark such code in some way and flag an error if it is executed.

#### Path Coverage

There are classes of errors which branch coverage cannot detect, such as:

```

$h = 0;

if ($x)

{

$h = { a => 1 };

}

if ($y)

{

print $h->{a};

}

```

100% branch coverage can be achieved by setting (\$x, \$y) to (1, 1) and then to (0, 0). But if we have (0, 1) then things go bang.

The purpose of path coverage is to ensure that all paths through the program are taken. In any reasonably sized program there will be an enormous number of paths through the program and so in practice the paths can be limited to those within a single subroutine, if the subroutine is not too big, or simply to two consecutive branches.

In the above example there are four paths which correspond to the truth table for \$x and \$y. To achieve 100% path coverage they must all be taken. Note that missing elses count as paths.

In some cases it may be impossible to achieve 100% path coverage:

a if \$x;

b;

c if \$x;

50% path coverage is the best you can get here. Ideally, the code coverage tool you are using will recognise this and not complain about it, but unfortunately we do not live in an ideal world. And anyway, solving this problem in the general case requires a solution to the halting problem, and I couldn't find a module on CPAN for that.

Loops also contribute to paths, and pose their own problems which I'll ignore for now.100% path coverage implies 100% branch coverage.Path coverage and some of its close cousins are also known as predicate, basis path and LCSAJ (Linear Code Sequence And Jump) coverage.

#### **Toggle Coverage**

Toggle coverage measures design activity in terms of changes in signal logic values. Toggle coverage reports provide the following information:

- 1. Whether monitored signals were initialized.

- 2. Whether monitored signals experienced rising and/or falling edges.

- 3. The number of rising and falling edges during simulation.

Toggle coverage reports help to verify the quality of the stimulus and locate dead (=unused) structure in the design. Signals which were not initialized during simulation or are not exercised properly by the testbench can be easily identified.

#### FSM Coverage

inite state machine (FSM) coverage answers the question, "Did I reach all of the states and traverse all possible paths through a given state machine?"

There are two types of coverage detail for FSMs that Covered can handle:

State coverage - answers the question "Were all states of an FSM hit during simulation?" State transition coverage - answers the question "Did the FSM transition between all states (that are achievable) in simulation?"

For a design to pass full coverage, it is recommended that the FSM coverage for all finite state machines in the design to receive 100% coverage for the state coverage and 100% for all achievable state transitions. Since Covered will not determine which state transitions are achievable, it is up to the verification engineer to examine the executed state transitions to determine if 100% of possible transitions occurred.

#### Time Coverage

This isn't really code coverage at all, it's profiling of a sort, but while we're seeing what code gets exercised, why not just see how long it takes for it to be exercised? Maybe it will show up some problems with the algorithm being used, or something.

It's usually a good idea to start with the most simple metrics and move on to the more powerful ones later. It would be nice to be able to achieve 100% coverage for all the criteria, that is probably not a sensible goal for all but the smallest of projects. So what is a sensible goal? Well, it depends. It depends on the goals of project you are working on. It depends on the cost of failure. The code coverage tool will have various limitations in the coverage it performs. One would hope that statement and branch coverage would be almost universally available and consistent, but a number of coverage tools handle only statement coverage. Condition and path coverage, where available, will almost certainly not provide complete information, especially in the case of path coverage. Other coverage criteria may or may not be catered for.

Some Code Coverage tools are:

**Verification Navigator** : An integrated design verification environment that enables a consistent, easy-to-use and efficient verification methodology with a powerful set of bestin-class tools for managing the HDL verification process. These tools include HDL checking, coverage analysis, test suite analysis and FSM analysis. The environment includes an extensible flow manager for easy incorporation of custom verification flows. Verification Navigator supports Verilog, VHDL and mixed language designs and integrates seamlessly with all leading simulation environments.

**SureCov** : Engineering teams designing today's chips and semiconductor IP cores need to know, with confidence, how thoroughly the functional test suite is exercising the

design. Verisity's SureCov measures FSM and code coverage with the lowest simulation overhead of any tool available, and without requiring changes to the source design. The SureSight graphical user interface shows exactly which parts of the design have been covered and which have not.

**Code Coverage Tool** : A freeware code coverage tool. Code coverage tool is a Verilog code coverage analysis tool that can be useful for determining how well a test suite is covering the design under test.

#### **1.6 Functional Verification**

I will be concentrating more on functional verification as my project is functional verification of an OPTICAL CHIP design. The main purpose of functional verification is to ensure that a design implements intended functionality. The starting point for functional verification is specifications. The verification engineer interprets the specification and verifies whether the design coincides with the specifications or not. Functional verification, as a process can show that a design meets the intent of its specifications, but cannot prove it. One can easily prove that a design does not implement a desired functionality by identifying just one discrepancy. But, the converse is not. No one can prove that there are no discrepancies. Functional verification can be accomplished using three complementary but different approaches: black box, white box and grey box.

#### **1.6.1 Black Box Functional Verification**

As the name suggests, the design to be verified is looked upon as a black box. i.e. only the interface is known for the design. The internal information of the design is not know. The intention is to verify that the design generates required output for a specific input applied. With a black box approach, the functional verification must be performed without any knowledge of the actual implementation of the design. All verification must be accomplished through the available interfaces, without direct access to the internal state of the design, with knowledge of its structure and implementation. This method suffers from an obvious lack of visibility and controllability. It is difficult to set up interesting state combination or to isolate some functionality. It is equally difficult to observe the response from the input and locate the source of the problem.

The advantage of black box approach is that it does not depend on any specific implementation. Whether the design is implemented in a single ASIC, multiple FPGAs or board, is irrelevant. It forms a true conformance verification that can be used to show that a particular design implements the intent of a specification regardless of its implementation. Kin very ;large or complex design, black box approach requires some non functional modifications to provide additional visibility and controllability.

Additional software accessible registers to control some internal states can be provided. In complex design, some module is taken from third party. This IP (Intellectual Property) is fully verified, but to verify its working within our design, it is verified using black box approach. In my project, the design using an IP of 32 bit embedded processor from Tensilica. For this module, black box approach was used.

#### **1.6.2** White Box Functional Verification

As the name suggests, white box approach has full visibility and controllability of the internal structure and implementation of the design being verified. This approach has the advantage of being able to quickly setup an interesting combination of states and inputs or isolate any functionality. Results can be observed as verification progresses and the source of any problem can be located.

This approach is tightly integrated with a particular implementation and cannot be used on alternative implementations or future redesigns. It also require detailed knowledge of the design implementation to know which significant conditions to create and which results to observe. In my project, for module level functional verification, all the modules were verified using white box approach. This approach ensures that design behave properly with respect to any functionality. All FIFOs, counters or datapaths are appropriately steered and sequenced.

This approach is the main verification used to verify any design. It is the foremost important approach to verify any design that is done for the first time. It verifies the design from all respects. The designer modifies and updates the design as per the feedback from the functional verification team. The final outcome is the completely verified and almost correct design which can be synthesized and fabricated further.

#### **1.6.3** Grey Box Functional Verification

Grey box approach is a compromise between the aloofness of a black box approach and the dependence on the implementation of white box approach. As in black box approach, a grey box approach controls and observes a design through its top level interfaces, but it is aware of the internal controls and can use them. This approach is used based on the priority of the features to be verified. If a functionality is to be verified is not prime one, then to attain the deadline, grey box approach can be used.

#### 1.7 BUGS

Neither any human being nor any process is perfect. Hence, there is always a possibility of having a bug in the design. Bug can be in the small functionality of some micro module, timing mismatch, short circuit, open circuit, current/voltage tolerances, etc. Endless cycles are done to identify and locate the bug. The aim of bringup functional verification is to develop test cases to find bugs, which have occurred due to the

fabrication process, and the bugs that might have been missed during its functional verification at earlier stage. They aim to test the functionality of the design being manufactured.

Bugs usually come in three categories:

1) Bugs that have software work around.

2) Bugs that have minor impact on performance or behavior and may ultimately be tolerable or require a layer of respin just to be safe.

3) Bugs that are showshoppers and which actually requires a respin.

The bugs detected in the design after silicon are to be taken care by the software team as nothing can be done to the RTL now. Sometimes in case of some critical failure, extra external peripheral block can be added to nullify the effect of the bug. Other bugs are taken care of in the next version of the chip.

#### **1.8 Chip Bringup Verification**

This is a part of the complete chip verification process that consists of both verification and testing. It is done on both RTL and the first chip that has arrived from the fab. It is a sort of bringup functional test. It takes into account, the chip with all its peripheral devices and is a board level testing. The aim is not to verify every small sub module in the design but to verify the data paths within and outside to the chip.

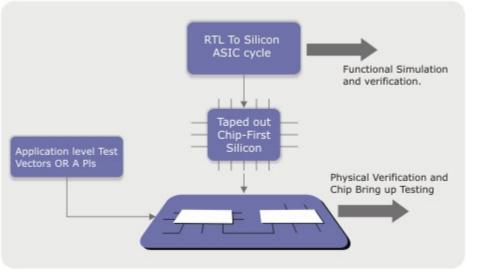

After the chip RTL is designed and redesigned from the feedback from the verification side, and after completion of all timing analysis of the chip design, the RTL gets ready for being getting fabricated. Hence, the chip RTL is ready for tap out. This is a very critical period and decision that the RTL is stable affects the cost of the final chip. Hence, this is done only after RTL is considered as being free from bugs. This RTL is given to the fab where the silicon cycle begins. The time between the chip RTL tap out and the arrival of first chip on silicon is used to develop the bringup environment, test cases and the operational board of the chip. The fig 1.3 depicts this phase of chip design.

Courtesy: eInfochips

Fig 1.2 The Chip On Board

The first task done is the finalization of the test plan for the bringup activity. This will include the tests to be written for the each module of the chip to check its functionality and datapath. More emphasize is given on following verification.

To verify core functionality

To verify interactions with peripheral blocks

To verify dataflow within and external to the chip

To simulate for the chip application.

The verification engineers starts with the development of the environment for the chip bringup. This is a verification done at a quite high level of abstraction. This is again done in terms of chip module. Each module is to be verified with its interactions with all its onchip modules and external devices. The environment is made reusable and generic so that it is applicable to all the modules of the chip. No signal is forced as in functional verification of the design. Every signal arrives from its source and passing thought all the hops in its path. This is to ensure the complete data flow.

As the bringup environment gets stable, test cases are written as per the test plan. References are taken from the test cases of functional verification. These test cases are written for the module of interest and the input to the module comes from its actual peripheral sources and is not forced like done in functional verification at module level.

The other task is the development of the operational board for the chip. This board is to be used to run all the test cases developed for bringup after they are simulated. The board as all peripheral devices required by the chip to accomplish its application. All the input source devices are present on board. This is board is used as a demo board later for chip marketing. The software team starts working on the development of the firmware for the chip. They develop the application code for the chip. Various algorithms required are also developed. The bugs which will be detected by the process of bringup verification are to be handled later by the software. Hence, the software team starts concentrating on such issues.

Other testing done on the chip is using the tester board. It consists of only the chip and no other peripheral devices. It aims to exercise chip will different combinations of test vectors. All the signals are forced on the chip in the test.

#### **1.9** The Verification Methodology

Methodology is the step by step procedure to be followed for successful accomplishment of any project. As digital logic designs grow larger and more complex, functional verification has become the number one bottleneck in the design process. Reducing verification time is crucial to project success. The only way to address this problem is to adopt a reuse-oriented, coverage-driven verification methodology built on the rich semantic support of a standard language. For Verification, the Methodology used contributes great to the final conclusion for the process. Design Methodology covers from plan to closure and it includes the Verification Methodology midway. Some Approaches are stated under:

#### Constrained-random Stimulus Generation

Traditional verification relies on directed tests, in which the testbench contains code to explicitly create scenarios, provide stimulus to the design, and check (manually or with self-checks) results at the end of simulation. Directed testbenches may also use a limited amount of randomization, often by creating random data values rather than simply filling in each data element with a predetermined value.By building randomization into the types of scenarios that are created, not just in the data values that get generated, additional tests are much more likely to hit corner cases and thereby find more design bugs.

#### Coverage-driven Verification

Coverage metrics serve two critical purposes throughout the verification process. The first is to identify holes in the process by pointing to areas of the design that have not yet been sufficiently verified. This helps to direct the verification effort by answering the key question of what to do next — for example, which directed test to write or how to vary the parameters for constrained-random testing.

#### Assertions based Verification

The capabilities of any verification environment can be enhanced by the addition of assertions, which are statements of design intent. Ideally, as the designer writes the RTL, he or she documents with assertions the requirements on how the design is expected to behave and the assumptions on interfaces with adjoining blocks. Assertions can range from low-level statements about how specific design elements should behave to high-

level, end-to-end rules about how information should flow through a design. Assertions can be specified in many ways, including with general RTL expressions, special statements within hardware verification languages, and the built-in assertion constructs

#### 1.10 High Level Verification Languages

Verilog and VHDL were widely used for verification languages. Due to increase in complexity of functionality within designs, the need for developing language that would aid verification grew. As a part of it, many new verification languages developed. These languages are very powerful in creating conditions which verification engineers require to verify the design from all aspects. Many features of powerful languages are blended together in these languages to support all new approaches. I will be discussing some high level verification languages. These languages are now evolving fr both design and verification. Today's system-on-a-chip designs require multi-discipline engineering teams with a range of skills covering embedded software, system architecture, RTL design and verification. Traditionally these teams use a variety of C modeling styles for architecture design and a variety of hardware description languages (HDLs) and hardware verification languages (HVLs) for RTL design and verification. These traditional methods have led to very complex design flows, prohibited reuse, and have increased the total time to market and development costs for today's chip designs.

Two industry standards have emerged to allow convergence of the different C-based and HDL and HVL-based approaches. These are SystemC, for C-based system-level modeling and SystemVerilog, providing a unified language for RTL design and verification. Both SystemC and SystemVerilog span multiple levels of abstraction. These languages can support verification at transaction level of abstraction. They enable ease call to functions of other languages and hence provide good interface. Assertion based approach is well supported. Object oriented approach and reusability is taken care of in these languages.

#### System Verilog

IEEE 1800TM SystemVerilog is the industry's first unified hardware description and verification language (HDVL) standard. SystemVerilog is a major extension of the established IEEE 1364TM Verilog language. It was developed originally by Accellera to dramatically improve productivity in the design of large gate-count, IP-based, bus-intensive chips. SystemVerilog is targeted primarily at the chip implementation and verification flow, with powerful links to the system-level design flow. SystemVerilog has been adopted by 100's of semiconductor design companies and supported by more than 75 EDA, IP and training solutions worldwide.

#### System C

SystemC provides hardware-oriented constructs within the context of C++ as a class library implemented in standard C++. Its use spans design and verification from concept to implementation in hardware and software. SystemC provides an interoperable modeling platform which enables the development and exchange of very fast systemlevel C++ models. It also provides a stable platform for development of system-level tools. The Open SystemC Initiative (OSCI) is an independent not-for-profit organization composed of a broad range of companies, universities and individuals dedicated to supporting and advancing SystemC as an open source standard for system-level design.

#### Vera

Vera® is an industry-leading testbench automation product that increases design quality by finding simple as well as corner-case bugs, quickly. Vera allows engineers to create coverage-driven tests using advanced testbench concepts like constrained-random stimulus generation, real-time data and temporal checking and extensive analysis of functional coverage. Vera combines next-generation constraint solving and coverage analysis engines with a proven reference verification methodology and interfaces to leading Verilog and VHDL simulators. Vera supports the OpenVera® hardware verification language, including OpenVera Assertions, and is an integral part of the Synopsys Discovery<sup>™</sup> Verification Platform.

#### e

It is the most powerful HVL. Specman is the compiler/debugger/simulator is for e language. Specman Elite offers a comprehensive verification environment that is based on the e hardware verification language (HVL). The Verisity's Specman Elite is acquired now by Cadence. It is playing an important part in developing reusable verification components.

### THE VERIFICATION METHODOLOGY & FLOW

#### 2.1 Introduction

Methodology is defined as (1) "a body of methods, rules, and postulates employed by a discipline", (2) "a particular procedure or set of procedures", or (3) "the analysis of the principles or procedures of inquiry in a particular field". The common idea here is the collection, the comparative study, and the critique of the individual methods that are used in a given discipline or field of inquiry. Methodology refers to more than a simple set of methods; rather it refers to the rationale and the philosophical assumptions that underlie a particular task.

Verification is a critical part in the specification to silicon path. Hence, it should be done with proper planning and proper methods to make the process effective and quicker. The ultimate aim is to attain the most critical challenges while maximizing overall speed and efficiency. Following an appropriate path is very important for this. Hence, for any verification process, first the approaches, methods, algorithms, sequences, etc is decided upon from all aspects.

#### 2.2 The Verification Methodology

As already mentioned earlier, the methodology adopted plays a vital role int the progress and accomplishment of the process. Verification remains the single biggest challenge in the design of system-on-chip (SoC) devices and reusable IP blocks. As designs continue to grow in size and complexity, new techniques emerge that must be linked by an effective methodology for significant adoption and deployment. The SoC industry needs a reuse-oriented, coverage-driven verification methodology built on the rich semantic support of a standard language. Different approaches are possible for targeting verification of a design.

#### 2.2.1 The Bottom Top Methodology

In the project, Bottom Top Methodology is followed. The designer have written the RTL Code for the design. But the design is not complete yet. It will be modified and new features will be added based on the feedback from verification process. In Bottom Top Methodology, the verification starts with from the base of the design. In the project, the complete design is divided into functional modules which can be individually verified. These modules are to be verified using white box approach with full visibility. The designer and verification engineer interact to find bugs with the design and modify the RTL to get a functionally correct design. The level of abstraction at module level is very low. Not many assumptions are made. Interest is to verify the design with transaction in

each signal. The modules are to be verified for all possible inputs and even the invalid inputs. Corner cases are to be identified to verify the design from all aspects. After the completion of this phase, the level of abstraction rises. Now all the modules are to be integrated to and verification is done for correctness of the interactions between the modules. At this time, the modules are assumed to be functionally correct and only there mutual interactions is verified. After this phase system level verification is done. The design is verified for its functionality with the all peripherals and system components. The level of abstraction is highest here. The approach will be clearer as I start with the Verification flow.

#### 2.3 The Verification Flow

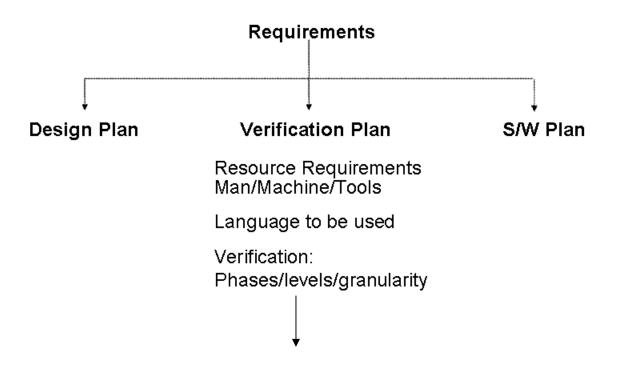

I will be discussing the complete flow followed by the company to achieve the verification. I will start with common approach for any designing and will proceed with concentration on the verification. Any project is the outcome of some requirement. As without any requirement, there is no profit in going for any project. Hence, depending on the market requirement and market availability for the project product, a project is finalized. Figure below shows the Verification Flow followed for the project. It shows the complete flow from Plan To Closure. Different Tools are used at each step. The Flow goes in loop as the project progresses. Depending on the feedback from tool or updation of RTL due to addition of new feature or fixing of some bug, the flow undergoes in a loop.

Fig2.1 Verification Flow

#### 2.3.1 Design Plan, Software Plan & Verification Plan

The Project Plan decides other plans for the project. These are the Design Plan, Software Plan and the Verification Plan. These three teams play part in the project. These are the most important teams responsible for successful completion of the project. Design Plan and Software Plan states all the requirements from there point of view.

#### **Verification Plan**

The Verification plan acts as a specification for the verification effort. It is used to define what is first time success, how the design is verified and which testbenches are written. The verification plan states everything related to Man/Machine & Tool requirements. It gives the approach to verify every module. The verification plan includes:

- 1. Requirements (Man/Machine) Verification.

- 2. The languages to be used for verification.

- 3. The tools to be used for all tasks in verification.

- 4. The engineers to be worked on the project and the duties to be assigned to them.

- 5. The requirements in terms of System OS, S/W Drivers, Application S/W, etc.

- 6. The CHIP configuration.

- 7. Level of granularity/abstraction for all modules to be verified.

- 8. Division of the complete verification process into different phases with deadlines defined for each of them.

- 9. All the verification specific things.

The verification process is divided into phases.

**First Phase** : This is the Block level verification. Each block is assigned to individual and is verified with interactions with the designer.

**Second Phase** : This is Cluster level verification. Few blocks with high mutual interactions are combined and are verified.

**Third Phase** : This is Full Chip level verification. All blocks are combined and the functionality of the complete design is verified.

**Fourth Phase** : This is System level verification. The chip is verified with the system in which it will be used. Third Party Models are included here.

#### 2.3.2 First Step To Project

As the complete plan for all three major team is ready, now they start working on the project. Design team starts the designing of individual blocks depending on the architecture finalized. Software team starts with the implementation of algorithm to be used to make sure that it will work in the design. If the algorithm works well, then RTL coding for it is done. The software team then starts with the necessary software required by the project.

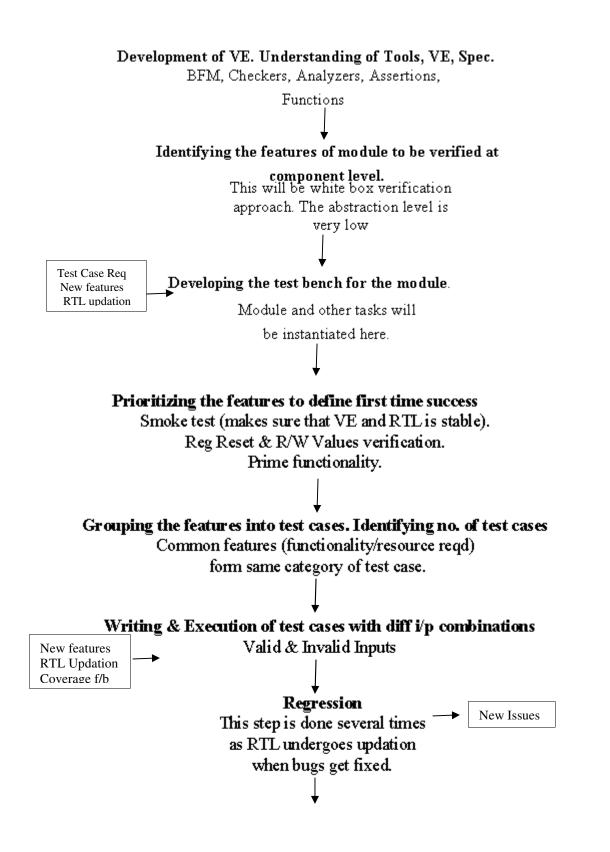

#### **Development of VE**

The verification team's task starts with complete understanding of the specification. IN our project, the chip works on a protocol. So, we need to completely understand that the protocol first and then the specifications stated for each block. While verifying, it is required to also check that designer stick to the protocol. Then all the tools to be used is studied. I have described all the tools used in our project in detail in later chapters. Then starts the development of Verification Environment. All the requirements required from VE is mentioned in verification plan. The VE is developed accordingly. The VE in our project is in C++ and Verilog. The BFMs (Bus Functional Models), Checkers, Analyzers, Assertions, etc are written as a part of VE.

#### 2.3.2 Identifying The Features

The development of VE is completed at this point. It would be modified or updated later depending on the requirements as verification proceeds. Now, each verification engineer is given individual module and it is his/her responsibility to verify it. Now, starts the identifications of the features to be verified. This is a white box approach and hence all the features have to be verified. There would be some features which are to be verified at full chip level and not at module level. e.g. interrupt propagation structure.

#### 2.3.4 Developing The TestBench

When the design will be verified, it is required that the design should be given the same environment which it will find when it will be actually used in the system. The testbench is like a universe for the design. Testbench is a closed system. It generates all the inputs and compares the outputs generated by the design. Testbench will configure the design as per the requirements by the test case which verify design functionality. It is important to be able to develop generic testbench which is applicable for verification of all functionality of the design. The testbench is updated as per the feedback from verification process later.

#### 2.3.5 Priotizing Features

For any design, few features are of prime importance. Bugs in such functionality implementing design, leads to more bugs in the functionalities depending on them. Hence, such functionality must be considered first. In any design, you will find many

configurable registers. The configuration, operation and output from the design depend on these registers. So, it is of prime importance to see that all registers are functionally correct.

#### 2.3.6 Grouping Into test Cases

The ultimate aim is to verify all the features of the design within the deadline. So, time taken is very important. Hence, the prime objective is to keep the number of test cases less and still be able to verify all the features. Hence, the features are grouped into same category of test cases depending on the functionality they implement. some features require similar configuration, granularity or verification strategies. Hence, to increase the productivity, these features should be grouped into common test case. Again here the priority among the features is always taken care of. Now, all the test cases required is known. Number of test cases required for each functionality verification is known.

#### 2.3.7 Writing & Execution Of Test Cases

The test cases are written and are executed with valid and invalid inputs. All possible corner cases are applied on the design. For the failing test cases, debugging is done. The source of problem is found. The issue could be related to VE, Test Case or RTL. Once it is confirmed that the problem is related to the RTL, bug is filled for that. Designer debugs the design and locates the problem. The RTL is modified accordingly to fix the bug. The test case is executed again. This process repeats till the test cases passes.

#### 2.3.8 Regression

As and when bugs are filed, the designer debugs the RTL and modifies it. Hence, the RTL goes on updating as the verification progresses. Hence, there can be a chance that a test case passing previously might fail with this new updated RTL. Hence, after every updating of RTL, regression of all test cases is done. Again, at the end of the verification, all test cases are executed for the same.

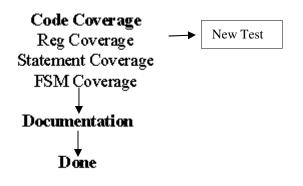

#### 2.3.9 Code Coverage

This is very important task to which defines the effort placed by verification engineers and the completion of the verification task. From the feedback from the coverage tool, new test cases required are written and executed. It is desirable to get 100% coverage. But this is a difficult task. Depending on the deadline of the project, the coverage required can be loosen.

#### 2.3.10 Documentation

This is the final step in the process and declares the closure of the verification process. It includes documenting all the effort done and the results generated. This documentation can be used by some other person or team in case the design is updated later.

#### 2.4 Designer – Verification Engineer Interaction

At all the steps discussed earlier, interaction between designers and verification engineers is required. Any open bug is discussed by both to come to a conclusion. The partition of the design into modules is done by the both teams together. Many DFV (Design For Verification) features are added to the RTL to aid the verification process. Some more register for configuration or some mux to bypass some functionality can be added.

#### **Design For Verification**

There are two major reasons for the presence of design errors (bugs) in a design. First, the sheer complexity of a module, often including multiple-state machines, makes it virtually impossible to anticipate all possible conditions to which the module can be subjected in the context of an application. Typically the state space is very large and bugs can be buried very deep into the logic. Hence, some corner cases may simply not have been anticipated in the implementation. Second, designing a module often requires the designer to assume a particular behavior on the interface, that is, make assumptions on the behavior of modules physically connected to the module under design. These assumptions are needed to assure minimum area/maximum speed micro architectures to be designed. Analyzing the bugs indeed shows that incorrect or imprecise assumptions are a major cause of design flaws.

To improve the quality of the design process we clearly have to address specification, design, and verification in a concerted manner. Similar to other seemingly independent tasks in the past such as manufacturing test, design quality needs to become the whole team's concern, and the methodology employed must support this notion. That is exactly what the DFV methodology offers coherent methodology to find design errors through constrained-random stimulus generation and advanced tools for formal state-space analysis, powerful means to eliminate ambiguity in specifications, and improved conformance checking capabilities to ensure that the imported design IP complies with required standards.

## THE MIME MODULE FOR FUNCTIONAL VERIFICATION

#### **3.1 Introduction**

The revolutionary growth of communication is further revolutionized by the evolution of optical networks and standard for it namely SONET & SDH. The need for chips to work in optical network is increasing and the market is increasing. Hence, an optical networking chip finds a good market in today's world. Depending on the customer's requirements and need, the company came up with a SONET/SDH Processor & Cross Connect chip. This chip is called OTII. It works on the SONET/SDH standard.

#### 3.2 The Protocols/Standards

#### 3.2.1 Historical Background

When data is transmitted over a communications medium, a number of things must be provided on the link, including framing of the data, error checking, and the ability to manage the link (to name a few). For optical communications these functions have been standardized by the ANSI T1X1.5 committee as Synchronous Optical Networking (SONET) and by the ITU as Synchronous Digital Hierarchy (SDH).

In those days, the telephone companies looked at optical communications as simply a replacement for the older wire or microwave communications they had been using for years. But then they encountered a practical problem. Vendors of optical communications equipment had used their own framing techniques on the optical fiber. Once you selected a vendor, you were stuck with that vendor for all the equipment in that optical network. Thus was born the concept of standards in optical communications. It's extremely important to recognize that the first standards for optical communications were focused on handling voice circuits, and especially legacy plesiochronous channels like DS-1s and DS-3s. If you keep this fact in mind, many of the odd things about SONET and SDH will make more sense. At the time that these standards were developed, the tremendous volumes of data traffic had not appeared and most people did not foresee it.

Fig3.1 Optical Network

#### 3.2.2 Introduction to SONET/SDH

SONET/SDH defines the low level framing protocol used on these optical links. By "framing", we mean a block of bits (or octets) which have a structure, and which utilize some technique which allows us to find the boundaries of that frame structure. Parts of the block may be devoted to overhead for the network provider to use to manage the network. Other parts will be dedicated to carrying payload, or information we want to communicate. The end-to-end connection through a SONET/SDH network is always called the "path." The connection between major nodes, such as between add/drop multiplexers is called a "line." And the link between an add/drop multiplexer and a regenerator, or between two regenerators, is called a "section." The SONET is a subset of SDH. So, i will be discussing the SONET first. It is equally applicable to SDH as well.

PTE = Path Terminating Equipment LTE = Line terminating Equipment STE = Section Terminating Equipment

Fig3.3 Basic SONET Frame