# MODELING AND CONTROLLING OF THE DC-UPS USING MICROCONTROLLER PIC 16F877

# Major Project Report Final Review

Submitted in partial fulfillment of the requirements

For the degree of

# MASTER OF TECHNOLOGY IN ELECTRICAL ENGINEERING

(Power Electronics, Machines and Drives)

By

Ghata Shashank Patel

12MEEP16

#

I like to dedicate my thesis to

Almighty and My Family...

# Undertaking For Originality of the Work

I, Ghata Shashank Patel(Roll No:12MEEP16), give undertaking that the Major Project entitled "Modeling and Controlling of the DC-UPS using Microcontroller PIC16F877" submitted by me, towards the partial fulfillment of the requirement for the degree of Master of Technology in Power Electronincs, Machines and Drives , Electrical Engineering, under Institute of Technology, Nirma University, Ahmedabad is the original work carried out by me and I give assurance that no attempt of plagiarism has been made. I understand that in the event of any similarity found subsequently with any published work or any Dissertation work elsewhere, it will result in severe disciplinary action.

.....

# Signature of Student

Date:

Place: Ahmedabad

Endorsed by:

## Faculty Guide

Prof. Tejas H. Panchal

Department of Electrical Engineering,

Institute of Technology,

Nirma University,

Ahmedabad.

#### **Industrial Guide**

Mr. Ajit Patel

Deputy General Manager,

Engineering Department,

Hitachi-Hirel Power Electronics Ltd,

Gandhinagar.

# Certificate

This is to certify that the Major Project Report entitled "Modeling and Controlling the DC-UPS using Microcontroller PIC16F877 submitted by Ms. Ghata Shashank Patel (Roll No: 12MEEP16) towards the partial fulfillment of the requirements for the award of degree in Master of Technology (Electrical Engineering) in the field of Power Electronics, Machines and Drives of Nirma University in the record of work carried out by her under our supervision and guidence. The work submitted has in our opinion reached a level required for being accepted for examination. The results embodied in this major project work to the best of our knowledge have not been submitted to any other University or Institution for award of any degree or diploma.

Date: 12/05/2014

## Faculty Guide

Prof. Tejas H. Panchal

Department of Electrical Engineering,

Institute of Technology,

Nirma University,

Ahmedabad.

# **Head of Department**

Department of Electrical Engineering

Institute of Technology

Nirma University

Ahmedabad

#### Industrial Guide

Mr. Ajit Patel

Deputy General Manager,

Engineering Department,

Hitachi-Hirel Power Electronics Ltd,

Gandhinagar.

#### Director

Institute of Technology

Nirma University

Ahmedabad

# Acknowledgement

Apart from the efforts of author, the success of any project depends on the guidelines and encouragement of many other individuals. I take this opportunity to express my gratitude to the people who have been instrumental in the successful completion of this project.

First and foremost, I gratefully acknowledge to my industrial Guide, Mr. Ajit Patel, DGM, Engineering Department at Hitachi-Hirel Power Electronics Pvt Ltd and my faculty guide Prof. Tejas H. Panchal, Assistant Professor, Institute of Technology, Nirma University. I thank them for their continuous efforts, co-operation, support and encouragement. I am grateful to them for giving me their precious time and guidance at every level of the project. Without their encouragement and guidance this project would not have materialized.

I would like to thank **Dr.P.N.Tekwani**, Head of Elect. Engg. Department of Institute of Technology, Nirma University for his valuable support to carry out the project work.

I also like to express my sincere thanks to all faculty members of Electrical Engg.Dept., Nirma University and my classmates, PEMD 2012-2014 for their help.

At the last but not the least I would like to express thank to God and my family for blessing me with all that I have today. Without your blessings and well wishes nothing would have been possible.

Ghata Patel

# Abstract

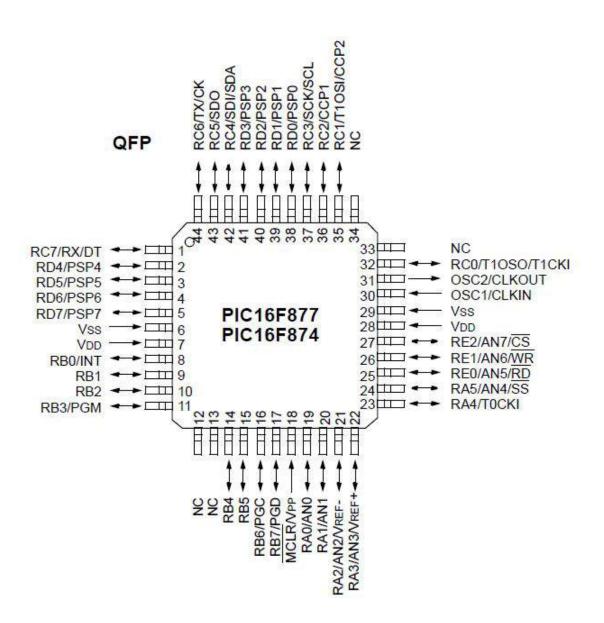

The uninterruptible power supply (UPS) is used in applications for which a loss of supply could have severe consequence. Out of the two types of UPS, the DC-UPS offers several advantages like efficiency, reliability, power quality and economy as compared to the AC-UPS. The DC-UPS is an internal part of the AC-UPS (DC-UPS + Inverter = AC UPS). If it is considered from the Inverter usage point of view, the DC-UPS is considered as a Off-line UPS. The DC-UPS can be used in applications like radio base stations and repeaters, SCADA systems, tower and obstruction lightening, remote telemetry, video cameras, gate openers, security systems, roadway caution signs, LED traffic controls, WiFi/WiMax back-up power, grid-tie solar systems, low voltage lighting, Railway coach battery charger etc. Due to the so many advantages offered, the DC-UPS is developed which has specifications:  $3 \phi$ , 50 Hz, 415 V AC input; 405 V DC, 25 A Output. The DC-UPS consists of a six pulse fullycontrolled rectifier, a choke, a capacitor and a battery bank containing 34 batteries, fuse, MCCB, thyristor firing circuit, feedback control circuit, power supply etc. For the easy controlling of the system parameters like voltage and current, a microcontroller PIC16F877 is used. This microcontroller is a 40-pin IC having 20 MHz clock input, 200 ns instruction cycle and many more features. The tasks like generation of the gating signals for thyristos, zero crossing detection of the input line-to-line voltage, conversion of analog signal to digital form and many more are taken care by the microcontroller.

# Abbreviations

| AC                 | Alternating Current                          |

|--------------------|----------------------------------------------|

| DC                 | Direct Current                               |

| UPS                | Uninterruptible Power Supply                 |

| EMI                | Electromagnetic Interference                 |

| PWM                | Pulse Width Modulation                       |

| PFC                | Power Factor Correction                      |

| SCADA              | Supervisory Control and Data Acquisition     |

| IGBT               | Insulated Gate Bipolar Transistor            |

| MOSFET             | Metal Oxide Field Effect Transistor          |

| THD                |                                              |

| WDT                |                                              |

| RAM                | Random Access Memory                         |

| CPU                |                                              |

| SSP                | Synchronous Serial Port                      |

| PSP                | Parallel Slave Port                          |

| USART Universal Sy | ynchronous Asynchronous Receiver Transmitter |

| ADC                | Analog to Digital Converter                  |

| SPI                | Serial Peripheral Interface                  |

# Nomenclature

| $I_L$ Load Current                                                     |

|------------------------------------------------------------------------|

| $I_B$                                                                  |

| $I_O$                                                                  |

| P <sub>O</sub> Output Power                                            |

| $V_S$                                                                  |

| $I_S$                                                                  |

| $V_{XL}$ Line Choke Voltage Drop                                       |

| $D_{max}$                                                              |

| $D_{min}$                                                              |

| $V_d$                                                                  |

| $I_d$                                                                  |

| $I_{ac}$                                                               |

| f                                                                      |

| $V_{ac}$                                                               |

| $V_m$                                                                  |

| $\phi$                                                                 |

| $E_{drm}$                                                              |

| $t_H$ Output High-level duration for the pulase generated using IC 555 |

| $t_L$ Output Low-level duration for the pulase generated using IC 555  |

| T                                                                      |

| $V_{drop}$                                                             |

| $B_m$                                                                  |

| $\eta$                                                                 |

| $\delta$                                                               |

| $K_w$                                                                  |

| $A_p$                                                                  |

# Contents

| U            | nder                            | taking For Originality of the Work                                                                                                                                                                                                                  | iii                                                      |

|--------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| $\mathbf{C}$ | ertifi                          | cate                                                                                                                                                                                                                                                | iv                                                       |

| $\mathbf{A}$ | ckno                            | wledgement                                                                                                                                                                                                                                          | v                                                        |

| A            | bstra                           | ct                                                                                                                                                                                                                                                  | vi                                                       |

| A            | bbre                            | viations/Nomenclature                                                                                                                                                                                                                               | vii                                                      |

| Li           | st of                           | Tables                                                                                                                                                                                                                                              | xii                                                      |

| Li           | st of                           | Figures                                                                                                                                                                                                                                             | xiii                                                     |

| 1            | 1.1<br>1.2<br>1.3<br>1.4<br>1.5 | UPS Configurations                                                                                                                                                                                                                                  | 1<br>2<br>3<br>4<br>5<br>6<br>10<br>11<br>11<br>12<br>15 |

| 2            | Bloc 2.1 2.2                    | ck Diagram and Technical Specifications of the DC-UPS  Block Diagram of the DC-UPS  2.1.1 Interfacing of Microcontroller with the peripheral circuits of the DC-UPS  Technical Specifications  2.2.1 Mains Input  2.2.2 DC Output Or DC Bus Charger | 16<br>16<br>19<br>23<br>23<br>23                         |

|              |                                 | 2.2.3 Protection                                                                                                                                                                                                                                    | 23                                                       |

CONTENTS

|   | 2.2.4 Indications                                                                                                                                                                                                                                                           |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 2.2.5 Metering                                                                                                                                                                                                                                                              |

| 3 | Design of Output LC Filter and Input Source Impedance  3.1 Calculations of Input Source Impedance  3.2 Design of Output LC Filter  3.2.1 Design of Inductor  3.2.2 Design of Capacitor  2.2  3.2.2 Design of Capacitor  2.3  3.3  3.3  3.3  3.3  3.3  3.3  3.               |

| 4 | Rating of SCR, Circuit Breaker and MCCB  4.1 Rating Calculation and Selection of SCR  4.1.1 Selection of SCR  4.1.2 Heat Sink Calculations  2.2 Selection of Circuit Breaker and MCCB  3.3 Selection of Circuit Breaker and MCCB                                            |

| 5 | Design of Power Supply5.1Schematic of Power Supply35.2Design of Transformer35.3Hardware results of the Power Supply module3                                                                                                                                                 |

| 6 | Design of Firing Circuit386.1Schematic Design of Firing Circuit386.1.1Design Calculations for Firing Circuit46.2Simulation of the Firing Circuit46.3Hardware result of the Firing Circuit Module4                                                                           |

| 7 | Desing of Feedback Circuit557.1 Design of Output Voltage Feedback Circuit557.2 Design of Output Current Feedback Circuit567.3 Design of Feedback circuit of Input Current and Input Voltage567.4 Simulation of Feedback Circuits567.5 Hardware result of Feedback Circuit66 |

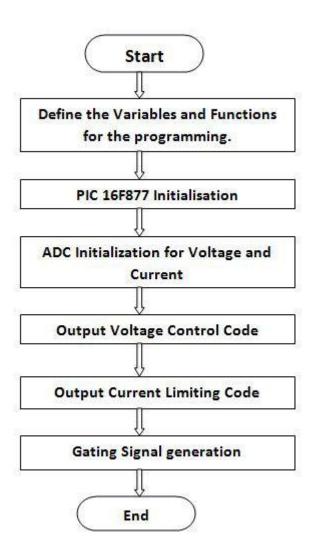

| 8 | PIC 16F877 and Implementation of Code608.1 PIC 16F877 and its features608.2 Implementation of C Code70                                                                                                                                                                      |

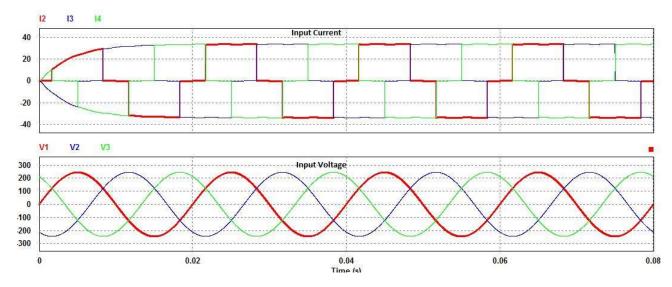

| 9 | Simulation Results  9.1 Introduction to PSIM                                                                                                                                                                                                                                |

| xi |

|----|

|    |

|            | Simulation of the DC-UPS in open loop        |                |

|------------|----------------------------------------------|----------------|

| -          | Results of the DC-UPS C-UPS Hardware results | <b>83</b>      |

| 11.1 Concl | n and Scope of Work in future usion          | 90<br>90<br>91 |

# List of Tables

| Ι | Table of Signals                                                   | 21 |

|---|--------------------------------------------------------------------|----|

|   | Data Given for Selection of SCR                                    |    |

| I | Parameters of Power Supply                                         | 32 |

| Ι | Hardware Result of the DC-UPS in No load and Full load condition . | 83 |

# List of Figures

| 1.1 | Block diagram of typical UPS system                                                        | 2   |

|-----|--------------------------------------------------------------------------------------------|-----|

| 1.2 | On-line UPS System                                                                         | 4   |

| 1.3 | Off-line UPS System                                                                        | 5   |

| 1.4 | The DC-UPS                                                                                 | 6   |

| 1.5 | The AC-UPS                                                                                 | 6   |

| 1.6 | Harmonics spectrum of ac input current for a passive PFC SMPS                              | 8   |

| 1.7 | DC-UPS supplying multiple loads                                                            | 13  |

| 1.8 | DC-UPS using Active Front End Rectifier                                                    | 14  |

| 1.9 | DC-UPS using Uncontrolled Rectifier followed by a boost chopper                            | 14  |

| 2.1 | Generalised Block diagram of the DC-UPS                                                    | 17  |

| 2.2 | A Six Pulse Fully-controlled Rectifier                                                     | 18  |

| 2.3 | Interfacing of Microcontroller with the peripheral circuits of the $\operatorname{DC-UPS}$ | 20  |

| 4.1 | Thermal Equivalent Circuit of SCR                                                          | 29  |

| 5.1 | Schematic Design of Linear Power Supply                                                    | 33  |

| 5.2 | Transformer for Power Supply                                                               | 35  |

| 5.3 | Power Supply Module                                                                        | 36  |

| 5.4 | Power Supply Module Result1: -12 V (Scale: X-axis= 2.5 ms per di-                          |     |

|     | vision nad Y-axis= 5 V per division)                                                       | 36  |

| 5.5 | Power Supply Module Result1: +12 V (Scale: X-axis= 2.5 ms per                              | 0.5 |

| 5.6 | division nad Y-axis= 5 V per division)                                                     | 37  |

| 5.0 | sion nad Y-axis= 5 V per division)                                                         | 37  |

|     | sion had 1-axis— 5 v per division)                                                         | 31  |

| 6.1 | Design of Firing Circuit                                                                   | 39  |

| 6.2 | A section of a Firing Circuit consisting of IC 555                                         | 40  |

| 6.3 | Firing Circuit Simulation Model                                                            | 45  |

| 6.4 | Signal from PIC:50Hz and Signal from IC 555:20KHz (Scale: X-axis                           |     |

|     | 0.002 sec per division and Y-axis 0.2 V per division)                                      | 46  |

| 6.5 | Firing Signal generation for the thyristor                                                 | 47  |

| 6.6 | Front view of the Firing Circuit                                                           | 48  |

| 6.7 | Back view of the Firing Circuit                                                            | 48  |

LIST OF FIGURES xiv

| 6.8  | A signal genrated by IC 555 ,<br>Switching Frequency 20 KHz, 20% ON Time and 80% OFF Time (Scale: X-axis<br>$50\mu$ sec per division and Y-axis |  |  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|      | 5V per division)                                                                                                                                |  |  |

| 6.9  | Gate Pulse Before MOSFET (Scale: X-axis 5 msec per division and                                                                                 |  |  |

| 0.0  | Y-axis 5 V per division)                                                                                                                        |  |  |

| 6.10 |                                                                                                                                                 |  |  |

| 0.10 | division and Y-axis 5 V per division)                                                                                                           |  |  |

| 6 11 | Expanded Gate pulse without Load (without SCR)(Scale: X-axis 100                                                                                |  |  |

| 0.11 | $\mu$ sec per division and Y-axis 5 V per division)                                                                                             |  |  |

| 6 12 | Gate pulse with SCR connected (Scale: X-axis 5 msec per division and                                                                            |  |  |

| 0.12 | Y-axis 5 V per division)                                                                                                                        |  |  |

| 6 13 | Expanded Gate pulse with SCR connected (Scale: X-axis 5 $\mu$ sec per                                                                           |  |  |

| 0.10 | division and Y-axis 5 V per division)                                                                                                           |  |  |

|      | division and 1-axis 5 v per division)                                                                                                           |  |  |

| 7.1  | Output Voltage Feedback Circuit Stage1                                                                                                          |  |  |

| 7.2  | Output Voltage Feedback Circuit Stage2                                                                                                          |  |  |

| 7.3  | Output Voltage Feedback Circuit Stage3                                                                                                          |  |  |

| 7.4  | Output Voltage Feedback circuit                                                                                                                 |  |  |

| 7.5  | Output Current Feedback circuit                                                                                                                 |  |  |

| 7.6  | A section of output current feedback circuit                                                                                                    |  |  |

| 7.7  | Input current feedback circuit                                                                                                                  |  |  |

| 7.8  | Input Voltage Feedback circuit                                                                                                                  |  |  |

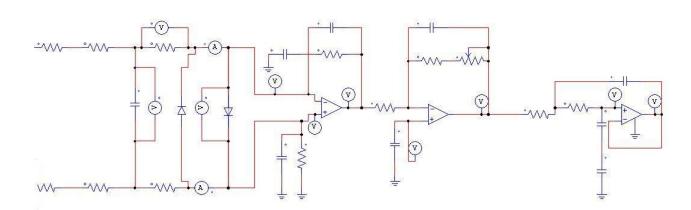

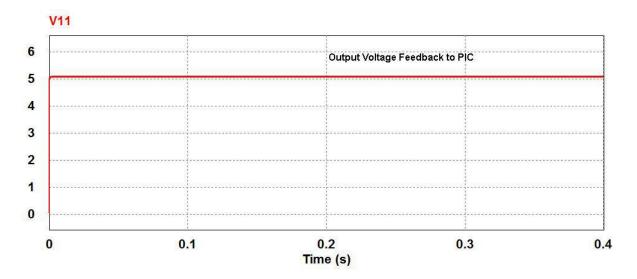

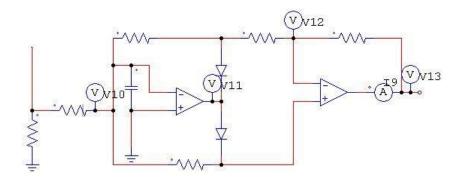

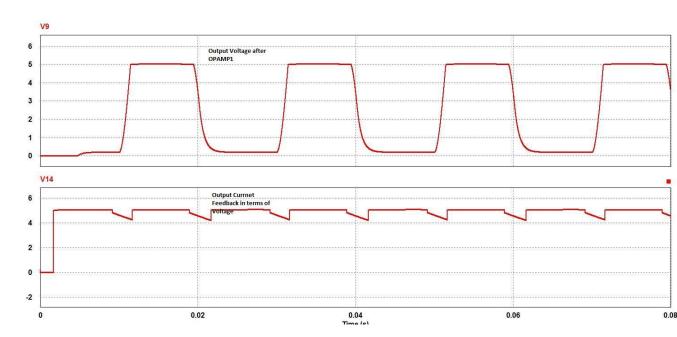

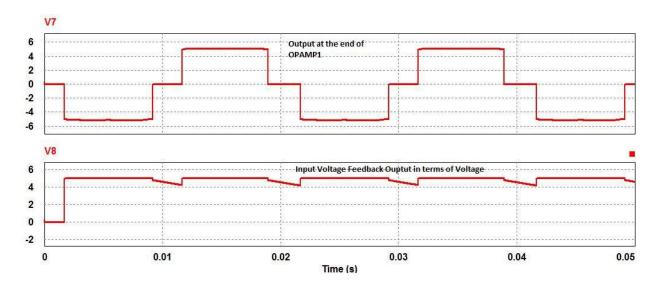

| 7.9  | Output Voltage feedback simulation model                                                                                                        |  |  |

|      | Output Voltage feedback waveform to PIC (Scale: X-axis 0.01 sec per                                                                             |  |  |

| , 0  | division, Y-axis 1 V per division                                                                                                               |  |  |

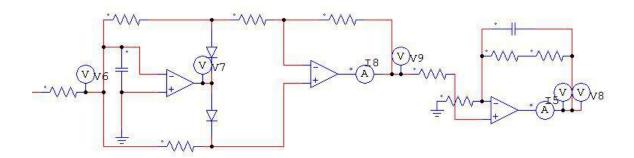

| 7.11 | Input Voltage feedback simulation model                                                                                                         |  |  |

|      | Input Voltage feedback waveform to PIC (Scale: X-axis 0.02 sec per                                                                              |  |  |

|      | division and Y-ais 1 V per division )                                                                                                           |  |  |

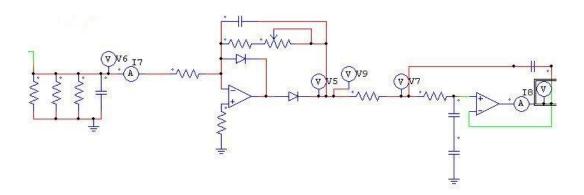

| 7.13 | Input Current feedback simulation model                                                                                                         |  |  |

|      | Input Current feedback waveform to PIC (Scale: X-axis 0.02 sec per                                                                              |  |  |

|      | division and Y-ais 1 V per division )                                                                                                           |  |  |

| 7.15 | Output Current feedback simulation model                                                                                                        |  |  |

|      | Output Current feedback waveform to PIC                                                                                                         |  |  |

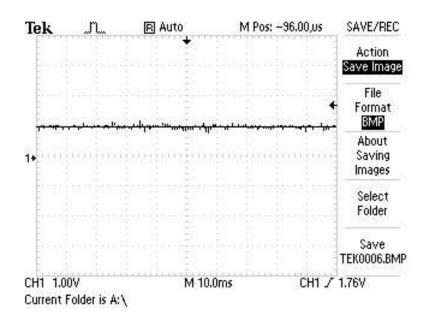

|      | Front view of the Feedback Circuit                                                                                                              |  |  |

|      | Back view of the Feedback Circuit                                                                                                               |  |  |

|      | Output of the Hardware                                                                                                                          |  |  |

|      |                                                                                                                                                 |  |  |

| 8.1  | Pin Diagram of the PIC 16F877                                                                                                                   |  |  |

| 8.2  | Flowchart of Implementation                                                                                                                     |  |  |

| 0.1  |                                                                                                                                                 |  |  |

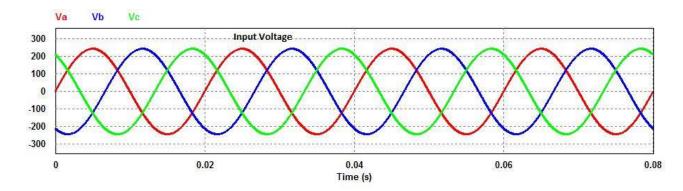

| 9.1  | Six pulse rectifier simulation model                                                                                                            |  |  |

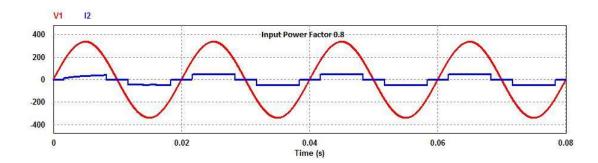

| 9.2  | Input Voltage(Phase) and Input Current(Line to line rms) of the rec-                                                                            |  |  |

|      | tifier (Scale: X-axis 0.02 sec per division and Y-axis 20 A per division,                                                                       |  |  |

|      | 100 V per division)                                                                                                                             |  |  |

LIST OF FIGURES xv

| 9.3   | Input power factor of the rectifier (Scale: X-axis 0.02 sec per division                                                                      |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------|

|       | and Y-axis 100 V per division)                                                                                                                |

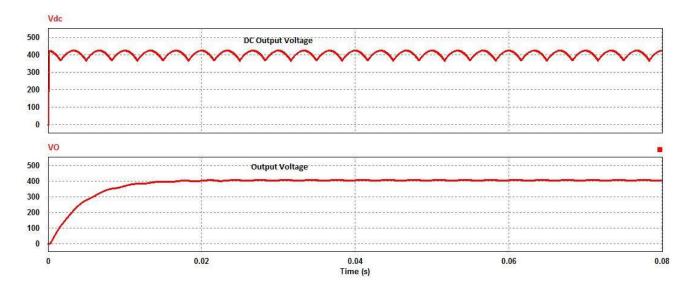

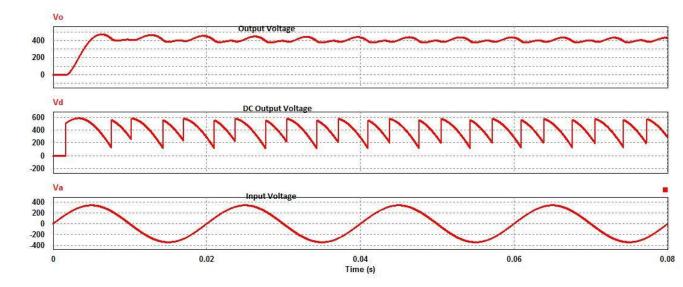

| 9.4   | DC output Voltage and Ouptut Voltage of rectifier (Scale: X-axis 0.02                                                                         |

|       | sec per division and Y-axis 5 A per division)                                                                                                 |

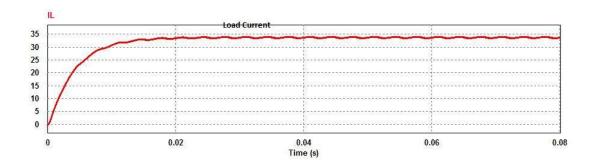

| 9.5   | Load current of rectifier                                                                                                                     |

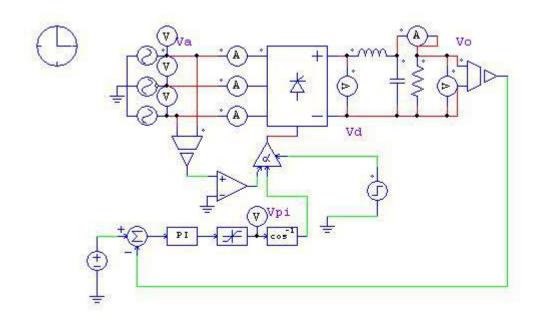

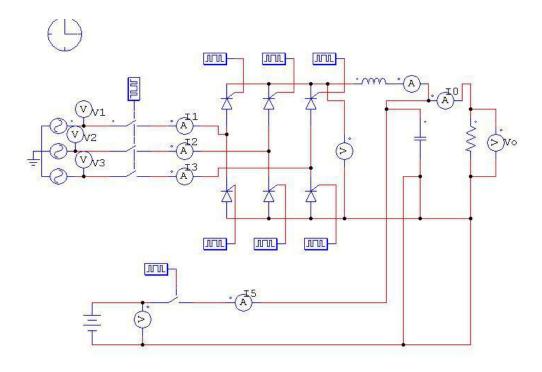

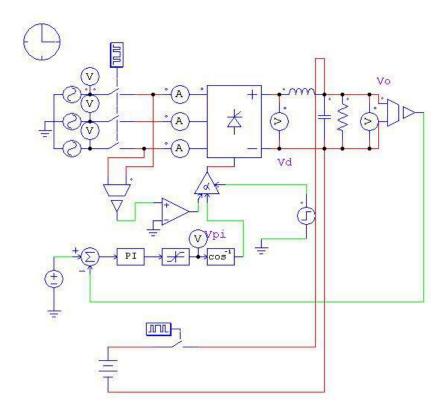

| 9.6   | Simulation model of Closed Loop Control of the Three-phase Contolled                                                                          |

|       | Rectifier                                                                                                                                     |

| 9.7   | Output Voltage and Output DC of closed loop controlled rectifier under normal conditions (Scale: X-axis 0.02 sec per division and Y-axis 100  |

|       | V per division)                                                                                                                               |

| 9.8   | Input Voltage Line-to-Line RMS of closed loop controlled rectifierunder normal conditions (Scale: X-axis 0.02 sec per division and Y-axis 200 |

|       | V per division)                                                                                                                               |

| 9.9   | Output Voltage, DC Output Voltage and Input line-to -line RMS Voltage under over voltage condition(Scale: X-axis 0.02 sec per division and    |

|       | Y-axis 200 V per division)                                                                                                                    |

|       | Simulation of UPS                                                                                                                             |

| 9.11  | Output Voltage Scale: X-axis- 0.01 sec per div and Y-axis- 100 V per                                                                          |

| 0.40  | div                                                                                                                                           |

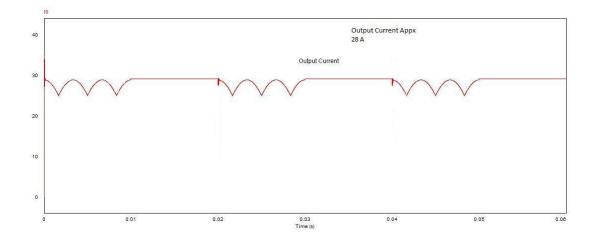

|       | Output Voltage Scale: X-axis- 0.01 sec per div and Y-axis- 10 A per div                                                                       |

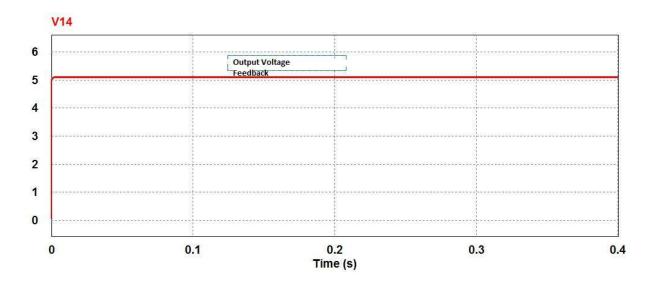

|       | Simulation model of Closed loop control of DC-UPS                                                                                             |

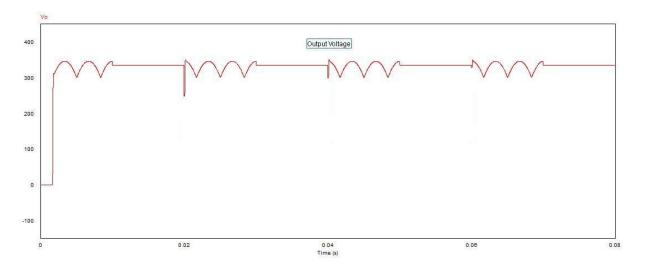

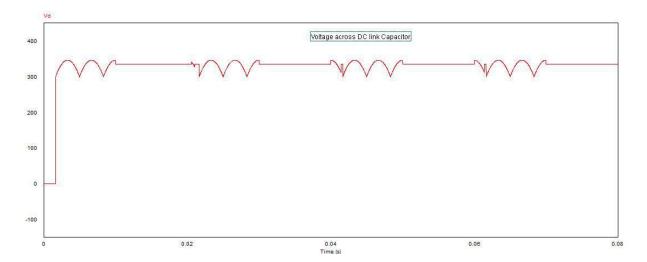

|       | Output Voltage Scale: X-axis- 0.02 sec per div and Y-axis- 50 V per div Voltage acrodd DC link Capacitor Scale: X-axis- 0.02 sec per div and  |

|       | Y-axis- 50 V per div                                                                                                                          |

| 10.1  | Rectifier Module                                                                                                                              |

|       | Hardware Set-up for DC-UPS                                                                                                                    |

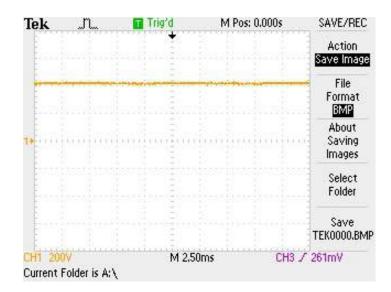

|       | Output Voltage (Scale: X-axis 2.5 msec per div and Y-axis 200 V per div) $V_O = 405$ V                                                        |

| 10.4  | DC Current 25A, CT ratio: 1/1000 (Scale: X-axis:2.5 msec per div                                                                              |

|       | and Y-axis: 200 mV )                                                                                                                          |

| 10.5  | Pulsating DC Output 405V (Scale: X-axis 2.5 msec per div and Y-axis 200 V per div)                                                            |

| 10.6  | Output Voltage Ripple 4.8V (Scale:X-axis 5 msec per div and Y-axis                                                                            |

| 10.0  | 5 V per div )                                                                                                                                 |

| 10.7  | Input Current 28 A(Scale: X-axis 5 msec per div and Y-axis 20 A per                                                                           |

| 100   | div                                                                                                                                           |

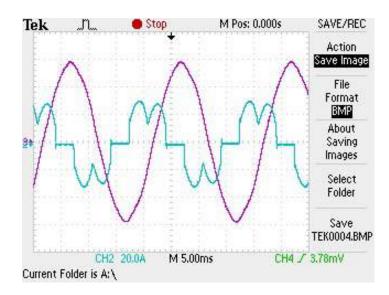

| 10.8  | Input Current and Input Voltage(Scale: X-axis 5 msec per div and                                                                              |

| 10.0  | Y-axis 20 A per div and 100 V per div                                                                                                         |

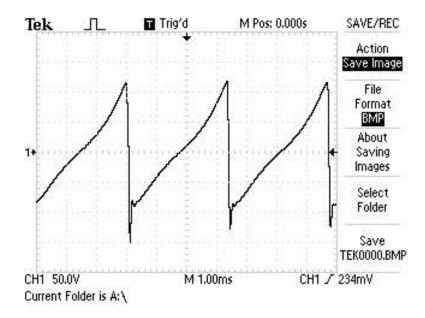

| 10.9  | Voltage across Inductor (Scale: X-axis 1 msec per div and Y-axis 50 V                                                                         |

| 10 14 | per div)                                                                                                                                      |

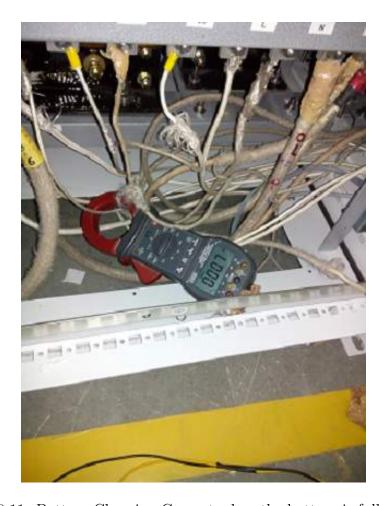

|       | OLoad Current Measured using ACCT                                                                                                             |

| 10.1  | Battery Charging Current when the battery is fully charged                                                                                    |

# Chapter 1

# Introduction to UPS

In applications, such as a medical intensive care systems, chemical plant process control, safety monitors or a major computer installations, where even a temporary loss of supply could have severe consequence, there is need to provide an uninterruptible power supply system which can maintain the supply under all conditions. Therefore, the function of a UPS is to provide an interrupted free supply to power to the ac load, which cannot be directly fed from dc source and dc is required to be converted into ac. A UPS a power conditioner which [1]:

- a. Provides good quality power to the load at all conditions of supply power.

- b. Regulates the load voltage when the mains voltage fluctuates.

- c. Provides complete isolation between the load and the mains.

- d. Suppresses the line transient (voltage spikes) and minimizes EMI (RFI) problems.

- e. Provides a constant voltage and constant frequency supply to the critical load.

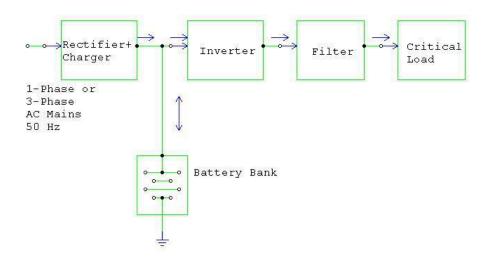

Figure 1.1 shows the block diagram of a typical UPS system. A rectifier converts a single-phase or three-phase ac voltage into dc, which supplies power to the inverter as well as the battery bank (to charge it). The inverter gets a dc input voltage from

Figure 1.1: Block diagram of typical UPS system

the rectifier when the ac mains is ON, and from the battery bank when the ac mains is OFF. Inverter converts this dc voltage into ac voltage and through a suitable filter applies it to the load. If the PWM inverter is used, then the filter can be eliminated. A static switch will connect or disconnect the battery from the input of the inverter depending on the status of ac mains.

# 1.1 UPS Configurations

Depending on the arrangement of the basic blocks, UPS systems are classified as:

- a. On-line or inverter preferred UPS system.

- b. Off-line or line-preferred UPS system.

- c. Line-interactive UPS system.

These configurations have been discussed in the following sections.

# 1.1.1 On-line UPS (Inverter Preferred)

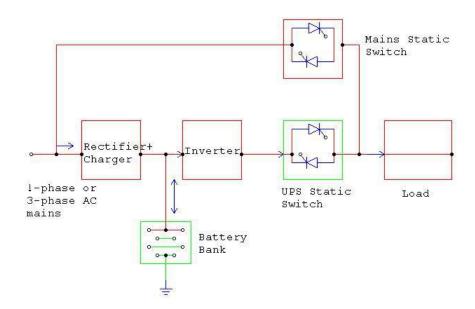

Fig 1.2 shows the block diagram of the on-line UPS systems. On this mode of operation, the load is always connected to the inverter through the UPS static switch. The UPS static switch is normally ON switch. It turns-off only when the UPS system fails. In that case the Mains Switch Off switch and used only when UPS is to be bypassed. The various operating modes are:

#### Mode I:

When the ac mains is ON, the rectifier circuit will supply the power to the inverter as well as to the battery. Therefore, it acts as a rectifier cum charger. Hence, its ratings are usually higher. The inverter output is connected to the load via UPS static switch. Battery will be charged in this mode.

#### Mode II:

If the supply power fails suddenly, the rectifier output will be zero and hence the battery-bank now supplies power to the inverter without any interruption and delay. There will not be any change in inverter as well as the load.

After restoration of the line supply, the charger supplies the inverter and recharges the battery automatically first in constant current mode and then in the constant potential mode. Various rates of battery charge may be set depending upon the application. The inverter has to be designed carefully because it supplies the load continuously. There should not be frequent failure of the inverter-system.

#### Mode III:

In case if the UPS fails (inverter fails), then the normally OFF mains static switch is turned-on which automatically transfers the ac lines to the load in less than cycle period with no phase discontinuity. This not only maintains power to the load, but also actuates the failure alarm signal to draw attention of the attendant. This type of system is more popular because it can provide fill isolation of the critical load from the ac line and also provides power conditioning. Its changeover time is very less and there is no interruption during transfer from line to battery and vice versa.

This system protects the critical load against surges, spikes, line noise, frequency and voltage variation, brownout and outages. All these protections are not available in the off line systems.

Figure 1.2: On-line UPS System

# 1.1.2 Off-line UPS(Line Preferred)

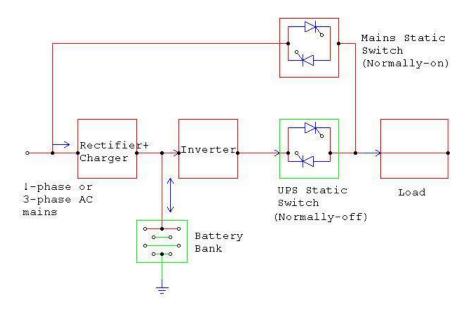

The block diagram for the off-line UPS is shown in 1.3. As it can be observed, the only difference between the off-line UPS is that mains-static switch here is a normally ON switch. It connects the ac mains directly to the load when the mains is ON. The battery charger is a stabilized one which maintains the battery on float at fully charged condition and at the same time provides stabilized power to the inverter. The other static switch, i.e UPS static switch is normally OFF switch. It is closed only when the mains fails. Thus, in the off-line UPS, the inverter comes into the circuit only when the mains fails.

The rectifier/charger has to do only one function, to charge the battery bank. Therefore, its size and power rating is lower than that of an on-line UPS system

Figure 1.3: Off-line UPS System

charger. Under the condition of mains failure, the static switch operate to disconnect the mains from the load and connect the load to the UPS output. The battery will then supply the power to the load via the inverter. The total time taken to sense the power failure and make a changeover from mains to UPS is about 5 ms (1/4 cycle). Here no isolation is provided between the load and mains and hence this UPS is not recommended for highly critical loads.

# 1.2 The AC-UPS and The DC-UPS

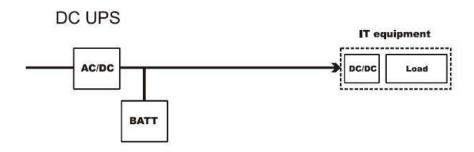

#### The DC-UPS:

The DC UPS is very simple in implementation and operation. The only parameter which requires management and supervision, is the voltage. This concept provides direct connection of the battery to the load, 1.4, which is a great advantage for reliable service.

Figure 1.4: The DC-UPS

## The AC-UPS:

In comparison, the AC UPS is far more complex and intricate to operate. All of the parameters: voltage, frequency, phase, and waveform require management, control and supervision, at a minimum. An ac bypass switch adds to the complexity.

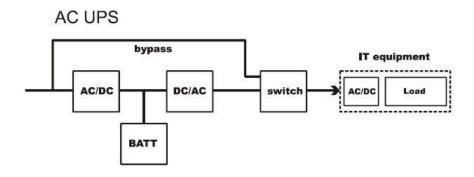

Figure 1.5: The AC-UPS

# 1.3 Difference between AC-UPS and DC-UPS

# A. Energy efficiency comparison[2]

The total efficiency of a direct current system can be made greater than in present ac systems owing to elimination of the extra conversion step of the inverters. The centralization of rectifiers and PFC circuits can be made more efficient than when each single device includes rectifying the ac to dc with (more or less effective) power factor correction. Moreover, all equipment connected to the mains network would be embraced by the PFC technique in contrast to now, when a lot of small, and indeed also large, equipment is not included. Use of dc will provide higher energy efficiency and reduced losses when DC/DC converters are used in electric equipment instead of AC/DC power supplies.

The efficiency of electric power distribution and equipment can become 5-20 % higher as compared to the present ac solutions. DC/DC converters can reach an efficiency of 85-90 % as compared to AC/DC power supplies which provide an efficiency of 65-75 %, typical values of PC power supplies.

Even if you compare best-in-class AC/DC to DC/DC you find a 2-5% advantage to the DC/DC, at a lower cost. A number of factors contribute to the lower power losses. Such factors are fewer conversion steps and that continuously running inverters, used in AC UPS equipment, no longer are needed. The reduced losses in the power supplies also means less cooling requirements for the premises.

The buildings can be designed for an effective connection of alternative energy sources, for instance photovoltaic- or fuel cells. Connection of such cells to a direct current system is highly efficient as no losses for transformation to alternating current will occur.

Altogether, the efficiency of the use of electrical power is estimated to increase by 5-20 % for applications that could be supplied with direct current. This estimation also takes into account losses of a potentially needed transformer to isolate the dc plant from the incoming ac grid. If the better efficiency of the DC UPS means that otherwise necessary cooling equipment can be eliminated or reduced, a figure up to 30 % may be reached.

The most common class of AC UPS has 85 % efficiency, but many UPS systems operate on lower efficiency. If connected directly to a high voltage line a best in class DC UPS can operate at 98 % efficiency.

# B. Power quality comparison

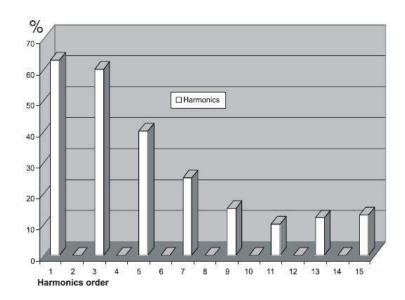

The most important deficiencies of power quality in AC UPS systems are the current harmonics, Fig 1.6. They lead to very high currents in the neutral line causing risk of fire and disturbances in operation. The harmonics give rise to leakage currents, disturbing earth fault breakers and generating stray currents with undesirable magnetic fields which may disturb equipment and annoy people. Leakage currents may disturb operating function, reduce the lifetime of equipment and, if worst comes to worst, destroy it due to strongly increased wear of e.g. ball bearings of fans in ventilation systems etc.

Figure 1.6: Harmonics spectrum of ac input current for a passive PFC SMPS

#### C. Reliability Comparision

Now, due to IT/telecom convergence, AC UPS is introduced on a large scale in telecommunication systems and other mission critical use, reliability has become more important for UPS technology than before. The requirements traditionally imposed by telecom systems on the power supply system and the portion of unavailability

that may be allocated to the power supply system of a telecom installation is 510-7, which is equivalent to 15 seconds of service disruption per year. This requirement was derived from the service level needed for telephony service given in Bellcore standards to 5.3 min (5 nines 99,999 %) telephony service down time per year as a target level. The difference is found to be as large as 7600 times in advantage of the DC UPS. In large-scale operation and use, this difference will give a valuable contribution to overall performance and economy on system level for the operators and the public, when using internet.

## D. Economy

The economical aspects of operating a data centre is complex and involves many parameters. One dominant factor is cost for the total energy supply and system inclusive of cooling. Lowest possible heat dissipation i.e. highest possible efficiency in equipment is of course a key factor. But other aspects like the reliability of the power supply system and the power quality are important for a continuous low cost operation. Simplicity and good overview facilitates maintenance and low cost for service and trouble shooting.

Operators face a situation where the heat dissipation has become the limiting factor for expansion of data centres. Modern blade servers has become so compact, powerful and heat producing, that the data centre cooling system has become a bottle neck blocking expansion. Expensive data centre floor area can not be used unless the complete cooling system is upgraded. This leads to extreme marginal effects in cost. Conversely even small improvements in efficiency will have tremendous impact on cost.

A qualitative estimation shows that there definitely is a potential for great savings in total cost of operation of data centres by using DC UPS. We judge the range to be of 10 to 30

# 1.4 Application of DC-UPS

The applications of the DC-UPS are listed below: [3]

- a. SCADA Systems reliable glitch free power with long-term back-up power

- b. Tower and Obstruction Lighting beacons stay flashing during a utility power outage

- c. Remote Telemetry tolerates voltage drops from long power lines

- d. Video Cameras keep on seeing even when the power goes out

- e. Gate Openers provide continued access during a power outage or storm

- f. Security Systems operate even when the power is cut

- g. Roadway Caution Signs continue working when needed most

- h. LED Traffic Controls maintain traffic flow during an outage

- i. DC Industrial Controls use back-up power for control and monitoring on the factory floor

- j. WiFi/WiMax Back-up Power keeps communications up and running for public safety

- k. Grid-tie Solar Systems charge 12 or 24 Volt batteries with high voltage DC

- 1. Low Voltage Lighting stays lit and provides safety on walkways, stairs, and exit indicators, provides complete isolation between the load and the mains.

The above mentioned applications are the low power applications of the DC-UPS.

There are also high power applications of the DC-UPS such as,

a. In railways as battery charger (RCB- Railway Battery Coach).

b. Telecom power supply in the rural area or at a place where electricity is not available all the time.

# 1.5 Literature Survey

# 1.5.1 Overview of UPS

An Uninterruptible Power Supply, or UPS, is an electronic device that provides an alternative electric power supply to connected electronic equipment when the primary power source is not available. Unlike auxiliary power, a UPS can provide instant power to connected equipment, which can protect sensitive electronic devices by allowing them to shut down properly and preventing extensive physical damage. However, a UPS can only supply energy for a limited amount of time, typically 15 to 20 minutes. Although its use can extend to a virtually unlimited list of applications, in past years the UPS has become even more popular as a means of protecting computers and telecommunication equipment, thus preventing serious hardware damage and data loss.

UPS systems provide for a large number of applications in a variety of industries. Their common applications range from small power rating for personal computer systems to medium power rating for medical facilities, life-support systems, data storage, and emergency equipment, and high power rating for telecommunications, industrial processing, and online management systems. Different considerations should be taken into account for these applications. As an example, a UPS for emergency systems and lighting may support the system for 90-120 minutes. For other applications like computer backup power, a UPS may typically support the system for 15-20 minutes. If power is not restored during that time, the system will be gracefully shut down.

If a longer backup period is considered, a larger battery is required. For process

equipment and high power applications, some UPS systems are designed to provide enough time for the secondary power sources, such as diesel generators, to start up. [4]

There are two types of UPS: (i) AC-UPS and (ii) DC-UPS

#### What is DC-UPS?

Direct Current Uninterruptible Power Supply presents the superior method of simple parallel redundancy and direct contact between the load and the backup battery, providing emergency power to a load when the input power source (main power) fails. Besides the increased reliability, DC UPS is a Green Power solution to energy conservation and cost-cutting, as well as obvious advantages in security and operation making this the ideal choice for powering today's Smart Grid Communication equipment.

# 1.5.2 Topologies of the DC-UPS

There are so many topologies are available for DC-UPS. Out of these the following three topologies are well-known:

- a. Using Active front end rectifier

- b. Using the uncontrolled rectifier followed by a boost chopper

- c. Using a thyristorised six pulse rectifier

#### Using Active front end rectifier

This kind of rectifier is the IGBT based PWM rectifier.

In this topology, we can get almost unity input power factor and THD less than 5%. IGBT does not provide protection against surges and spikes occured in the input side of the DC-UPS. IGBT has less current handling capacity than that of the thyristor.

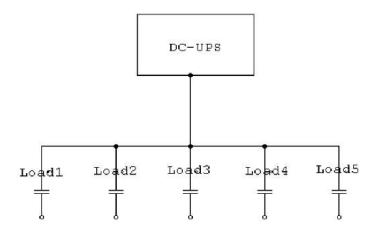

Figure 1.7: DC-UPS supplying multiple loads

Due to this, IGBT based rectifier cannot be used in the DC-UPS where the current capacity is required to be higher.

And also the switching losses are higher in this case due to the higher switching frequency of the IGBT.

In the system as shown in the fig(1.7) where the DC-UPS is supplying the multiple load, if we are using the active front end rectifier and any spikes and surges occurs and rectifier fails, all the loads connected will not get the power supply. So there is also the question of reliability in this scheme.

Fig(1.8) shows the front end rectifier (PWM rectifier) supplying the load.

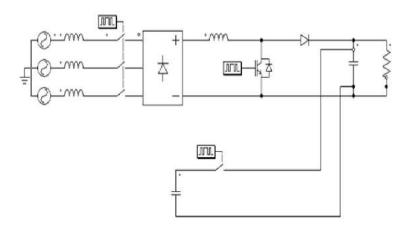

## Using the uncontrolled rectifier followed by a boost chopper

In this case we can get the input power power factor around 0.93. And also the losses associated with are higher due to the additional conversion stage of the chopper i.e. DC-DC power conversion. So the efficiency of this scheme is poor as compared to other two topologies.

## Using a thyristorised six pulse rectifier

This topology provides higher reliability and also higher efficiency.

Figure 1.8: DC-UPS using Active Front End Rectifier

Figure 1.9: DC-UPS using Uncontrolled Rectifier followed by a boost chopper

But the maximum power factor in the input side is around 0.8 which can be improved using the PFC.

So this topology is better than the above two topologies and this scheme is widely used.

Using this scheme, we can operate the system upto 25-30 % of the full load. After that the power factor of the system will be leading and that can create the problem in the source and control system.

# 1.6 Summary

We have discussed the different topologies of the DC-UPS and also the advantages of the DC-UPS over AC-UPS.

So from the above discussions, in this project a 3- $\phi$  DC-UPS system with the thyristorised six pulse rectifier will be developed.

# Chapter 2

# Block Diagram and Technical Specifications of the DC-UPS

The DC-UPS is an internal part of the AC-UPS (DC UPS+ Inverter= AC-UPS). Unlike, the AC-UPS, the DC-UPS does not have the inverter i.e DC to AC conversion stage. As discussed in the Chapter 1, the DC-UPS is better as compared to the AC-UPS in terms of Reliability, Economy, Energy Efficiency and Power Quality.

# 2.1 Block Diagram of the DC-UPS

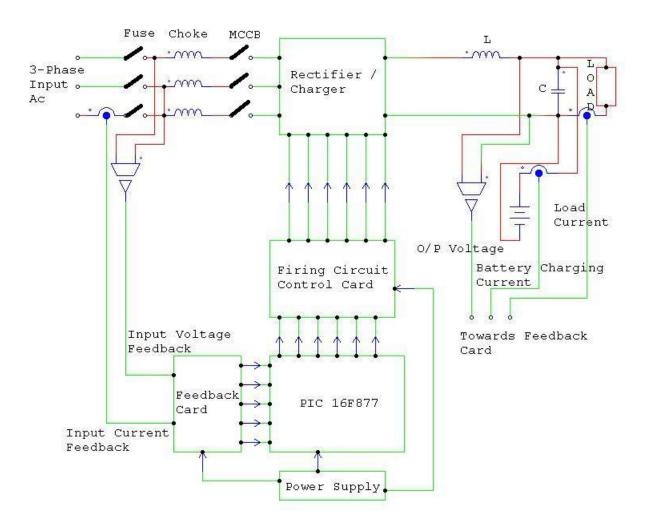

The generalised block diagram of the DC-UPS is as shown in the figure 2.1. The microcontroller based DC-UPS consists of three-phase fully controlled rectifier, a firing circuit for thyristors, a feedback circuit, a power supply, a battery- bank etc.

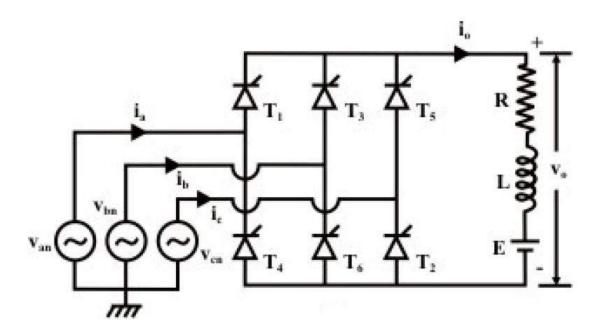

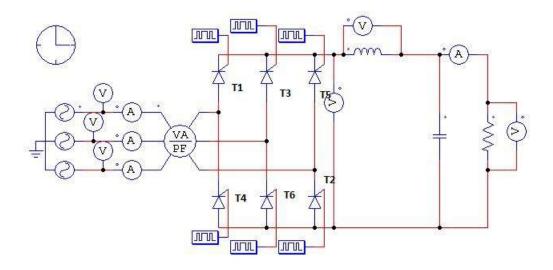

## Three Phase Fully Controlled Rectifier

The circuit diagram of the three-phase fully controlled rectifier is as shown in figure 2.2. The rectifier is used to convert AC into DC. The rectifier is used as a charger and it will supply the DC-load directly. When mains are on, the rectifier supplies the load directly and also charges the battery-bank. When mains are off, the rectifier is off and the load is fed from the battery.

Figure 2.1: Generalised Block diagram of the DC-UPS

Figure 2.2: A Six Pulse Fully-controlled Rectifier

# The Feedback Circuit

In this case, we shall measure the following quntities to control input voltage, input current, output DC voltage, battery charging current and load current.

- a. RY line voltage

- b. YB line voltage

- c. BR line voltage

- d. Input current

- e. Output DC voltage

- f. Battery charging current

- g. Load current

#### Output LC Filter

The output LC filter is used to smoothen the DC output. So that the ripple in the output dc voltage will be less than 2%.

#### The Battery Bank

When mains are on, the rectifier supplies the load directly and also charges the battery-bank. When mains are off, the rectifier is off and the load is fed from the battery. Based on the demand of the system, the battery charges in either constant voltage or constant current mode. It can charge either boost or float mode.

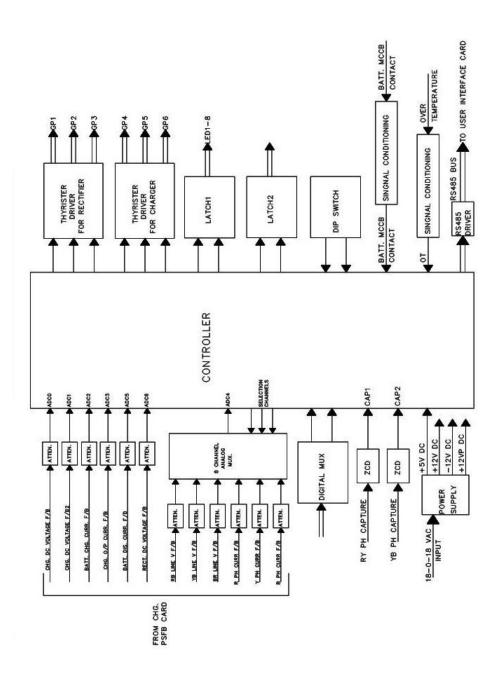

# 2.1.1 Interfacing of Microcontroller with the peripheral circuits of the DC-UPS

The interfacing of the microcontroller with the peripheral circuits of the DC-UPS is shown in the fig(2.3)

## POWER SUPPLY:

This module generates +12 V DC, -12 V DC, +12 VP DC and +5 V DC from I/P AC (18-0-18 V). +5 V acts as power supply to the controller, latches and analog as well as digital multiplexers. +12 V and -12 V are used for DC supply of operational amplifier ICs. +12 VP is used for thyristor gate drive section.

#### SIGNAL CONDITIONING AND ATTENUATION:

This module provides appropriate attenuation/amplification as well as filtering to the analog signals from charger PSFB card and converts them into acceptable range of the ADC of microcontroller (+5 V). Following table shows the different conditioning provided to the various signals.

Figure 2.3: Interfacing of Microcontroller with the peripheral circuits of the DC-UPS

Table I: Table of Signals

| SR. NO. | SIGNAL               | CONDITIONING PROVIDED                  |

|---------|----------------------|----------------------------------------|

| 1       | CHG. DC VOLTAGE F/B  | Attenuation, gain setting, filtering   |

| 2       | CHG. DC VOLTAGE F/B2 | Attenuation, filtering                 |

| 3       | BATT. CHG. CURR. F/B | Attenuation, gain setting, filtering   |

| 4       | CHG. O/P CURR. F/B   | Attenuation, gain setting, filtering   |

| 5       | BATT. DIS. CURR. F/B | Attenuation, gain setting, filtering   |

| 6       | RECT. DC VOLTAGE F/B | Attenuation, filtering                 |

| 7       | RY LINE VOLTAGE F/B  | Rectification, gain setting, filtering |

| 8       | YB LINE VOLTAGE F/B  | Rectification, gain setting, filtering |

| 9       | BR LINE VOLTAGE F/B  | Rectification, gain setting, filtering |

| 10      | R PH CURR. F/B       | Rectification, gain setting, filtering |

| 11      | Y PH CURR. F/B       | Rectification, gain setting, filtering |

| 12      | B PH CURR. F/B       | Rectification, gain setting, filtering |

#### 8 CHANNEL ANALOG MULTIPLEXER:

This module selects a particular analog input analog input among six analog inputs like RY line voltage, YB line voltage, BR line voltage, R Ph current, Y Ph current, B Ph current as per selection signals received from the micro controller and routs that signal to the ADC input channel of microcontroller. These Inputs are used for metering and alarms purpose.

#### RY and YB LINE CAPTURE:

This module detects zero crossing of input RY line voltage and YB line voltage. Micro controller captures these ZCD waveforms and monitors frequency and phase sequence of input line voltages.

#### MICROCONTROLLER

This module performs following tasks.

a. It captures these ZCD waveforms from the RY and YB line capture module and monitors frequency and phase sequence of input line voltages.

#### CHAPTER 2. BLOCK DIAGRAM AND TECHNICAL SPECIFICATIONS OF THE DC-UPS22

- b. It controls the soft start of rectifier as well as charger.

- c. It converts different analog signals from the signal conditioning and attenuation module to the digital form and depending on them it controls the o/p voltage as well as o/p current of charger.

- d. It monitors Over temperature condition and generates alarm in appropriate condition.

- e. It controls LED indication through latch.

- f. It monitors battery MCCB contact.

- g. It generates alarms depending on analog signal reading.

- h. It controls communication with the UI card.

#### THYRISTOR DRIVER:

Micro Controller generates six firing pulses to fire SCR at preset value. This firing pulses are AND with high frequency pulses to convert into high frequency. This high frequency pulses are given to Current Amplifier circuit involving MOSFET and pulse transformer. Out of these six pulses three pulses are used for rectifier soft start. And other three pulses are used for the soft start and control of the charger.

#### LATCH:

Latch controls LED indication as per selection and control signals from the microcontroller.

## 2.2 Technical Specifications

## 2.2.1 Mains Input

Voltage: 415 V +- 15 %; Three-phase Three wire

Frequency: 50 Hz + 5%

Input Power Factor: 0.75 to 0.8 @ full load

## 2.2.2 DC Output Or DC Bus Charger

Voltage: 357 V to 459 V DC

(Total no of Batteries are 34

Max battery Charging Voltage= 13.5 \* 34= 459 V

Min battery Charging Voltage= 10.5\* 34= 357 V)

Voltage Regulation : 1%

Max DC Bus Voltage Ripple : 2 % rms

Overall Efficiency: 97%

### 2.2.3 Protection

- a. Short circuit protection

- b. over voltage protection

- c. under voltage protection

#### 2.2.4 Indications

- a. DC Voltage High

- b. DC Voltage Low

- c. Input under Voltage

### CHAPTER 2. BLOCK DIAGRAM AND TECHNICAL SPECIFICATIONS OF THE DC-UPS24

- d. Input over voltage

- e. System on Battery

- f. Low Battery

- g. Low Battery cut-off

- h. Overload

- i. Over temperature trip

- j. DC Ground Fault

## 2.2.5 Metering

- a. Input Voltage

- b. Output Voltage

- c. Load Current

- d. Battery Charging Current

- e. Battery Discharging Current

## 2.3 Power Sizing Calculations

Load Current  $(I_L)=20$  A

Battery Charging Current  $(I_B)=5$  A

$$TotalOutputCurrent(I_O) = I_L + I_B$$

(2.1)

$$I_O = 20 + 5 = 25 \text{ A}$$

$$OutputPower(P_O) = V * I_O (2.2)$$

$P_O = 459*25 = 11.475 \text{ KW}$

$$InputPower = \frac{P_O}{OverallEfficiency}$$

(2.3)

Input Power=11.475/0.97 = 11.829 KW

$$InputKVA = \frac{InputPower}{PowerFactor}$$

(2.4)

Input KVA= 11.829/0.8 = 14.78 KVA

$$InputLineCurrent = \frac{InputKVA}{3^{1/2} * InputVoltage}$$

(2.5)

Input Line Current= 14.78/(1.73\*415) = 20.57 A per phase

# Chapter 3

# Design of Output LC Filter and Input Source Impedance

## 3.1 Calculations of Input Source Impedance

Here, the voltage drop in the line to line choke is 4-6%.

$V_S$ = 240 V per phase

Line choke voltage drop  $V_{XL} = 5\%$  of 240 V =240\*5/100= 12 V per phase  $I_S = 20.57$  A

$$Z = 2 * \pi * f * L \tag{3.1}$$

$$L = \frac{I_S}{V_{XL} * 2 * \pi * f} \tag{3.2}$$

$L{=}20.57/(12^*2^*3.14^*50){=}\ 5.459\ \mathrm{mH}$

## 3.2 Design of Output LC Filter

## 3.2.1 Design of Inductor

$$R = \frac{V_d}{I_d} \tag{3.3}$$

## CHAPTER 3. DESIGN OF OUTPUT LC FILTER AND INPUT SOURCE IMPEDANCE27

$$R=460/25=18.4 \Omega$$

$$RippleFactor = \frac{I_{ac}}{I_d} \tag{3.4}$$

Ripple Factor= 30 %

$$I_{ac} = \frac{4 * V_m}{3 * 2^{1/2} * \pi * (R^2 + 4 * \omega^2 * L^2)^{1/2}}$$

(3.5)

$$I_d = \frac{2 * V_m}{\pi * R} \tag{3.6}$$

f = 6\*50 = 300 Hz

Using the equations 5.4, 5.5, and 5.6, we can get L=26.9 mH

## 3.2.2 Design of Capacitor

Ripple factor = 2%

$V_d = 2\%$  of 459 V=(459\*2)/100 =9.18 V

$$V_{ac} = \frac{V_m}{4 * 2^{1/2} * f * R * C} \tag{3.7}$$

$$V_d = V_m * (1 - \frac{1}{4 * f * R * C})$$

(3.8)

$$RippleFactor = \frac{V_{ac}}{V_d} \tag{3.9}$$

Using equations 5.7, 5.8 and 5.9, we can find out the value of C=1647  $\mu$ F

# Chapter 4

# Rating of SCR, Circuit Breaker and MCCB

## 4.1 Rating Calculation and Selection of SCR

### 4.1.1 Selection of SCR

To determine the selection of SCR, first of all we need to calculate the Repeatative peak off-state voltage, RMS and Average current.

The datas available for the calculations are listed below:

Table I: Data Given for Selection of SCR

| Parameters        | Values |

|-------------------|--------|

| Vin               | 415 V  |

| Iout              | 25 A   |

| Iout rms          | 25 A   |

| Form Factor       | 1.7321 |

| fin               | 50 Hz  |

| Overload Factor   | 1.5    |

| Overload Duration | 10 s   |

Figure 4.1: Thermal Equivalent Circuit of SCR

Table II: Data for Heat Sink Calculation

| Parameters                                   | Values              |

|----------------------------------------------|---------------------|

| Maximum junction Temperature                 | 125 C               |

| Vto.25                                       | 1.1 V               |

| Vt0.125                                      | 0.8V                |

| Rjs                                          | 1.1 C/W             |

| Rsa                                          | $0.55 \mathrm{C/W}$ |

| Ambient Temperature Ta                       | 45 C                |

| No of switches per heat sink                 | 6                   |

| No of parallel devices on the same heat sink | 1                   |

| Cooling Method                               | Natural Air Cooling |

| Pdevice                                      | 10 W                |

| Ptot                                         | 61 W                |

$$E_{DRM} = E_{RRM} = V_i n * 2^{1/2} * OverloadFactor$$

(4.1)

$E_{DRM} = =415*2^{1/2}*2=1173 \text{ V}$

where  $E_{DRM}$ = Repeatative Peak off-state Voltage

So we need to select the SCRs having ratings of 1400V and 50 A (rms).

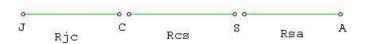

## 4.1.2 Heat Sink Calculations

The datas for the calculations for the heat sink are given below:

a. Total temp rise on Heat sink= $R_{sa}^*P_{tot}=0.55^*$  61 =33.55 C

- b. Temp at Heat Sink=  $T_s = T_a \, + \, 34$  =45+34=79 C

- c. Total temp rise on junction= $R_{js}$ \*  $P_{device}$  =1.1\*10 =11 C

- d. Temp at Junction= $T_j = T_s + 11 = 79 + 11 = 90$  C

The device to be chose is SKKH27, which is a combination of two SCRs.

## 4.2 Selection of Circuit Breaker and MCCB

In this case the input current I = 20.57 A

For selection of Circuit Breaker, we need to take CB current I= 125% of 20.57 A = 125\*20.57/100 = 25.71 A

Overload Duration= 10 sec

the  $I^2$ t rating of CB= 25.71<sup>2</sup>\*10 =660  $A^2$ sec

And same procedure has to be followed for the selection of the MCCB. While selecting the CB or an MCCB, care must be taken that

$$Fuse I^2 t < Thyristor I^2 t \tag{4.2}$$

## Chapter 5

# Design of Power Supply

This module generates +12 V DC, -12 V DC, +12 VP DC and +5 V DC from I/P AC (18-0-18 V). +5V acts as power supply to the controller, latches and analog as well as digital multiplexers. +12 V and -12 V are used for DC supply of operational amplifier ICs. +12 VP is used for thyristor gate drive section.

## 5.1 Schematic of Power Supply

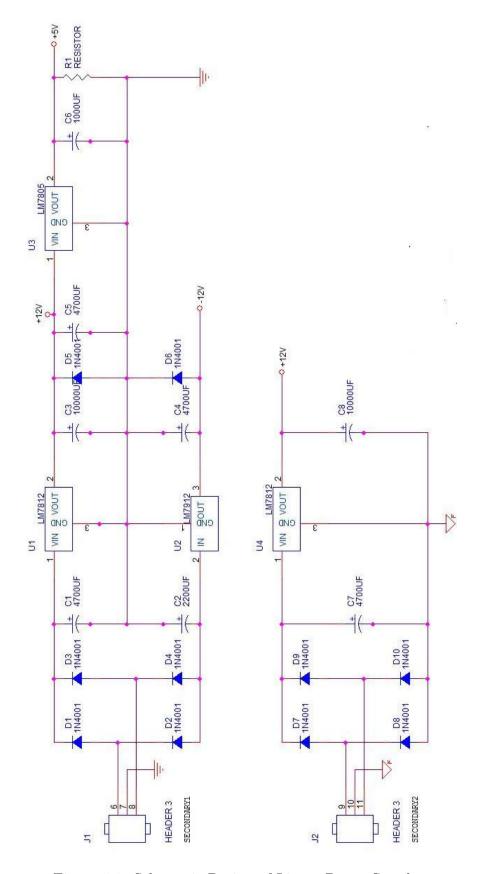

This is a linear regulated power supply. It is designed to supply microcontroller and OP-AMPs. To generate the +12 V, IC 7812 is used and to generate the -12 V, IC 7912 is used and to generate the +5 V, IC 7805 is used. +12 V, -12 V and +5 V are generated using a common ground and another +12 V is generated using an isolated ground.

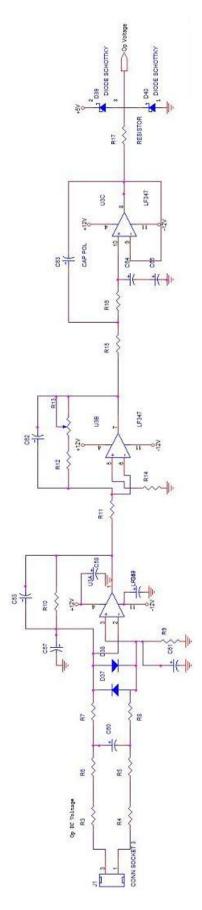

The schematic design of the power supply is as shown in the fig(10.2).

#### Calculations of Capacitance

$$V_{(ripple)} = \frac{I}{2 * f * C} \tag{5.1}$$

Vripple is to be considered as a 1% of the volatge at that point.

So considering eq 5.1, we can get the values of Capacitance as shown in the table.

Table I: Parameters of Power Supply

| Parameter                            | Values               |

|--------------------------------------|----------------------|

| Transformer primary voltage Vp       | 240 V                |

| Transformer secondary1 volatge Vs1   | 23.29 V              |

| Transformer secondary2 Voltage Vs2   | 9.31 V               |

| Current in the circuit I             | 1 A                  |

| Power consumption in secondary 1 Ps1 | 27 W                 |

| Power Consumption in secondary Ps2   | 12 W                 |

| Transformation ratio Vp/Vs1          | 10:1                 |

| Transformation ratio Vp/Vs2          | 25:1                 |

| C1                                   | $4700~\mu\mathrm{F}$ |

| C2                                   | $2200~\mu\mathrm{F}$ |

| C3                                   | $10000 \ \mu F$      |

| C4                                   | $10000 \ \mu F$      |

| C5                                   | $4700~\mu\mathrm{F}$ |

| C6                                   | $1000~\mu\mathrm{F}$ |

| C7                                   | $4700~\mu\mathrm{F}$ |

| C8                                   | $10000 \ \mu F$      |

| %hline D1-D10                        | 1N4001               |

Figure 5.1: Schematic Design of Linear Power Supply

## 5.2 Design of Transformer

## Design of Secondary 1

- a. Output Voltage at IC 7812 and IC 7912= +12 V and -12 V respectively

- b. So the total dc output at the regulator output= 24 V

- c. Min. Voltage drop across each IC= 2 V

- d. Min. Voltage at the regulator input = 24+4=28 V

- e. Min. Losses in the rectifier = 1.25 V

- f. Conversion Factor from AC to DC= 28V/1.25 = 22.4 V

- g. To maintain 28V DC at the rectifier output, we required 22.4 V at the transformer secondary.

- h. Min. AC voltage required  $V_{in}=V_s=22.4/0.85=26.35 \text{ V}$

- i. Transformation Ratio= $V_p/V_s = 240/26.35 = 9:1$

- j. Power Consumption in control Circuit (PCB) P= V\*I=(12\*1)+(12\*1)+(5\*1)=27 W

#### Design of Secondary 2

- a. Output Voltage at IC 7812 = +12 V

- b. So the total dc output at the regulator output= 12 V

- c. Min. Voltage drop across each IC= 2 V

- d. Min. Voltage at the regulator input= 12+2= 14 V

- e. Min. Losses in the rectifier = 1.25 V

- f. Conversion Factor from AC to DC= 14V/  $1.25=11.2~\mathrm{V}$

Figure 5.2: Transformer for Power Supply

- g. To maintain 14 V DC at the rectifier output, we required 11.2 V at the transformer secondary.

- h. Min. AC voltage required  $V_i n = V_s = 11.2/0.85 = 13.17 \text{ V}$

- i. Transformation Ratio= $V_p/V_s$  =240/13.17 =18:1

- j. Power Consumption in control Circuit (PCB) P= V\*I=12\*1=12 W

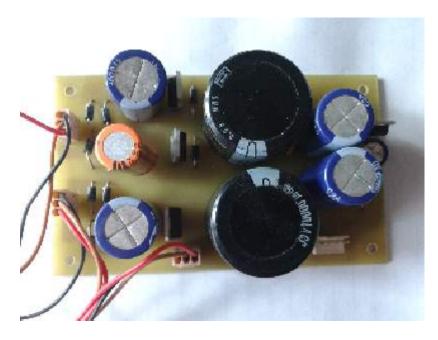

## 5.3 Hardware results of the Power Supply module

Figure 5.3: Power Supply Module

The hardware of the power supply module is as shown in fig5.3.

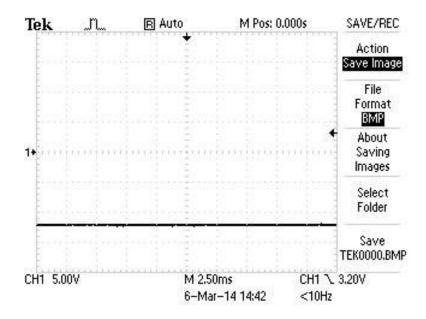

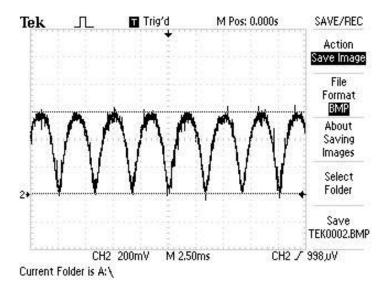

Figure 5.4: Power Supply Module Result1: -12 V (Scale: X-axis= 2.5 ms per division nad Y-axis= 5 V per division)

This -12 V output can be got across the anode terminal of diode D6 and ground.

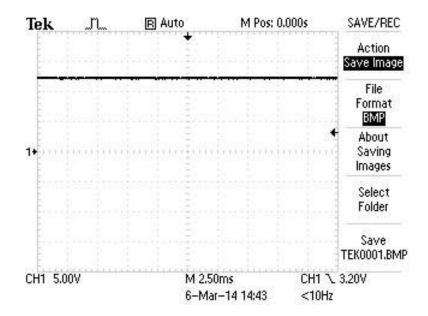

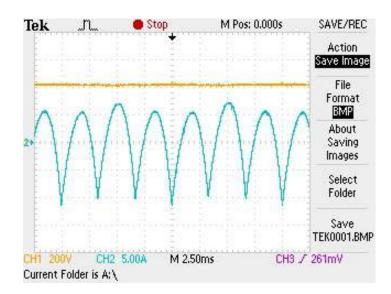

Figure 5.5: Power Supply Module Result1: +12 V (Scale: X-axis= 2.5 ms per division nad Y-axis= 5 V per division)

This +12 V output can be got across two terminals: (i) across capacitor C5 and (ii) across terminal 3 of IC U4 and ground.

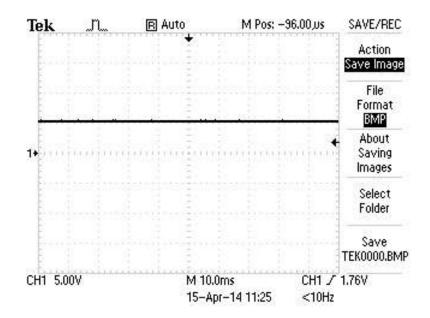

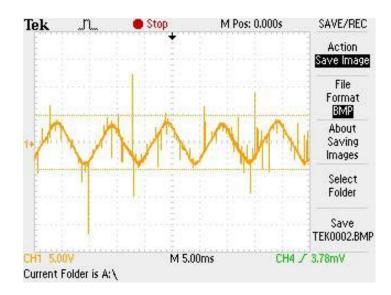

Figure 5.6: Power Supply Module Result1: +5 V (Scale: X-axis= 10 ms per division nad Y-axis= 5 V per division)

This +5 V output can be got across capacitor C6.

# Chapter 6

# Design of Firing Circuit

## 6.1 Schematic Design of Firing Circuit

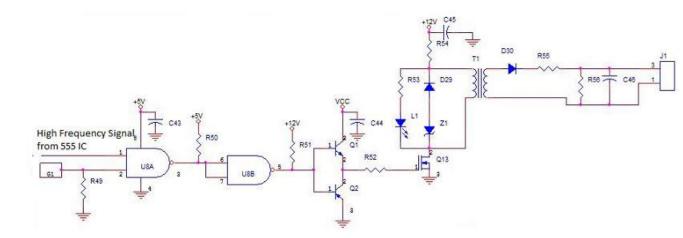

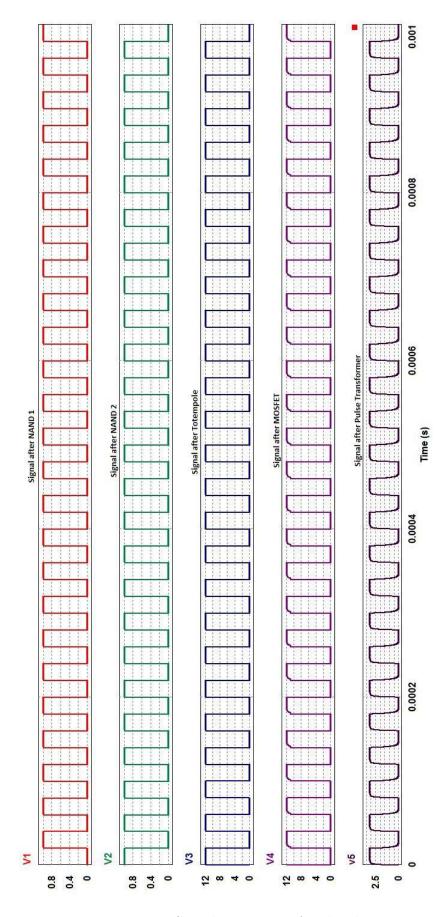

Figure 6.1 shows the firing circuit for the six pulse rectifier. It consists of two NAND gates, a combination of an NPN and PNP transistor (Totempole arrangement), a MOSFET and a pulse transformer. The detailed description of the circuit is explained below.

To generate the firing sequence for the thyristors the following steps needs to be followed.

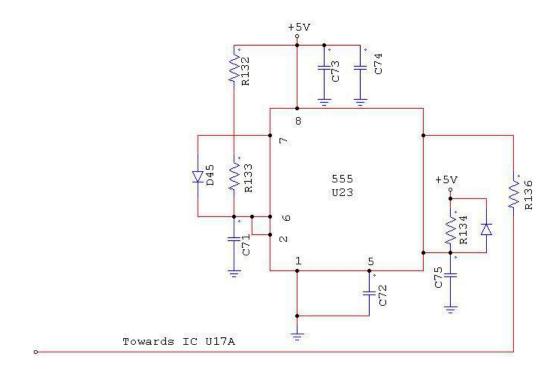

- a. A pulse train is generated using the multivibrator IC 555. The frequency of this pulse is approximately 20 KHz.(Refer Fig 6.2). The frequency of the pulse depends on resistors  $R_{133}$ ,  $R_{132}$  and capacitor  $C_{71}$ . Here U23 is the IC 555. The calculations for the same are shown in the next section.

- b. Six different pulses of 50 Hz having different phase shifts for all the six thyristors are provided by the microcontroller.

- c. A pulse train from the IC 555 and the pulses from the microcontroller are processed using NAND gate(U8A) as shown in Fig 6.1.

- d. The generated pulse is given to NAND gate(U8B) which functions as an invert-

Figure 6.1: Design of Firing Circuit

ing buffer. Both the NAND gates are part of the single IC 40107. In the ablove steps the highest amplitude of the pulse will be 1.

- e. This pulse is given to the transistor to tempole arrangement that also works as a buffer. In this case when the voltage at the common base point of the arrangement will be higher than the above NPN transistor will conduct and when the voltage at that point will be less then the ground level than below PNP transistor will conduct. This way the pulse will pass through it. Here the amplitude of the pulse will be converted to 12 V.

- f. A MOSFET is a high frequency semiconductor switch. In this case it will allow the train of pulse of higher frequency to pass throught it. And thus the current handling capacity of the pulse will be increased

- g. A pulse transfomer is provided to maintan the isolation between the control and power circuit.

- h. LED is provided to check the continuity of the pulses. And combination of diode and a zener diode is used to clamp the noises in the circuit.

Figure 6.2: A section of a Firing Circuit consisting of IC 555

Similar to the circuit shown in fig 6.1, we need six similar circuits for all the six thyristors of the rectifier. The signal generation at the end of each section is shown in fig6.4 and fig6.5 using simulation.

The fig2.2 in chapter 2, the three phase fully controlled rectifier is shown. There are a set of switches are provided for single phase i.e.T1 and T4 for R-phase, T3 and T6 for Y-phase and T5 and T2 for B-phase. This two switches of the single phase are complementory in nature i.e they cannot be turned on at the same time otherwise the short circuit will take place. At a time only two switches out of six are conducting. Above three switches have their cathodes at the same potential but the lower switches have their cathodes at different potential so we need to provide the isolation between each cathode and gate terminal.

## 6.1.1 Design Calculations for Firing Circuit

### Astable operation of Timer IC 555

$C_{71}$  charges through  $R_{132}$  and  $R_{133}$  and discharges through  $R_{133}$  only.

Threshold Voltage Level=  $0.67*V_{CC}$

$$=3.35 \text{ V}$$

Trigger Voltage Level=  $0.33*V_{CC}$

$$=1.65 \text{ V}$$

Decoupling CONT voltage to ground with a capacitor can improve operation.

$$V_{CC} = 5 \text{ V}$$

$$V_{I(Reset)} = 5 \text{ V}$$

$$I_{O} = 200 \text{ mA}$$

$$R_{132} = 2.88 \ \Omega$$

$$R_{133} = 1.44 \ \Omega$$

$$C=10 \mu F$$

$$R_{136}=1 \text{ K}\Omega$$

Output high-level duration,

$$t_H = 0.6938(R_{132} + R_{133})$$

C

$$=0.693*4.32*10*10^{-}6=30 \mu sec$$

Low-level Duration,

$$t_L = 0.693(R_{133}) \text{ C}$$

$$=0.693*1.44*10*10^{-}6 = 10 \mu sec$$

$$T=t_H + t_L = 40 \mu sec$$

$$f=144/(R_{132}+2R_{133})C$$

$$=144/5.76*10*10^{-6} =20 \text{ KHz}$$

$$OutputDriverdutyCycle = \frac{t_L}{t_L + t_H} = \frac{R_{133}}{R_{132} + 2R_{133}} = 0.80$$

(6.1)

$$OutputWaveformdutyCycle = \frac{t_H}{t_L + t_H} = 1 - \frac{R_{133}}{R_{132} + 2R_{133}} = 0.2$$

(6.2)

$$LowtoHighRatio = \frac{t_L}{t_H} = \frac{R_{133}}{R_{132} + R_{133}} = 0.33 \tag{6.3}$$

Frequency of the signal from the Microcontroller = 50 Hz

### U8 is the NAND gate IC 40107.

Current Handling Capacity of U8 = 70 mA.

$$V_{DD}=5$$

V

$$R_{109}=5/70^*10^{-3}=714~\Omega$$

$$R_{110}=12/~70^*10^{-3}=1714~\Omega$$

The

### Totempole arrangement (Combination of NPN and PNP transistors)

$$I = 500 \text{ mV}$$

$$V_{Drop} = 0.7 \text{ V}$$

$$R_{111} = 12 \text{-} 0.7 / 500 = 22.6 \Omega$$

selected NPN transistor is H44 and PNP transistor is H45.

## Flyback Converter (Consistiong of a MOSFET)

Data Given,

Input Voltage  $V_S$ =12 V

Tolerance of Input Voltage= 1%

DC Output Voltage  $V_{DC} = 12 \text{ V}$

Output Voltage Ripple= 1%

Output Current  $I_O = 2 \text{ A}$

Output Current Ripple = 5%

Switching Frequency = 20 KHz

Flux Density  $B_m = 0.2 \text{ T}$

Efficiency  $\eta = 0.8$

Duty Cycle  $D_{max}=0.75$

Window Utilisation Factor  $K_w = 0.4$

Diode Drop= 1.5 V

Current Density  $\delta = 3 \text{ A/mm}^2$

Isolated Flyback Converter

$$V_{Smax} = V_S + 1\% = 13.2 \text{ V}$$

$$V_{Smin} = V_S - 1\% = 10.8 \text{ V}$$

$$D_{min} = (V_{Smin} * D_{max})/V_{Smax} = 0.37$$

$$P_{02} = (V_O + V_D + 5\% \text{ of } V_O)I_O = 29.4 \text{ Watt}$$

AreaProduct,

$$A_P = \frac{D^{1/2} * P_{02} * (1 + \frac{1}{\eta})}{K_w * J * B_m * f} = 1003mm^4$$

(6.4)

But selected  $A_P = 10159.20 \text{ mm}^4$  and the selected port core is **P18/11**.

and so  $A_c = 136 \text{ mm}^2$ ,  $A_w = 74.7 \text{ mm}^2$ .

Consider  $N_1/N_2=0.66=n$

$$N_1 = \frac{V_{Smax} * D_{max}}{B_m * A_c * f} = 8 \tag{6.5}$$

$$n = \frac{N_2}{N_1} = \frac{V_O + V_D + 5\% of V_O}{V_{Smax} * D_{max}}$$

(6.6)

$N_2 = 12$

$$I_2 = I_o * D_{max}^{1/2} = 1.34A (6.7)$$

$$I_1 = \eta * I_2 = 1.072A \tag{6.8}$$

$$Gauage of primary wire, a_1 = I_1/J = 24 (6.9)$$

$$Gauageofsecondarywire, a_2 = I_2/J = 26$$

(6.10)

$$L_1 = \frac{V_{Smin} * D_{max}}{I_1 * f} \tag{6.11}$$

$$flux = \frac{mmf}{reluctance} \tag{6.12}$$

Using eqution (9.10) and (9.11), we can get,

$$Length of Airgap, l_g = \frac{\mu_0 * N_1^2 * A_c}{L_1} = 0.08mm$$

(6.13)

#### **MOSFET Selection**

Calculated Values,

$I_{peak}$ =1.54 A and  $V_{CE}$ =21.22 V

Selected Values,

$I_{peak}$ =3 A and  $V_{CE}$ =60 V

### Diode Selection $D_{70}$

$$I_{peak} = 0.73 \text{ A}$$

$$I_{avq} = 0.20 \text{ A}$$

Reverse Blocking Voltage= 30 V

Selected MOSFET is IRF 510S.

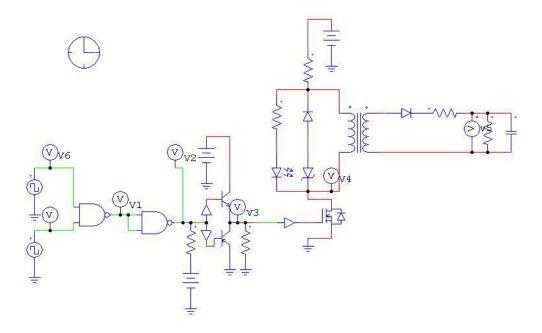

Figure 6.3: Firing Circuit Simulation Model

## 6.2 Simulation of the Firing Circuit

The simulation model of the firing circuit is as shown in the fig 6.3.

We have discussed the generation of the firing pulses of the thyristor so far. The theory has been implemented using the simulation as well as hardware results.

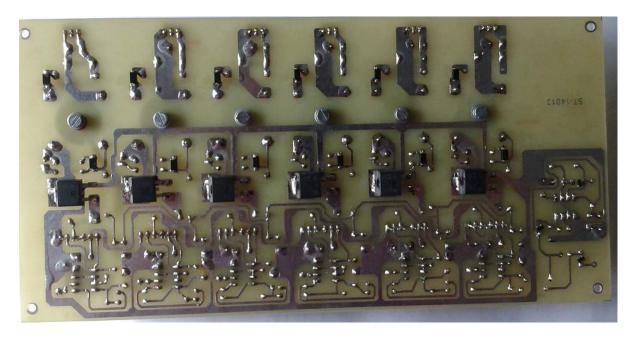

## 6.3 Hardware result of the Firing Circuit Module

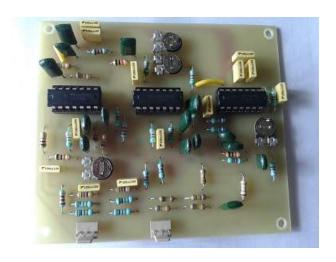

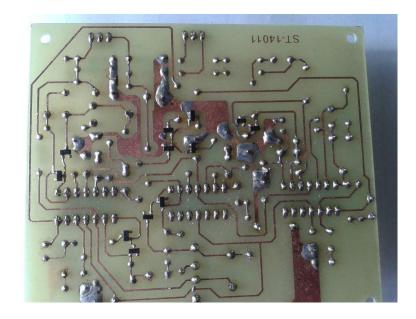

The front view and the back view of the feedback circuit are shown in fig6.6 and fig6.7

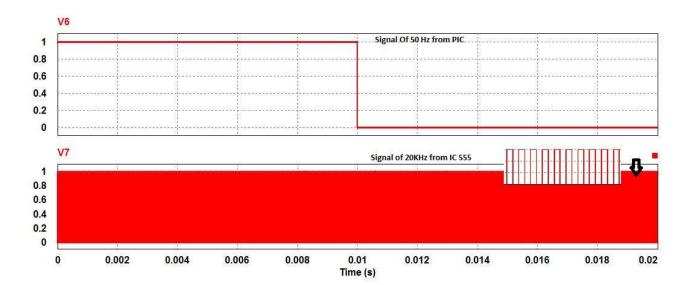

Figure 6.4: Signal from PIC:50Hz and Signal from IC 555:20KHz (Scale: X-axis 0.002 sec per division and Y-axis 0.2 V per division)

Figure 6.5: Firing Signal generation for the thyristor

Figure 6.6: Front view of the Firing Circuit

Figure 6.7: Back view of the Firing Circuit

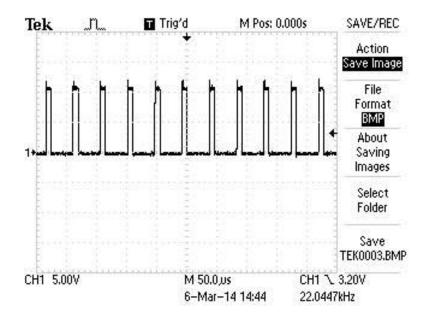

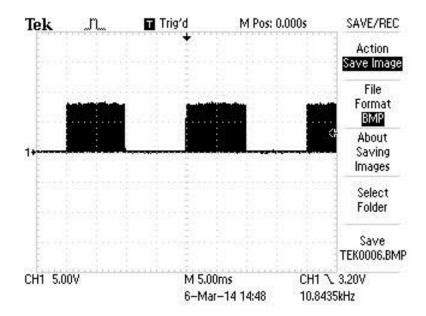

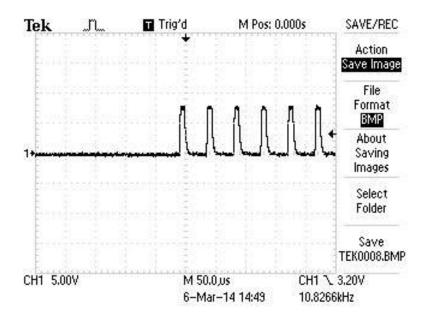

Figure 6.8: A signal genrated by IC 555, Switching Frequency 20 KHz, 20% ON Time and 80% OFF Time (Scale: X-axis  $50\mu$ sec per division and Y-axis 5V per division)

This signal is generated using IC 555 having frequency of 20KHz and duty cycle 0.2. This signal is applied to the U8A NAND gate terminal 1 as shown in fig6.1.

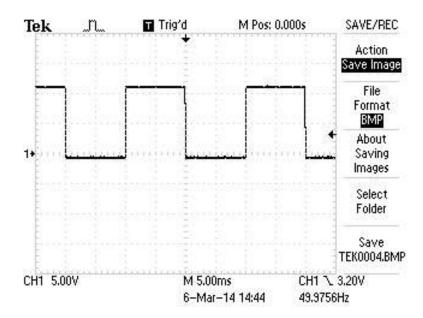

Figure 6.9: Gate Pulse Before MOSFET (Scale: X-axis 5 msec per division and Y-axis 5 V per division)

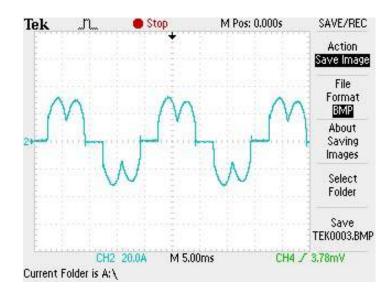

Figure 6.10: Gate pulse without Load (without SCR) (Scale: X-axis 5 msec per division and Y-axis 5 V per division)

This are the gating pulse when the pulse is not applied to the gate of the SCR. We get this kind of pulse as the SCR is not connected and so the capacitor  $C_{48}$  is not getting time to discharge completely. Refer fig6.1.

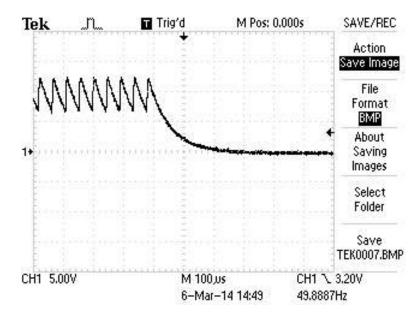

Figure 6.11: Expanded Gate pulse without Load (without SCR)(Scale: X-axis 100  $\mu$ sec per division and Y-axis 5 V per division)

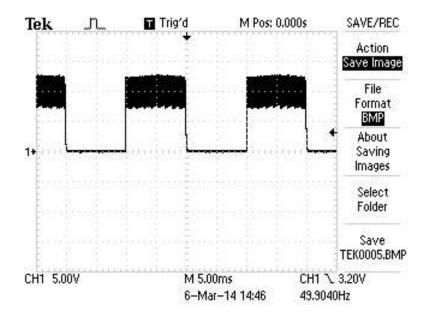

Figure 6.12: Gate pulse with SCR connected (Scale: X-axis 5 msec per division and Y-axis 5 V per division)

This is the gating signal when the SCR is connected.

Figure 6.13: Expanded Gate pulse with SCR connected (Scale: X-axis 5  $\mu$ sec per division and Y-axis 5 V per division)

# Chapter 7

# Desing of Feedback Circuit

## 7.1 Design of Output Voltage Feedback Circuit

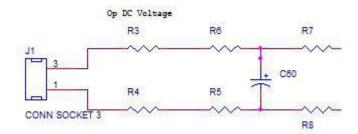

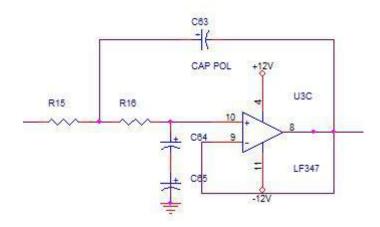

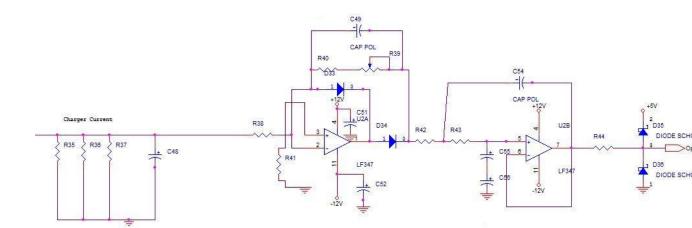

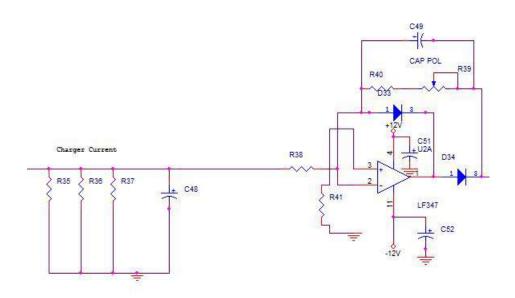

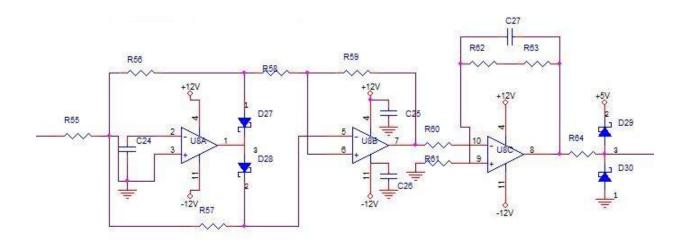

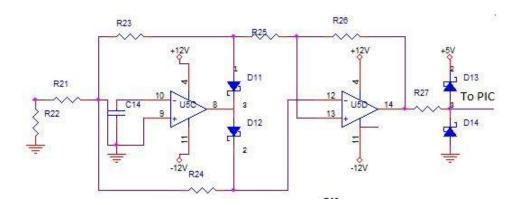

The fig7.4 shows the the output voltage feedback circuit. The design of each part of the circuit is explained below:

### Signal Condtioning in Charger PSFB card

This stage provides a resistive network to the DC voltage feedback sensing OPAMP U3 of charger feedback circuit. After this stage the voltage will be step down to certain mV and it will be applied to OPAMP1 U3A.

Here the U3 is the OPAMP IC LF347.

Figure 7.1: Output Voltage Feedback Circuit Stage1

Figure 7.2: Output Voltage Feedback Circuit Stage2

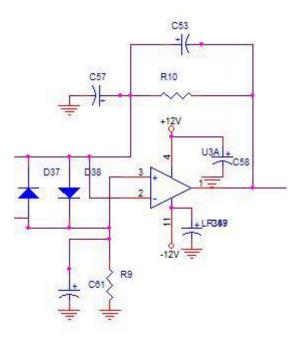

## Signal Condtioning in First stage of output voltage feedback circuit

In this stage the gain of the OPAMP U3A will be negative and so the output voltage after this stage will be negative.

Gain provided by first stage = -(

$$R_{10}/(R_4+R_5+R_8 \text{ of PSFB card})$$

)