#### "DESIGN AND IMPLEMENTATION OF COMPACT AND ISOLATED LOW VOLTAGE HIGH CURRENT DC POWER SUPPLY USING SYNCHRONOUS RECTIFIER"

#### Major Project Report

Submitted in partial fulfillment of the requirements for Degree of

> Master of Technology In Electrical Engineering

(Power Electronics, Machines & Drives)

By

Grishma K. Shah 12MEEP24

DEPARTMENT OF ELECTRICAL ENGINEERING

INSTITUTE OF TECHNOLOGY

NIRMA UNIVERSITY

AHMEDABAD-382481

MAY 2014

#### Certificate

This is to certify that the Major Project Report entitled "Design and Implementation of Compact and Isolated Low-Voltage High-Current DC Power Supply using Synchronous Rectifier" submitted by Ms.Shah Grishma K.(12MEEP24) towards the partial fulfillment of the requirements for the award of degree in Master of Technology (Electrical Engineering) in the field of Power Electronics, Machines & Drives of Nirma University is the record of work carried out by her under our supervision and guidance. The work submitted has in our opinion reached a level required for being accepted for examination. The results embodied in this major project work to the best of our knowledge have not been submitted to any other University or Institution for award of any degree or diploma.

Date:

#### Institute-Guide

Prof. Dr. P. N. Tekwani

Head of Department,

Department of Electrical Engineering,

LTD. Nirma University,

Ahmedabad.

#### **Industry-Guide**

Mr. Vinod Patel AGM, (R& D) Department AMTECH ELECTRONICS (I) E-6, Electronics Zone, G.I.D.C. Gandhinagar.

Director

Dr. K. Kotecha

Institute of

Technology, Nirma

University,

Ahmedabad.

Dedicated to My Family...

### Undertaking for Originality of the Work

I Grishma Ketankumar Shah, Roll No. 12MEEP24, give undertaking that the Major Project entitled "Design and Implementation of Compact and Isolated Low-Voltage High-Current DC Power Supply using Synchronous Rectifier" submitted by me, towards the partial fulfillment of the requirements for the degree of Master of Technology in Power Electronics Machines & Drives, Electrical Engineering, under Institute of Technology of Nirma University, Ahmedabad, is the original work carried out by me and I give assurance that no attempt of plagiarism has been made. I understand that in the event of any similarity found subsequently with any published work or any dissertation work elsewhere; it will result in severe disciplinary action.

| Signature of Student         |  |  |

|------------------------------|--|--|

| Date:                        |  |  |

| Place:                       |  |  |

|                              |  |  |

|                              |  |  |

|                              |  |  |

|                              |  |  |

|                              |  |  |

|                              |  |  |

|                              |  |  |

|                              |  |  |

| Endorsed by:                 |  |  |

|                              |  |  |

| (Signature of Project Guide) |  |  |

|                              |  |  |

Prof. Dr. P. N. Tekwani

Head of Department, Department of Electrical Engineering, Nirma University, Ahmedabad. Mr. Vinod patel

AGM, (R& D) Department

AMTECH ELECTRONICS (I) LTD.

E-6, Electronics Zone, G.I.D.C.

Gandhinagar.

#### Acknowledgements

First of all, I would like to thank AMTECH Electronics(I) Ltd., Gandhinagar, for giving me an opportunity to perform the project under its premises and give me the industrial exposure. I express my sincere gratitude to Mr.Vinod Patel, AGM(R&D), AMTECH Electronics (I) Ltd., Gandhinagar, for his valuable guidance and co-operation. His perfectionism has made me improve many details of my work. He challenged me to find technical solutions to realistic problems. He always helped me and gives sincere advice and innovative ideas throughout the period we have worked together.

My sincere appreciation must be extended to my institute guide Dr.P.N.Tekwani, Head of Department, Department of Electrical Engineering, Nirma University for his valuable suggestions and inspiration and for allowing me to do my project work at AMTECH Electronics.

I would like to thank Mr. Bharat Pandya, Assistant Manager (R&D), for his support and advice. His extensive knowledge and helpful attitude gains my sincere admiration. I would also like to thank to Mr.Vijyendra Kharbikar, Mr.Parth Patel, Mr.Bhavin Bhakhtaria and Mr.Dinesh Bharada for their continual efforts and support towards my project work.

Finally I gratefully appreciate the patience, support and motivation of all my family members and friends to achieve my goal.

-Grishma K.Shah

**12MEEP24**

#### Abstract

With advances in modern power electronics, Low-Voltage High-Current DC power supply is used extensively in industrial applications like arc furnace, fusion technology, arc welding etc. In conventional dissipative techniques, it has many disadvantages like lower efficiency, higher weight and size. The main aim of this project is to meet industrial needs like isolation between source and load, minimize the switching loss, high conversion efficiency, lower distortion in output voltage, current and also reduces the power supply package size using high frequency converters. Different Isolated Converter topologies such as Forward Converter, Flyback Converter, Push-Pull Converter, Half-Bridge Converter and Full-Bridge Converter, among all these topologies Phase Shifted Full-Bridge topology has been selected in order to achieve the High Power applications. In this topology PWM techniques are used for power switches, so that they are going to switch at high frequencies which results in the reduction of the size of transformer, weight and cost of the overall power supply. At a lower switching frequencies and without use of Quasi Resonant Converter, the switching losses (turn on and turn off losses) are significant part of the power losses, which reduces the efficiency and increase the size of overall Power Supply. An attractive alternative method to reduce the switching losses and improve the efficiency is that to replace the hard switching by soft switching in which zero voltage/zero current switching is used. In Low-Voltage applications, conduction loss of the diode bridge rectifier contributes significant power losses in the Power Supply compared to the synchronous rectifier. Feed forward technique has been adapted to minimize the output ripple from the DC link. The simulation of whole system was done in PSIM software and along with DLL block. After examining the simulation results the whole scheme implemented in hardware. The simulation of 900 W and 15 kW DC Power Supply was carried out and hardware of 900 W Prototype DC Power Supply was implemented. The 15 kW High Frequency Transformer is designed and prepared.

### Abbreviation

| ADC    | Analog to Digital Converter                       |

|--------|---------------------------------------------------|

| DSP    | Digital Signal Processor                          |

| EMI    | Electromagnatic Interference                      |

| IGBT   | Insulated Gate Bipolar Transistor                 |

| MOSFET | Metal Oxide Semiconductor Field Effect Transistor |

| PWM    | Pulse Width Modulation                            |

| PI     | Proportional Integral                             |

| QRC    | Quasi Resonant Converter                          |

| SMPS   | Switched Mode Power Supply                        |

| VSI    |                                                   |

| ZVS    | Zero Voltage Switching                            |

### NOMENCLATURE

| parea of primary windin       | g            |

|-------------------------------|--------------|

| $s_s$                         | g            |

| tarea of tersary windin       | g            |

| $A_c$                         | e            |

| $A_w$                         | V            |

| $A_p$ Area of Produc          | :t           |

| $B_m$                         | у            |

| $C_{oss}$                     | S            |

| $C_R$                         | e            |

| $C_{XFMR}$                    | e            |

| Duty cycl                     | e            |

| $\overline{V}_s$              | У            |

| $\overline{V}_{RES}$          | у            |

| Input Curren                  | ıt           |

| $\mathcal{O}_o$ Output Curren | ıt           |

| Transformer Primary Curren    | ıt           |

| U                             | у            |

| $K_w$                         | r            |

| $\mathcal{L}_R$               | r            |

| $N_p$ Number of primary turn  | $\mathbf{S}$ |

| $N_s$                         | $\mathbf{S}$ |

| $P_o$ Output Power            | r            |

| $P_{IN}$ Input Power          | r            |

| $P_{Lcu}$                     | s            |

| $P_{Lcore}$                   | $\mathbf{s}$ |

| $V_d$                         | р            |

| $V_{IN}$                      | e            |

| Voltag                        | e            |

| Efficienc                     | У            |

## Contents

| $\mathbf{C}$ | ertifi                                 | cate             | ii                                |

|--------------|----------------------------------------|------------------|-----------------------------------|

| U            | nder                                   | taking           | iv                                |

| A            | ckno                                   | wledgement       | v                                 |

| $\mathbf{A}$ | bstra                                  | net              | vi                                |

| A            | bbre                                   | viation          | vii                               |

| N            | omei                                   | aclature         | viii                              |

| Li           | st of                                  | Tables           | xii                               |

| L            | ist o                                  | f Figures        | xiii                              |

| 1            | Inti<br>1.1<br>1.2<br>1.3<br>1.4       | General Overview | 1<br>1<br>2<br>2<br>3             |

| 2            | 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6 | Introduction     | 66<br>77<br>88<br>88<br>100<br>10 |

| 3            | <b>Qua</b> 3.1                         | Introduction     | 15<br>15<br>15                    |

CONTENTS

|   | 3.3 | Resona | ant Circuit Design with 18kHz Switching Frequency of 15 kW  |

|---|-----|--------|-------------------------------------------------------------|

|   |     | Power  | Supply                                                      |

|   |     | 3.3.1  | Resonant Capacitance $C_R$                                  |

|   |     | 3.3.2  | Resonant Inductor $L_R$                                     |

|   |     | 3.3.3  | Energy and Dead time conditions for achieving ZVS:          |

|   |     | 3.3.4  | Minimum(critical) Primary current                           |

|   | 3.4 | Resona | ant Circuit Design with 18 kHz Switching Frequency of 900 W |

|   |     | Protot | ype Power Supply                                            |

|   |     | 3.4.1  | Resonant Capacitance $C_R$                                  |

|   |     | 3.4.2  | Resonant Inductor $L_R$                                     |

|   |     | 3.4.3  | Energy and Dead time conditions for achieving ZVS:          |

|   |     | 3.4.4  | Minimum(critical) Primary current                           |

| 4 | Des | ign of | 18 kHz High Frequency Transformer                           |

|   | 4.1 | _      | uction                                                      |

|   |     | 4.1.1  | The characteristics of High Frequency Transformer windings: |

|   |     | 4.1.2  | Properties of Ferrite Core                                  |

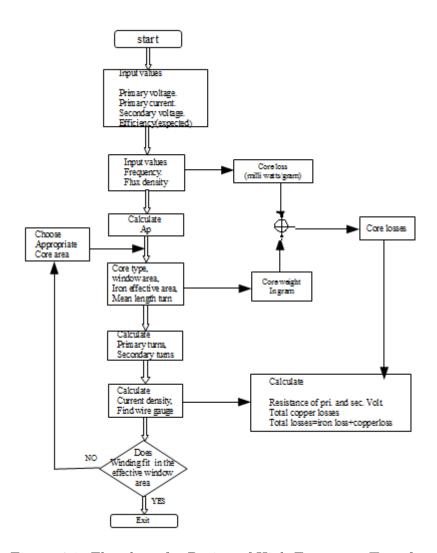

|   | 4.2 | Design | and Flowchart for High Frequency Transformer                |

|   | 4.3 |        | and Development of 900 VA,18 kHz Transformer for Prototype  |

|   |     |        | Supply                                                      |

|   |     | 4.3.1  | Design Specifications:                                      |

|   |     | 4.3.2  | Selection of Magnetic Core:                                 |

|   |     | 4.3.3  | Dimension of EE 65/32/27 Ferrite Core:                      |

|   |     | 4.3.4  | Calculation of Number of turns:                             |

|   |     | 4.3.5  | Development of Transformer                                  |

|   |     | 4.3.6  | Theoretical Calculations:                                   |

|   |     | 4.3.7  | Practical Results:                                          |

|   | 4.4 | Design | of L-C Filter                                               |

|   |     | 4.4.1  | Calculate the value of Inductor                             |

|   |     | 4.4.2  | Calculate the value of Capacitor                            |

|   | 4.5 | Develo | opment of 20 $\mu H$ Inductor                               |

|   |     | 4.5.1  | Selection of Magnetic Core                                  |

|   |     | 4.5.2  | Calculation of Numbers of Turns                             |

|   |     | 4.5.3  | Calculate the length of airgap                              |

|   | 4.6 | Design | n of 18 kHz,15 kVA Transformer                              |

|   |     | 4.6.1  | Design Specifications:                                      |

|   |     | 4.6.2  | Selection of Magnetic Core:                                 |

|   |     | 4.6.3  | Calculation of Number of turns:                             |

|   |     | 4.6.4  | Theoretical Calculations:                                   |

|   | 4.7 | Design | of L-C Filter                                               |

|   |     | 4.7.1  | Calculate the value of Inductor                             |

|   |     | 472    | Calculate the value of Capacitor                            |

CONTENTS xi

| <ul> <li>5.1 Introduction</li></ul>                                                                                                                                                                                                                                                                              | 44  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.2.1 Voltage Control method(CV mode control)                                                                                                                                                                                                                                                                    |     |

| 5.2.2 Feed-Forward Control  5.3 Simulation of 500 A and 30 V Power Supply with 18 kHz Switchin Frequency  6 Simulation of 900 W Prototype Power supply with DLL  6.1 Simulation of Close-Loop Control through DLL Block  7 Hardware Results of 900 W in Open-Loop Control  7.1 Theoritical Calculation of Losses |     |

| <ul> <li>5.3 Simulation of 500 A and 30 V Power Supply with 18 kHz Switchin Frequency</li></ul>                                                                                                                                                                                                                  |     |

| Frequency                                                                                                                                                                                                                                                                                                        |     |

| 6 Simulation of 900 W Prototype Power supply with DLL 6.1 Simulation of Close-Loop Control through DLL Block                                                                                                                                                                                                     | _   |

| 6.1 Simulation of Close-Loop Control through DLL Block                                                                                                                                                                                                                                                           | 40  |

| 7 Hardware Results of 900 W in Open-Loop Control 7.1 Theoritical Calculation of Losses                                                                                                                                                                                                                           | 57  |

| 7.1 Theoritical Calculation of Losses                                                                                                                                                                                                                                                                            | 5'  |

| 7.1 Theoritical Calculation of Losses                                                                                                                                                                                                                                                                            | 65  |

|                                                                                                                                                                                                                                                                                                                  |     |

| 7.1.1 Total Losses of IGBT                                                                                                                                                                                                                                                                                       |     |

| 7.1.2 Losses Of Mosfet                                                                                                                                                                                                                                                                                           |     |

| 7.1.3 Losses Of Schottkey Diode                                                                                                                                                                                                                                                                                  |     |

| 7.1.3 Losses of Schottkey Blode                                                                                                                                                                                                                                                                                  |     |

|                                                                                                                                                                                                                                                                                                                  |     |

|                                                                                                                                                                                                                                                                                                                  |     |

|                                                                                                                                                                                                                                                                                                                  |     |

| 7.4.1 Design of RC Snubber                                                                                                                                                                                                                                                                                       | 70  |

| 8 Hardware Results of 900 W in Closed Loop Control                                                                                                                                                                                                                                                               | 79  |

| 8.1 Closed Loop Conrol                                                                                                                                                                                                                                                                                           | 79  |

| 8.1.1 Closed Loop Control Algorithm through DSP TMS320F2811                                                                                                                                                                                                                                                      | 80  |

| 8.2 Hardware Results in Closed Loop Conrol                                                                                                                                                                                                                                                                       | 80  |

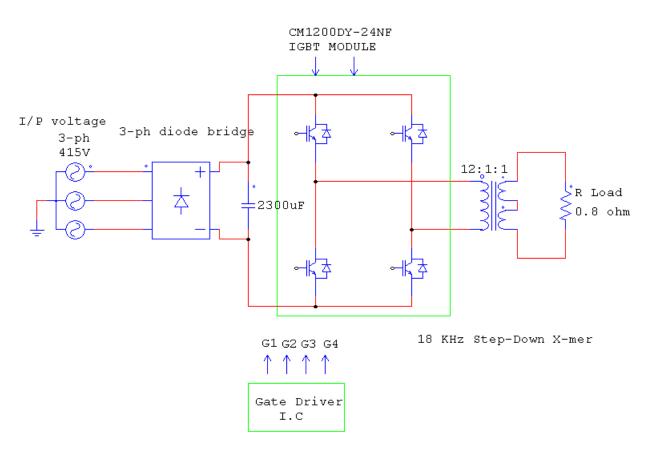

| 9 Hardware Results in Isolated 15 kW Power Supply                                                                                                                                                                                                                                                                | 92  |

| 9.1 Practical Results                                                                                                                                                                                                                                                                                            | 95  |

| 10 Conclusion and Future Scope                                                                                                                                                                                                                                                                                   | 90  |

| 10.1 Conclusion                                                                                                                                                                                                                                                                                                  | 90  |

| 10.2 Future Work                                                                                                                                                                                                                                                                                                 |     |

| References 97                                                                                                                                                                                                                                                                                                    | . 0 |

## List of Tables

| I   | Dimension of EE 65/32/27 Ferrite Core             | 28 |

|-----|---------------------------------------------------|----|

| II  | Dimension of EE 65/32/27 Ferrite Core             | 28 |

| III | Dimension of UU93/76/30 Ferrite Core              | 38 |

| IV  | Dimension of UU93/76/30 Ferrite Core              | 38 |

| Ι   | Conduction Losses of Schottky Diode(DSS2x101-02A) | 66 |

| II  | Conduction Losses of MOSFET (IRFP4668PbF)         | 67 |

| III | $R=1\Omega$ (Load) with MOSFET                    | 71 |

## List of Figures

| 2.1  | Flyback Converter Circuit                                                      | 7  |

|------|--------------------------------------------------------------------------------|----|

| 2.2  | Forward Converter Circuit                                                      | 8  |

| 2.3  | Push-Pull Converter Circuit                                                    | 9  |

| 2.4  | Half-Bridge Converter Circuit                                                  | 9  |

| 2.5  | Full-Bridge Converter Circuit                                                  | 10 |

| 2.6  | Comparison between Synchronous Rectifier and Diode Rectifier Con-              |    |

|      | duction loss                                                                   | 11 |

| 2.7  | Full-Wave Synchronous Rectifier                                                | 13 |

| 2.8  | Forward Synchronous Rectifier                                                  | 13 |

| 2.9  | Current-Doubler Synchronous Rectifier                                          | 14 |

| 2.10 |                                                                                | 14 |

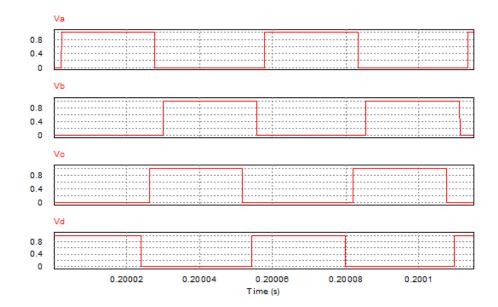

| 3.1  | Gate Pulses of Phase Shifted PWM control waveform                              | 17 |

| 4.1  | Flowchart for Design of High Frequency Transformer                             | 25 |

| 4.2  | Dimension of EE 65/32/27 Ferrite Core                                          | 28 |

| 4.3  | ,                                                                              | 31 |

| 4.4  |                                                                                | 34 |

| 4.5  | Overall view of $20\mu H$ Inductor                                             | 35 |

| 4.6  |                                                                                | 38 |

| 4.7  |                                                                                | 41 |

| 4.8  | Overall View of 18 kHz,15 kVA Transformer with UU 93/76/30 Ferrite             |    |

|      | Core                                                                           | 42 |

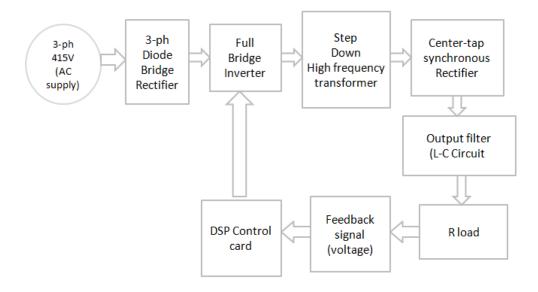

| 5.1  |                                                                                | 45 |

| 5.2  |                                                                                | 46 |

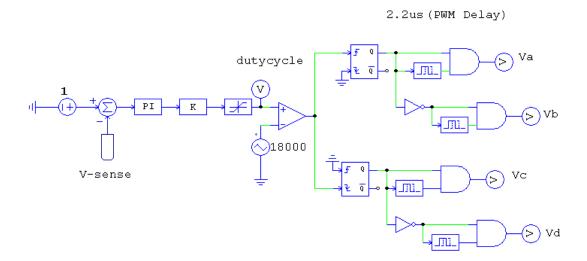

| 5.3  | Gate pulse generation circuit                                                  | 47 |

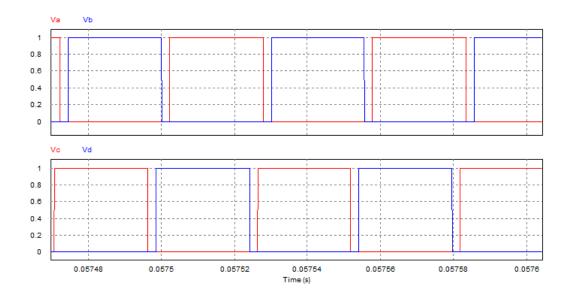

| 5.4  | Gate pulses For IGBTs at full load and minimum phase shifting $V_{duty}$ =0.44 | 48 |

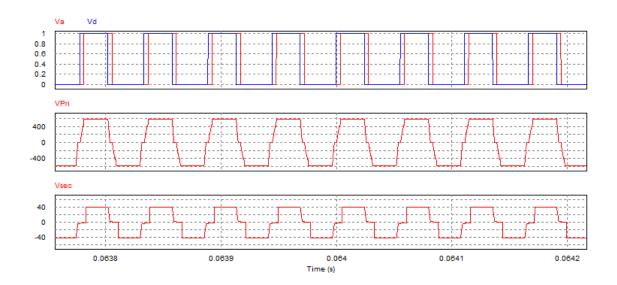

| 5.5  | Phase shift in duty cycle, Transformer Primary Voltage, Transformer            |    |

|      | Secondary Voltage                                                              | 48 |

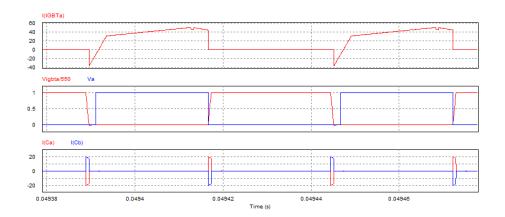

| 5.6  | Current flowing through IGBTa, Zero Voltage Switching across IGBTa,            |    |

|      | Current flowing through capacitor a & b                                        | 49 |

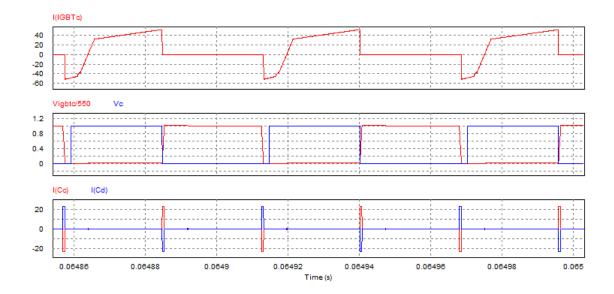

| 5.7  | Current flowing through IGBTc, Zero Voltage Switching across IGBTc,            |    |

|      | Current flowing through capacitor c & d                                        | 49 |

LIST OF FIGURES xiv

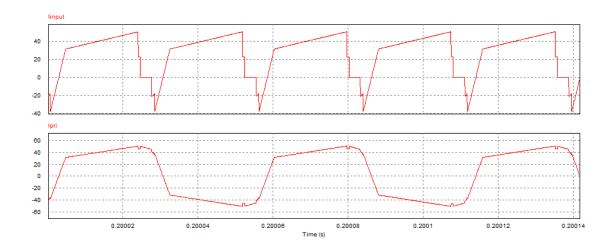

| 5.8  | Input current, Transformer primary current                             | 50      |

|------|------------------------------------------------------------------------|---------|

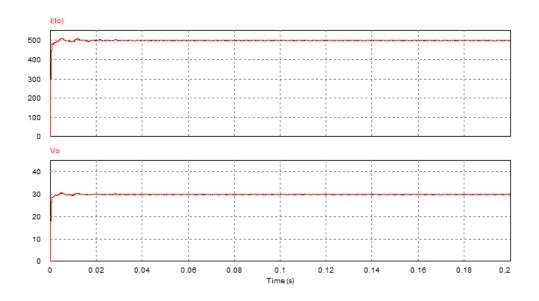

| 5.9  | Output Current and Output Voltage at full load and max. duty cycle     | 50      |

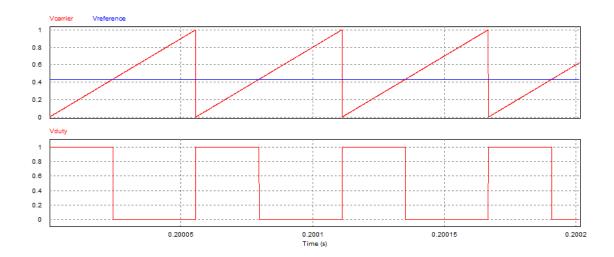

| 5.10 | Reference signal compared with error signal, Compared pwm pulse        | 51      |

|      | PWM Delay of 2.2 us between IGBT a & b, IGBT c & d                     | 51      |

|      | input Power factor, current flowing through line choke, Voltage across |         |

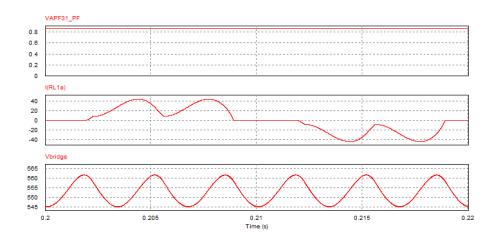

|      | diode bridge                                                           | 52      |

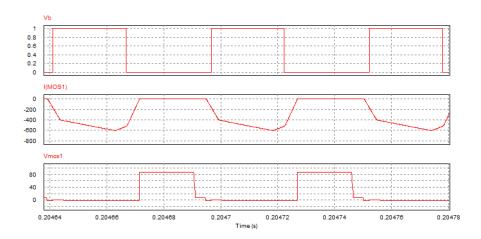

| 5.13 | gate pulse for MOSFET1, current flowing through MOSFET1, Voltage       | _       |

| 0.10 | across MOSFET1                                                         | 52      |

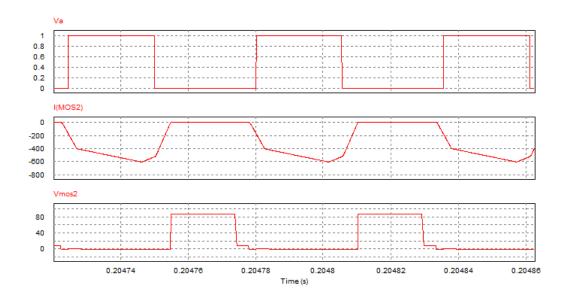

| 5 14 | gate pulse for MOSFET2, current flowing through MOSFET2, Voltage       | _       |

| 0.11 | across MOSFET2                                                         | 53      |

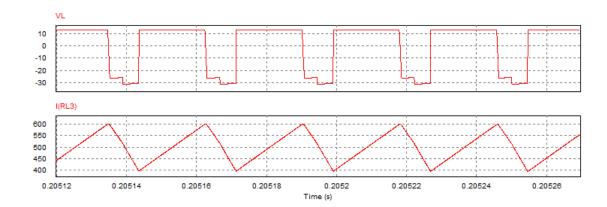

| 5 15 | Inductor voltage and Inductor current                                  | 53      |

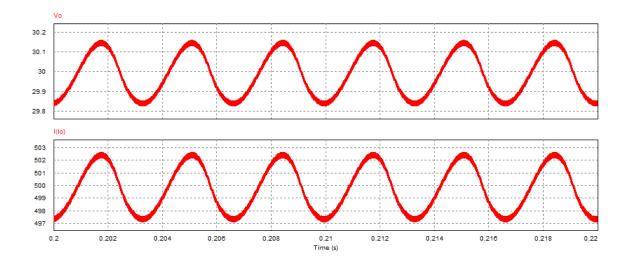

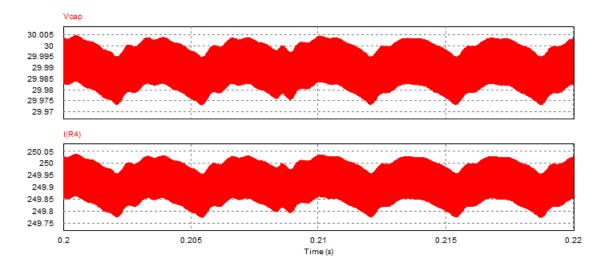

|      | Output voltage and Output current with ripple                          | 54      |

|      | Feed-Forward method                                                    | 54      |

|      | Output voltage and output current with 40mv ripple at 100% load        | 55      |

|      | Output voltage and output current with at 75% load                     | 55      |

|      | · · · · · · · · · · · · · · · · · · ·                                  | 56      |

| 5.20 | Output voltage and output current with at $50\%$ load                  | 50      |

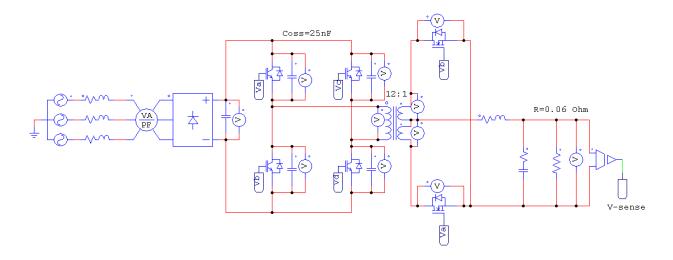

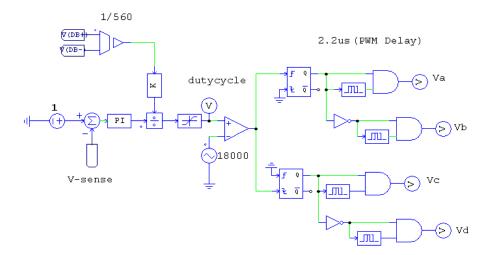

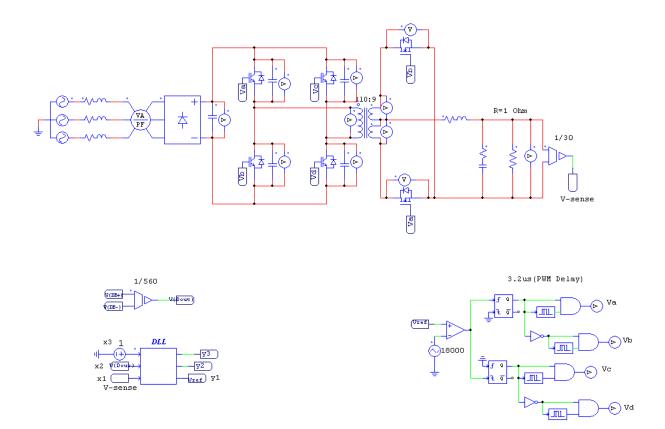

| 6.1  | Simulation of close loop circuit with DLL block                        | 58      |

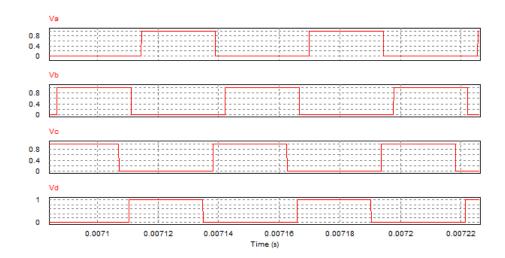

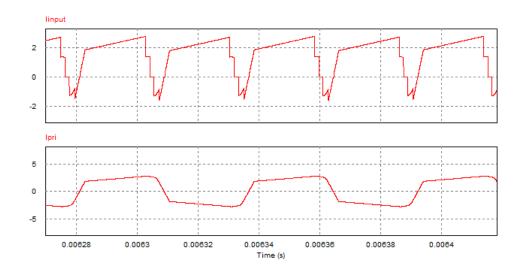

| 6.2  | Gate Pulse Generation Circuit at Vref=1                                | 59      |

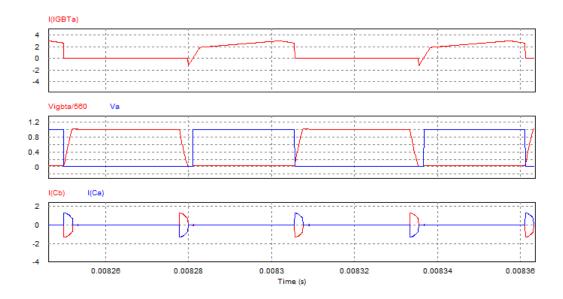

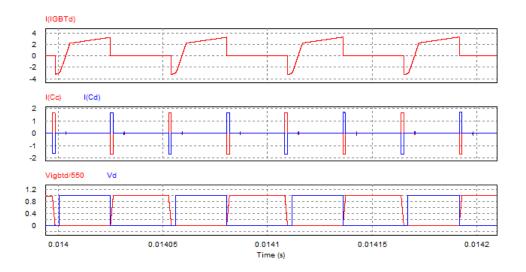

| 6.3  | Current flowing through IGBT a,Zero voltage switching across IGBT      |         |

| 0.0  | a & gate pulse for Switch a, Current flowing through capacitor a & b   | 59      |

| 6.4  | Input current, primary current                                         | 60      |

| 6.5  | Current flowing through IGBTd, Zero voltage switching across IGBTd     |         |

| 0.0  | & gate pulse for Switch d, Current flowing through c & d               | 60      |

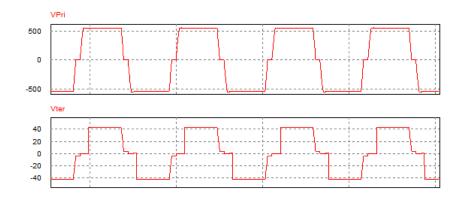

| 6.6  | Transformer Primary and tersary Voltage                                | 61      |

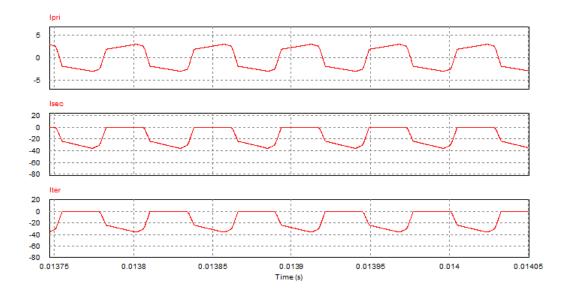

| 6.7  | Primary current, Secondary current and tersary current                 | 61      |

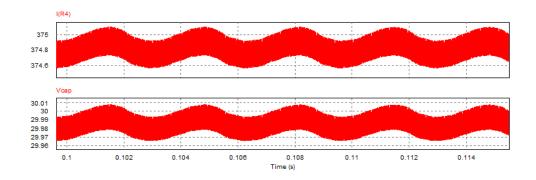

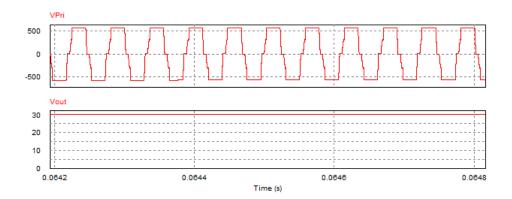

| 6.8  | Transformer primary voltage and output voltage at Vref=1, Vduty=0.43   | O1      |

| 0.0  | and Vout=30V                                                           | 62      |

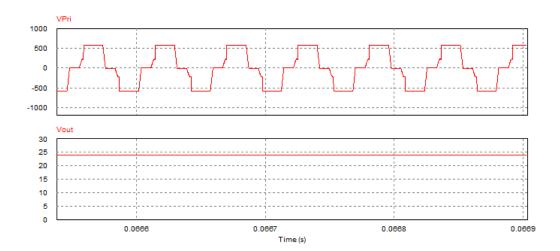

| 6.9  | Transformer Primary Voltage and Output Voltage at Vref=0.8, Vduty=0.3  |         |

| 0.5  | and Vout=24V                                                           | 4<br>62 |

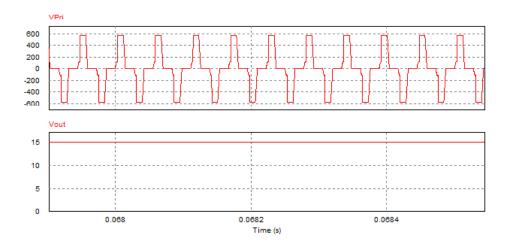

| 6 10 | Transformer Primary Voltage and Output Voltage at Vref=0.5, Vduty=0.2  |         |

| 0.10 | and Vout=15V                                                           | 63      |

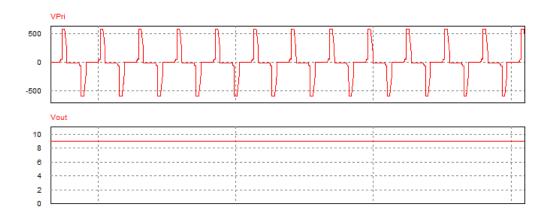

| 6 11 | Transformer primary voltage and output voltage at Vref=0.3, Vduty=0.10 | 00      |

| 0.11 | and Vout=9V                                                            | 63      |

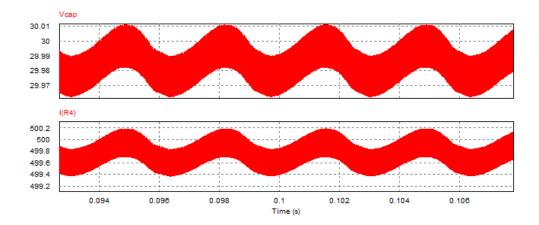

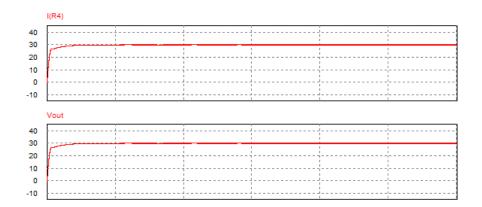

| 6 10 | Output Voltage and Current at full load                                |         |

|      |                                                                        | 64      |

| 0.13 | Output voltage and Current with 40 mv (Peak-Peak) ripple               | 64      |

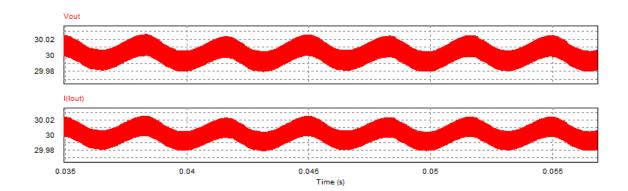

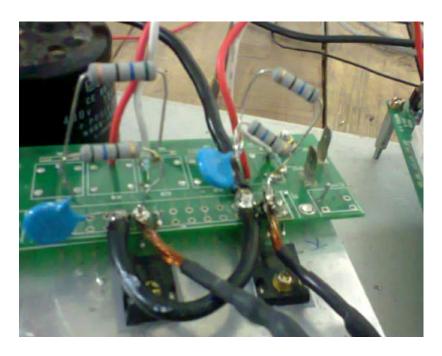

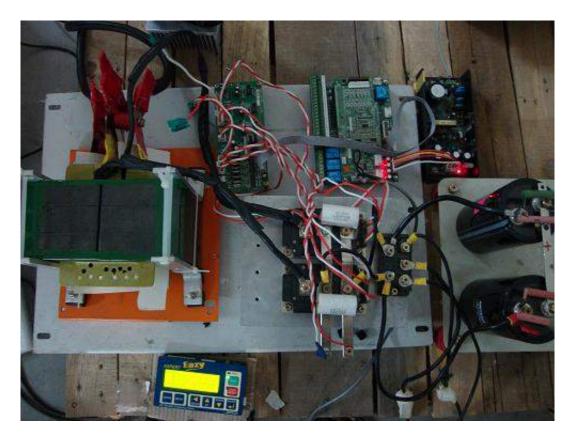

| 7.1  | Circuit of Hardware Setup for 900W Isolated DC Power Supply            | 67      |

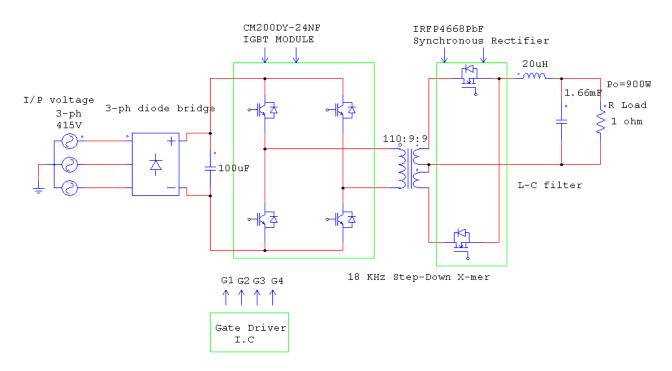

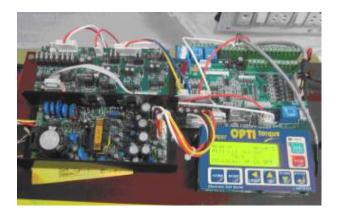

| 7.2  | Hardware Setup                                                         | 68      |

| 7.3  | Overall View of RC snubber                                             | 71      |

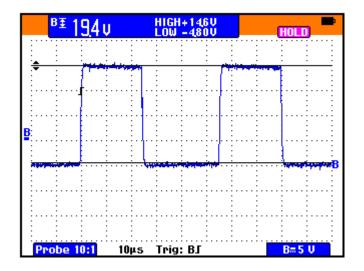

| 7.4  | Gate pulse with the amplitude of 19.4 V                                | 72      |

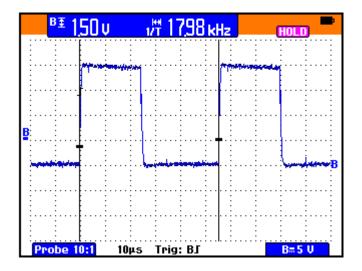

| 7.5  | Gate pulse of 18KHz Switching frequency                                | 72      |

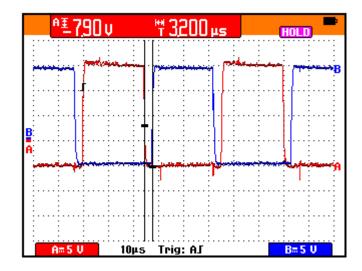

| 7.6  | Deadband between s/w a&b and s/w c&d $(3.2\mu s)$                      | 73      |

|      | = 1                                                                    |         |

LIST OF FIGURES xv

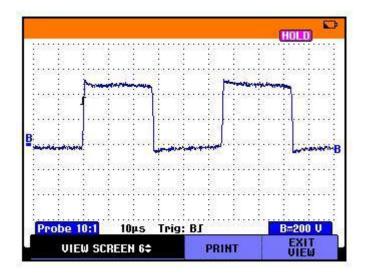

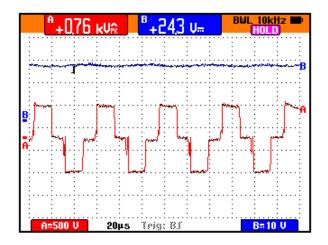

| 7.7  | Voltage across IGBT a $V_{IGBTa}$ =570 V                                            | 73 |

|------|-------------------------------------------------------------------------------------|----|

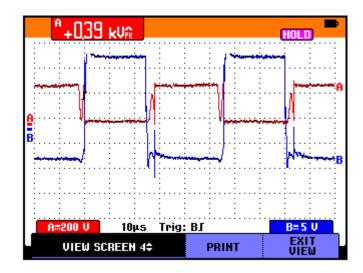

| 7.8  | Gate pulses of s/w a and d at 40% phase shifting                                    | 74 |

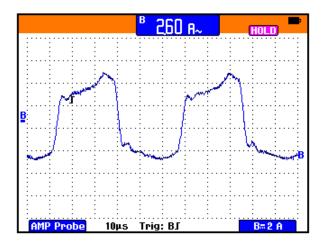

| 7.9  | Transformer primary current                                                         | 74 |

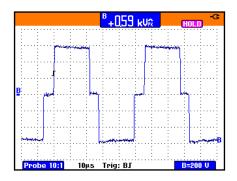

| 7.10 | Transformer primary voltage at 40% phase shifting and $V_{pri}=\pm 570\mathrm{V}$ . | 75 |

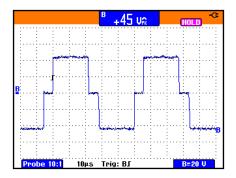

| 7.11 | Transformer secondary voltage at 40% phase shifting and $V_{sec}=\pm 45\mathrm{V}$  | 75 |

| 7.12 | Output voltage across Load (Vout=30.8 V) at $R=1\Omega$                             | 76 |

| 7.13 | Voltage across MOS 1 $V_{MOS1}$ =80V(Peak)                                          | 76 |

|      | Gate pulses of s/w a and Voltage across IGBT a                                      | 77 |

| 7.15 | Transformer tersary voltage and Gate pulse of MOS 2                                 | 77 |

|      | Gate pulses of s/w b and Voltage across IGBT b at $R=2\Omega$                       | 78 |

|      | Output voltage across Load (Vout=30 V) at R=2 $\Omega$                              | 78 |

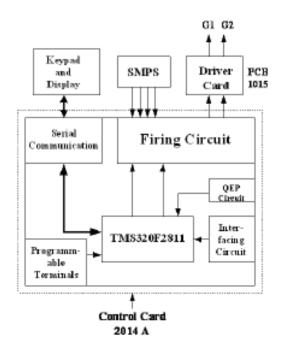

| 8.1  | Block diagram of close-loop control through DSP                                     | 80 |

| 8.2  | Close-loop control setup with control card PCA 2014A                                | 81 |

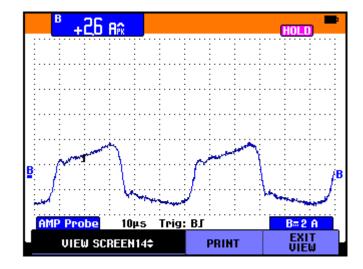

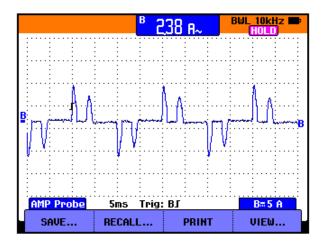

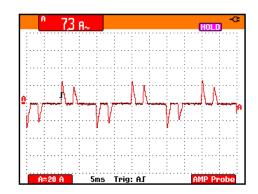

| 8.3  | Input current Iin=2.38 A(rms)                                                       | 83 |

| 8.4  | Transformer primary current=2.60A(rms)                                              | 83 |

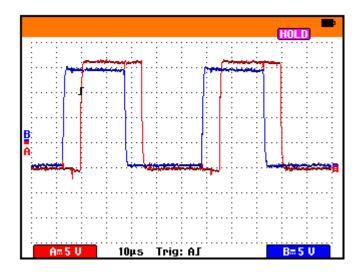

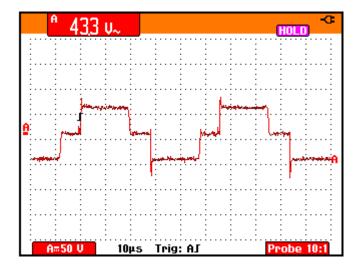

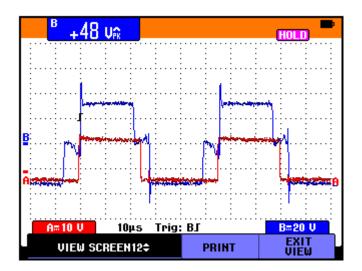

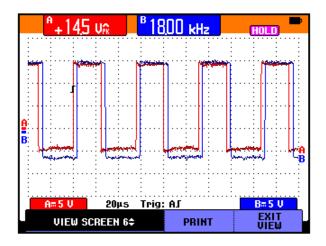

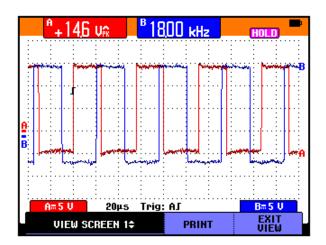

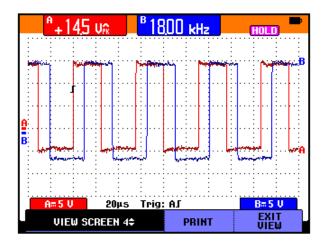

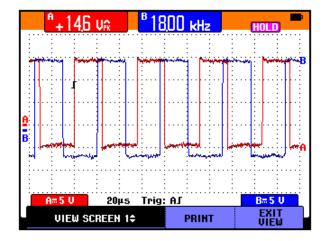

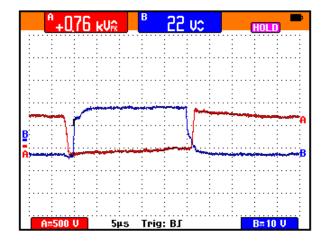

| 8.5  | Gate pulses of s/w a & d $V_{duty} = 0.42 \dots \dots \dots \dots$                  | 84 |

| 8.6  | Gate pulses of s/w a & c $V_{duty} = 0.42 \dots \dots \dots \dots$                  | 84 |

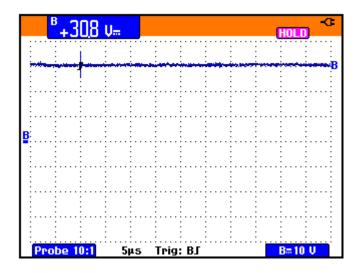

| 8.7  | $V_o=30$ V(DC) settled at $V_{ref}=1$ & $V_{duty}=0.42$                             | 85 |

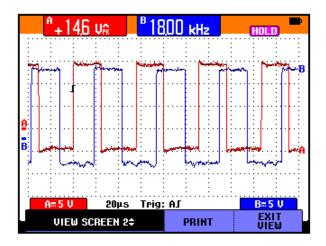

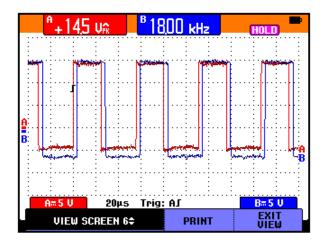

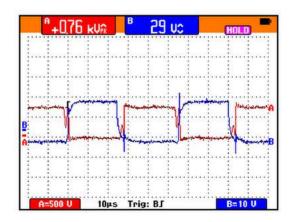

| 8.8  | Gate pulses of s/w a & d $V_{duty} = 0.34$                                          | 85 |

| 8.9  | Gate pulses of s/w a & c $V_{duty} = 0.34$                                          | 86 |

| 8.10 | $V_o = 24 \text{V(DC)}$ settled at $V_{ref} = 0.8 \& V_{duty} = 0.34 \dots$         | 86 |

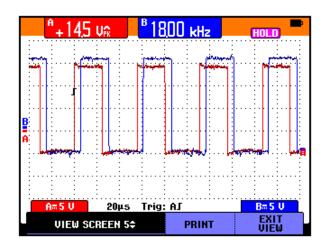

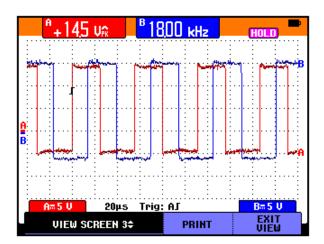

| 8.11 | Gate pulses of s/w a & d $V_{duty} = 0.22 \dots \dots \dots \dots$                  | 87 |

| 8.12 | Gate pulses of s/w a & c $V_{duty} = 0.22 \dots \dots \dots \dots$                  | 87 |

| 8.13 | $V_o=15V(DC)$ settled at $V_{ref}=0.5 \& V_{duty}=0.22 \ldots \ldots$               | 88 |

| 8.14 | Gate pulses of s/w a & d $V_{duty} = 0.10 \dots \dots \dots \dots$                  | 88 |

| 8.15 | Gate pulses of s/w a & c $V_{duty} = 0.10 \dots \dots \dots \dots$                  | 89 |

| 8.16 | $V_o=9V(DC)$ settled at $V_{ref}=0.3 \& V_{duty}=0.10 \ldots$                       | 89 |

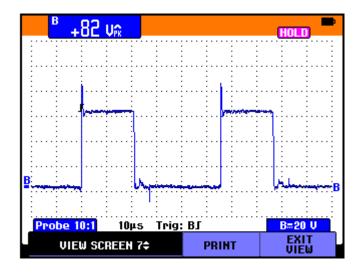

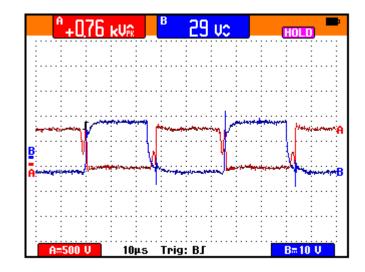

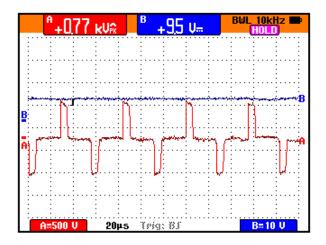

| 8.17 | Gate pulses of s/w a and Voltage across IGBT a                                      | 90 |

| 8.18 | Gate pulses of s/w c and Voltage across IGBT c                                      | 90 |

| 8.19 | Gate pulses of s/w c and Voltage across IGBT c at $V_{ref} = 0.7$                   | 91 |

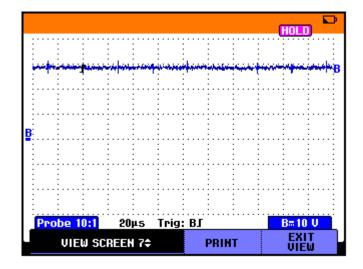

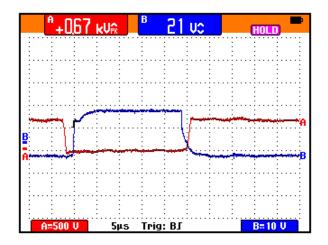

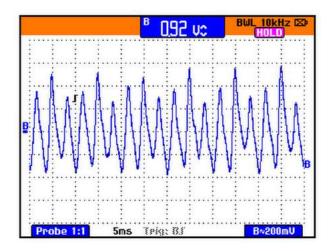

| 8.20 | Output voltage with ripple                                                          | 91 |

| 9.1  | Circuit Diagram for Hardware Setup                                                  | 93 |

| 9.2  | Overall view of Hardware setup                                                      | 94 |

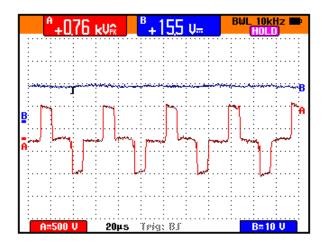

| 9.3  | Input current                                                                       | 94 |

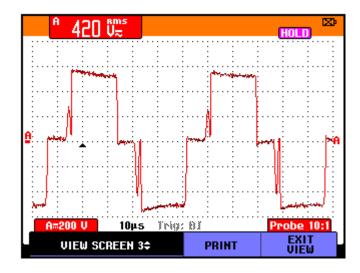

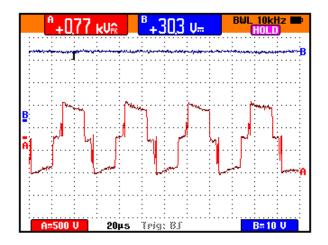

| 9.4  | Transformer Primary Voltage=±590 V                                                  | 95 |

| 9.5  | Transformer Secondary and tersary voltage=±45 V                                     | 95 |

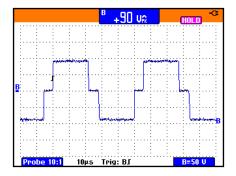

| 9.6  | Output Voltage across Load=±90V                                                     | 95 |

## Chapter 1

### Introduction

#### 1.1 General Overview

DC Power supplies are extensively used in industrial applications. Some critical application cannot tolerate failure of power supply as well variation in supply. The isolated low-voltage and high-current DC power supply is widely used in many applications like arc furnace, fusion technology, welding power supply etc. There are many DC-DC power conversion applications where the voltage source has to be converted to a low output voltage, high efficiency, high power density, high reliability and low EMI. These are some of the most desirable features for these converters. In conventional Full-Bridge inverter, the transformer voltage is asymmetrical, so transformer core gets saturated and due to the high switching frequency the circuit parasitic have negative effects on the converter performance, so switching losses increases in high power applications. This creates the need of snubbers that increase the overall losses and bringing down the efficiency. If one is going for higher voltage rating, then its conduction losses increases and cost also increases. So to eliminate this problem, Phase Shifted full bridge inverter is selected. In this topology, When QA & QC both are ON then transformer voltage is zero so the core winding is reset and there is no do saturation problem, at that time energy is freewheeling. There is no energy transfer from primary to secondary. As compared to Resonant Converter, Quasi-Resonant Converters are able to control output voltage in wide range and it is comparatively easy to achieve the control of duty cycle. It is advantageously to use the parasitic circuit elements to achieve the zero voltage switching or zero current switching so there is no need of extra Resonant components. In the Quasi-Resonant Converters, a high-frequency resonant tank circuit is connected across the switch which is employed to shape the switch current and voltage so that high-current and high-voltage is never present simultaneously. As a result, stresses and switching losses in the devices are greatly reduced. Depending on how the high-frequency resonant circuit is connected to the switch, the Quasi -Resonant Converters can be either ZCS-QRCs or ZVS-QRCs, accordingly it eliminates either turn-off or turn-on loss [1]. The majority of power loss comes from the rectification on the low-voltage side. So Synchronous rectification by using MOSFETs is recommended in place of Diode rectification [2]. Isolation is required in some of important industrial applications. Switched mode power regulators do not provide the necessary isolation. Hence two stage conversion DC-AC and AC-DC is required. The isolation is provided by inter stage high frequency transformer.

#### 1.2 Scope of the Work

The main aim of this project is to set up hardware model of Low-Voltage High-Current Power Supply with isolation and compact power supply package size. The High Frquency Transformer is designed to achieve the ZVS (Zero Voltage Switching) to eliminate the turn on losses as well as to provide the isolation between source and load. As far we have seen, in Low-Voltage applications, conduction losses of the diode bridge rectifier contribute significant power losses in the Power Supply compared to the synchronous rectifier. So the synchronous rectifier is used in place of diode bridge recifier to achieve the high effeciency. The 900 W Prototype DC Power Supply is fabricated and tested.

The work is divided in to four stages. In the first stage: Selection of the topology for isolated DC-DC converter and designing of converter was done. In the second stage, simulation was done using PSIM software and various control schemes with analog as well as DLL blocks was developed. In the third stage, hardware component design was required and hardware module was set up. In the fourth stage, software was need to be implemented using DSP based control and finally combined hardware set up was tested.

#### 1.3 Objectives

To design and implement a low-voltage high-current power supply with a regulated output voltage using DSP. Main objectives are to design a converter with the following requirements:

- Cost efficient AC/DC converter

- Output power:15 kW

- Output voltage: (0-30) V

- Output current:500 A

- Input voltage(3-ph): $415V \pm 15\%$

- Switching frequency of inverter:18000 Hz

- Output voltage ripple:40 mV(rms)

- Efficiency > 90%

#### 1.4 Literature Survey

Literature survey plays a very important role in the project. Literature survey consists of power topology, control schemes and related papers that includes mathematical modeling, simulation and experimental results. Some important information related to isolated DC-DC converters, phase shifted full-Bridge topology, high frequency transformer, Synchronous rectifier. Papers were taken from IEEE conference proceedings, journal proceedings, standard publications and application notes of different manufactures.

In this paper titled "Resonant, quasi-resonant, multi-resonant and soft swiching techniquesmerits and limitations" The quasi resonant converter achieves high efficiency, due to limitation of switching losses. turn on losses are limited because of inductive character of the load. The turn off losses are reduced by snubber capacitors, paralelly connected to power transistors. With charging and discharging of these capacitors, we can achieve the zero voltage switching mode. This quasi-resonant converter is able to control output voltage in wide range compared to resonant converter [1].

In this paper titled "Design of a 2.5 kW DC/DC Full-bridge Converter" It was found that by going from 20 kHz to 100 kHz the converter weight can be reduced by approximate 10% and by using the center-tap instead of full wave-bridge rectification the efficiency can improve by approximately 1-3%, from 94% up to approximately 97% efficiency can be achieved [2].

In this paper titled "Efficiency Improvement Techniques of High Current Low Voltage Rectifiers Using MOSFETs" This paper presents techniques for loss minimization in high-current low-voltage power supplies. Due to the use of synchronous rectification using MOSFETs offers the advantage of reducing the conduction losses significant compared to conventional rectification, with the possibility of achieving almost zero conduction losses through parallel connection. The design consideratious for paralleling MOSFETs are briefly discussed in this paper, as paralleling is required for high current requirements [7].

In this thesis, "Compact Isolated High Frequency DC/DC Converters Using Self-Driven Synchronous Rectification" This thesis introduces a mimimize of conduction losses using self-driven method to drive the secondary side synchronous rectifiers. Mimimize of conduction losses using self-driven method introduces two additional transformers that increase the overall size of the converter. Also, this topology introduced a new magnetic integration method to eliminate the need for the two additional gate driver magnetic cores, The magnetic integration reduces the overall converter size[9].

In this paper titled "Switching Analysis of Synchronous Rectifier MOSFETs with Phase-Shifted Full-Bridge Converter and Current Doubler" in this paper discussed the switching analysis of synchronous rectifier used the switch as MOSFETs in a phase-shifted full-bridge converter topology with a current doubler. Mainly two types of topologies are introduced for gate pulses of synchronous rectifier (SR) MOSFETs. The two different gate pulses introduced the Synchronous rectifier MOSFET operations during every stage for both topologies and the calculation of losses foe each and every stage is discussed[11].

In this paper titled "Design of Phase Shifted Full Bridge Converter with Current Doubler Rectifier" A wide range of isolated topologies are available for the dc-dc stage, high power rating could be realized with either a half-bridge or full-bridge. A full-bridge has half the rms current compared to a half-bridge, and it has been used for higher power rating applications, also it can be implemented with phase shifted control which provides Zero Voltage Switching (ZVS) for primary side switches, current doubler rectifier with synchronous rectification is the most suitable for high current application, as it splits the output current between two filter inductors, which reduces conduction losses, improves thermal distribution, and allows for lower profile, in addition to the ripple cancellation effect on the output capacitance [12].

In this paper titled "Phase-Shifted Full-Bridge, Zero-Voltage Transition Design Considerations" In this note highlight the design considerations in a high frequency power supply using the Phase Shifted PWM control technique. In this switching technique including comparisons for fixed frequency non resonant and variable frequency Zero Voltage Switching (ZVS) is discussed [13].

In this paper titled "ZVS Phase Shift Full Bridge CFD2 Optimized Design" in this paper the ZVS (Zero Voltage Switching) phase shifted full bridge converter is used in IFX board achieves this reduction of switching losses due to a zero voltage turn-on of the MOSFETs. In this design the ZVS operation is maintained from full load to light

load, but due to higher leakage inductance duty loss in secondary side transformer is higher [14].

In this paper titled "High Efficiency Current-Doubler Rectifier with Low Output Current Ripple and High Step-Down Voltage Ratio" This paper presents a current-doubler rectifier with high step-down voltage ratio and low output current ripple. In this proposed scheme, two extra inductors are introduced to extend the duty ratio of switches, and two extra diodes are used to provide discharge paths for the two extra inductors. To check the merits of the proposed rectifier, its performance indexes, such as secondary winding peak current of the isolation transformer, output current ripple and voltage gain function are discussed and compared with the conventional current-doubler rectifier [16].

In this paper titled "Design of efficient low voltage high current dc to dc power supply" In this paper low voltage high current DC to DC power supply is analysied. The converter is using single switch forward converter. On secondary side rectification, synchronous rectifiers are used. The voltage conversion ratio of the converter is high. Transformer based topologies are used for converters requiring high conversion ratio. The suitability of the proposed winding arrangement is used to improve the efficiency of the power supply. The magnetic design of the secondary winding arrangement is given. The loss calculation and the experimental results of the power supply are presented [19].

In this paper titled "Analysis and design of an Auxiliary Commutated Full Bridge DC/DC Converter Topology including the effect of Leakage Inductance" the transformer has high turns ratio between the primary and secondary windings, the value of leakage inductance is relatively high. This high value of leakage inductance is not large enough to achieve the zero voltage switching (ZVS) over the wide range of load conditions, but it can be used to minimize the circulating current of the auxiliary commutation circuit [27].

## Chapter 2

## Isolated Topologies for DC-DC Converter

#### 2.1 Introduction

Power supplies which are used extensively in industrial applications are often required to meet all or most of the following conditions.

- a. Isolation between the source and the load.

- b. Controlled direction of power flow.

- c. High power density for reduction of size and weight.

- d. High conversion efficiency.

Depending upon the output voltage, the power supplies can be categorized into two types:

- 1. DC POWER SUPPLIES

- 2. AC POWER SUPPLIES

Controlled DC Power supply can be obtained from the phase controlled rectifiers, but there are certain disadvantages, which led to the Switched Mode Power Supplies. An AC to DC rectifiers operates at supply frequency of 50 Hz so to obtain almost negligible ripple in the DC output voltage, physical size of the filter circuits required is large. This makes the DC power supply bulky, inefficient and weighty. In the other side, SMPS works like a DC chopper. By operating the on/off switch very rapidly, ripples can be easily filtered by the using of L and C filter circuits, which are small

in size and less weighty. By varying the duty cycle of the switching device by PWM techniques controls the output DC voltage [2] [3].

There are five common configurations for isolated DC-DC Power supply on primary side:

- Flyback topology

- Forward topology

- Push-Pull topology

- Half-Bridge topology

- Full-Bridge topology

#### 2.2 The Flyback Converter:

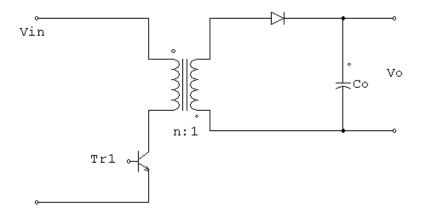

2.1 shows that use of a single transistor switch means that the transformer can only be driven asymmetrical, this results in a large core size. The Flyback is an isolated version of the buck-boost, so it is not used as a transformer but used as a coupled inductor. When the transistor is turned on, current flowing through the primary winding and energy is stored in the core. When the transistor is turned off, When the switch is turned off, current flowing through the secondary side and energy is released to the output.

Figure 2.1: Flyback Converter Circuit

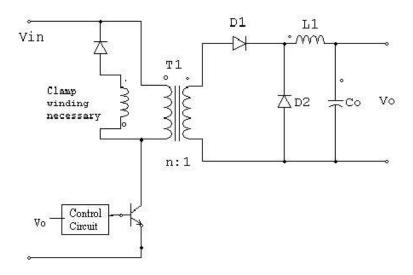

2.2 shows that the Forward Converter is also a single switch isolated topology, this is based on the buck converter with the addition of a inductor and another diode

Figure 2.2: Forward Converter Circuit

in the output circuit. In contrast to the Flyback, the Forward Converter has a true transformer action, When the transistor is turn on, energy is transferred directly to the output through the inductor. The polarity of the secondary winding is opposite to flyback, hence current flowing through diode D1.

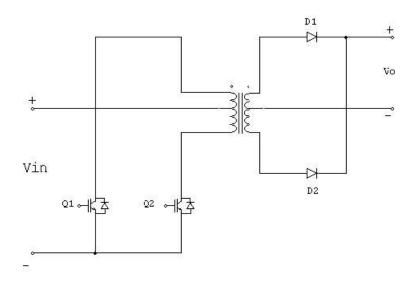

#### 2.3 The Push-Pull Converter:

2.3 shows that one of the best symmetrical types of converter, this permits much smaller transformer sizes and it provides higher output power. The primary is a center-tapped arrangement and each transistor switch is driven alternately, here transformer drives in both direction. The Push-Pull transformer is half the size of that for push-pull and flyback, it resulting in a more compact design compared to other converter.

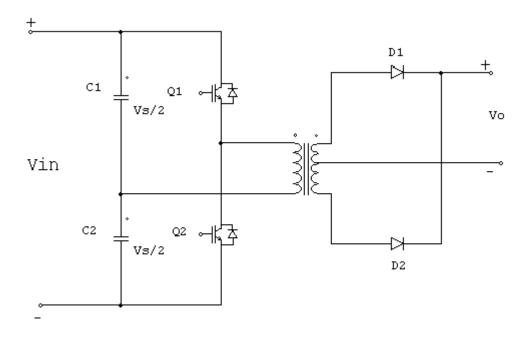

#### 2.4 The Half-Bridge Converter:

2.4 shows that the Half-Bridge Converter is also referred to as the single ended Push-Pull, and in principal is a balanced version of the Forward Converter. The two main bulk capacitors C1 and C2 are connected in series and an artificial input voltage mid-point is provided. The two transistors switches are driven alternately, and this connects each capacitors across the single primary winding each half cycle.

Figure 2.3: Push-Pull Converter Circuit

Figure 2.4: Half-Bridge Converter Circuit

Figure 2.5: Full-Bridge Converter Circuit

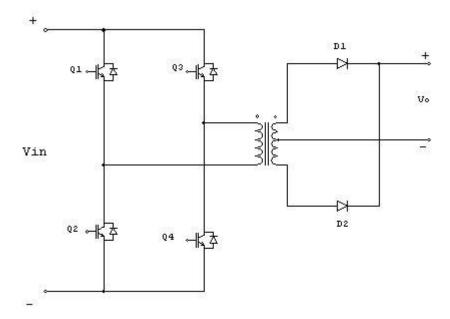

#### 2.5 The Full-Bridge Converter:

2.5 shows that the Full-Bridge Converter is a higher power version of the Half-Bridge, and provides the highest output power level of any of the converters which are discussed. The maximum current ratings of the power transistors will determine the upper limit of the output power of the half-Bridge. These levels can be doubled by using the Full-Bridge, which is obtained by adding another two transistors and clamp diode to the Half-Bridge arrangement [4] [5] [6].

So on primary side(high-voltage) selected topology is Full-Bridge converter, for the high(several kilowatts) power applications this topology is widely used. One should kept in mind that it has more cost than other topology because maximum switches are use.

## 2.6 Isolated topologies for Secondary Side (Low-Voltage)

The topology selection for a high frequency, compact, low voltage and high current converter is driven by thermal performance and power density. The converters ef-

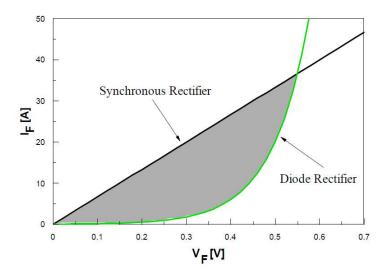

Figure 2.6: Comparison between Synchronous Rectifier and Diode Rectifier Conduction loss

ficiency must be maximized and the hot spots must be eliminated to improve the thermal performance in applications where a heat sink cannot be applied. In this application large step-down ratio is required, such as a 560 volt input to less than 35 volt output, the efficiency could be optimized with the use of a step down high transformer. On the secondary side conduction losses are dominant. So to minimize the conduction losses, MOSFET synchronous rectifiers (SR) can replace the diodes but the circuit implementation becomes more complex. The parallel combination of multiple synchronous rectifiers can further reduce the conduction losses. The parallel combination of multiple synchronous rectifiers will lower the effective Rds(on) and therefore it reduce I2 \* R losses. so the RMS current is divided between each synchronous rectifier, the losses are distributed and the thermal burden reduced.

In low output-voltage applications, the conduction loss of diode rectifier contributes significantly to the overall power loss. The rectifier conduction loss is proportional to the product of its forward-voltage drop  $(V_F)$  and the forward conduction current  $(I_F)$ . But the Forward Voltage drop of a synchronous rectifier can be lower than that of a diode rectifier, it reduces the rectifier conduction loss. So the synchronous rectifiers are widely used in Low voltage applications. 2.6 shows that the comparison between synchronous rectifier and diode rectifier conduction losses [7] [8] [20].

#### Secondary Side Different Synchronous Rectifier Topologies:

Isolated topologies can have multiple of secondary topologies, The four most commonly used secondary side topologies are the Full-Wave, Forward, Center-tap and Current-Doubler Rectifiers.

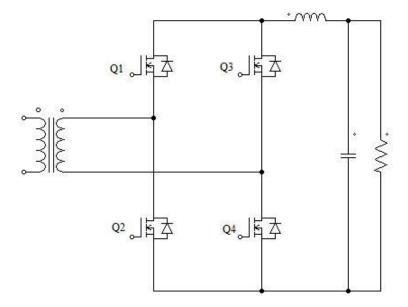

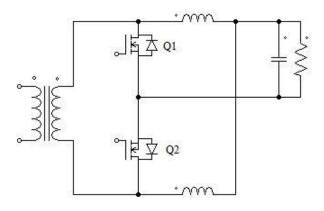

2.7 shows that during the power delivery period of the Full-wave Synchronous Rectifier, the filter inductor current is conducting through two mosfets in series. The conduction losses of the Full-wave Rectifier are twice of the Current-Doubler Rectifiers, Forward rectifiers, Center-tap and Current-Doubler Rectifiers. it is not suitable for Low-Voltage, High-Current applications but used in High- Voltage applications.

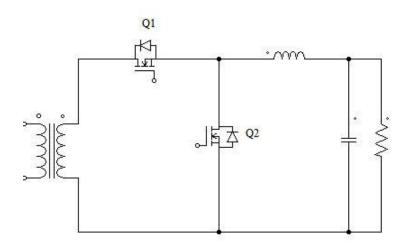

2.8 shows that the Forward Synchronous Rectifier has the most basic structure and it contains a simple two switches, high frequency transformer, a single filter inductor and a capacitor. This topology is least suitable for High-Current, Low-Voltage applications because the Forward Rectifier has a larger filter inductor and larger rectification losses. The filter inductor is sized to support the full load current at the converter's switching frequency. During the power delivery period the inductor current will flow through Q1, and during the freewheeling period Q2 will carry the full inductor current.

2.9 shows that Current-Doubler Circuit, Compared to the Forward and Center-tap Rectifiers, the current doubler has an additional filter inductor. The frequency seen by the filter inductors is the same as the switching frequency in the current doubler, but the size of these inductors can also be reduced. The filter inductors size reduction comes from a partial cancellation of the ripple current due to the interleaving properties of the Current Doubler.

2.10 shows that the Center-tap Synchronous Rectifier compared to the Forward topology, the filter inductor in the Center-tap Synchronous Rectifier is designed at twice the switching frequency which results in a smaller inductance value and also reduce the size. The filter inductor value is inversely proportional to the effective ripple current frequency, which results in a fifty percent reduction in the required inductance value. During the freewheeling period in a symmetrically driven Center-tap Rectifier the filter inductor current is evenly distributed between both rectifiers Q1 and Q2 resulting in lower rectifier conduction losses [9].

So on secondary side (low voltage) Center-tap Synchronous Rectifier is selected, due to the main advantage of the filter inductor in the Center-tap Synchronous Rectifier is designed at twice the switching frequency resulting in a smaller inductance value and lower conduction losses.

Figure 2.7: Full-Wave Synchronous Rectifier

Figure 2.8: Forward Synchronous Rectifier

Figure 2.9: Current-Doubler Synchronous Rectifier

Figure 2.10: Center-tap Synchronous Rectifier

## Chapter 3

## Quasi Resonant Converter

#### 3.1 Introduction

In the Quasi Resonant Converters, a high-frequency resonant tank circuit connected around the PWM switch is employed to shape the switch current and voltage so that high current and high voltage are never present simultaneously. As a result, stresses and switching losses in the devices are greatly reduced. Depending on how the high-frequency resonant circuit is connected to the switch, the Quasi -Resonant Converters can be either ZCS-QRCs or ZVS-QRCs, accordingly it eliminates either turn-off or turn-on loss [10][27]. In the Quasi Resonant Converters compared to Resonant Converter, it is able to control output voltage in wide range and it is comparatively easy to achieve and it is advantageously used the parasitic circuit elements to achieve the zero voltage switching or zero current switching so no need of extra resonant component.

#### 3.1.1 Advantages of ZVS (Zero voltage switching)

In a hard switching device, in order to reduce the switching losses for the semiconductor components, paralleling of passive components such as resistors, inductors and capacitors can be used. This different kind of parallel combinations of passive components is called snubber. Lossy snubbers are needed in order to absorb and dissipate voltage and current transients on the switching devices, so efficiency is decreses and cost is increses, but in a soft switching device, ZVS (Zero Voltage Switching) is achieved through the switching element of parasitic output capacitances resonate with the leakage inductance of the transformer and oscillate the switch voltage to zero before the switch turn on. At this stage, ZVS (which means no switching loss) occurs and a significant improvement in efficiency gained.

• Reduce or eliminate voltage and current spikes.

- Limit di/dt or dv/dt.

- Shape the load line to keep it within the safe operating area (SOA).

- Transfer power dissipation from the switch to a resistor.

- Reduce total losses due to switching.

- Reduce EMI by damping voltage and current ringing.

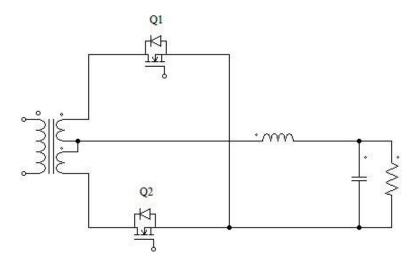

## 3.2 Why select the Phase Shifted Full-Bridge Topology?

In order to reduce the size and the weight of magnetic components it is desirable to increase the switching frequency for DC-DC converters. When conventional PWM converters are operated at high frequencies, the circuit parasitic has negative effects on the converter performance. Switching losses increase in high power applications and snubbers and/or other means of protection are required, which introduce significant losses and lower the efficiency. In the case of the conventional full bridge converter, the diagonally opposite switches (SA and SB, or SC and SD) are turned on and off simultaneously. When all four switches are turned off, the load current freewheels through the synchronous rectifier. In this case the energy stored in the leakage inductance of the power transformer causes severe ringing with IGBT Junction capacitance. This creates the need for using snubbers that increase the overall losses due to that efficiency is decreased. If snubbers are not used, the selection of the devices becomes more difficult as the voltage rating for these switches has to be much higher. The conduction losses and as a result the overall losses increase. At the same time the cost is also increases. So in order to minimize the parasitic ringing, the Phase Shifted Full-Bridge Topology is selected. In this topology the gate signals of SC and SD are delayed (Phase-Shifted) with respect to those of SA and SB as shown in 3.1. There is a small amount of overlap between SA and SB, and SC and SD, which is called PWM delay (PWM delay AB, and PWM delay CD). PWM delay will prevent the same-side IGBTs (SA and SB, or SC and SD) from turning on simultaneously, which would result in a short circuit that burns out the IGBTs. In addition, the delay time helps so that the primary of the transformer is either connected to the input voltage or shorted. The leakage inductance current is never interrupted, thus solving the problem of parasitic ringing associated with the Conventional Full-Bridge PWM converter. When the PWM pulse is off, the snubber inductance Lr, by way of storage energy, will resonate with the output capacitances of the IGBTs and oscillate the IGBT voltage to zero before the IGBTs turn on. At this stage, ZVS (which means

Figure 3.1: Gate Pulses of Phase Shifted PWM control waveform

no switching loss) occurs and a significant improvement in efficiency is gained [11].

The energy stored in the leakage inductance can be used to discharge the energy stored in the IGBT junction capacitance to achieve zero voltage switching (ZVS) conditions for all four switches in the primary side. In this case, the converter requires no additional resonant components [12] [13].

## 3.3 Resonant Circuit Design with 18kHz Switching Frequency of 15 kW Power Supply

#### 3.3.1 Resonant Capacitance $C_R$

The specified IGBT switch output capacitance  $C_{oss}$  will be multiplied by 4/3 factor as per the IGBT manufacturers application note to approximate the correct average capacitance value with a varying drain voltage. During each transition, two switch capacitances are driven in parallel, doubling the total capacitance to 8/3\* $C_{oss}$ . Transformer capacitance  $C_{XFMR}$  must also be added as it is not negligible in many high frequency application.

$$C_R = \frac{8}{3}C_{oss} + C_{XFRM} \tag{3.1}$$

$$C_R = \frac{8}{3}(25n) + 5n$$

$$C_R = 71nF$$

The capacitive energy required to complete the transition  $W_{CR}$ :

$$W_{CR} = \frac{1}{2} C_R V_I^2 \tag{3.2}$$

The energy can be expressed as:

$$W_{CR} = \frac{1}{2} \left( \frac{8}{3} C_{oss} + C_{XFRM} \right) V_I^2 \tag{3.3}$$

#### 3.3.2 Resonant Inductor $L_R$

ZVS may be lost partially or completely due to lack of energy or insufficient dead time. During no load and light load conditions, ZVS may be lost if the inductive energy available in the circuit is not sufficient to charge and discharge the output capacitance of the two IGBTs in the same bridge leg in addition to the transformer capacitance.

Calculate the resonant inductor value  $L_R$  ( $L_R$ = External series inductance+ Leakage inductance) and minimum primary current required for any application. These parameters are calculated as per the following equations.

#### The first criterion for achieving ZVS is:

$$\frac{1}{2} \times L_R \times I_P^2 > \frac{1}{2} \times C_R \times V_I^2 \tag{3.4}$$

$$L_R > \frac{C_R \times V_I^2}{I_P^2} \tag{3.5}$$

$$L_R > \frac{(71n)\times(415)^2}{(28.2)^2}$$

$$L_R > 16\mu H$$

So for Zero voltage switching requirement must be greater than 16  $\mu H$  but primary side leakage inductance of transformer is 32  $\mu H$  so external inductance is not require to connect in series with primary winding of transformer[14].

#### 3.3.3 Energy and Dead time conditions for achieving ZVS:

The second criterion for achieving ZVS is that the delay time is long enough to allow resonant voltages to finish the energy transfer in  $C_{oss}$  and  $L_R$ . Assuming the frequency of the resonant is  $F_{RES}$ .

$$T_{RES} = \frac{1}{F_{RES}} \tag{3.6}$$

While the  $C_{oss}$  of the IGBT discharges from  $V_I = \max$  to zero and the  $C_{oss}$  of the IGBT charges from  $V_I = \text{zero to max}$ . The delay time(dead band) must be greater than  $\frac{1}{4}T_{RES}$ .

$$F_{RES} = \frac{1}{2\Pi\sqrt{L_R C_R}} \tag{3.7}$$

$$F_{RES} = \frac{1}{2\Pi\sqrt{(30\mu)(70n)}}$$

$F_{RES} = 109.82 \text{ KHz}$

$$T_{RES}$$

=9.10  $\mu s$

The resonant tank period must be at least four times higher than the transition time to fully resonant within the maximum transition time  $T_R$  at light load.

$$T_R = \frac{1}{4} T_{RES} \tag{3.8}$$

$T_R = 2.27 \ \mu s$

But for achieving the ZVS, the delay time or dead band  $(t_{max})$  must be greater than  $\frac{1}{4}T_{RES}$ . Otherwise the IGBT cannot achieve ZVS. If Delay time below  $\frac{1}{4}T_{RES}$  will cause switching at a non-zero voltage(partial ZVS), on the other hand, delay time higher than  $\frac{1}{4}T_{RES}$  will cause extra body diode conduction losses, furthermore, might cause losing ZVS if the resonant circuit is highly damped (or lossy). The larger delay time will cause the maximum duty cycle to be smaller, impacting the hold-up time performance [15].

$$T_{MAX} > \frac{1}{4} T_{RES} \tag{3.9}$$

Select the value of  $T_{MAX}$ =2.2  $\mu s$

#### 3.3.4 Minimum(critical) Primary current

The minimum primary current required for the phase-shifted application can now determined because below this critical current level will result in lossy transition and also ZVS can not be achieved below critical current.

$$I_{PRI} = \sqrt{\frac{C_R \times V_I^2}{L_R}} \tag{3.10}$$

$I_{PRI} = 19.1 \text{ A}$

But transformer primary current in this case is 28.2 A, which is more than minimum primary current [16] [17].

# 3.4 Resonant Circuit Design with 18 kHz Switching Frequency of 900 W Prototype Power Supply

#### 3.4.1 Resonant Capacitance $C_R$

$$C_R = \frac{8}{3}C_{oss} + C_{XFRM} (3.11)$$

$$C_R = \frac{8}{3}(5n) + 5n$$

$$C_R = 15.66 \text{ nF}$$

Where,

$C_{oss}$  = output capacitance of IGBT which is mention in IGBT's datasheet

$V_I$ = Input voltage= 415 V

$I_P$ = Input current= 2.4 A

The capacitive energy required to complete the transition  $W_{CR}$ :

$$W_{CR} = \frac{1}{2} C_R V_I^2 \tag{3.12}$$

The energy can be expressed as:

$$W_{CR} = \frac{1}{2} \left( \frac{8}{3} C_{oss} + C_{XFRM} \right) V_I^2 \tag{3.13}$$

#### 3.4.2 Resonant Inductor $L_R$

The first criterion for achieving ZVS is

$$\frac{1}{2} \times L_R \times I_P^2 > \frac{1}{2} \times C_R \times V_I^2 \tag{3.14}$$

$$L_R > \frac{C_R \times V_I^2}{I_P^2} \tag{3.15}$$

$$L_R > \frac{(15.66n)\times(415)^2}{(2.4)^2}$$

$$L_R > 440 \mu H$$

So for Zero voltage switching requirement must be greater than 440  $\mu H$  but primary side leakage inductance of transformer is 600  $\mu H$  so external inductance is not require to connect in series with primary winding of transformer[15].

#### 3.4.3 Energy and Dead time conditions for achieving ZVS:

The second criterion for achieving ZVS is that the delay time is long enough to allow resonant voltages to finish the energy transfer in  $C_{oss}$  and  $L_R$ . Assuming the frequency of the resonant is  $F_{RES}$ .

$$T_{RES} = \frac{1}{F_{RES}} \tag{3.16}$$

While the  $C_{oss}$  of the IGBT discharges from  $V_I = \max$  to zero and the  $C_{oss}$  of the IGBT charges from  $V_I = \text{zero to max}$ . The delay time(dead band) must be greater than  $\frac{1}{4}T_{RES}$ .

$$F_{RES} = \frac{1}{2\Pi\sqrt{L_R C_R}} \tag{3.17}$$

$$F_{RES} = \frac{1}{2\Pi\sqrt{(440\mu)(15.66n)}}$$

$F_{RES} = 60.63 \text{ kHz}$

$T_{RES}$ =16.5  $\mu s$

$$T_R = \frac{1}{4} T_{RES}$$

(3.18)

$T_R = 4.12 \ \mu s$

Select the value of  $T_{MAX}$ =3.2  $\mu s$

#### 3.4.4 Minimum(critical) Primary current

The minimum primary current required for the phase-shifted application can now determined because below this critical current level will result in lossy transition and also ZVS can not be achieved below critical current.

$$I_{PRI} = \sqrt{\frac{C_R \times V_I^2}{L_R}} \tag{3.19}$$

$I_{PRI} = 2.14 \text{ A}$

But transformer primary current in this case is 2.4 A, which is more than minimum primary current [16] [17].

### Chapter 4

### Design of 18 kHz High Frequency Transformer

#### 4.1 Introduction

The fundamental requirements of magnetic material for power transformers are the lowest core loss, highest relative permeability, the largest saturation flux density and the lowest remanent flux density. magnetic material using as the cores of power transformers keep charging as the operating frequency increased. At the line frequency of 50/60 Hz, iron, silicon steel are the major materials for the cores of the power transformers. They have high saturation flux density, thus they can handle high power transformer at low operating frequency. when the operating frequency of power transformer increased, the eddy current inside the magnetic cores becomes a critical problem for the transformer designers. Although the laminated core material have been used, the power loss generated inside magnetic core can destroy whole power transformer. As the operating frequency is increased more and more magnetic materials have been introduced for high frequency power transformer application [18].

## 4.1.1 The characteristics of High Frequency Transformer windings:

When the operating frequency increases, the total number of turns decreases significantly. Therefore the total length of the copper winding is also decreased dramatically. The power loss due to DC resistance almost becomes zero suddenly. It is very good for the power transformer design. However, with disappearing of the DC. At high frequencies, the major loss within windings is due to eddy currents produced by the skin and proximity effects. These effects can cause the windings losses to be significantly greater than the  $I^2R$ loss calculated using the DC resistance of the copper winding.

#### 4.1.2 Properties of Ferrite Core

Ferrite is a class of ceramic material with useful electro magnetic properties. It is basically a mixture between iron oxide and different kinds of metal oxides. These kinds of metal oxide in various amounts allows the manufacturer to produce many types of ferrites for different applications. Ferrite cores have very high permeability. Resistivity is really high so eddy currents can be neglected when it comes to ferrite cores and for high frequency range ferrite core is widely used.

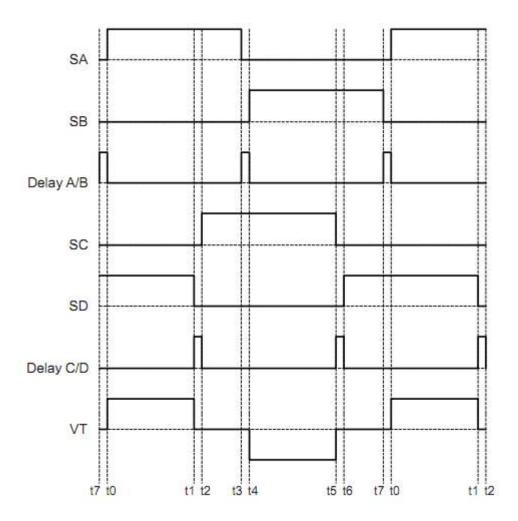

## 4.2 Design and Flowchart for High Frequency Transformer

Steps for designing the High Frequency Transformer is as follows:

step1:

Calculate the output power.

step 2:

Calculate the area product.

Step 3:

Select the Core from the table with a value close to the calculated one.

Step 4;

Calculate the core losses in mw/g from the graph of flux density, frequency and core losses for the ferrite core.

Step 5:

Calculate the primary and secondary turns.

Step 6

Find the wire gauge and calculate the resistance of the resistance of the windings.

Step 7:

Calculate the copper losses and the total losses.

Step 8:

Check whether the turns fit into the effective window area.

The inequality is as follows:

$A_W K_W > \Sigma A_I N_I$

Figure 4.1: Flowchart for Design of High Frequency Transformer

Where  $A_W K_W$  is the effective window area available for the winding. $\Sigma A_I N_I$  is the area occupied by the winding.

## 4.3 Design and Development of 900 VA,18 kHz Transformer for Prototype Power Supply

The AC-DC low-voltage high-current power supply requires DC-DC converter, a ferrite Core Transformer, Synchronous rectifier, L-C filter. So the following criteria were followed [19].

#### 4.3.1 Design Specifications:

- 3-ph Input Voltage( $V_{IN}$ )= 415 V±15%

- Input Current( $I_{IN}$ )=2.40 A(rms)

- Output Voltage $(V_O)$ = 0-30 V

- Output Current( $I_O$ )=30 A

- Switching Frequency( $F_s$ ) =18 kHz

Output Power  $(P_O)$ :

$$P_O = V_O \times I_O \tag{4.1}$$

$P_{O} = 30 \times 30$

$P_{O} = 900 \text{ W}$

If we consider 90% efficiency, then Input Power( $P_{IN}$ ) becomes;

$$P_{IN} = \frac{P_O}{\eta} \tag{4.2}$$

$P_{IN} = 1000 \text{ W}$

Input Current  $(I_{IN})$ :

$$I_{IN} = \frac{P_{IN}}{V_{IN}} \tag{4.3}$$

$I_{IN} = 2.40 \text{ A(rms)}$

The governing equation for Full-bridge configuration is given by:

$$P_O = V_O I_O + V_d I_O + P_{Lcu} + P_{Lcore} \tag{4.4}$$

Where,

$V_d$ =Diode Voltage drop=1 V

$V_O$ =Output Voltage=30 V

$P_{Lcu} + P_{Lcore} =$  Cu Losses and Core Losses = 10 % of  $V_OI_O = 90$  W

$P_O(with losses) = 1020 \text{ W}$

#### 4.3.2 Selection of Magnetic Core:

Area of  $Product(A_P)$ :

$$A_P = A_C A_W \tag{4.5}$$

$$A_P = \frac{P_O(\sqrt{2} + \frac{1}{\eta})}{4K_W J B_m F_s} \tag{4.6}$$

Where,

$A_P$ =Area of Product

$A_c$ =Area of core

$A_W$  = Window area

$K_w$ = Window utilization factor=0.4

$B_m = \text{Maximum flux density} = 0.2 \text{ Tesla}$

J=Current Density= $2-5 \text{ A}/mm^2$  is good compromise between conductor resistance and window area. Here it is taken  $3A/mm^2$ .

So put all these value in to equ.4.6

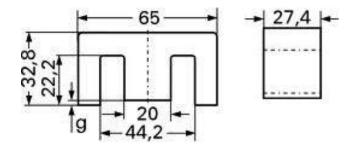

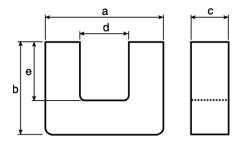

Table I: Dimension of EE 65/32/27 Ferrite Core

| Core No.      | a mm  | b mm  | c mm  | d mm    | e mm  | f mm |

|---------------|-------|-------|-------|---------|-------|------|

| EE $65/32/27$ | 65 mm | 32 mm | 27 mm | 44.2 mm | 22 mm | 20mm |

Table II: Dimension of EE 65/32/27 Ferrite Core

| Core No.   | Ap $mm^4$         | $Ac mm^2$    | Aw $mm^2$       |

|------------|-------------------|--------------|-----------------|

| E 65/32/27 | $3,04,616 \ mm^4$ | $567 \ mm^2$ | $537.24 \ mm^2$ |

$A_P=2,98,128 \ mm^4$

From the product area, Selected core is E65/32/27.

#### 4.3.3 Dimension of EE 65/32/27 Ferrite Core:

Figure 4.2: Dimension of EE 65/32/27 Ferrite Core

The dimensions and performance parameters of EE 65/32/27 Ferrite Core are given in Table 4.1 and 4.2;

#### 4.3.4 Calculation of Number of turns:

Primary Turns $(N_p)$ :

$$N_p = \frac{V_{IN}}{2A_C B_m F_s} \tag{4.7}$$

$N_p = 110 \text{ turns}$

Secondary turns( $N_s$ ):

$$N_s = \frac{E_s}{2A_C B_m F_s} \tag{4.8}$$

where,

$$E_s = \frac{V_O + V_d + (0.1V_O)}{D_{max}}$$

(4.9)

$E_s = 40 \text{ V}$

Hence  $N_s = N_t = 9$  turns

Wire cross section area of primary winding  $(a_p)$ :

$$ap = \frac{I_{pri}}{J} \tag{4.10}$$

$ap = 0.66 \ mm^2$

So take the 3 parallel wire of SWG-25.

NOTE: Current flowing through SWG-25 is 608 mA.

Wire cross section area of secondary winding  $(a_s)$ :

$$a_s = \frac{I_{sec}}{J} \tag{4.11}$$

$a_s = at = 7 \ mm^2$  so take the 14 parallel wire of SWG-25.

#### Cross-check:

$$a_p = 0.66mm^2$$

$$a_s = at = 7mm^2$$

$$N_p = 110 \text{ turns}$$

$$N_s = N_t = 9 \text{ turns}$$

$$A_w = 537.24 \ mm^2$$

$$K_w = 0.4$$

$$A_w K_w > a_p N_p + 2a_s N_s \tag{4.12}$$

$214 \ mm^2 > 198mm^2$

So, the above condition is satisfied, So core selection is proper.

#### 4.3.5 Development of Transformer

To make transformer following steps were followed;

- a. Make the bobbin as per dimensions of selected core.

- b. Wound the primary, secondary and tertiary windings in such a way that gives sufficient leakage inductance.

- c. The insulation layer between primary and secondary winding should be such that it gives desired isolation between them.

- d. Measurement of magnetizing inductance of primary, secondary and tertiary windings also measure the leakage inductance and resistance.

#### 4.3.6 Theoretical Calculations:

Primary Resistance=0.2268  $\Omega$

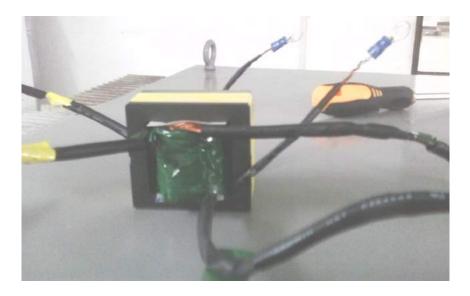

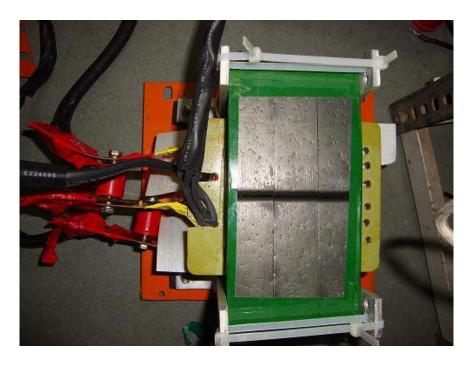

Figure 4.3: Overall view of 18 kHz, 900 VA Transformer

Secondary Resistance=18.9 m $\Omega$

Tertiary Resistance=18.9 m $\Omega$

Magnetizing Inductance=95.5 mH

Leakage Inductance of primary winding=440  $\mu H$

Leakage Inductance of secondary winding=4  $\mu H$

Leakage Inductance of tertiary winding=4  $\mu H$

#### 4.3.7 Practical Results:

Primary Resistance= $0.5 \Omega$

Secondary Resistance=14 m $\Omega$

Tertiary Resistance=15.2 m $\Omega$

Magnetizing Inductance=87 mH

Leakage Inductance of primary winding=440  $\mu H$

Leakage inductance of secondary winding=1.2  $\mu H$

Leakage Inductance of tertiary winding=1.3  $\mu H$

#### 4.4 Design of L-C Filter

To filter the output voltage and current low-pass L-C filter is needed.

#### 4.4.1 Calculate the value of Inductor

In a inductor, the core flux is decided by the load current. Thus if the load current increases, there is possibility that the core may saturate and inductance will come down. So before decide the value of inductor maximum load current must be known.

$$L = \frac{V_o \times (1 - D)}{\Delta I \times F_s} \tag{4.13}$$

Where,

Output voltage=  $V_o$ =30 V

Duty cycle= 0.85

$\Delta I$ = ripple current= 40% of output current=12 A

Switching Frequency= $F_s$ =18 kHz

$L = 20\mu H$

#### 4.4.2 Calculate the value of Capacitor

$$C = \frac{D \times I_o}{\Delta V \times F_o} \tag{4.14}$$

Where,

Output current=  $I_o$ =30 A

Duty cycle= 0.85

$\Delta V$  = ripple voltage= 40m% of output voltage= 1.2 V

Switching Frequency= $F_s$ =18 kHz

C = 1.66 mF

#### 4.5 Development of 20 $\mu H$ Inductor

Primary consideration in designing an inductor is that value of maximum load current (37 A) and to select the core, which does not saturate at this current. With provision of appropriate air gap in the coil so it can carry considerably larger current without saturating the core [18] [20].

#### 4.5.1 Selection of Magnetic Core

For the selection of Core, Area of product can be calculated. The Energy and Area of product calculations are as follows;

$$E = \frac{1}{2}LI_m^2 (4.15)$$

E=0.0137 joules

$$A_p = \frac{2E}{K_w K_c J B_m} \tag{4.16}$$

Where,

There is only one winding so  $K_c=1$

$K_{w} = 0.4$

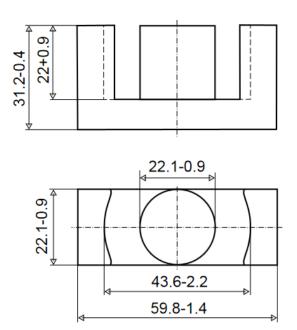

Figure 4.4: Dimension of ETD 59 Ferrite Core

$J=3 A/mm^2$

$B_m$ =0.2 Tesla

$A_p = 114.08 \ mm^4$

From core selection table, Selected core is ETD 59 whose Area of product is 142.15  $mm^4$ , which is greater than calculated.

#### 4.5.2 Calculation of Numbers of Turns