# Front-end ASIC Design and Verification of Programmable and Precision Delay Timing Generator for CCD Detectors

# Major Project Report

Submitted in partial fulfillment of the requirements for the degree of

Master of Technology in Electronics & Communication Engineering (VLSI Design)

By

Urvi Mehta (13MECV11)

Electronics & Communication Engineering Branch Electrical Engineering Department Institute of Technology Nirma University Ahmedabad-382 481 May 2015

# Front-end ASIC Design and Verification of Programmable and Precision Delay Timing Generator for CCD Detectors

# Major Project Report

Submitted in partial fulfillment of the requirements for the degree of

Master of Technology in Electronics & Communication Engineering (VLSI Design)

By

Urvi Mehta (13MECV11)

Under the guidance of

#### **External Project Guide:**

Shri Mohammad Waris Shri Rajiv kumaran Sci/Eng.,SAC ISRO,Ahmedabad. **Internal Project Guide:**

**Dr. Usha S. Mehta** Professor,EC Institute of Technology, Nirma University, Ahmedabad.

Electronics & Communication Engineering Branch Electrical Engineering Department Institute of Technology Nirma University Ahmedabad-382 481 May 2015

# Declaration

This is to certify that

- 1. The thesis comprises my original work towards the degree of Master of Technology in VLSI Design at Nirma University and has not been submitted elsewhere for a degree.

- 2. Due acknowledgment has been made in the text to all other material used.

- Urvi Mehta 13MECV11

# Certificate

This is to certify that the Major Project entitled "Front-end ASIC Design and Verification of Programmable and Precision Delay Timing Generator for CCD Detectors" submitted by Urvi K. Mehta (13MECV11), towards the partial fulfillment of the requirements for the degree of Master of Technology in VLSI Design, Nirma University, Ahmedabad is the record of work carried out by her under our supervision and guidance. In our opinion, the submitted work has reached a level required for being accepted for examination. The results embodied in this major project, to the best of our knowledge, haven't been submitted to any other university or institution for award of any degree or diploma.

Date:

Internal Guide

**Dr. U. S. Mehta** (Professor, EC)

Program Co-ordinator

**Dr. N. M. Devashrayee** (Professor, EC)

#### HOD

**Dr. P.N. Tekwani** (Professor,EE)

External guide

Place: Ahmedabad

Shri. Mohammad Waris (Sci/Engr -SD)

Shri. Rajiv Kumaran (Sci/Engr -SF)

**Shri. Sanjeev Mehta** (Head -SFED)

Director

**Dr.K Kotecha** (Director,IT-NU)

# Acknowledgements

I would like to express my gratitude and sincere thanks to **Dr.P.N.Tekwani**, Head of Electrical Engineering Department, and **Dr. N. M. Devashrayee**, PG Coordinator of M.Tech VLSI Design program for allowing me to undertake this thesis work and for their guidelines during the review process.

I am deeply indebted to my thesis supervisor **Dr. Usha S. Mehta**, Professor, E.C.Dept., Nirma University for her constant guidance and motivation.

I would like to express my gratitude towards thesis supervisor Shri. Mohammad Waris (Scientist/Engineer-SD) Shri. Rajiv Kumaran (Scientist/Engineer-SF), and Shri. Sanjeev Mehta (Head, Sensor Front End Electronic Division), Sensor Electronic Group, Sensor Development Area (SEDA), at Space Application Centre (SAC), Ahmedabad, Indian Space Research Organization (ISRO). Without their experience and insights, it would have been very difficult to do quality work. I am grateful to Shri. J. Ravisankar, Head, HRDD, for giving me the opportunity to pursue this thesis in the premises of SAC-ISRO.

Last, but not the least, I would like to thank my family members for their constant support.

- Urvi Mehta 13MECV11

## Abstract

Charge Coupled Devices (CCD) work by converting light into a pattern of electronic charge in a silicon chip.CCDs have features like high sensitivity, high linear dynamic range, electronic shuttering capability and low dark current.Various CCD architectures like linear array, full frame, interline, TDI, etc. are used for various application.One of the main unit in a CCD based satellite imaging system is Timing Generator producing various kinds of readout clocks and control signals for different CCD architectures .

This Project discusses about the front-end ASIC design of programmable and precision delay timing generator for various CCD architectures. Various CCD requires different types and number of clocks for its operation. The aim is to provide flexibility in terms of number of different types of clocks, effective image area, read out feature and a very precise delay control for each clock. Programmable clock generation with precise delay is implemented with an all digital Delay Locked Loop (DLL) because of its features like low power, smaller area, high noise immunity and synthesizable circuit. Precise delay resolution in sub nano seconds (approximately 620 ps) is obtained at clock frequency of 20 MHz. Programmable pulse generation logic is designed which can generate pulses with variable frequency and with variable pulse widths. The design is targeted with 180 nm technology. A single chip can cater to support various CCD architectures with full programmability.

Assertion based and coverage driven constrained random verification of precision delay timing generator is carried out using system verilog.

# Contents

| D        | eclar  | ation                                                                                                | iii          |

|----------|--------|------------------------------------------------------------------------------------------------------|--------------|

| C        | ertifi | cate                                                                                                 | iv           |

| A        | ckno   | wledgements                                                                                          | $\mathbf{v}$ |

| 1        | Inti   | roduction                                                                                            | 1            |

|          | 1.1    | Objective and scope of the project                                                                   | 1            |

|          | 1.2    | Organization of Thesis                                                                               | 2            |

| <b>2</b> | Inti   | coduction to CCD Fundamentals                                                                        | 3            |

|          | 2.1    | Introduction to CCD                                                                                  | 3            |

|          |        | 2.1.1 Structure of CCD                                                                               | 3            |

|          |        | 2.1.2 Steps of CCD imaging Operation                                                                 | 4            |

|          | 2.2    | CCD based Satellite imaging System                                                                   | 5            |

|          | 2.3    | CCD Detector Array Architectures                                                                     | 6            |

|          | 2.4    | CCD Signal Processing Blocks                                                                         | 9            |

|          | 2.5    | Timing Generator                                                                                     | 10           |

|          | 2.6    | Image data acquiring and processing systems                                                          | 11           |

|          | 2.7    | Summary                                                                                              | 11           |

| 3        | Pre    | cision Timing Generation                                                                             | 12           |

|          | 3.1    | Phase Locked Loop (PLL)                                                                              | 12           |

|          | 3.2    | Delay line $\ldots$ | 14           |

|          |        | 3.2.1 Coarse Delay Line                                                                              | 14           |

|          |        | 3.2.2 Fine Delay Line                                                                                | 15           |

|          | 3.3    | Delay Locked Loop (DLL) $\ldots$                                                                     | 16           |

|          |        | 3.3.1 Analog DLL                                                                                     | 17           |

|          |        | 3.3.2 Digital DLL                                                                                    | 20           |

|          | 3.4    | Approaches For Digital DLL Designs:                                                                  | 22           |

|          |        | 3.4.1 Register controlled DLL (RDLL)                                                                 | 22           |

|          |        | 3.4.2 Counter controlled DLL (CDLL)                                                                  | 23           |

|          |                      | 3.4.3 Successive Approximation Register Controlled DLL (SAR-DLL) 24       |  |  |  |  |

|----------|----------------------|---------------------------------------------------------------------------|--|--|--|--|

|          | 3.5                  | Edge Programmable timing signal generation (clock pulse generation) 25    |  |  |  |  |

|          | 3.6                  | Summary                                                                   |  |  |  |  |

| 4        | $\mathbf{Des}$       | ign Requirements And Specifications 29                                    |  |  |  |  |

|          | 4.1                  | Clock Requirements for Timing Generator                                   |  |  |  |  |

|          |                      | 4.1.1 CCD Driving Clocks                                                  |  |  |  |  |

|          | 4.2                  | CCD signal Processing Clocks                                              |  |  |  |  |

|          | 4.3                  | Programmability features of Detector Clocks                               |  |  |  |  |

|          | 4.4                  | Targeted Specifications for Timing Generator                              |  |  |  |  |

|          | 4.5                  | Summary                                                                   |  |  |  |  |

| <b>5</b> | $\operatorname{Det}$ | ailed Design 33                                                           |  |  |  |  |

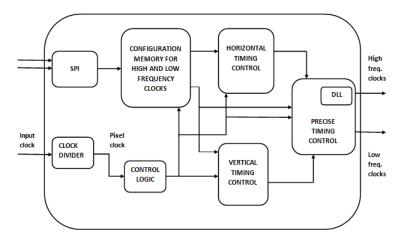

|          | 5.1                  | Top level architecture of Precision timing generator for CCD detectors 33 |  |  |  |  |

|          | 5.2                  | Serial Peripheral Interface (SPI)                                         |  |  |  |  |

|          | 5.3                  | Configuration Memory for high frequency and low frequency clocks 35       |  |  |  |  |

|          | 5.4                  | Clock divider                                                             |  |  |  |  |

|          | 5.5                  | Precision timing control                                                  |  |  |  |  |

|          |                      | 5.5.1 Phase detector                                                      |  |  |  |  |

|          |                      | 5.5.2 Counter based Controller                                            |  |  |  |  |

|          |                      | 5.5.3 MUX based delay line                                                |  |  |  |  |

|          |                      | 5.5.4 Fine clock pulse generator                                          |  |  |  |  |

|          | 5.6                  | Horizontal timing control                                                 |  |  |  |  |

|          | 5.7                  | Vertical Timing Control                                                   |  |  |  |  |

|          | 5.8                  | Line and Frame synchronizing pulse generation block                       |  |  |  |  |

|          | 5.9                  | Exposure clock generation block                                           |  |  |  |  |

|          | 5.10                 | Horizontal and Vertical Masking block                                     |  |  |  |  |

|          |                      | 5.10.1 Masking Toggle generation logic                                    |  |  |  |  |

|          | 5.11                 | Summary                                                                   |  |  |  |  |

| 6        | $\mathbf{Sim}$       | ulation And Synthesis Results 50                                          |  |  |  |  |

|          | 6.1                  | Block level STA results                                                   |  |  |  |  |

|          |                      | 6.1.1 Horizontal coarse clock generator                                   |  |  |  |  |

|          |                      | 6.1.2 Horizontal and vertical fine clock generator                        |  |  |  |  |

|          |                      | 6.1.3 Horizontal and Vertical blanking                                    |  |  |  |  |

|          |                      | 6.1.4 Vertical coarse clock generator                                     |  |  |  |  |

|          |                      | 6.1.5 DLL                                                                 |  |  |  |  |

|          |                      | 6.1.6 Line and frame synchronization pulse generator                      |  |  |  |  |

|          |                      | 6.1.7 Exposure clock generator                                            |  |  |  |  |

|          | 6.2                  | Simulation Results                                                        |  |  |  |  |

|   |     | 6.2.1    | DLL                                                                                                  |

|---|-----|----------|------------------------------------------------------------------------------------------------------|

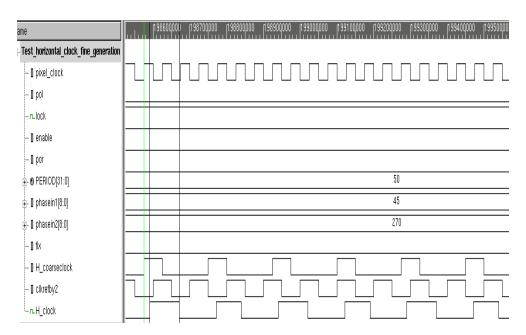

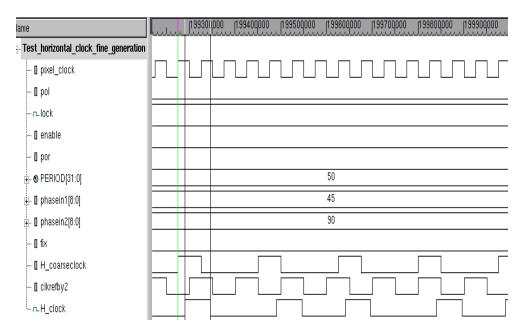

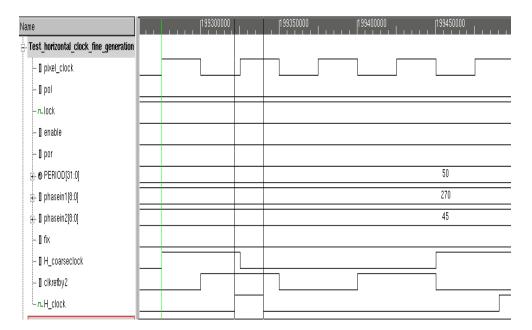

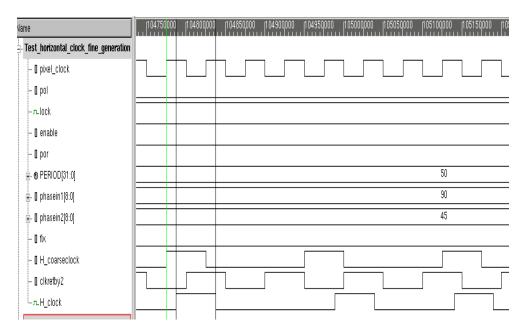

|   |     | 6.2.2    | Fine clock generator                                                                                 |

|   |     | 6.2.3    | Horizontal clock                                                                                     |

|   |     | 6.2.4    | Vertical clock                                                                                       |

|   |     | 6.2.5    | Line and Frame synchronization pulses                                                                |

|   |     | 6.2.6    | Exposure Clock                                                                                       |

|   | 6.3 | Summ     | ary                                                                                                  |

| 7 | Ver | ificatio | n 59                                                                                                 |

|   | 7.1 | Direct   | ed v/s Constrained Random Verification                                                               |

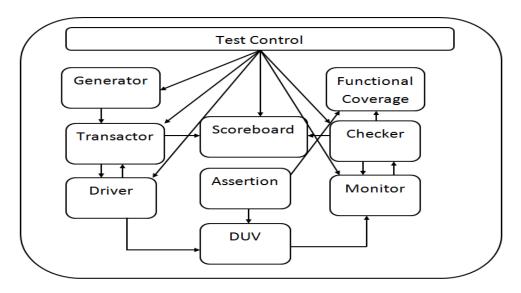

|   | 7.2 | Basic .  | Architecture of Coverage Driven Constrained Random Verification $\ldots$ 60                          |

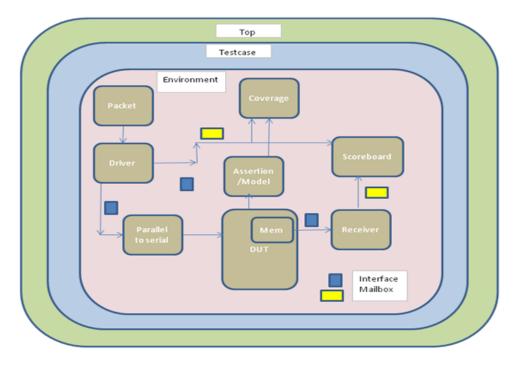

|   | 7.3 | Verific  | ation Environment for Timing Generator                                                               |

|   | 7.4 | Verific  | ation Plan $\ldots$ |

|   |     | 7.4.1    | Verification checks for SPI                                                                          |

|   |     | 7.4.2    | Verification checks for SPI to Memory Interface                                                      |

|   |     | 7.4.3    | Verification checks for Memory 64                                                                    |

|   |     | 7.4.4    | Verification checks for Clock divider                                                                |

|   |     | 7.4.5    | Verification checks for Line and frame Synchronization pulse 64                                      |

|   |     | 7.4.6    | Verification checks for Exposure shuttering control                                                  |

|   |     | 7.4.7    | Verification checks for Horizontal Clock                                                             |

|   |     | 7.4.8    | Verification checks for Fine clock generation                                                        |

|   |     | 7.4.9    | Verification checks for Horizontal Masking Signal Generation 65                                      |

|   |     | 7.4.10   | Verification checks for Toggle Masking                                                               |

|   |     | 7.4.11   | Verification checks for Vertical coarse clock                                                        |

|   |     | 7.4.12   | Verification checks for Vertical Masking Signal Generation 66                                        |

|   |     | 7.4.13   | Verification checks for CLPOB signal generation                                                      |

|   | 7.5 | Covera   | age Plan                                                                                             |

|   | 7.6 | Code (   | Coverage Results                                                                                     |

|   |     | 7.6.1    | Horizontal coarse clock                                                                              |

|   |     | 7.6.2    | Fine clock generator                                                                                 |

|   |     | 7.6.3    | Delay Lock Loop (DLL)                                                                                |

|   |     | 7.6.4    | Phase Detector                                                                                       |

|   |     | 7.6.5    | Controller                                                                                           |

|   |     | 7.6.6    | Horizontal Blanking                                                                                  |

|   |     | 7.6.7    | Horizontal Masking Toggle                                                                            |

|   |     | 7.6.8    | Horizontal Masking                                                                                   |

|   |     | 7.6.9    | Vertical coarse clock generation                                                                     |

|   |     | 7.6.10   | Vertical Blanking                                                                                    |

|   |     | 7.6.11   | Vertical Masking                                                                                     |

| 8 | Con | clusio | n And Future Work                    | 76 |

|---|-----|--------|--------------------------------------|----|

|   | 7.7 | Functi | onal coverage results                | 75 |

|   |     | 7.6.15 | Summary of code coverage results     | 74 |

|   |     | 7.6.14 | CLPOB signal generation              | 73 |

|   |     | 7.6.13 | Exposure clock generation            | 73 |

|   |     | 7.6.12 | Line and frame Sync pulse generation | 73 |

# List of Figures

| 2.1  | Basic structure of CCD[4]                                          | 4  |

|------|--------------------------------------------------------------------|----|

| 2.2  | System level architecture of CCD based satellite imaging system    | 5  |

| 2.3  | CCD Array Architectures [7]                                        | 6  |

| 2.4  | CLPOB and PBLK placement[9]                                        | 9  |

| 2.5  | CLPOB masking[9]                                                   | 9  |

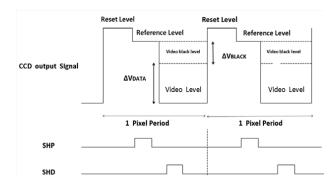

| 2.6  | CCD signal Double correlation sampling                             | 9  |

| 3.1  | Block diagram of PLL                                               | 13 |

| 3.2  | PLL in lock (N=2 in this case)                                     | 13 |

| 3.3  | precision delay control with PLL clock                             | 13 |

| 3.4  | Inverter based coarse delay line[10]                               | 15 |

| 3.5  | NAND based coarse delay line[10]                                   | 15 |

| 3.6  | MUX based Delay line $[10]$                                        | 15 |

| 3.7  | Typical digital controlled fine delay line[10]                     | 16 |

| 3.8  | Thermometric/logarithmic digital controlled fine delay line $[10]$ | 16 |

| 3.9  | Analog DLL                                                         | 17 |

| 3.10 | XOR based $PD[12]$                                                 | 18 |

| 3.11 | D-Flipflop based $PD[12]$                                          | 18 |

| 3.12 | Basic charge pump structure $[12]$                                 | 18 |

| 3.13 | Single ended voltage controlled delay line cell                    | 19 |

| 3.14 | differential implementation of a VCDL delay line $cell[12]$        | 20 |

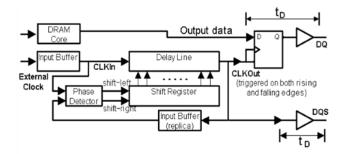

| 3.15 | Digital $DLL[12]$                                                  | 21 |

| 3.16 | Block diagram of RDLL[13]                                          | 23 |

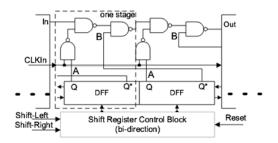

| 3.17 | Delay element in RDLL[13]                                          | 23 |

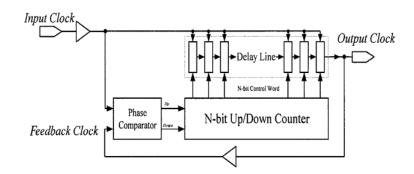

| 3.18 | Block Diagram of CDLL[14]                                          | 24 |

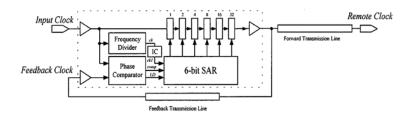

| 3.19 | Block Diagram of SAR DLL[14]                                       | 24 |

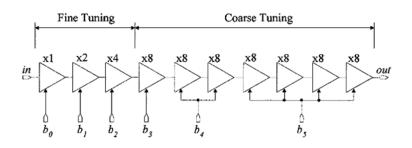

| 3.20 | Binary weighted delay line in SAR- DLL[14]                         | 25 |

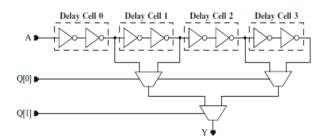

| 3.21 | An edge programmable timing signal generator                       | 26 |

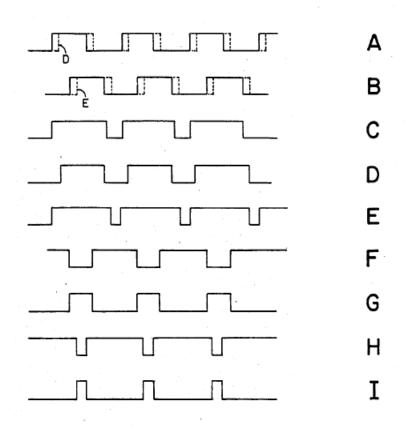

| 3.22 | Programmable Pulse generator waveforms[16]                         | 27 |

| 5.1  |                                                                    | 33 |

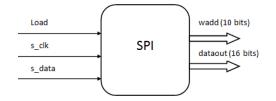

| 5.2  | Block diagram of SPI                                               | 34 |

| 5.3        | Timing diagram of SPI                                                                                                                     | 34  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----|

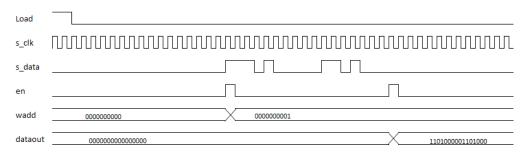

| 5.4        | Block diagram of configuration memory                                                                                                     | 35  |

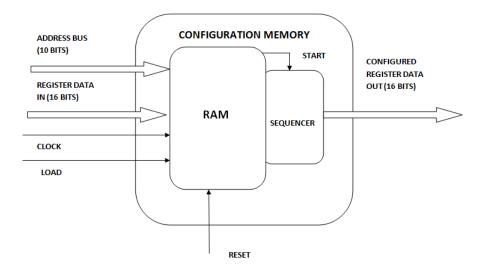

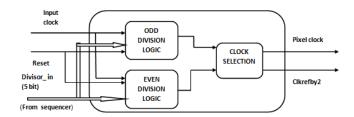

| 5.5        | Block diagram of clock divider                                                                                                            | 36  |

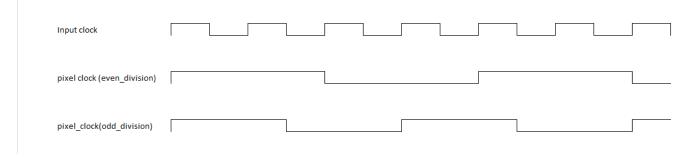

| 5.6        | Timing diagram for clock divider                                                                                                          | 36  |

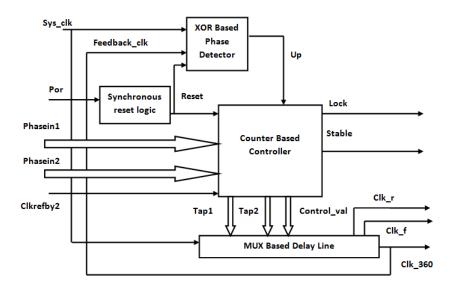

| 5.7        | Block Diagram of DLL                                                                                                                      | 37  |

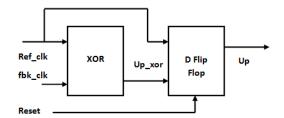

| 5.8        | Block diagram of Phase detector                                                                                                           | 38  |

| 5.9        | Timing diagran of Phase detector                                                                                                          | 38  |

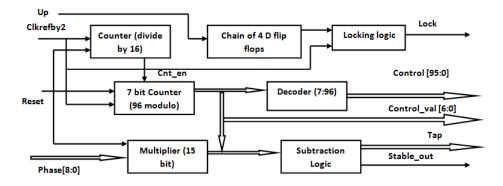

| 5.10       | Block diagram of Counter based controller                                                                                                 | 39  |

| 5.11       | Block diagram of MUX based delay line                                                                                                     | 39  |

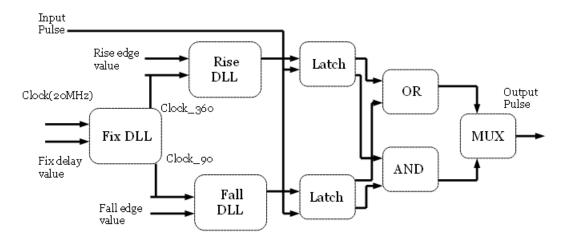

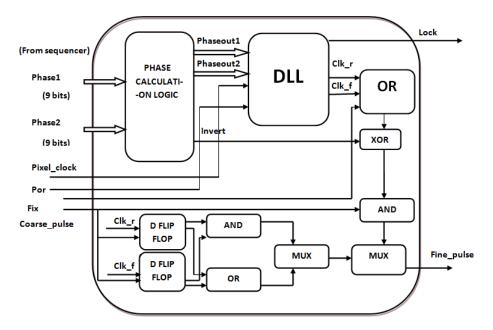

| 5.12       | Block diagram of fine clock pulse generator                                                                                               | 40  |

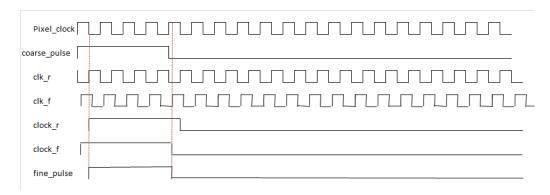

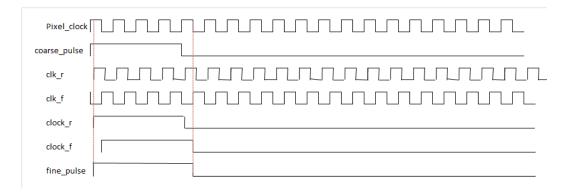

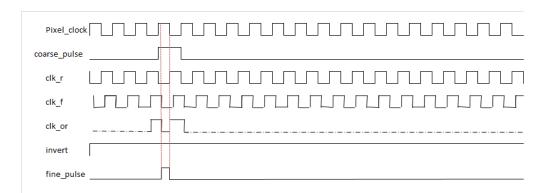

| 5.13       | Timing diagram for case 1                                                                                                                 | 40  |

| 5.14       | Timing diagram for case $2 \ldots \ldots$      | 41  |

| 5.15       | Timing diagram for case 3                                                                                                                 | 41  |

| 5.16       | Timing diagram for case 4                                                                                                                 | 41  |

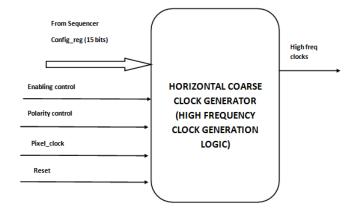

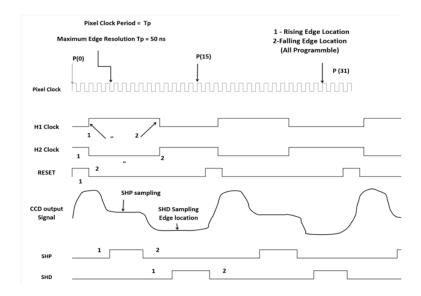

| 5.17       | Block diagram of horizontal coarse clock generator                                                                                        | 42  |

| 5.18       | Timing diagram for high frequency clock                                                                                                   | 42  |

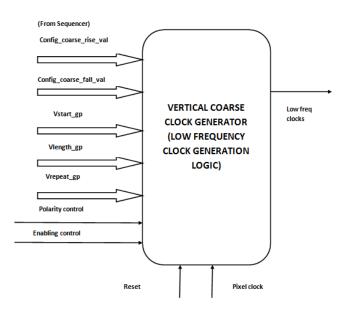

| 5.19       | Block diagram of Vertical coarse clock generator                                                                                          | 43  |

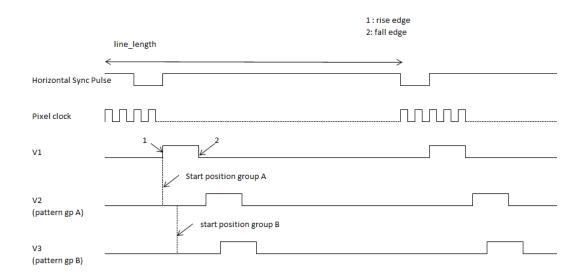

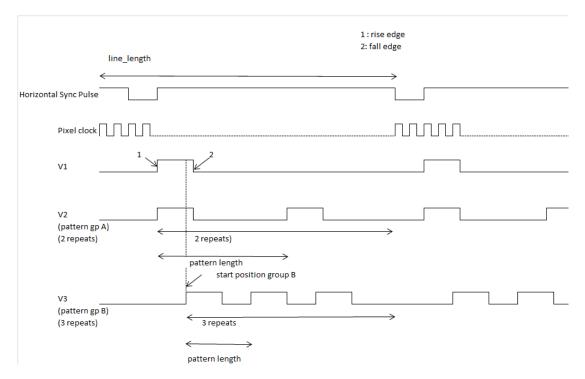

| 5.20       | timing diagram for vertical pattern group                                                                                                 | 44  |

| 5.21       | timing diagram for vertical pattern group                                                                                                 | 45  |

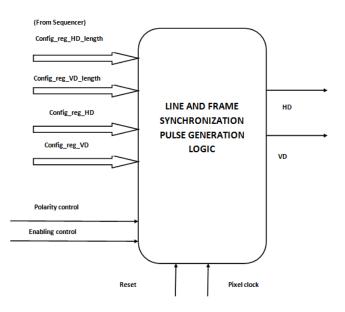

| 5.22       | Block diagram of line frame Synchronization pulse                                                                                         | 45  |

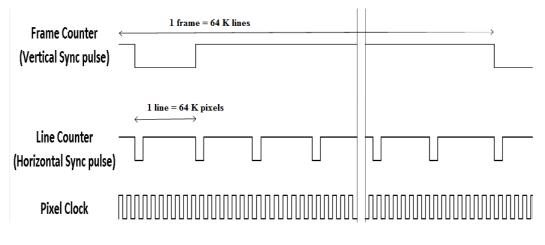

| 5.23       | Timing diagram of line frame Synchronization pulse                                                                                        | 46  |

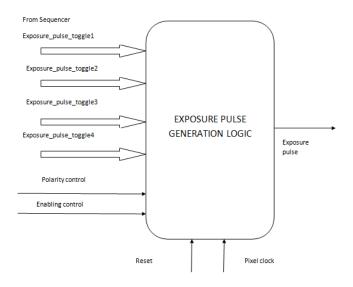

| 5.24       | Block diagram of exposure clock generation                                                                                                | 46  |

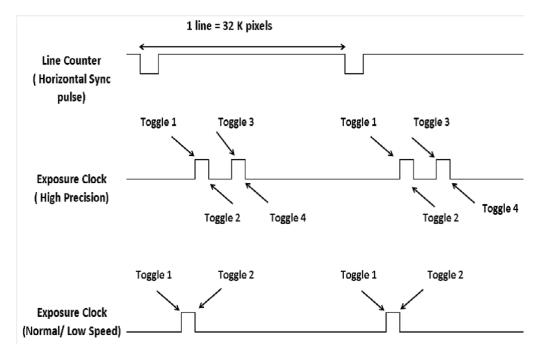

| 5.25       | Timing diagram for exposure clock generation                                                                                              | 47  |

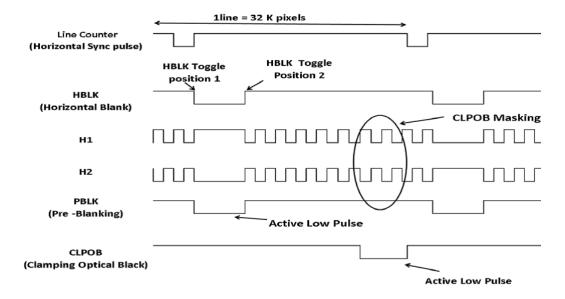

| 5.26       | Timing diagram for Masking                                                                                                                | 47  |

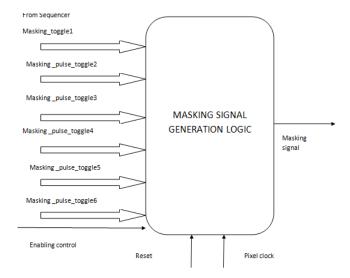

| 5.27       | Block diagram of Masking signal generation                                                                                                | 48  |

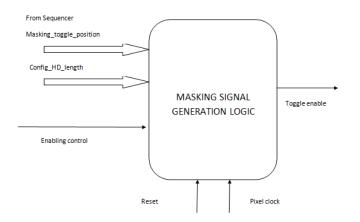

| 5.28       | Block diagram of Masking toggle generation                                                                                                | 48  |

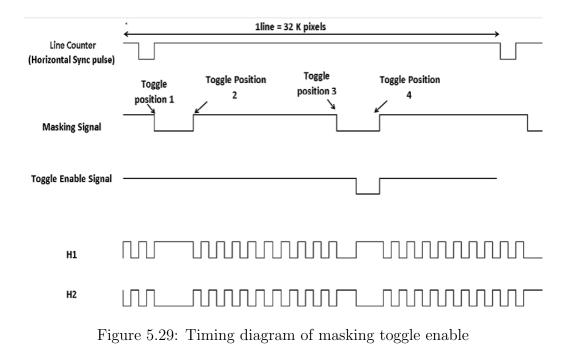

| 5.29       | Timing diagram of masking toggle enable                                                                                                   | 49  |

| 0.1        |                                                                                                                                           | 50  |

| 6.1        | linearity of delay line                                                                                                                   | 52  |

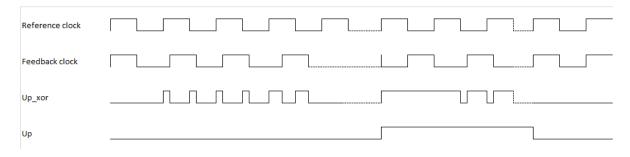

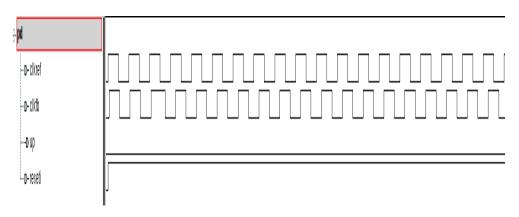

| 6.2        | Phase detector when phase difference less than $180^{\circ}$                                                                              | 52  |

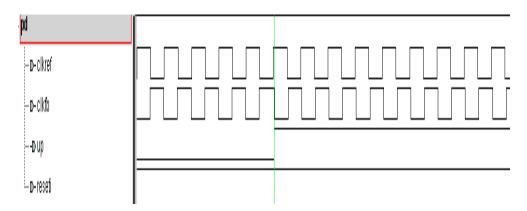

| 6.3        | Phase detector when phase difference equal to $180^{\circ}$                                                                               | 53  |

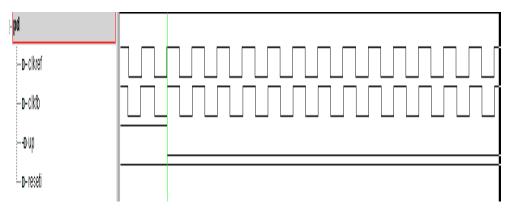

| 6.4        | Phase detector when phase difference equal to $360^{\circ}$                                                                               | 53  |

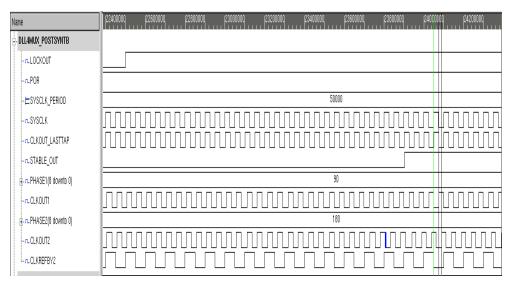

| 6.5        | DLL                                                                                                                                       | 53  |

| 6.6        | Clock pulse with pulse width greater than pixel clock period and phase2 -                                                                 | F 4 |

| a <b>-</b> | $phase1 > 180^{\circ} \dots \dots$  | 54  |

| 6.7        | Clock pulse with pulse width greater than pixel clock period and phase2 -                                                                 | ۲.4 |

| <b>C</b> O | $phase 1 < 180^{\circ} \dots \dots$ | 54  |

| 6.8        | Clock pulse with pulse width greater than pixel clock period and phase1 -                                                                 | ~ ~ |

|            | $phase 2 > 180^{\circ} \dots \dots$ | 55  |

| 6.9  | Clock pulse with pulse width greater than pixel clock period and phase1 -                                                                 |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | $phase 2 < 180^{\circ} \dots \dots$ | 55 |

| 6.10 | Clock pulse with pulse width less than pixel clock period and phase difference                                                            |    |

|      | less than $180^{\circ}$                                                                                                                   | 56 |

| 6.11 | Clock pulse with pulse width less than pixel clock period and phase difference                                                            |    |

|      | greater than $180^{\circ}$                                                                                                                | 56 |

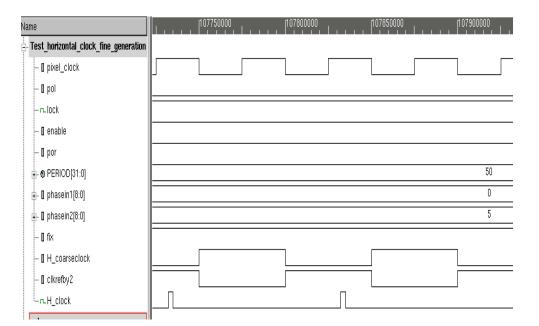

| 6.12 | Horizontal clock                                                                                                                          | 57 |

| 6.13 | Vertical clock sequence                                                                                                                   | 57 |

| 6.14 | Line and Frame synchronization pulses                                                                                                     | 58 |

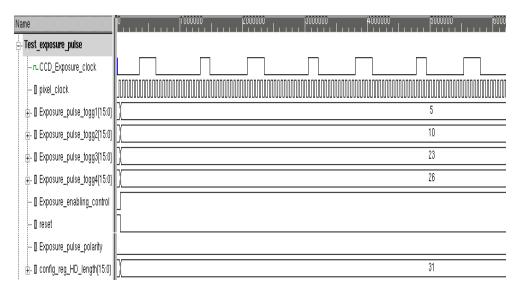

| 6.15 | Exposure clock pulses                                                                                                                     | 58 |

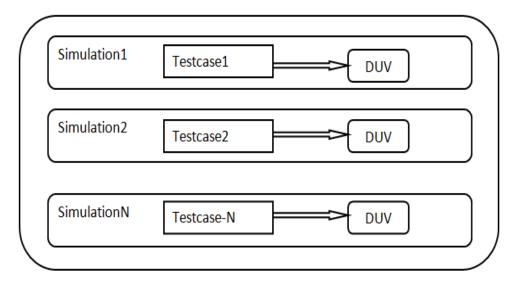

| 7.1  | Directed Verification Approach                                                                                                            | 59 |

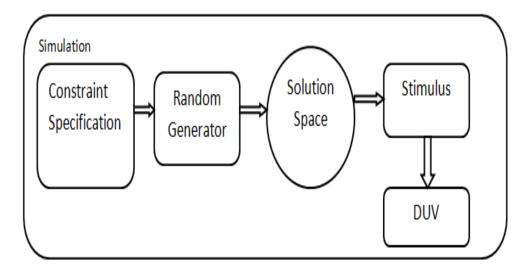

| 7.2  | Constrained Random Verification Approach                                                                                                  | 60 |

| 7.3  | Basic Architecture of Constrained Random Verification Environment                                                                         | 60 |

| 7.4  | Verification Environment for Timing Generator                                                                                             | 62 |

# List of Tables

| 2.1  | Summary of Clock requiremnts for CCD array architectures      | 7  |

|------|---------------------------------------------------------------|----|

| 3.1  | Summary of PLL, Delay line and DLL                            | 21 |

| 6.1  | Operating conditions                                          | 50 |

| 6.2  | STA results of Horizontal coarse clock generator              | 50 |

| 6.3  | STA results of Horizontal and vertical fine clock generator   | 50 |

| 6.4  | STA results of Horizontal and Vertical blanking               | 51 |

| 6.5  | STA results of Vertical coarse clock generator.               | 51 |

| 6.6  | STA results of DLL.                                           | 51 |

| 6.7  | STA results of Line and frame synchronization pulse generator | 51 |

| 6.8  | STA results of Exposure clock generator                       | 52 |

| 7.1  | Code coverage for horizontal coarse clock                     | 69 |

| 7.2  | Code coverage for Fine clock generator                        | 69 |

| 7.3  | Code coverage for Delay Lock Loop (DLL)                       | 70 |

| 7.4  | Code coverage for Phase Detector                              | 70 |

| 7.5  | Code coverage for Controller                                  | 70 |

| 7.6  | Code coverage for Horizontal Blanking                         | 71 |

| 7.7  | Code coverage for Horizontal Masking Toggle                   | 71 |

| 7.8  | Code coverage for Horizontal Masking                          | 71 |

| 7.9  | Code coverage for Vertical coarse clock generation            | 72 |

| 7.10 | Code coverage for Vertical Blanking                           | 72 |

| 7.11 | Code coverage for Vertical Masking                            | 72 |

| 7.12 | Code coverage for Line and frame Sync pulse generation        | 73 |

| 7.13 | Code coverage for Exposure clock generation.                  | 73 |

| 7.14 | Code coverage for CLPOB signal generation                     | 73 |

| 7.15 | Summary of code coverage results                              | 74 |

| 7.16 | Summary of Functional coverage results                        | 75 |

# List of Abbreviations

| ADC           | Analog to digital convertor             |

|---------------|-----------------------------------------|

| ADDLL         | All Digital Delay Lock Loop             |

| ADLL          | Analog Delay Lock Loop                  |

| AFE           | Analog front end                        |

| ASIC          | Application specific Integrated circuit |

| CCD           | Charge coupled Device                   |

| CDS           | Correlated double sampling              |

| CLPOB         | Clamping Optical black                  |

| DLL           | Delay Locked Loop                       |

| $\mathbf{FF}$ | Full Frame                              |

| FIL           | Frame Interline                         |

| $\mathrm{FT}$ | Frame Transfer                          |

| HBLK          | Horizontal Blank                        |

| HD            | Horizontal Sync pulse                   |

| IC            | Integrated Circuits                     |

| IL            | Interline                               |

| PBLK          | Pre-Blank                               |

| PD            | Phase Detector                          |

| PLL           | Phase Locked Loop                       |

| SPI           | Serial Peripheral Interface             |

| STA           | Static Timing Analysis                  |

| TDI           | Time delay Integration                  |

| VBLK          | Vertical Blank                          |

| VD            | Vertical Sync pulse                     |

# Chapter 1

# Introduction

Charge Coupled Devices (CCD) work by converting light into a pattern of electronic charge in a silicon chip.CCDs have features like high sensitivity, high linear dynamic range, electronic shuttering capability and low dark current.One of the main unit in a CCD based satellite imaging system is Timing Generator producing various kinds of readout clocks and control signals for various CCD architectures like linear, full frame, interline, TDI, etc. based on the application. In general, CCD camera comprises of high-speed CCD sensor, CCD output signal processing circuits, timing controller, timing generator, timing driver and external optics system. One of the critical requirements of these CCD are accurate clock pulse and sequences which are the main function of Timing generator and Control block.[1][2]

### 1.1 Objective and scope of the project

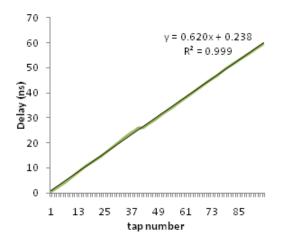

The aim of this project is to carry out front end design of programmable high precision timing generator ASIC which can generate the various driving time and processing time sequences for various CCD architectures. It should also provide the flexibility in terms of effective image area, number of clocks required for a particular CCD along with the precise and programmable delay control for each clock. An All Digital Delay Locked Loop (ADDLL) is used in order to achieve the precise delay control of the order of 620 ps.. A single chip can support various CCD architectures with programmable and precision delay controls for critical clocks.

CCD driving clocks includes horizontal (readout) clocks, vertical clocks (image transfer/transport clocks), storage clocks, stage selection clocks, reset clocks, exposure clocks etc. Processing clocks includes clocks for CDS (correlated double sampling), black pixel clamping, Preblanking clocks, ADC clock etc. to assure the high image quality of CCD camera.

In the Phase-I of this project, block level front-end ASIC design of timing generator is

developed using VHDL. and the pre-synthesis simulation is done by developing the testbenches in verilog(directed test cases). Also the synthesis, Static timing analysis and post synthesis simulation of a Delay locked Loop (DLL), a critical block for precise timing generation is carried out., Synopsys tools are used for design and analysis. The design is targeted with 180nm technology. In Phase-II of the project, the synthesis of remaining design blocks is carried out and analyzed for timing requirements (STA). Also SPI is developed for serial writing into memory. Assertion based and coverage driven constrained random verification of whole design is carried out using system verilog.

#### **1.2** Organization of Thesis

The thesis is organized with Chapter 1 providing the introduction. Chapter 2 describes about CCD fundamentals and introduction to CCD based satellite imaging system which is part of literature survey. It provides basics of CCD operation, CCD structures, charge storage and transfer operation, clock requirements in processing blocks and some details about image data acquiring and processing system.

Chapter 3 discusses about different methodologies to obtain the precise delay control like PLL, delay lines and DLL along with the methods for generating pulses with different pulse width control.

Chapter 4 discusses design requirements and specifications including overall clock requirements which support all architectures, readout features for detector clocks, methods for generating programmble clocks, design specification and parameters with different clock categories.

Chapter 5 is about detailed design of timing generator, starts with proposed architecture for timing generator which contains proposed architecture with details description of identified blocks of design. This description includes block level information and functional description for each block in detail.

Chapter 6 discusses about simulation and synthesis results. The design blocks are synthesized and STA is done. The post synthesis simulation results are shown for various sub blocks of the design.

Chapter 7 is about verification of whole design. The verification environment is developed and various testcases are given randomly with constraints to achieve desirable coverage.

Chapter 8 is about the conclusion and future work of timing generator design.

# Chapter 2

# Introduction to CCD Fundamentals

### 2.1 Introduction to CCD

CCD (Charge Coupled Devices) detectors are widely used for imaging applications found in space and astronomy.CCDs detect a faint amount of light, convert light into pattern of electronic charge in a silicon chip and produce high resolution images.The CCD is a discrete-time device, i.e., analog signal such as light intensity is sampled at discrete times.The memory function comes by shifting these charges, simultaneously, down a row of cells, also in discrete time.[3] CCD can be used as analog memory. Applications include voice storage as in a telephone answering machine.

The more important and universally recognized applications of CCD are seen in image sensors. As an image sensor a CCD has an array of cells to capture a light image by the photo-electric effect. The packets of charge are not initially converted to an electrical signal, but rather moved from cell to cell by the coupling and decoupling of potential wells within the semiconductor that makes up the CCD. At the end of the line the charges, from all the different picture elements (pixels), can be converted to electrical signals. The idea here is to have a large number (may be millions) of sensing cells in order to achieve good resolution, but a small number (may be one) of readout cells for practicality.[4] [5]

#### 2.1.1 Structure of CCD

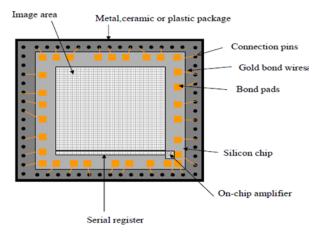

The basic structure of CCD is shown in the figure 2.1. It consists of an image area (a square array of pixels) of the CCD. An image then builds up that consists of a pattern of electric charge. At the end of the exposure this pattern is then transferred, pixel at a time, by way of the serial register to the on-chip amplifier. Electrical connections are made to the outside world via a series of bond pads and thin gold wires positioned around the chip periphery.

Figure 2.1: Basic structure of CCD[4]

#### 2.1.2 Steps of CCD imaging Operation

CCD imaging is performed in a three step process:

(1) Charge collection in a CCD

Exposure converts light into an electronic charge at discrete sites called pixels.Photons entering the CCD create electron-hole pairs. The electrons are then attracted towards the most positive potential in the device where they create 'charge packets'. Each packet corresponds to a pixel.

(2) Charge transfer which moves the packets of charge within the silicon substrate

Once charge has been integrated and held locally by the bounds of the pixel architecture, there should be some means of getting that charge to the sense amplifier which is physically separated from the pixels. The common methods used involve differing charge transfer techniques like techniques for four phase  $(4\phi)$  CCD, three phase  $(3\phi)$  CCD, pseudo two phase  $(P2\phi)$  CCD, true two phase  $(T2\phi)$  CCD[6].

(3) Charge to voltage conversion and output amplification [4] [5]

The packets of charge are eventually shifted to the output sense node where the electrons (which represent a charge) are converted to a voltage that is easier to work with off chip. Conventional techniques usually employ a floating diffusion sense node followed by a charge to voltage amplifier such as a source follower.[6]

#### 2.2 CCD based Satellite imaging System

High speed CCD camera systems are better choice for high-end real time visible imaging systems. All CCD based applications are completely dependent on the architecture of CCD detectors, their operation and processing of their output signals. The timing generator part of the CCD camera critically determines its performance. The working of CCD sensor depends on driving sequences which assure CCD with high transfer efficiency, high signal-to-noise ratio and credible CCD output signal while accurate CCD signal processing sequences ensures high quality of CCD image.[1][2]

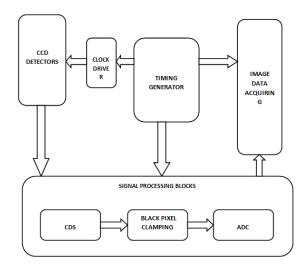

Figure 2.4 shows Timing Generator along with other system interfaces for any CCD based satellite imaging system. Complete system is divided into five blocks: CCD detector, Timing Generator, clock drivers, CCD output signal processing blocks and image data acquiring system.

Primarily Timing Generator generates clocks and sequences for two blocks i.e. CCD detector and CCD output signal processing. These clocks are required for image transfer, readout, exposure, reset, shuttering etc. The CCD output is processed by signal processing blocks which contain digitizer, CDS circuitry, black level clamp etc. Clocks required for signal processing block are CDS clocks, blanking/clamping pulses for pre-blanking as well as clamping the optical black region and latching clocks. The digitized pixel information is sent to the digital image processor chip, which performs the post processing which forms part of image data acquiring system. For synchronization between various blocks, additional clocks are required which is generated in timing generator block. Each of these blocks are explained below in detail.

Figure 2.2: System level architecture of CCD based satellite imaging system

### 2.3 CCD Detector Array Architectures

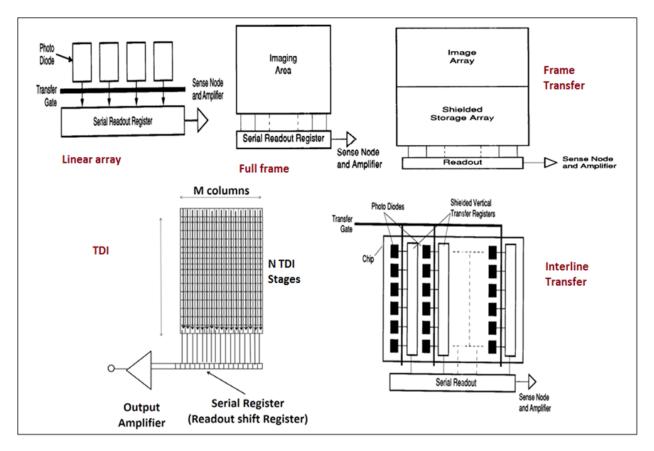

CCD array architectures are driven by the application. These array architectures can be categorized into various types:[7]

Linear arrays, Time delay and integration (TDI), Full frame, Frame transfer and Interline transfer devices are used for various industrial applications, scientific applications, consumer camcorders and professional television systems. Table 2.1 summarizes about clock requirements for these detector architectures.

Figure 2.3: CCD Array Architectures[7]

| Type of              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Clocks Required                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CCD                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CIOCKS Required                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Linear array         | <ul> <li>As shown in the figure 2.3 located next to each sensor is the transfer gate followed by CCD shift register.</li> <li>A variant of this is bilinear array. For a fixed pixel size, the bilinear readout increases the effective charge transfer effciency as the number of transfers is reduced by a factor of 2.</li> <li>Linear CCDs are used for fast operation and high resolution.</li> </ul>                                                                                                                                                                                                                                                    | <ul> <li>Transfer gate clock<br/>pulse to move the<br/>charge from<br/>photodiode into CCD<br/>transfer register.</li> <li>Clock pulse for serial<br/>readout operation.</li> <li>Reset gating clock<br/>when the charge is<br/>transferred from output<br/>register to amplifier.[7]</li> </ul>                                                                                                                                                                 |

| Full Frame<br>Arrays | <ul> <li>Here, after the integration, the image pixels are read out line by line through a serial register which then clocks its contents onto the output sense node.</li> <li>All charge must be clocked out of the serial register before the next line can be transferred. An electronic shutter can be used to shield the array during read out to avoid smear.</li> <li>The effective readout rate can be increased by factor of N, if N sub arrays are read out simultaneously. There is a tradeoff between the frame rate and image size.</li> <li>The full frame design is used for CCD imagers with higher resolution and higher density.</li> </ul> | <ul> <li>Exposure clocks which<br/>pulses the CCD<br/>substrate to clear out<br/>accumulated charge<br/>for electronic<br/>shuttering.</li> <li>Horizontal clocks<br/>for pixel read out<br/>operation</li> </ul>                                                                                                                                                                                                                                                |

| Frame<br>Transfer    | <ul> <li>A frame transfer imager consists of two identical arrays as shown in figure 2.3, one devoted to image pixels and one for the storage.</li> <li>After the integration cycle, charge is quickly transferred from light sensitive pixels to storage cells and readout off chip is carried out simultaneously when storage array is integrating the next frame.</li> <li>Continuous or shutter less operation is achieved resulting in faster frame rates than full frame device.</li> <li>Lower resolution and higher cost than full frame architecture.</li> </ul>                                                                                     | <ul> <li>Exposure clocks for<br/>electronic shuttering</li> <li>Horizontal clocks for<br/>pixel read out<br/>operation</li> <li>Vertical clocks for<br/>shifting each line of<br/>pixels into serial<br/>readout register</li> <li>Reset clocks for reset<br/>gating when charge is<br/>transferred from output<br/>register to amplifier</li> <li>Storage clocks for<br/>transferring each line<br/>of pixel from image<br/>area to storage area.[7]</li> </ul> |

| Table 2.1 Summary | of Clock requirements for | CCD array architectures[7] |

|-------------------|---------------------------|----------------------------|

|                   | 1                         |                            |

| linte ultra                        | The interior                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interline<br>Transfer              | <ul> <li>The interline array consists of photodiodes separated by vertical transfer registers (which are covered by an opaque metal shield). The signal charge produced is transferred to vertical shift register through transfer gate.</li> <li>The main advantage is that transfer from active sensors to shielded storage area is quick as charge transfer is performed simultaneously for all pixels.</li> <li>To solve the problem of smear, the signal charge is transferred to storage section at high speed.</li> </ul>                                                                                                                                                         | <ul> <li>Exposure clocks for<br/>electronic shuttering</li> <li>Horizontal clocks for<br/>pixel read out<br/>operation</li> <li>Vertical clocks for<br/>shifting each line of<br/>pixels into serial<br/>readout register</li> <li>Reset clocks for reset<br/>gating when charge is<br/>transferred from output<br/>register to amplifier</li> <li>Storage clocks for<br/>transferring each line<br/>of pixel from image<br/>area to storage area.[7]</li> <li>Vertical sensor gate<br/>pulses to transfer pixel<br/>charges from light<br/>sensitive area to<br/>vertical registers</li> </ul>             |

| Time Delay<br>Integration<br>(TDI) | <ul> <li>TDI, shown in figure 2.3, is a specialized detector readout mode used for observing a high-speed moving object under low light conditions normally undetectable by classic CCD imaging.</li> <li>TDI is designed to allow continuous movement of the object past the sensor to produce a continuous video image of a moving, two-dimensional object: a definite advantage over stop-then-start capture.</li> <li>The number of lines on the sensor corresponds to the increase in sensitivity than a single line scan camera.</li> <li>It provides exposure control by controlling the number of stages. This is generally achieved by turning off selection clocks.</li> </ul> | <ul> <li>Horizontal clocks for pixel read out operation</li> <li>Vertical clocks for shifting each line of pixels into serial readout register</li> <li>Reset clocks for reset gating when charge is transferred from output register to amplifier</li> <li>Vertical transfer clock pulses are used to transfer pixel charges from light sensitive area to vertical registers</li> <li>TDI stage selection clock for selecting the number of stages for exposure and the last stage of each register has a separate clock to speed up the signal transfer and reduce the video settling time.[7]</li> </ul> |

### 2.4 CCD Signal Processing Blocks

CCD Analog Front-end (AFE )clocks or Processing blocks include double correlation samplings (CDS) circuitry, black pixels clamp and ADC to assure the high image quality of CCD camera, which is sent to image acquiring system after digitization.

These clocks and pulses include CDS (Correlated Double Sampling) Clocks, Blanking/Clamping clocks and clocks for optical black region (CLPOB) which can reduce noise and sample true image data, Pre-blanking pulses (PBLK) for pre-scan pixel removal and ADC clocks which samples the true video signal and further sent to image data acquiring system. All these clocks and sequences are high frequency clocks.

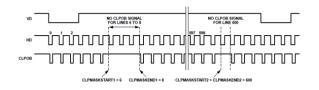

The timing diagram for CLPOB and PBLK clock pulses are shown in figure 2.4 and figure 2.5 respectively. Here HD and VD are horizontal and vertical synchronizing pulse respectively.

Figure 2.4: CLPOB and PBLK placement[9]

Figure 2.5: CLPOB masking[9]

Figure 2.6: CCD signal Double correlation sampling

This CDS technology is not only the important mean to restraint CCD camera noise but

also an important part of the video signal processing. The changes based on the reset noise and the reference level can be restrained by characteristics of correlation. The reset noise from the reset gate pulse will be neglected when CDS technology is used. CDS can also restraint the 1/f noise of the source follower.

The CDS circuit samples each CCD pixel twice to extract the video information and reject low frequency noise. Figure 2.6 illustrates how two CDS clocks, SHP and SHD, are used to sample the reference level (floating gate level) and data level (video level) of the CCD signal respectively. The reference level corresponds to the zero photo electrons. But the video level is not the actual signal level we required; it includes the video black level. If we only use these two levels we would not get the true signal or image data which represent the incident photons. The CCD has the black reference pixel or lines which show the video black level. The Black clamp clocks inform the processing circuit the positions of CCD black pixels or lines. So the CDS circuit gets the video black level and floating gate level. Then the black pixel signal, VBLACK and the true image data, VDATA are attained in succession. The value of VDATA is digitized by the analog-to-digital circuit. The A/D clocks should be synchronous with CCD video signal. For digital image processing and data acquiring, three synchronous clocks (pixel, line and frame) are necessary. [2][8]

## 2.5 Timing Generator

Timing generator is the critical block of a satellite imaging system. It provides various clocks to all other blocks. Most importantly it generates various timing sequences like exposure clocks, vertical (image transfer) clocks, Horizontal (readout) clocks, reset clocks, storage clocks etc for driving the given CCD architecture and processing timing sequences like CDS sampling clocks, latching clocks for digitizer and clamping clocks for clamping circuitry. Apart from these, it also generates some synchronization pulses (line and frame synchronization) for image acquiring system for post-processing and compression.

This Thesis discusses about design of precision timing generator which can support various CCD detector architectures. The aim is to provide different types of clocks with different readout features like rising/falling edge programmability with the precise delay control, polarity control, enabling control, masking, toggle positions, patterns, sequence and repeats pattern groups, etc. This Design also supports flexible image area for CCDs. Following Chapters show details about its design architecture and various features.

## 2.6 Image data acquiring and processing systems

CCD detector output signal processed and digitized by signal processing block. All processed image information is sent to image data acquiring and processing systems. This system can have different sub-blocks based on requirements. In general, this block can have digital image processing ASIC, image compression circuits, encoders and other image acquiring systems. This section performs different operations like image compression, final output image, image data acquisition and other processing.

# 2.7 Summary

This chapter gives basic idea about CCD architectures ,its working and also about system level blocks for CCD based satellite imaging system.Following section provides detail of Timing Generator block.

# Chapter 3

# **Precision Timing Generation**

Different types of CCD architectures and signal processing blocks require various types of clocks as described in the previous chapter. One of the important feature required in these horizontal and vertical clocks is the precise delay control. Typically delay control is achieved by using different phases of clock. In order to obtain this precise delay control following circuits can be used:

- 1. Phase Locked Loop (PLL)

- 2. Delay line

- 3. Delay locked loop (DLL)

## 3.1 Phase Locked Loop (PLL)

PLLs are used for clock synthesis and hence can be used to generate different phases from a clock.

A Phase-Locked Loop (PLL) is a feedback system that causes an output signal to track a reference signal in phase and frequency. When both the frequency and phase of these signals are synchronized, the PLL is said to be in the locked condition. The phase difference between the output and reference is a known value when the loop is locked. PLLs are found in a wide range of applications, including clock recovery, noise and jitter suppression in communications, clock synchronization in memory interface and high-performance microprocessors, and frequency synthesis for instrumentation and RF transceivers.

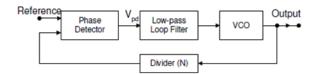

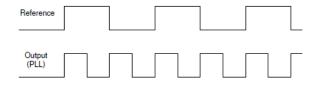

A basic PLL is a negative feedback system that consists of a phase detector, a low-pass loop filter and a voltage-controlled oscillator (VCO), as shown in Figure 3.1 A divide-by-N counter can be added in the feedback path to provide a frequency synthesis function. Figure 3.2 shows the waveform of a reference signal and PLL output when the loop is in lock (using a divide-by-2 in the feedback path). The frequency of the PLL output signal is twice the reference with zero-phase difference (assuming N=2).

Figure 3.1: Block diagram of PLL

The basic operations of a PLL can be divided into three steps: First, the phase detector (PD) matches the phase difference between two inputs and generates an error signal  $V_{Pd}$  whose average value is linearly proportional to the phase difference. A Loop filter (LF)(which is a first order system) is then used to suppress the high-frequency components of the PD output, allowing the average value (DC or low-frequency) to control the VCO frequency. Finally, an oscillator generates an output signal whose frequency is a linear function of the control signal out of the LF. The generated signal is fed back to the input of the PD and another phase comparison is started until the phase difference achieves a fixed relationship.

Figure 3.2: PLL in lock (N=2 in this case)

Figure 3.3: precision delay control with PLL clock

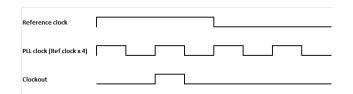

Figure 3.3 shows how PLL can be used to generate clocks with multiple and programmable phase shift. Here ,for example to obtain 4 edge placement within the reference clock period, a divider N=4 is required such that PLL output clock frequency is (4 x Reference clock). So if frequency of reference clock is 20 MHz, frequency of PLL output is (4 x 20) 80 MHz and the phase resolution changes from 50 ns to 12.5 ns and a precise delay control can be achieved.

#### 3.2 Delay line

In PLL based approach frequency multiplication is carried to generate different clock phases out. Another way to obtain precise delays is to use a Delay Line.

Digital delay lines are classified into two types:[10]

- 1. Coarse delay line also referred to as Gate delay DCDL

- 2. Fine delay line also referred to as Sub gate-delay DCDL.

There are various number of delay line structures that are employed or that have been proposed for different applications. The following section briefly discusses few of the commonly used DCDL structures.

#### 3.2.1 Coarse Delay Line

The coarse delay lines are composed of CMOS logic gates and are cascaded to form a delay line. The simplest of the delay lines for digital DLL is a chain of cascaded inverters with each stage consisting of a pair of inverters and the required output tap is selected by a multiplexer. The minimum delay of each stage is  $2T_D$  where  $T_D$  is the average CMOS gate delay and requires  $\log_2 N$  storage elements where N is the number of stages. A coarse delay line design is shown in the Figure 3.4. [10]

This implementation has four delay stages between the input and output. If the required number of delay stages is more then it may load the input clock. To overcome the loading, separate buffers must be introduced thus increasing the delay of each cell to more than  $2T_D$ . This increase in delay would depend on the amount of added buffering.

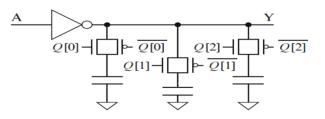

A work-around to this problem is shown in Figure 3.5.[10] In this structure, the loading on the input clock is prevented by varying the delay line in a telescopic fashion. Adapting this structure eliminates the need to introduce internal buffering of the clock signal thus maintaining the delay of each stage to  $2T_D$ . A shift register controls the delay of each cell. For example, when Q [0] =1 and Q [3:1] =0 the output clock signal would have a two nand gate delay i.e. the delay of A and B nand gates in cell 0. When Q [1] =1 and the rest of the values are low the output path would be nand gate C in cell 0, nand gate A in cell 1, nand gate B in cell 1, nand gate B in cell 0.[10]

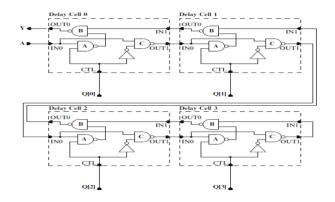

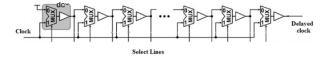

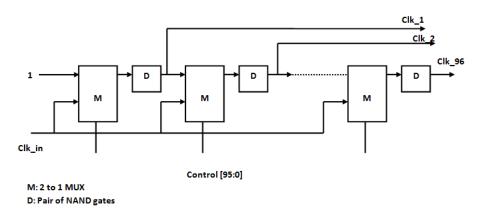

Figure 3.6 shows another implementation of coarse delay line. Here, the delay line consists of multiple delay cells connected in cascade. Each delay cell consists of a multiplexer (MUX) and a buffer. The input1 of the MUX of first delay cell is connected to supply and for all other delay cells the input1 is connected to the output of the previous stage cell. The input2

Figure 3.4: Inverter based coarse delay line[10]

Figure 3.5: NAND based coarse delay line[10]

of all the MUX are connected to clock. The delay line is controlled through the select lines which are the output of the control logic.[10]

Figure 3.6: MUX based Delay line[10]

#### 3.2.2 Fine Delay Line

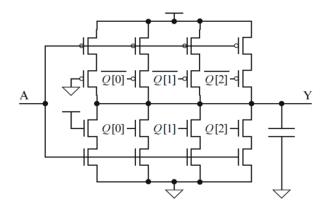

Two designs of the fine delay line, which generate delay by using the RC delay characteristics are shown in Figure 3.7 and Figure 3.8.

The structure in Figure 3.7 relies on varying cell resistance. The branches are controlled by using digital bits Q [2:0] which switch in a fixed specified pattern. The bits can only be thermometrically encoded for this circuit due to poor linearity behavior of the circuit. For increased dynamic range several stages can be cascaded. The greater the number of devices that are ON at a particular time smaller will be the RC delay.[10]

In the second design of the fine delay shown in Figure 3.8, the RC delay increases with the number of ON devices. The digital control bits can be encoded using both thermometric

Figure 3.7: Typical digital controlled fine delay line[10]

and logarithmic codes due to linear characteristics of the circuit. As in former structure the dynamic range increases by cascading several stages

Figure 3.8: Thermometric/logarithmic digital controlled fine delay line [10]

In case of coarse delay line the delay resolution obtained is in several hundreds of ps whereas in case of fine delay line the delay resolution is in tens of ps.

Challenges in designing delay line:

1. Every delay element should have equal delay.

2. The resolution of delay line is obtained by the amount of delay that can be achieved with a single delay element.

3. Another important thing is to get a 50 percent duty cycle of the output clock.Here due to the rise and fall time propagation delay differences of different gates, the duty cycle variations may occur.

## 3.3 Delay Locked Loop (DLL)

DLL can be used for a variety of applications which require precise time intervals. The function of the DLL is to align the input clock and delayed clock through phase detector (PD). Once this is done multiple phases can be derived from various stages of the delay line with each providing a stable clock signal that is a phase shifted version of the input clock.

DLL is a feedback system that aligns the feedback clock to the reference clock. This is done by delaying the input feedback clock after passing it through a delay line and controlling the delay using the control mechanism. Once the input feedback clock is delayed, a phase detector (PD) compares the phases of the two inputs. Based on PD output value, the delay is adjusted (increased or decreased) until the two phases are aligned.

A DLL is able to provide multiple clock signals which are separated from each other by a well-controlled phase shift (delay). This application of DLL is utilized in obtaining high precision clocks required for timing generators.

Generally a phase detector, delay line and a charge pump or counter make up a DLL.DLL can be either primarily analog or digital depending on the design components.

#### 3.3.1 Analog DLL

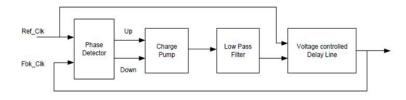

Analog DLLs (ADLL) were first used in clock distribution applications. The components of a conventional Analog DLL are, phase detector, charge pump, low pass filter and voltage controlled delay line as shown in Figure 3.9.[11]

Figure 3.9: Analog DLL

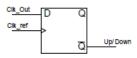

A phase detector compares two input signals and generates "UP" and "DN" output pulses that represent the direction and magnitude of the input phase error.Considering simple type of phase detectors such as the phase-frequency detectors are those which are only rising and falling edge sensitive. They produce a single pulse at the UP or DN output for each pair of input reference and feedback edges depending on which edge arrives first.

Some of the simple PD architectures are shown below. An XOR based PD is shown in figure 3.10. Once the difference is detected this information is passed on to the charge pump for further action where the magnitude of PD output is proportional to the phase difference between inputs. This kind of PD, however suffers from several limitations:

- 1. Any variation in the input duty cycle may cause this PD to generate wrong phase information.

- 2. Since this PD has a single output it complicates the design of subsequent blocks namely charge pump.

A much superior PD is based on flip flops as it can detect edges irrelative of the input signal's duty cycle. This type of PD can be used for frequency detection along with phase but the setup time may become a limiting factor in achieving good performance results. If the setup and hold times are not symmetric this may introduce a regular phase error as lagging and leading decisions based on the hold and setup times, respectively. This type of PD has been proposed in [12] and is shown in Figure 3.11.

Figure 3.10: XOR based PD[12]

Figure 3.11: D-Flipflop based PD[12]

A charge pump, connected to the phase detector, sources or sinks current for the duration of the UP and DN pulses from the phase detector. The net output charge is proportional to the difference between the pulse widths of the UP and DN outputs. The charge pump drives the loop filter which integrates and filters the charge current to produce the control voltage.

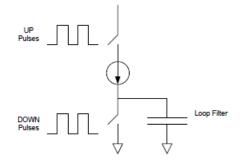

Figure 3.12 shows a general structure of a charge pump: it consists of a couple of controlled switches being controlled by the up/down signals from the PD and a couple of current sources where one is a current source and the other is a sink. Depending on the position of the switch, loop filter is either charged or discharged. This process continues until the DLL is locked, after that charge over loop filter remains unchanged.[12]

Figure 3.12: Basic charge pump structure [12]

A charge pump based on this working principle has certain limitations: Due to mismatches

between the charging and discharging currents may occur in jitter particularly once the DLL is locked. The non ideal behavior of switches may also introduce jitter in the signal. The most critical component in the performance of a DLL is a VCDL which directly influence DLL jitter performance and stability. The control Voltage drives a voltage-controlled delay line (VCDL) in a DLL which generates a delay proportional to the control voltage.

Ideally, the delay generated by each stage is equal to  $T_{ref}/n$  where  $T_{ref}$  is the time period of the input clock and n is the number of delay stages in a VCDL. Theoretically there is no limit to the number of delay stages in a VCDL but there are some practical constraints. It is to be noted here that the delay may not necessarily be an inverter. Both single ended and differential structures have been implemented where the differential structures having better common mode noise rejection characteristics.

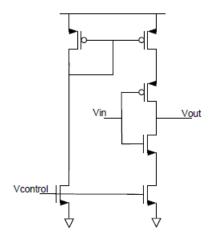

An example of single ended delay cells based on current starved inverters is shown in Figure 3.13. Current changes with Vcontrol, thus changing the driving capability of the delay stage.

Figure 3.13: Single ended voltage controlled delay line cell

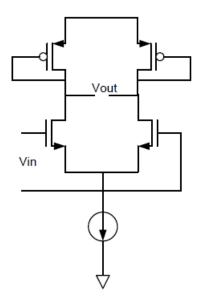

Figure 3.14 shows a differential implementation of a VCDL delay line cell as discussed in [12]. The resistance of the diode connected structure would be:

$$\mathbf{r}_{out} = \frac{1}{g_{out}} + \frac{1}{r_n} + \frac{1}{r_p}$$

where  $g_m$  is pmos load's transconductance, while  $r_p$  and  $r_n$  are the output resistances of pmos and nmos transistors. The transconductance can be expressed as

$$g_m = \sqrt{\mu_p} C_{ox} \frac{W}{L} I_{ss}$$

where  $I_{ss}$  is the tail source current. Substituting this value of gm to the above equation rout can be written as

$$\mathbf{r}_{out} = \frac{1}{g_n}$$

The delay of each stage is proportional to the RC constant and can be expressed as

$$t_d = \sqrt{2}r_{out} C_{out}$$

where  $C_{out}$  is the output capacitance at each node. It can be seen from this expression that the time delay  $t_d$  can be directly controlled by controlling  $I_{ss}$ .

Figure 3.14: differential implementation of a VCDL delay line cell[12]

Important points:

1. An Analog DLL is a complex analog circuit requiring process-specific implementation.

2. An Analog DLL generally provides better jitter performance at the expense of greater complexity.

3. Scaling of analog integrated circuits directly affects output resistance and intrinsic gain of the circuit. This results in higher power consumption and enhanced design complexity.

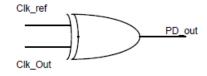

#### 3.3.2 Digital DLL

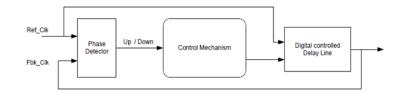

Digital DLLs (ADDLL) are characterized by their use of digitally controlled delay line. They are typically made of digital circuit elements. Figure 3.15 shows a conventional Digital DLL.Here there is a Phase Detector which compares the phase of reference and feedback clocks and generates a single up/down signal depending on the phase error. To avoid false detection the PD should spend minimum time in metastable state .The setup and hold times must be reasonably small.The setup and hold times should be comparable so as the resulting phase information is not biased. The clock to Q delay should be reasonably small but is usually not a stringent requirement.

Figure 3.15: Digital DLL[12]

Control mechanism (which can be of different types) is used to generate signals in order to control the delay of digitally controlled delay line depending on up/down signal.

The delay line is the most important component of the DLL and has a profound effect on the overall DLL performance. The various types of the Digitally controlled delay lines have already been discussed in previous section.

Important Points:

1. If the clock frequency is f and its period is T,length of a delay line is N delay of a unit delay element is t ,then for delay line to get locked over its entire length T = N \* t resolution = t.

2. Digital DLL has more noise immunity and synthesizable circuit makes it very attractive for clock alignment applications.

A comparison of PLL, Delay line, ADLL and ADDLL is summarized in table 3.1.

| PLL                    | Delay line         | ADLL                   | ADDLL                  |

|------------------------|--------------------|------------------------|------------------------|

| At least a second      | Zero order         | First order            | Zero order             |

| order system           | system             | system (LPF)           | system                 |

| To generate a          | No clock frequency | No clock frequency     | No clock frequency     |

| fractional delay clock | multiplication     | multiplication needed. | multiplication needed. |

| frequency              | needed. Less power | Less power consuming   | Least power            |

| multiplication is      | consuming          |                        | consuming              |

| required. Thus power   |                    |                        |                        |

| consuming.             |                    |                        |                        |

| Susceptible to PVT     | Susceptible to PVT | Less PVT invariant as  | Less PVT invariant as  |

| variations due to non  | variations         | compared to PLL.       | compared to PLL.       |

| linear locking         |                    |                        |                        |

| behavior               |                    |                        |                        |

| VCO is supply and      | Noise immunity is  | Noise immunity better  | Substrate and supply   |

Table 3.1 Summary of PLL, Delay line and DLL [12][17][18]