# DSP BASED CONTROLLER FOR UNITY POWER FACTOR FRONT-END PWM REGENERATIVE CONVERTER

### **Major Project Report**

Submitted in Partial Fulfillment of the Requirements for the Degree of

## MASTER OF TECHNOLOGY IN ELECTRICAL ENGINEERING

### (POWER APPARATUS & SYSTEMS)

By Khanduja Gagandip Singh Narendra Singh (07MEE006)

Department of Electrical Engineering Institute of Technology NIRMA UNIVERSITY OF SCIENCE AND TECHNOLOGY Ahmedabad 382 481 April 2009

#### CERTIFICATE

This is to certify that the Major Project Report entitled "DSP Based Controller for Unity Power Factor Front-End PWM Regenerative Converter" submitted by Mr. Khanduja Gagandip Singh Narendra Singh (07MEE006) towards the partial fulfillment of the requirements for the award of degree in Master of Technology (Electrical Engineering) in the field of Power Apparatus & Systems of Nirma University of Science and Technology is the record of work carried out by him under our supervision and guidance. The work submitted has in our opinion reached a level required for being accepted for examination. The results embodied in this major project work to the best of our knowledge have not been submitted to any other University or Institution for award of any degree or diploma.

Date:

#### Guide

Dr. P. N.Tekwani Professor Department of Electrical Engineering Institute of Technology Nirma University Ahmedabad

Head of Department Department of Electrical Engineering Institute of Technology Nirma University Ahmedabad **Director** Institute of Technology Nirma University Ahmedabad

#### ACKNOWLEDGEMENT

It gives me an immense pleasure in expressing thanks to **Dr. P. N. Tekwani**, Professor, Department of Electrical Engineer, Institute of Technology, Nirma University, Ahmedabad, for allowing me to take project under his guidance. I extend my deep sense of gratitude for his persistence encouragement, motivation and inspiration, which led me to pinnacle of success. Anything done would have been very difficult without his vast experience, innovative ideas and knowledge.

My sincere thanks to **Dr. K. Kotecha**, Director, Institute of Technology, **Prof. A. S. Ranade**, Head, Department of Electrical Engineering, Institute of Technology, Nirma University, Ahmedabad for allowing me to do my project work in the Institute with free mind and co-operation from learned senior professors in Electrical Department.

I also thank **Prof. U. A. Patel,** Section Head, and **Dr. P. N. Tekwani,** Professor, Department of Electrical Engineer, Institute of Technology, Nirma University, Ahmedabad, for their permission regarding use of PG computer lab as and when necessary.

I am thankful to **Prof. J. B. Patel**, Associate Professor, Department of Instrumentation & Control Engineering, Institute of Technology, Nirma University, Ahmedabad, for his valuable guidance for my project work during the training session.

I am also thankful to my senior **Mr. Dhaval Patel (06MEE008)** for providing me his valuable guidance and time for the project work during training session. I also thank **Mr. Harshad Patel,** Lab Assistant, Power Electronics lab and **Mr. Pratik Jani,** Lab Assistant, Power System Lab, Department of Electrical Engineer, Institute of Technology, Nirma University of Science and Technology, Ahmedabad for their cooperation regarding the usage of lab and equipments as and when required.

I am really thankful to **Mr. R. Ramesh,** Manager, Veeral Controls Pvt. Ltd., Gandhinagar and **Mr. Sanjay Parmar,** Engineer, Veeral Controls Pvt. Ltd., Gandhinagar for their kind help for their guidance and providing boost inductors for project work.

Thanks for the blessings & encouragement by God, my parents & family members to make me capable to reach up to this level.

Khanduja Gagandip Singh Narendra Singh 07MEE006

I

#### ABSTRACT

Solid state ac-dc conversion of electric power is widely used in adjustable-speed drives, switch-mode power supplies, uninterrupted power supplies, and utility interface with non conventional energy sources such as solar PV, etc., battery energy storage systems, in process technology such as electroplating, welding units, etc., battery charging for electric vehicles, and power supplies for telecommunication systems, measurement and test equipments. Conventionally, ac-dc converters, which are also called rectifiers, are developed using diodes and thyristors to provide controlled and uncontrolled dc power with unidirectional and bidirectional power flow. They have the demerits of poor power factor at input ac mains and slow varying rippled dc output at load end, low efficiency and large size of ac and dc filters. In light of their increased applications, a new breed of rectifiers has been developed using new solid state self commutating devices such as MOSFETs, insulated gate bipolar transistors, gate turn-off thyristors.

The report of major project is based on the performance comparison of single phase diode bridge rectifier and the proposed front-end converter in terms of the Total harmonic distortion (% THD) of the line current, power factor of the system and ability of energy saving of the converter by reverse power flow action. The parameters of the voltage control loop for proposed converter are derived by two methods named Unity Modulus (Magnitude Optimum) Method and Ziegler-Nichols method. The parameters obtained from both the methods are compared by the mathematical model for forward and reverse power flow mode of operation. The model is generated in simulink (MATLAB) and results are obtained for steady state, transient and dynamic conditions. It is observed that the unity power factor is maintained during all the conditions for various loads. Drastic reduction in %THD of input current waveform is obtained in proposed front-end converter with an added advantage of regenerative capability. For comparison of control loops results a programming file is also generated in MATLAB (M-file) and from the same step response and Nyquist plots are obtained for system control loops.

The fabrication of IGBT based gate driver circuit and dead band circuit is performed. The gate driver circuit results are obtained after the fabrication of the PCB. The results are obtained for the normal working condition and also for the fault condition. The obtained results show the required performance of the gate driver circuit and the dead band circuit. To understand the circuit in proper manner all the components are tested and the results for the same are obtained as per requirement.

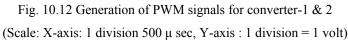

The PWM signals for the prototype front-end converter are generated with the help of the MICRO-2407 DSP trainer kit. The results for the generated signal show the PWM signals as per the requirement for the both converters.

# **LIST OF FIGURES**

| Figure    | Description                                                                                                                                                                                            | Page |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| No.       | Description                                                                                                                                                                                            | No.  |

| Chapter-1 |                                                                                                                                                                                                        |      |

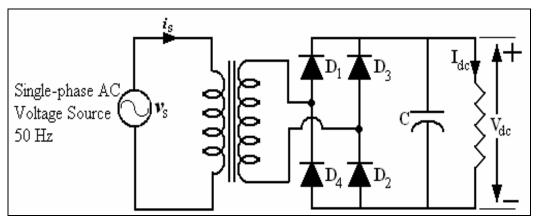

| 1.1       | Diode bridge type ac-to-dc converter                                                                                                                                                                   | 1    |

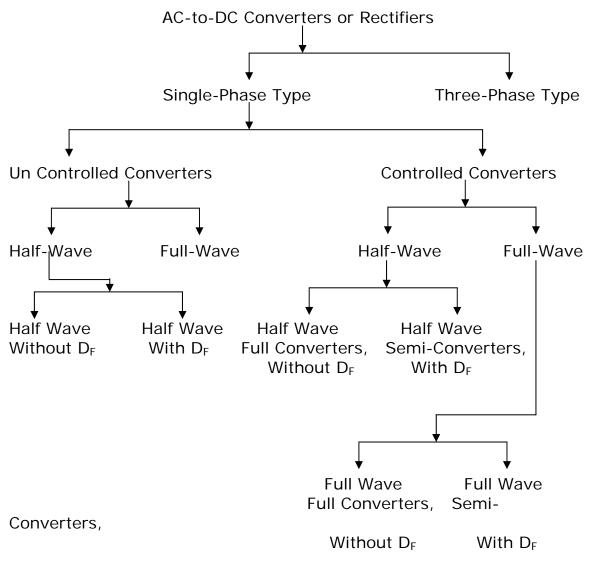

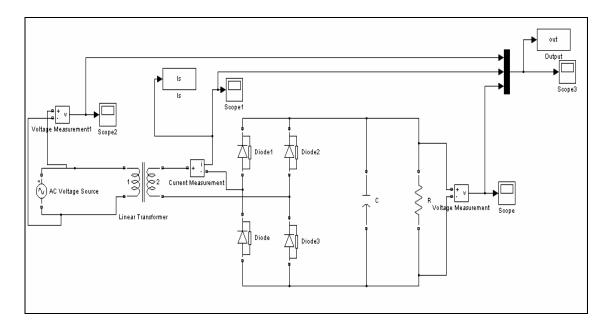

| 1.2       | Classification of converters                                                                                                                                                                           | 2    |

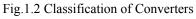

| 1.3       | Simulink model of diode bridge rectifier                                                                                                                                                               | 3    |

| 1.4       | Waveforms for $V_s$ , $V_{dc}$ and $I_s$ of single phase diode bridge rectifier                                                                                                                        | 3    |

| 1.5       | Normalized harmonic spectrum of line current for single phase diode bridge rectifier                                                                                                                   | 4    |

| Chapter-2 |                                                                                                                                                                                                        |      |

| 2.1       | Proposed front-end converter                                                                                                                                                                           | 10   |

| 2.2       | Phasor diagram of front-end converter                                                                                                                                                                  | 12   |

| Chapter-3 |                                                                                                                                                                                                        |      |

| 3.1       | Block schematic of current control loop                                                                                                                                                                | 16   |

| 3.2       | PI controller in S domain                                                                                                                                                                              | 18   |

| 3.3       | Block diagram of PI controller                                                                                                                                                                         | 18   |

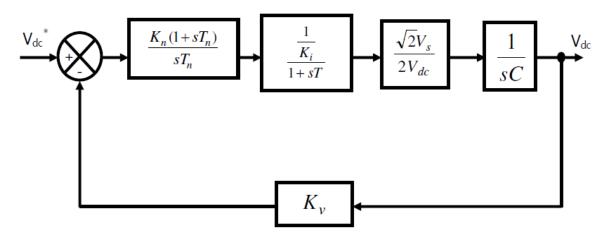

| 3.4       | Block schematic of voltage control loop                                                                                                                                                                | 20   |

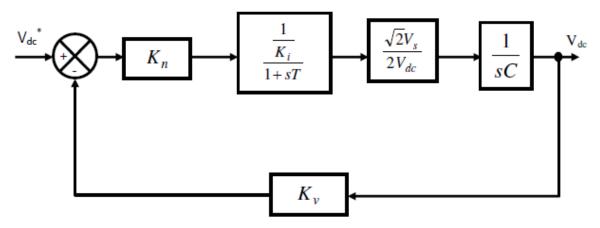

| 3.5       | Block schematic of voltage control loop from Ziegler-Nichols method                                                                                                                                    | 22   |

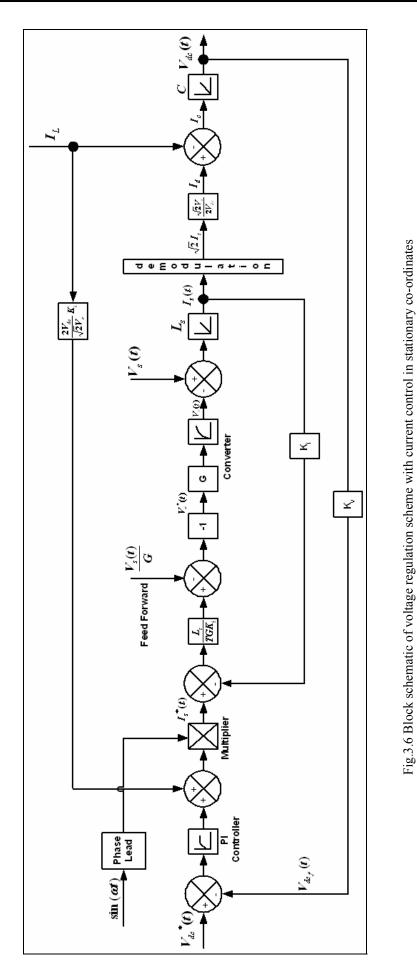

| 3.6       | Block schematic of voltage regulation scheme with current control in stationary co-ordinates                                                                                                           | 25   |

| Chapter-4 |                                                                                                                                                                                                        |      |

| 4.1       | Simulation blocks of mathematical model for front-end converter                                                                                                                                        | 27   |

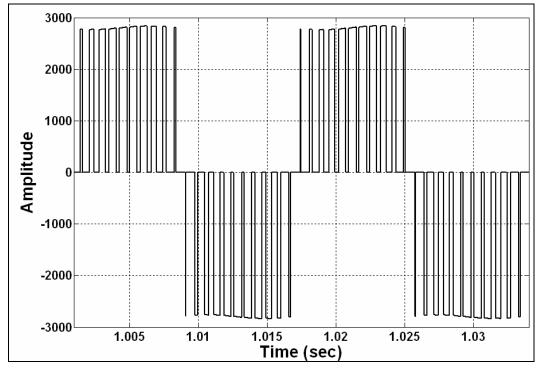

| 4.2       | Voltage waveform $V_{A1B1} = V_{A10} - V_{B10}$ (i.e. $V_{r1}$ )                                                                                                                                       | 27   |

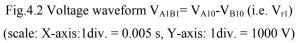

| 4.3       | Voltage waveform $V_{AB} = V_{A1B1} + V_{A2B2}$ (i.e. $V_r$ )                                                                                                                                          | 28   |

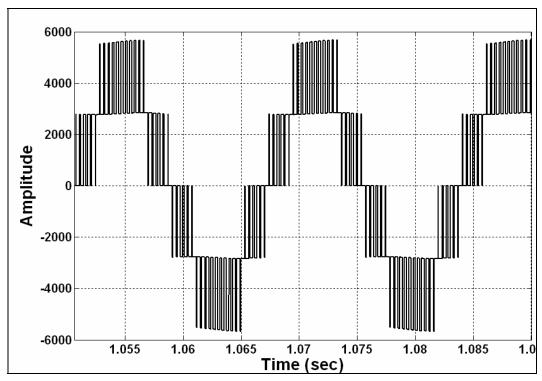

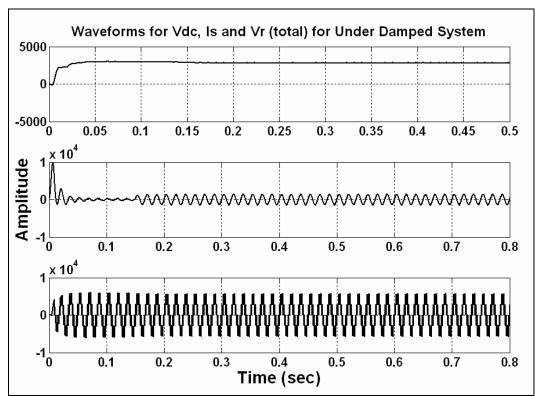

| 4.4       | $V_{dc}$ , $I_s$ & $V_r$ (total) waveforms of the proposed converter for under damped system (Unity Modulus method)                                                                                    | 29   |

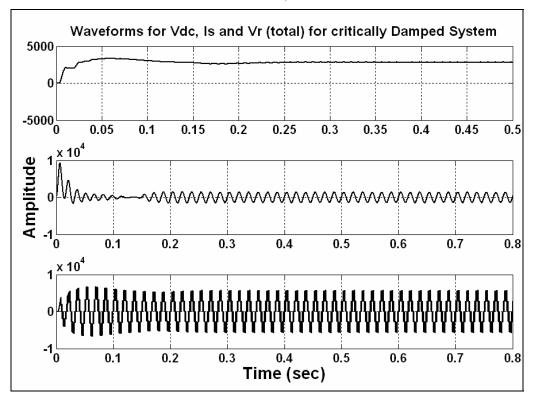

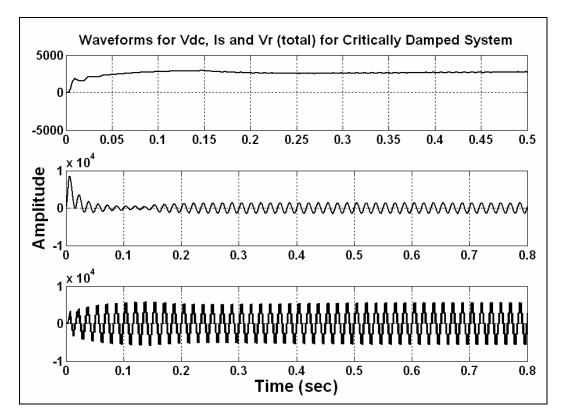

| 4.5       | $V_{dc}$ , $I_s \& V_r$ (total) waveforms of the proposed converter for critically damped system (Unity Modulus method)                                                                                | 29   |

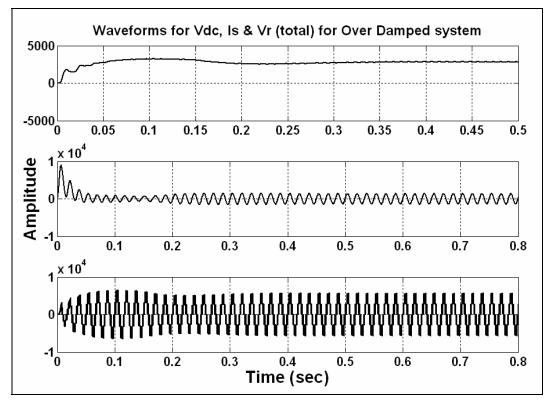

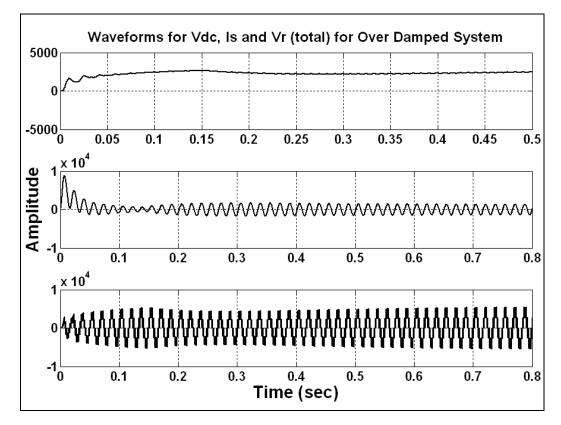

| 4.6       | $V_{dc}$ , I <sub>s</sub> & V <sub>r</sub> (total) waveforms of the proposed converter for over damped system (Unity Modulus method)                                                                   | 30   |

| 4.7       | $V_{dc}$ , $I_s \& V_r$ (total) waveforms of the proposed converter for under<br>damped system (Ziegler-Nichols method)<br>$V_t$ , $I_s \& V_r$ (total) waveforms of the proposed converter for        | 30   |

| 4.8       | $V_{dc}$ , $I_s \& V_r$ (total) waveforms of the proposed converter for critically damped system (Ziegler-Nichols method) $V_{dc}$ , $I_s \& V_r$ (total) waveforms of the proposed converter for over | 31   |

| 4.9       | $v_{dc}$ , $r_s \approx v_r$ (total) wavelolins of the proposed converter for over<br>damped system (Ziegler-Nichols method)                                                                           | 31   |

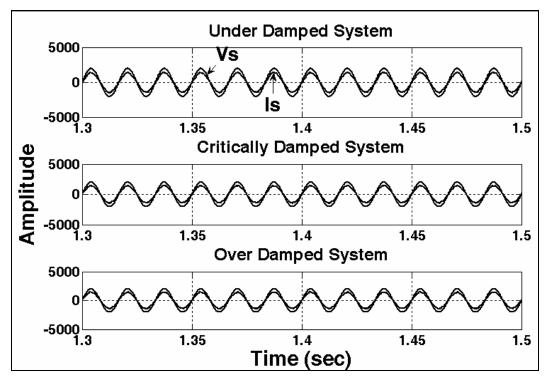

| 4.10 | $V_s$ and $I_s$ waveforms under motoring mode of operation                                                       | 32 |

|------|------------------------------------------------------------------------------------------------------------------|----|

| 4.11 | $V_s$ and $I_s$ waveforms under regenerative mode of operation                                                   | 32 |

| 4.12 | Waveforms of dc link voltage for under damped system                                                             | 33 |

| 4.13 | Waveforms of dc link voltage for critically damped system                                                        | 34 |

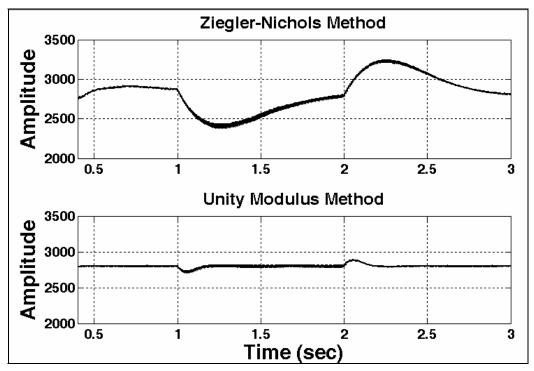

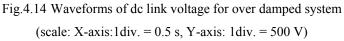

| 4.14 | Waveforms of dc link voltage for over damped system                                                              | 34 |

| 4.15 | $V_{dc}$ , $V_s$ and $I_s$ waveforms for under motoring to regenerative mode of operation                        | 35 |

| 4.16 | Vdc, Vs and Is waveforms for transition from motoring to regenerative mode of operation (Unity Modulus Method)   | 36 |

| 4.17 | Vdc, Vs and Is waveforms for transition from motoring to regenerative mode of operation (Zeigler-Nichols Method) | 36 |

| 4.18 | Vdc, Vs and Is waveforms for transition from regenerative to motoring mode of operation (Unity Modulus Method)   | 37 |

| 4.19 | Vdc, Vs and Is waveforms for transition from regenerative to motoring mode of operation (Zeigler-Nichols Method) | 37 |

| 4.20 | $V_{dc}$ , $V_s$ and $I_s$ waveforms from no load to full load under forward (motoring) mode of operation        | 38 |

| 4.21 | $V_{dc}$ , $V_s$ and $I_s$ waveforms from full load to no load under motoring mode of operation                  | 39 |

| 4.22 | $V_{dc}$ , $V_s$ and $I_s$ waveforms from no load to full load under reverse (regenerative) mode of operation    | 39 |

| 4.23 | $V_{dc}$ , $V_s$ and $I_s$ waveforms from full load to no load under regenerative mode of operation              | 40 |

| 4.24 | Waveforms of dc link voltage and line current for under damped system during fault condition                     | 41 |

| 4.25 | $V_{dc}$ , $V_s$ and $I_s$ waveforms during fault condition under motoring mode of operation                     | 41 |

| 4.26 | $V_{dc}$ , $V_s$ and $I_s$ waveforms during fault condition under regenerative mode of operation                 | 42 |

| 4.27 | Normalized harmonic spectrum of line current for one converter (i.e. $I_{s1}$ or $I_{s2}$ )                      | 42 |

| 4.28 | Normalized harmonic spectrum of combined current reflected to primary (i.e. $I_s$ )                              | 43 |

| 4.29 | Flow chart Representation of MATLAB Program for Front-End Converter                                              | 45 |

| 4.30 | Step response of current control loop for under damped system ( $\zeta = 0.707$ )                                | 46 |

| 4.31 | Step response of current control loop for under damped system ( $\zeta = 0.1$ )                                  | 46 |

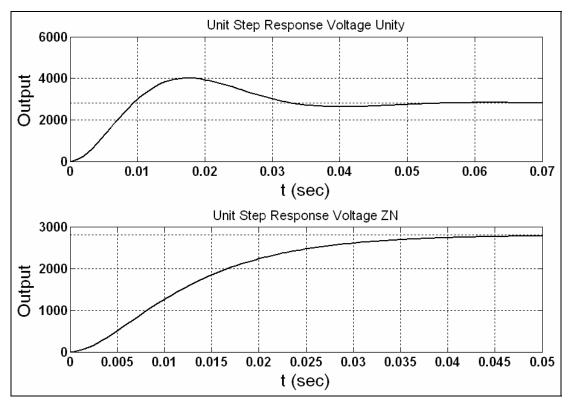

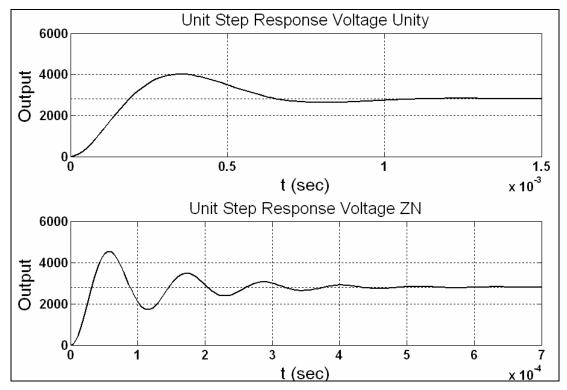

| 4.32 | Step response of voltage control loop for under damped system ( $\zeta = 0.707$ )                                | 47 |

| 4.33 | Step response of voltage control loop for under damped system ( $\zeta = 0.1$ )                                  | 47 |

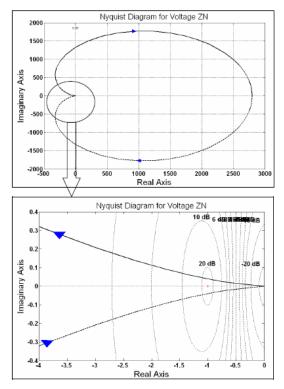

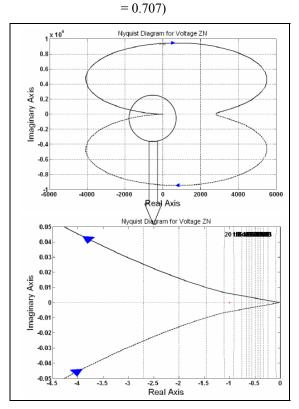

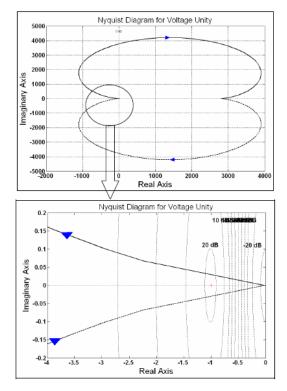

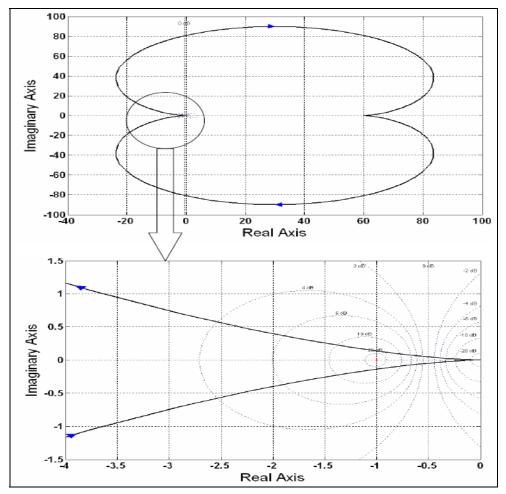

| 4.34 | Nyquist plot of Voltage control loop for under damped system (Ziegler-Nichols method, $\zeta = 0.707$ )          | 48 |

| 4.35 | Nyquist plot of Voltage control loop for under damped system (Unity Modulus method, $\zeta = 0.707$ )            | 48 |

| 4.36      | Nyquist plot of Voltage control loop for under damped system                                                                                       | 48 |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.37      | (Ziegler-Nichols method, $\zeta = 0.1$ )<br>Nyquist plot of Voltage control loop for under damped system<br>(Unity Modulus method, $\zeta = 0.1$ ) | 48 |

| Chapter-5 | (onity would include, $\zeta = 0.1$ )                                                                                                              |    |

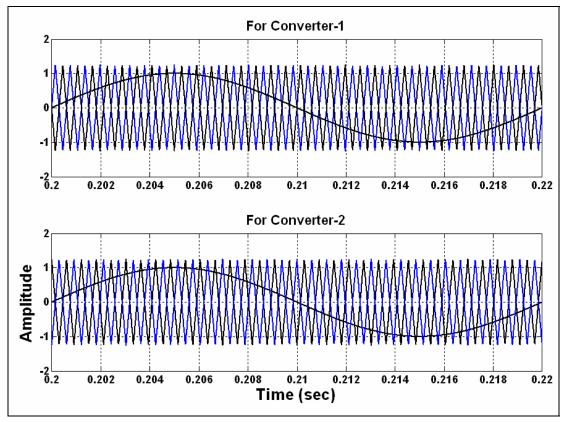

| 5.1       | Schematic of prototype front-end converter                                                                                                         | 49 |

| 5.2       | Carrier and reference waveforms for both converters                                                                                                | 53 |

| 5.3       | Voltage waveform $V_{A1B1} = V_{A10} - V_{B10}$ (i.e. $V_{r1}$ )                                                                                   | 53 |

| 5.4       | Voltage waveform $V_{AB} = V_{A1B1} + V_{A2B2}$ (i.e. $V_r$ )                                                                                      | 54 |

| 5.5       | $V_{dc},V_s$ and $I_s$ waveforms from full load to no load under motoring mode of operation                                                        | 54 |

| 5.6       | $V_{dc}$ , $V_s$ and $I_s$ waveforms for transition from motoring to regenerative mode of operation                                                | 55 |

| 5.7       | $V_{dc}$ , $V_s$ and $I_s$ waveforms during fault condition under motoring mode of operation                                                       | 55 |

| 5.8       | Normalized harmonic spectrum of combined current reflected to primary (i.e. $I_s$ )                                                                | 56 |

| 5.9       | Step response of current control loop for under damped system                                                                                      | 57 |

| 5.10      | Step response of voltage control loop for under damped system                                                                                      | 57 |

| 5.11      | Nyquist plot of Voltage control loop for under damped system                                                                                       | 58 |

| Chapter-6 |                                                                                                                                                    |    |

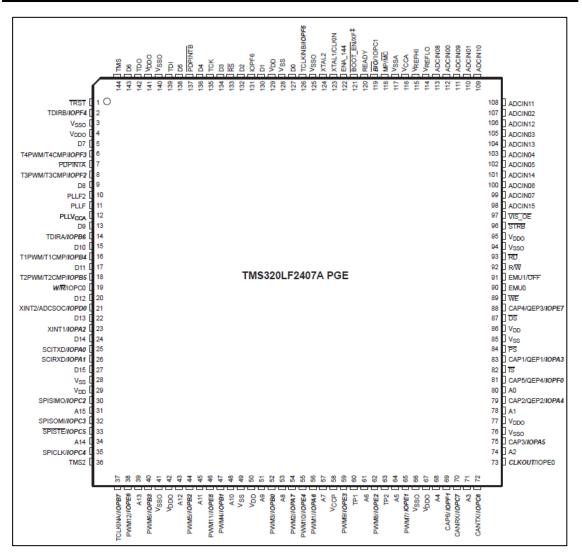

| 6.1       | Pin outs of TMS320LF2407A                                                                                                                          | 61 |

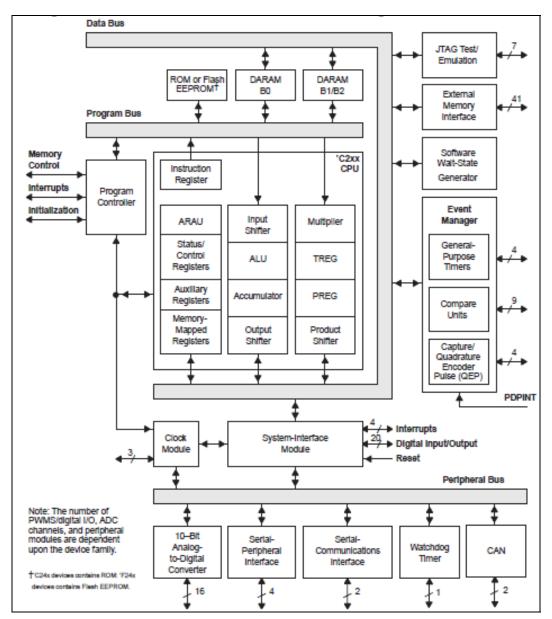

| 6.2       | TMS320C24x DSP controller functional block diagram                                                                                                 | 64 |

| 6.3       | A graphical overview of 240xA device                                                                                                               | 65 |

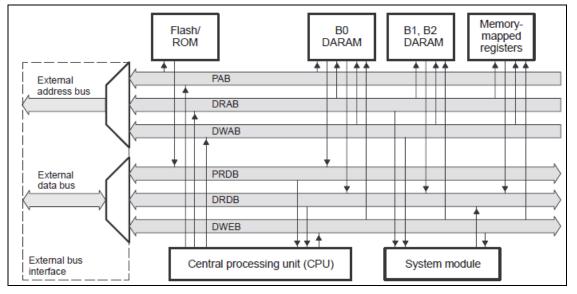

| 6.4       | C24x address and data bus structure                                                                                                                | 66 |

| 6.5       | Quadrature encode pulses                                                                                                                           | 70 |

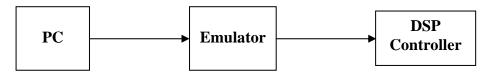

| 6.6       | Interfacing of PC to Micro-2407                                                                                                                    | 71 |

| Chapter-7 |                                                                                                                                                    |    |

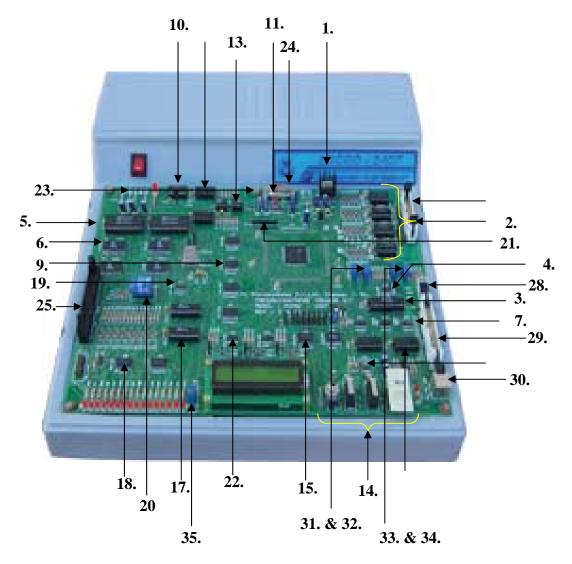

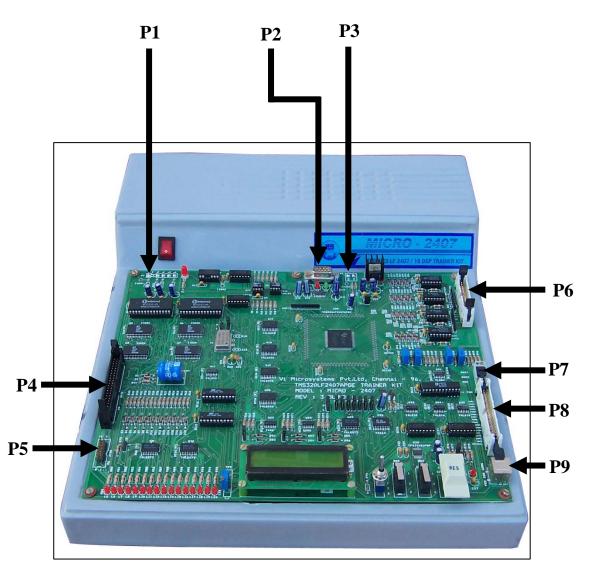

| 7.1       | Pictorial view of Micro-2407                                                                                                                       | 75 |

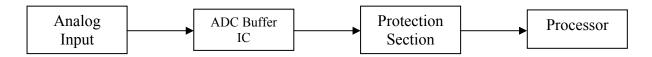

| 7.2       | Block diagram of ADC section                                                                                                                       | 75 |

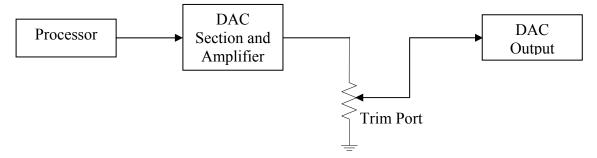

| 7.3       | Block diagram of DAC section                                                                                                                       | 76 |

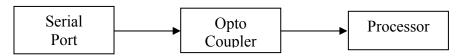

| 7.4       | Opto Coupler Block diagram                                                                                                                         | 76 |

| 7.5       | Pictorial view of Micro-2407 with connector details                                                                                                | 83 |

| Chapter-8 |                                                                                                                                                    |    |

| 8.1       | Over current protection by measuring the instantaneous on-state                                                                                    | 86 |

|           | collector-emitter voltage of the power transistor                                                                                                  |    |

| 8.2       | Schematic of an optocoupler used to couple signals to a floating                                                                                   | 87 |

|           |                                                                                                                                                    |    |

|           | (electrically isolated) drive circuit from a control circuit referenced                                           |     |

|-----------|-------------------------------------------------------------------------------------------------------------------|-----|

|           | with respect to the control logic ground (and power system neutral)                                               |     |

| 8.3       | Opto coupler isolation of base drive circuits                                                                     | 88  |

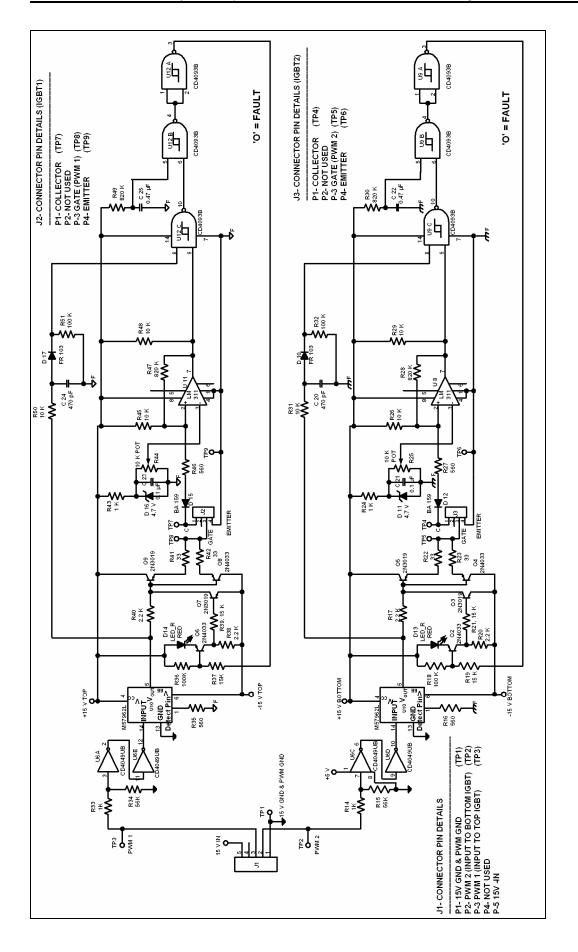

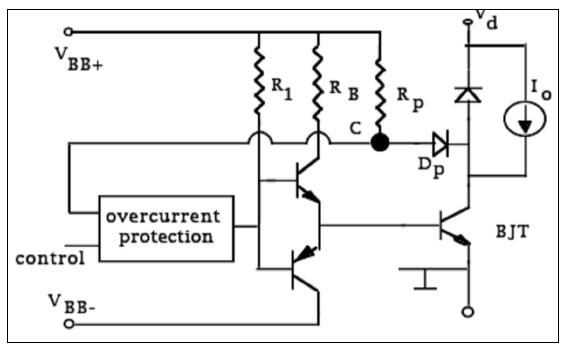

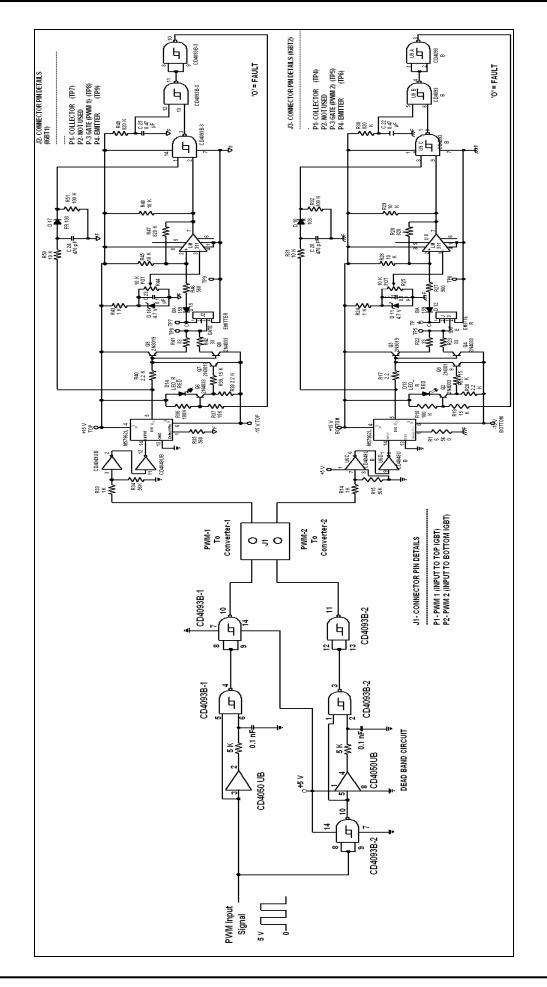

| 8.4       | Schematic of IGBT based gate driver circuit used for the prototype front-end converter                            | 89  |

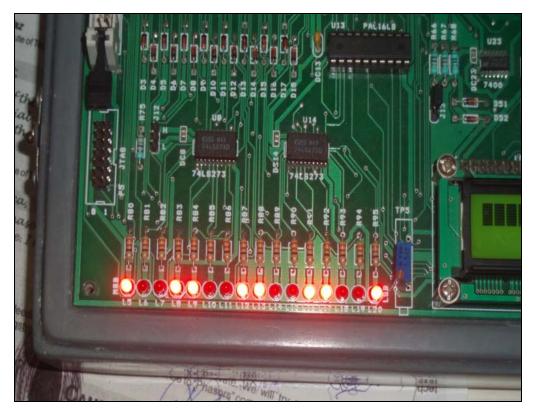

| 8.5       | Pictorial view of test setup of IC CD4049UB                                                                       | 92  |

| 8.6       | Pictorial view of output at IC CD4049UB                                                                           | 92  |

| 8.7       | Pictorial view of test setup of IC M57962L                                                                        | 93  |

| 8.8       | Pictorial view of output at IC M57962L                                                                            | 93  |

| 8.9       | Pictorial view of output up to IC M57962L (OPTOCOUPLER ISOLATOR)                                                  | 94  |

| 8.10      | Pictorial view of output up to port TR <sub>8</sub> (Gate pulse)                                                  | 94  |

| 8.11      | Over current protection by measuring the instantaneous on-state collector-emitter voltage of the power transistor | 95  |

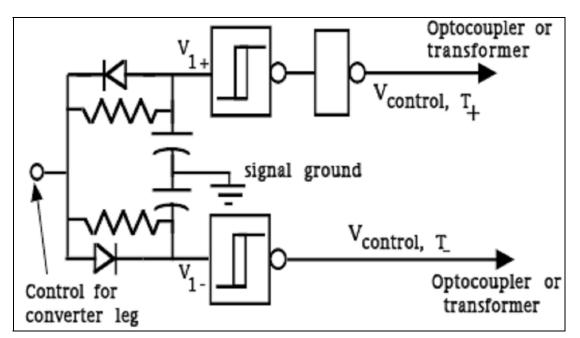

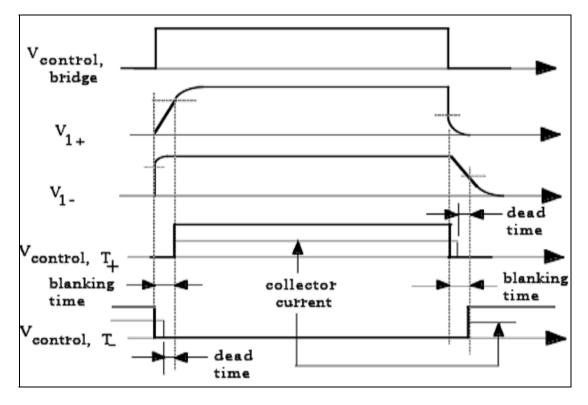

| 8.12      | Circuit to provide blanking times to the base drivers                                                             | 97  |

| 8.13      | Collector current waveforms showing dead time and blanking time                                                   | 97  |

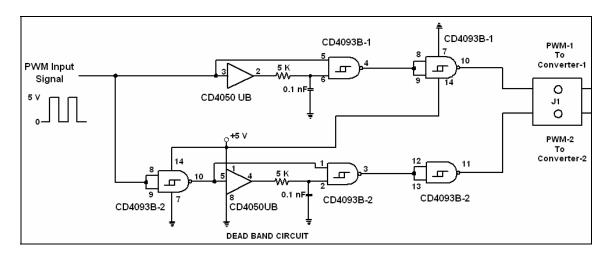

| 8.14      | Schematic of dead band circuit                                                                                    | 98  |

| 8.15      | Pictorial view of setup for manual fault creation at output of port TR <sub>8</sub> (Gate pulse)                  | 98  |

| 8.16      | Pictorial view of output at port TR <sub>8</sub> (Gate pulse) after fault                                         | 99  |

| 8.17      | Pictorial view of setup for fault creation at port TP <sub>7</sub> (connection of IGBT)                           | 99  |

| 8.18      | Pictorial view of output at port TP <sub>7</sub> (connection of IGBT)                                             | 100 |

| 8.19      | Pictorial view of setup for sort circuit protection of IGBT                                                       | 100 |

| 8.20      | Pictorial view of output for sort circuit protection of IGBT                                                      | 101 |

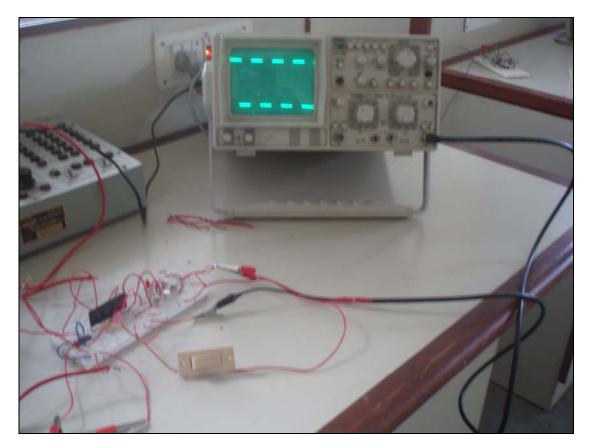

| 8.21      | Pictorial view of setup for testing of dead band circuit                                                          | 101 |

| 8.22      | Pictorial view of results from dead band circuit                                                                  | 102 |

| Chapter-9 |                                                                                                                   |     |

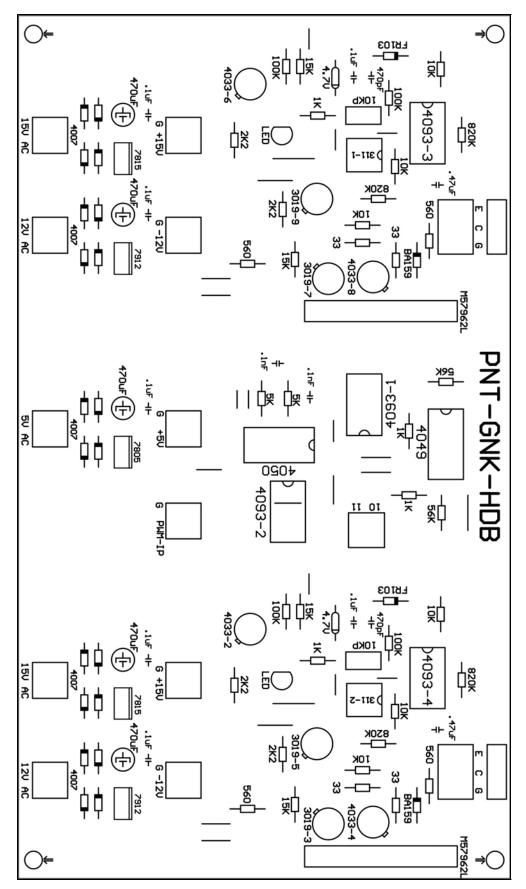

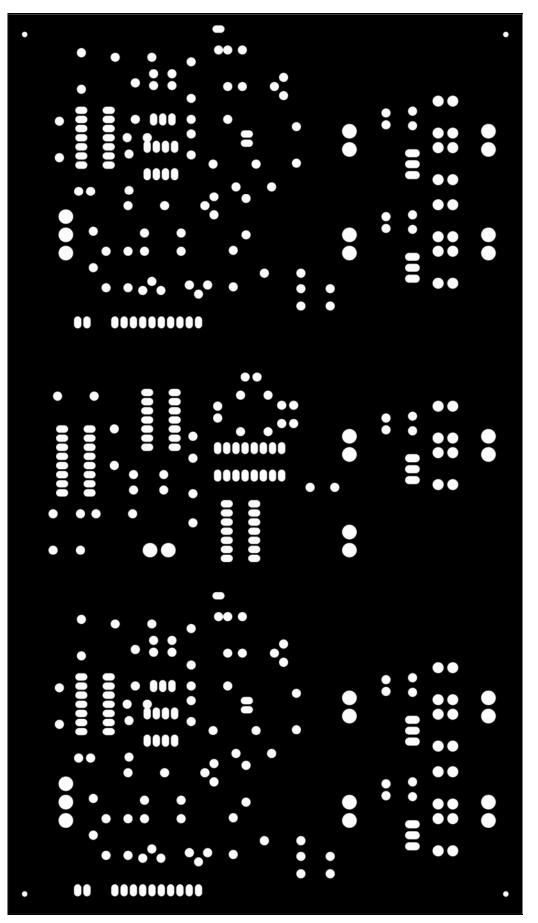

| 9.1       | Silk screen layer of the gate driver circuit with dead band and protection circuit and jumper details             | 104 |

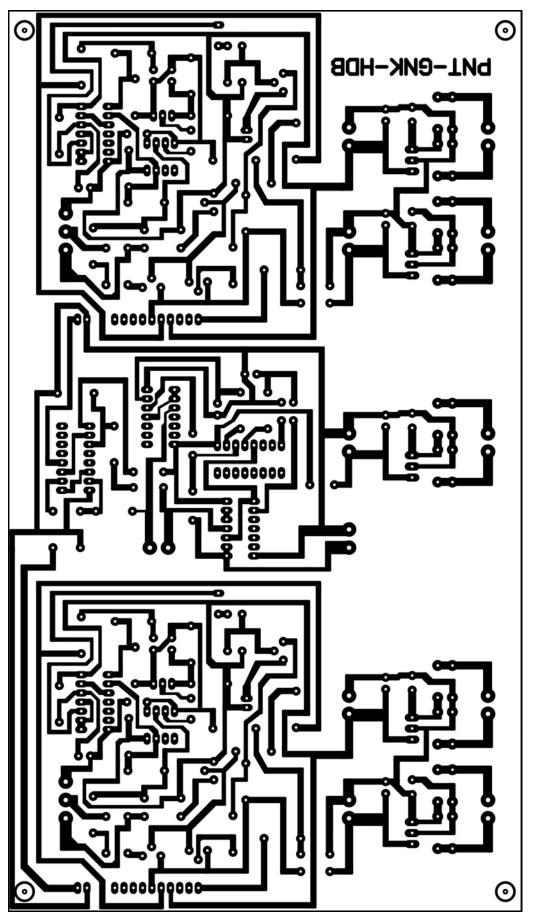

| 9.2       | Bottom layer of the gate driver circuit with dead band and protection circuit                                     | 105 |

| 9.3       | Solder mark layer of the PCB                                                                                      | 106 |

| 9.4       | Schematic of IGBT based gate driver circuit used for the prototype                                                | 108 |

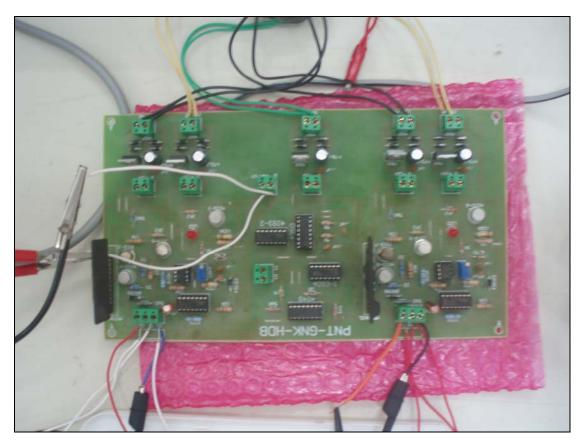

| 9.5       | front-end converter<br>Top view of fabricated IGBT gate driver card for one leg of<br>prototype converter         | 110 |

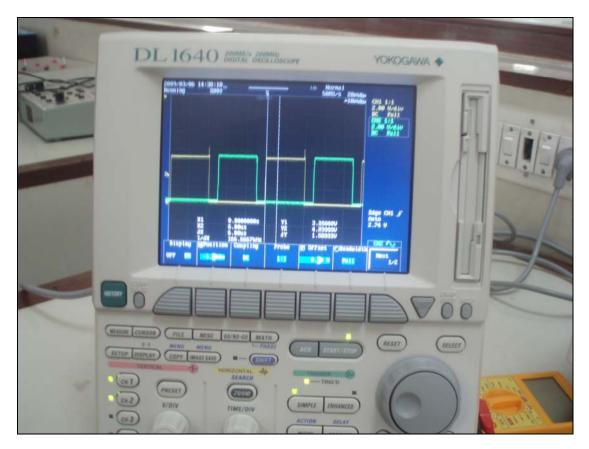

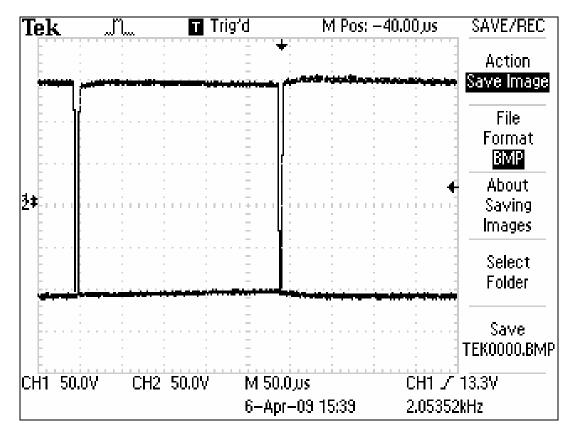

| 9.6        | Results of gate driver card for one leg of prototype converter                             | 111 |

|------------|--------------------------------------------------------------------------------------------|-----|

| 9.7        | Complementary switching patterns with dead band obtained using gate driver card            | 111 |

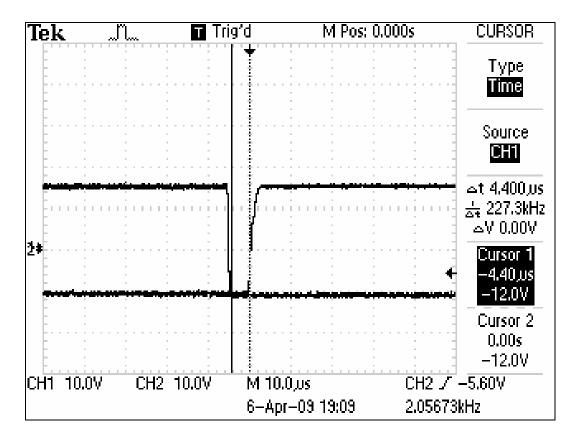

| 9.8        | Dead band of 4.4 $\mu$ sec obtained using dead band circuit of gate driver circuit         | 112 |

| 9.9        | Results for gate driver card when only one converter in working mode                       | 112 |

| 9.10       | Results for gate driver card when both converter are at fault condition                    | 113 |

| Chapter-10 |                                                                                            |     |

| 10.1       | Pictorial view of results for addition of values                                           | 115 |

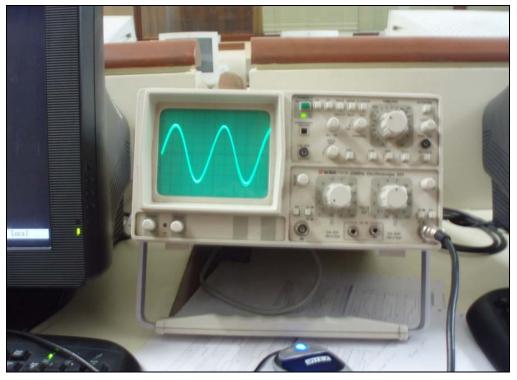

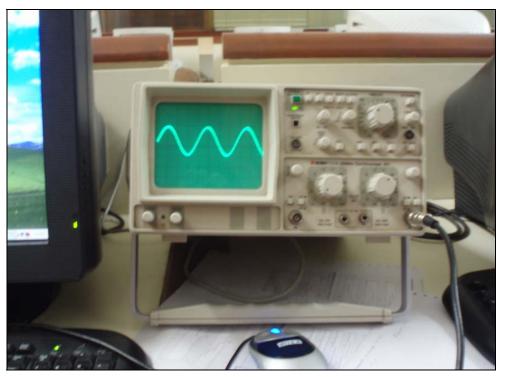

| 10.2       | Pictorial view of results for sine wave generation                                         | 115 |

| 10.3       | Pictorial view of sine wave generation (1V and 50 Hz)                                      | 116 |

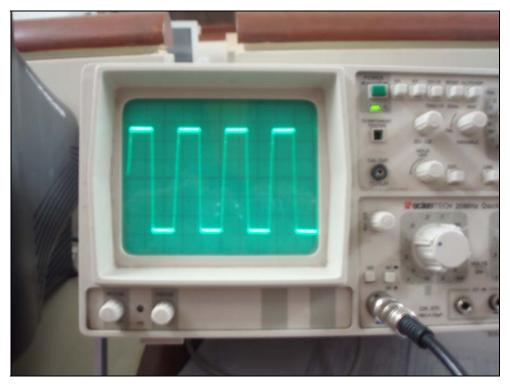

| 10.4       | Pictorial view of square wave generation                                                   | 116 |

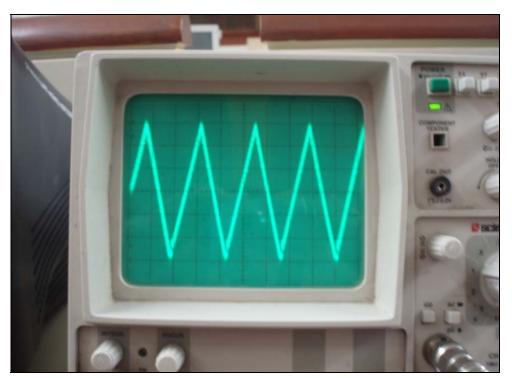

| 10.5       | Pictorial view of triangle wave generation                                                 | 117 |

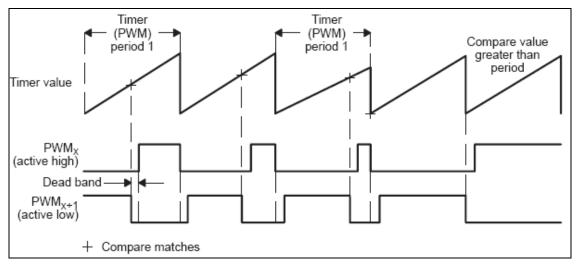

| 10.6       | Asymmetric PWM waveform generation with compare unit and PWM circuits ( $x = 1, 3, or 5$ ) | 118 |

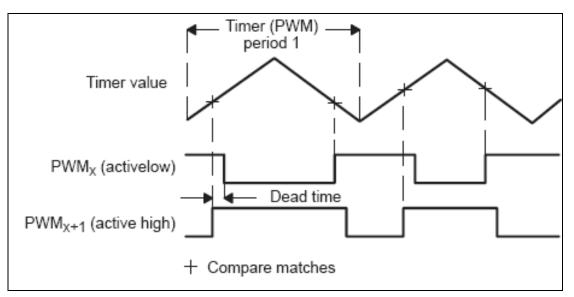

| 10.7       | Symmetric PWM waveform generation with compare units and                                   | 120 |

|            | PWM circuits $(x = 1, 3, or 5)$                                                            |     |

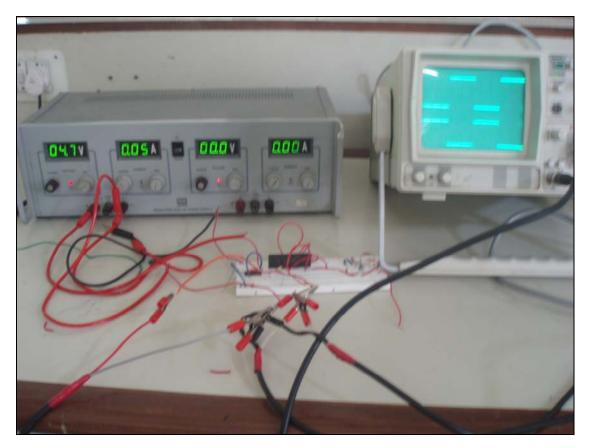

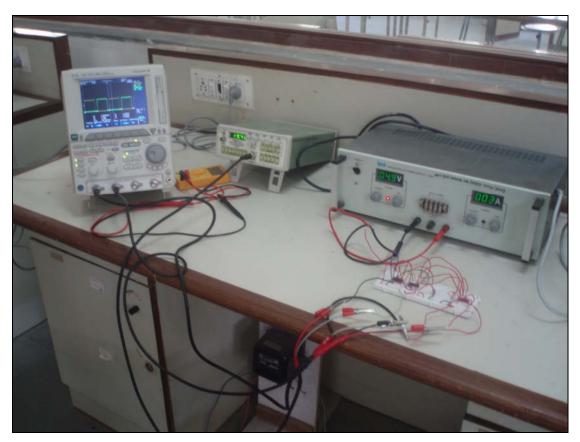

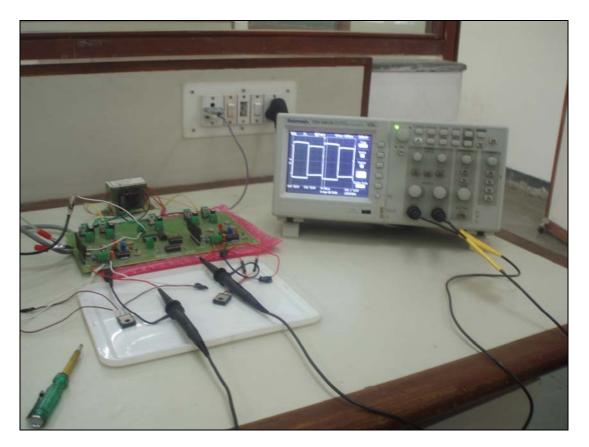

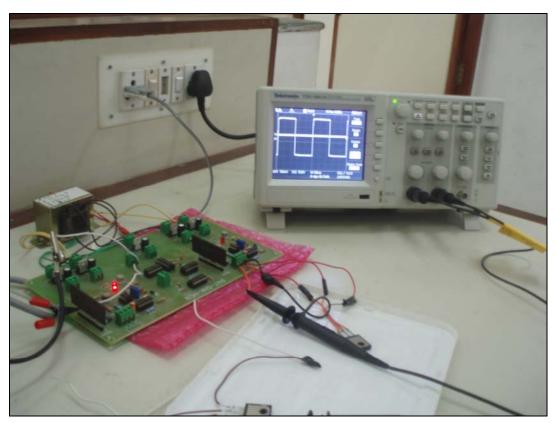

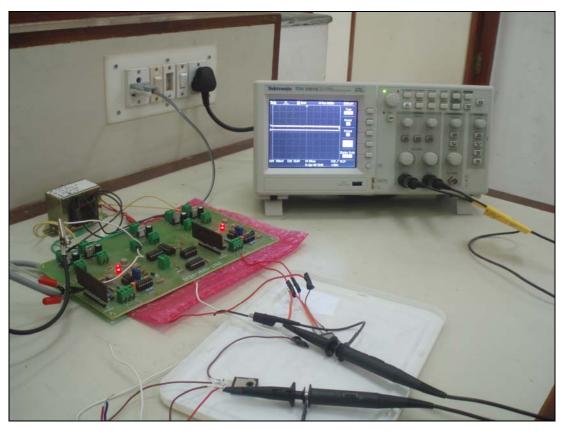

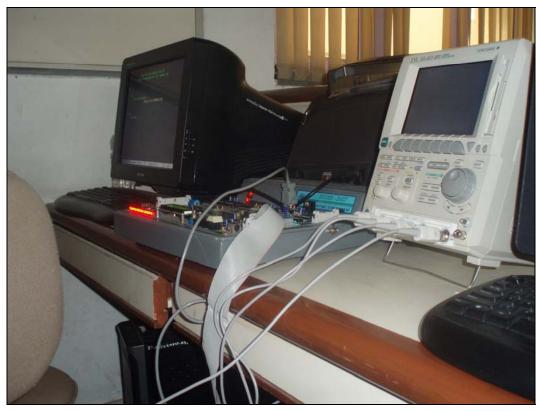

| 10.8       | Pictorial view of setup for generation of PWM signals from MICRO-2407 kit                  | 120 |

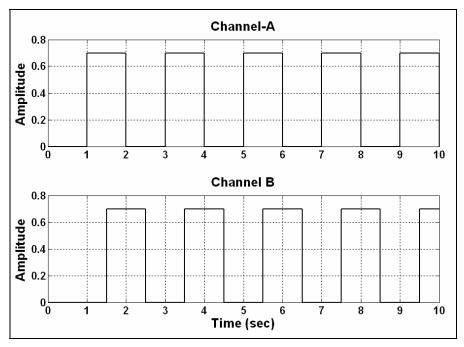

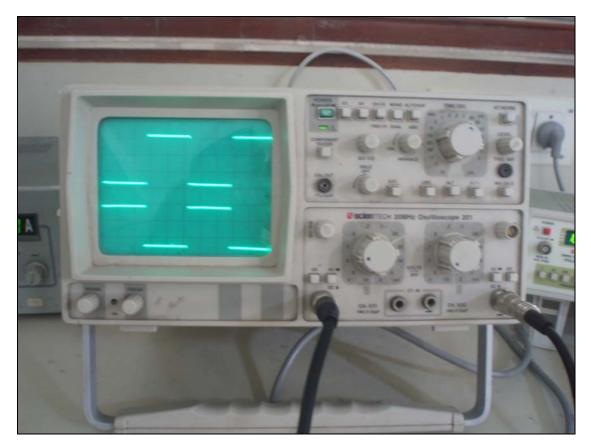

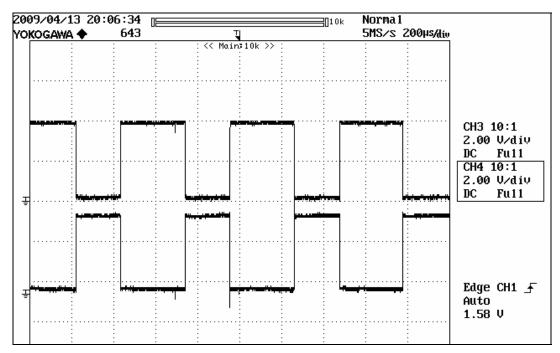

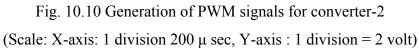

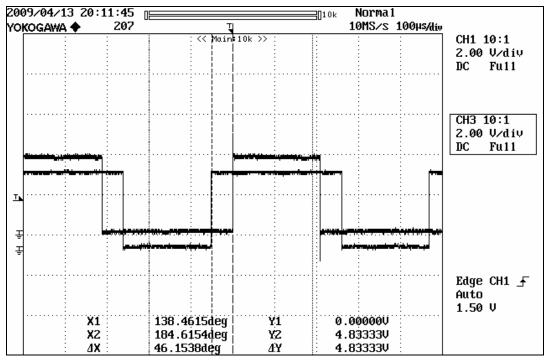

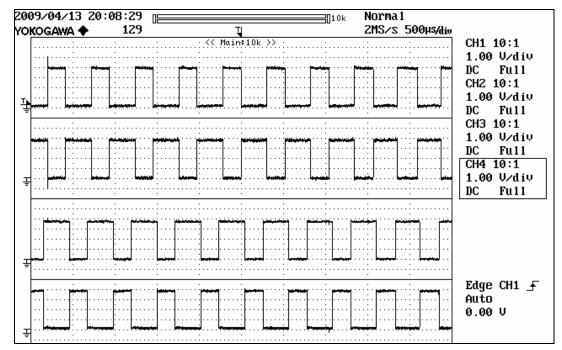

| 10.9       | Generation of PWM signals for converter-1                                                  | 121 |

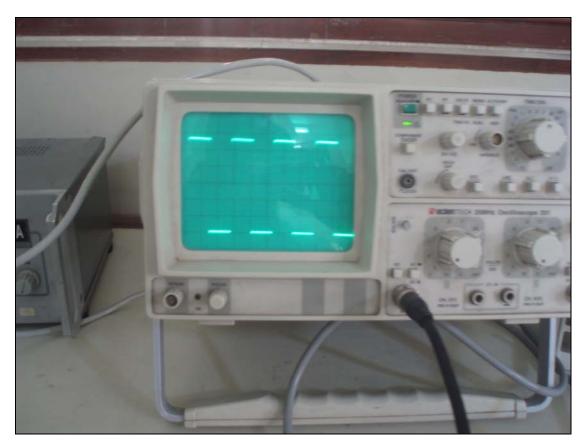

| 10.10      | Generation of PWM signals for converter-2                                                  | 121 |

| 10.11      | Generation of PWM signals for same legs of converter-1 & 2                                 | 122 |

| 10.12      | Generation of PWM signals for converter-1 & 2                                              | 122 |

|            |                                                                                            |     |

# LIST OF TABLES

| Table No. | Торіс                                                           | Page No. |

|-----------|-----------------------------------------------------------------|----------|

| Chapter-3 |                                                                 |          |

| 3.1       | Ziegler-Nichols rules for tuning the PID controller             | 21       |

| 3.2       | Comparison of PI controller parameters for voltage control      | 23       |

|           | loop                                                            | 23       |

| Chapter-7 |                                                                 |          |

| 7.1       | List of components for Micro-2407                               | 72       |

| 7.2       | Trim port functions                                             | 76       |

| 7.3       | Switch functions                                                | 77       |

| 7.4       | Jumper details                                                  | 78       |

| 7.5       | Signal description of P1 connector                              | 79       |

| 7.6       | Signal description of P2 connector                              | 79       |

| 7.7       | Signal description of P3 connector                              | 80       |

| 7.8       | Signal description of P6 connector                              | 80       |

| 7.9       | Signal description of P7 connector                              | 81       |

| 7.10      | Signal description of P8 connector                              | 81       |

| 7.11      | Signal description of P9 connector                              | 82       |

| Chapter-8 |                                                                 |          |

| 8.1       | Components list for IGBT gate driver                            | 90       |

| Chapter-9 |                                                                 |          |

| 9.1       | List of components for gate driver circuits (for one card only) | 109      |

## **ABBREVIATION**

| ASD  | Adjustable Speed Drives            |

|------|------------------------------------|

| ADC  | Analog to Digital Converter        |

| ARAU | Auxiliary Register Arithmetic Unit |

| CALU | Central Arithmetic and Logic       |

| CAN  | Control Area Network               |

| DAC  | Digital to Analog Converter        |

| EV   | Event Manager                      |

| FFC  | Feed Forward Controller            |

| GPIO | General Purpose Input Output       |

| JTAG | Joint Test Action Group            |

| PLL  | Phase Lock Loop                    |

| PWM  | Pulse Width Modulation             |

| SCI  | Serial Communication Interface     |

| SMPS | Switched Mode Power Supplies       |

| THD  | Total Harmonic Distortion          |

| UPS  | Uninterruptible Power Supplies     |

| WD   | Watch Dog                          |

|      |                                    |

# NOMENCLATURE

| K <sub>cr</sub>                 | Critical gain of the system          |

|---------------------------------|--------------------------------------|

| K <sub>i</sub>                  | Current feedback loop gain           |

| $K_1$                           | Current loop gain                    |

| ζ                               | Damping ratio                        |

| Ls                              | Input source inductance              |

| G                               | Maximum peak converter input voltage |

| P <sub>cr</sub>                 | Period of sustained oscillation      |

| K <sub>n</sub> , K <sub>p</sub> | PI controller gain                   |

| T <sub>n</sub> , T <sub>i</sub> | Time parameter of PI controller      |

| T <sub>r</sub>                  | Triangular carrier period            |

| $K_{v}$                         | Voltage feedback loop gain           |

# **CONTENTS**

| Acknowledgemer   | ıt                                                            | Ι  |

|------------------|---------------------------------------------------------------|----|

| Abstract         |                                                               | II |

| List of Figures  |                                                               | IV |

| List of Tables   |                                                               | IX |

| Abbreviation     |                                                               | X  |

| Nomenclature     |                                                               | X  |

| Chapter 1 : INTH | RODUCTION                                                     | 1  |

| 1.1              | Overview of the project                                       | 1  |

| 1.2              | Classification of converters                                  | 2  |

| 1.3              | Literature review                                             | 4  |

| Chapter 2 : PRO  | POSED FRONT-END CONVERTER                                     | 9  |

| 2.1              | Design specification for the proposed front-<br>end converter | 9  |

| 2.2              | Theoretical considerations                                    | 11 |

| Chapter 3 : DESI | IGN OF CONTROL LOOPS                                          | 15 |

| 3.1              | Current control loop design                                   | 15 |

| 3.2              | PI controller                                                 | 17 |

| 3.3              | Voltage control loop design                                   | 19 |

| Chapter 4 : SIMU | ULATION AND MATLAB PROGRAMMING                                | 26 |

| RES              | ULTS OF PROPOSED CONVERTER                                    | 20 |

| 4.1              | Simulation results for PWM switching                          | 26 |

| 4.2              | Simulation results for transient condition                    | 28 |

| 4.3              | Simulation results for dynamic condition                      | 33 |

| 4.4              | Simulation results for transition mode of operation           | 35 |

| 4            | 1.5    | Simulation results for different load conditions        | 38 |

|--------------|--------|---------------------------------------------------------|----|

| 4            | 1.6    | Simulation results for fault condition                  | 40 |

| 4            | 1.7    | FFT analysis of line current                            | 42 |

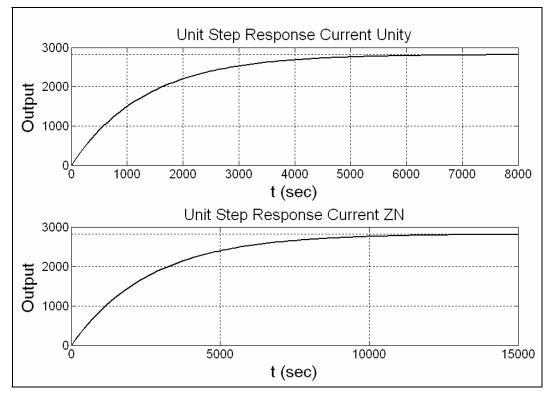

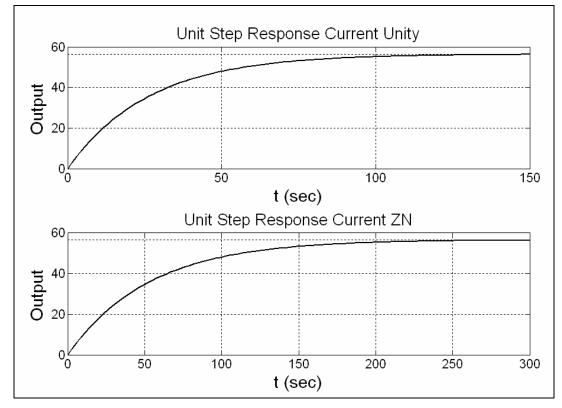

| 4            | 1.8    | Matlab programming of proposed converter<br>and results | 44 |

| Chapter 5: R | RATI   | NGS OF PROTOTYPE CONVERTER AND                          | 49 |

| S            | SIMU   | JLATION RESULTS                                         | 47 |

|              | 5.1    | Specifications of prototype converter                   | 49 |

| -            | 5.2    | Simulation results of prototype converter               | 52 |

| 1            | 5.3    | M-File results of prototype converter                   | 56 |

| Chapter 6: 0 | )VEF   | RVIEW OF DSP TMS320LF2407A                              | 59 |

|              | 6.1    | Introduction                                            | 59 |

|              | 6.2    | Features of TMS320LF2407A                               | 60 |

|              | 6.3    | Functional block diagram                                | 63 |

|              | 6.4    | Architecture of TMS320LF2407A                           | 67 |

| Chapter 7: D | Descri | ption of Micro-2407 trainer board                       | 72 |

|              | 7.1    | Features of Micro-2407                                  | 72 |

|              | 7.2    | Front panel description                                 | 74 |

|              | 7.3    | Jumper placed on Micro-2407                             | 78 |

| ,            | 7.4    | Connector details                                       | 79 |

| Chapter 8: D | ESIC   | <b>GN OF GATE DRIVER CIRCUIT</b>                        | 85 |

| 8            | 8.1    | Design consideration                                    | 85 |

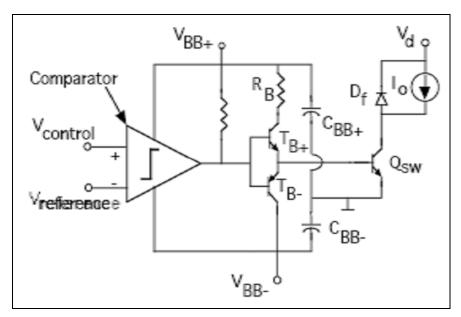

| 8            | 8.2    | Electrically isolated drive circuit                     | 86 |

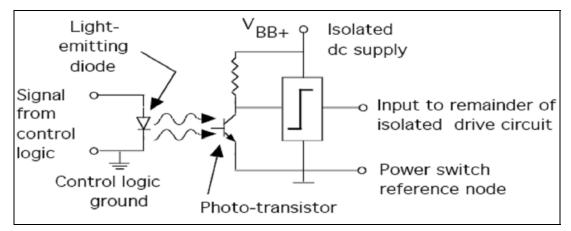

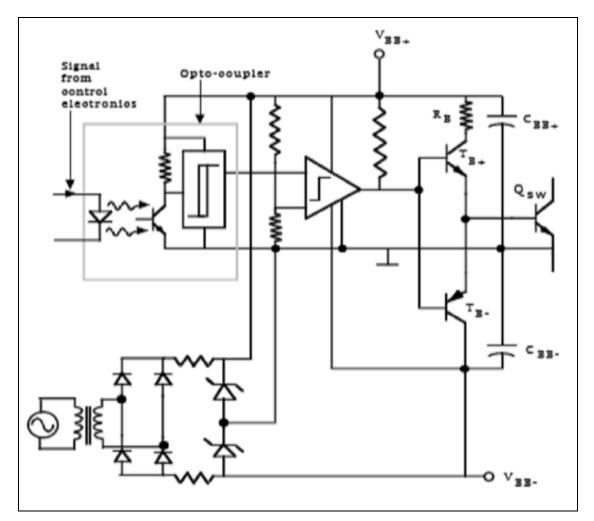

| 8            | 8.3    | Optocoupler isolated drive circuits                     | 87 |

| 8            | 8.4    | IGBT gate drive circuit                                 | 88 |

| 8            | 8.5    | Results of gate drive circuit                           | 91 |

| Q              | Over current protection and blanking times                         | 05        |

|----------------|--------------------------------------------------------------------|-----------|

| 8.             | for bridge circuits                                                | 95        |

| 8.             | 7 Results of protection and dead band circuit                      | <b>98</b> |

| Chapter 9: F.  | ABRICATION OF GATE DRIVER CIRCUIT                                  | 103       |

| Α              | ND RESULTS                                                         | 105       |

| 9.             | Layout of gate driver circuit                                      | 103       |

| 9.             | IGBT based fabricated gate drive circuit and results               | 107       |

| Chapter 10: PH | OGRAMMING AND EXECUTION                                            | 114       |

| 10             | 1 Installation of trainer kit (Micro-2407A)                        | 114       |

| 10             | 2 Examples on serial monitor mode (mode-1)                         | 114       |

| 10             | 3 PWM waveform generation with compare<br>3 units and PWM circuits | 117       |

| 10             | 4 Results of PWM waveform generation from<br>Micro-2407            | 120       |

| Chapter 11: Co | DNCLUSION                                                          | 123       |

| 11             | 1 Conclusion                                                       | 123       |

| 11             | 2 Future work                                                      | 124       |

| References     |                                                                    | 125       |

| Paper Publishe | d                                                                  | 127       |

# CHAPTER-1 INTRODUCTION

#### 1.1 Introduction and Overview of the Project

There are several conventional methods by which the output dc voltage can be controlled, e.g. a diode bridge with a tap changing transformer or an auto-transformer, as shown in fig.1.1. Although this method is simple but suffers from the demerits due to size, weight and cost of transformer. This type of control scheme was used to control dc voltage hence speed of dc motors used in electric traction of Indian Railways [1].

In case of an ac-to-dc phase controlled switching, the phase controller works as an ordinary contactor switch. For a certain period of time, the switch is closed (on), thus the input supply reaches to load and the output voltage can be obtained. Similarly, for the certain period of time the switch is open (off), thus the input voltage does not reach the load. Thus, instead of the complete input voltage reaching the load, the switch (phase controlled converter) slices the input voltage and only its part reaches the load. In this arrangement no transformer is required. Thus, the size, weight and cost reduce and efficiency is high.

Fig.1.1 Diode bridge type ac-to-dc converter

#### **1.2 Classification of Converters**

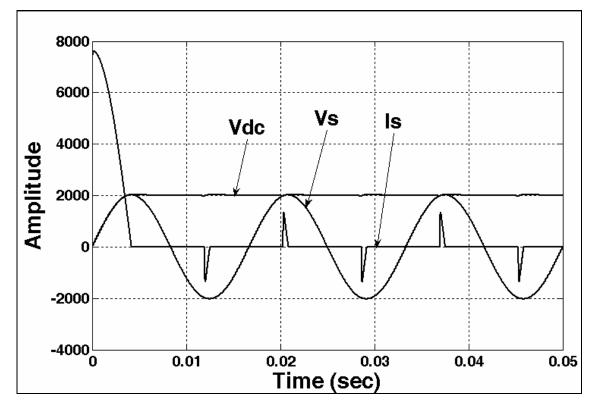

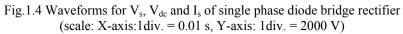

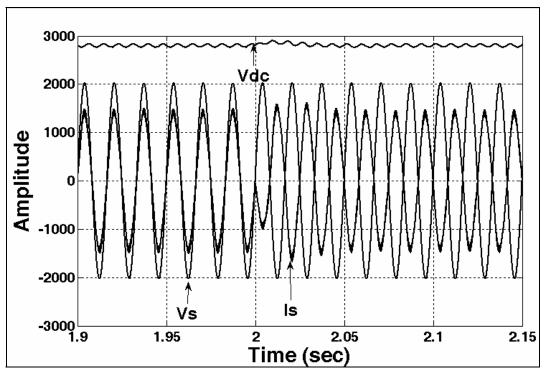

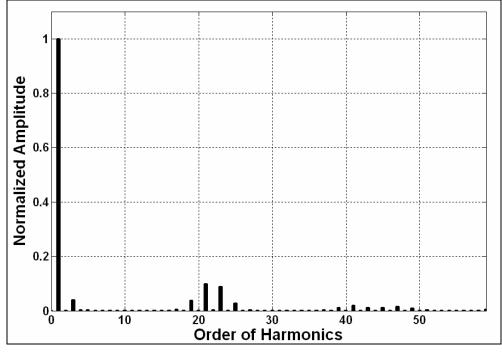

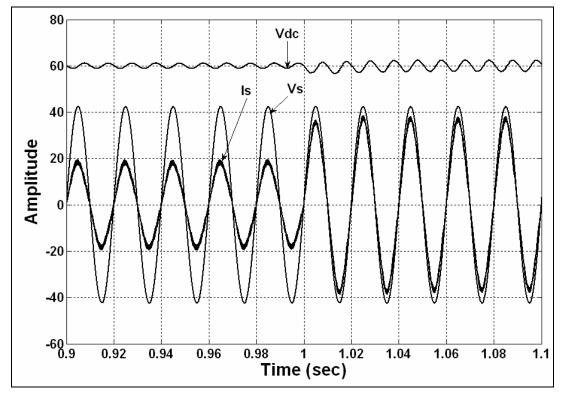

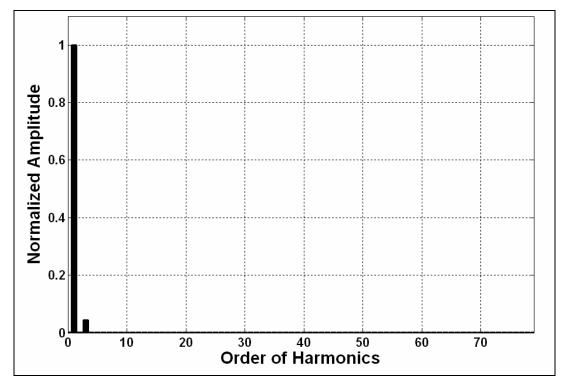

The converters can be classified according to supply system, devices used in the circuits and as per application. The general classification of ac-to-dc converter is shown in fig.1.2. The simulation of the single phase diode bridge rectifier is performed by considering various parameters according to the parameters of proposed front-end converter. The simulink model, waveforms for dc link voltage, source voltage and line

current and the result for the THD of the line current for diode bridge type ac-to-dc converter are shown in fig.1.3, 1.4 and 1.5 respectively.

Specifications of single phase diode bridge rectifier are:

- Input Voltage = 1432 Volts

- Output Voltage = 2000 Volts

- Supply Frequency = 60 Hz

- > DC Link Capacitor = 10000  $\mu$ F

- $\blacktriangleright$  Load Resistance = 40  $\Omega$

Fig.1.3 Simulink model of diode bridge rectifier

Fig.1.5 Normalized harmonic spectrum of line current for single phase diode bridge rectifier

#### Calculation of % THD:

% THD (Up to 11th Order) =

$$\sqrt{\frac{(0.9929)^2 + (0.9897)^2 + (0.985)^2 + (0.9786)^2 + (0.9708)^2 + (0.9614)}{(0.9506)^2 + (0.9383)^2 + (0.9246)^2 + (0.9096)^2 + (0.8934)^2 + (0.8759)}{(1)^2}}$$

% THD (Up to 25<sup>th</sup> Order) = 328.50%

#### **1.3 Literature Review**

Solid state ac-dc conversion of electric power [2] is widely used in adjustable-speed drives (ASDs), switch-mode power supplies (SMPSs), uninterrupted power supplies (UPSs), and utility interface with non conventional energy sources such as solar PV, etc., battery energy storage systems (BESSs), in process technology such as electroplating, welding units, etc., battery charging for electric vehicles, and power supplies for telecommunication systems, measurement and test equipments. Conventionally, ac-dc converters, which are also called rectifiers, are developed using diodes and thyristors to provide controlled and uncontrolled dc power with unidirectional and bidirectional power

flow. They have the demerits of poor power quality in terms of injected current harmonics, caused voltage distortion and poor power factor at input ac mains and slow varying rippled dc output at load end, low efficiency and large size of ac and dc filters. In light of their increased applications, a new breed of rectifiers has been developed using new solid state self commutating devices such as MOSFETs, insulated gate bipolar transistors (IGBTs), gate turn-off thyristors (GTO), etc., even some of which have either not been thought or not possible to be developed earlier using diodes and thyristors. Such pieces of equipment are generally known as converters, but specifically named as switchmode rectifiers (SMRs), power-factor correctors (PFCs), pulse width-modulation (PWM) rectifiers, multilevel rectifiers, etc. Because of strict requirement of power quality at input ac mains several standards have been developed and are being enforced on the consumers. Because of severity of power quality problems some other options such as passive filters, active filters (AFs), and hybrid filters along with conventional rectifiers, have been extensively developed especially in high power rating and already existing installations. However, these filters are quite costly, heavy, and bulky and have reasonable losses which reduce overall efficiency of the complete system. Even in some cases the rating of converter used in AF is almost close to the rating of the load. Under these observations, it is considered better option to include such converters as an inherent part of the system of ac-dc conversion, which provides reduced size, higher efficiency, and well controlled and regulated dc to provide comfortable and flexible operation of the system.

#### 1. Frank Flinders, Wardina Oghanna

In the paper titled "Simulation of a complex traction PWM rectifier using Simulink and the dynamic node technique" the authors describes This paper describes the development of a simulation model for an actual PWM converter system being used in train recently introduced to the Suburban rail transport system in Brisbane, Australia. The simulation model was developed as a teaching aid in modern traction drive technology for railway technical staff. The model is constructed using the SIMULINK graphical simulation platform.

#### 2. Thiyagarajah, K., Ranganathan, V.T., Iyengar, B.S.R.

In the paper titled "A high switching frequency IGBT PWM rectifier/ inverter system for AC motor drives operating from single phase supply" authors have explained a PWM rectifier/ inverter system using insulated gate- bipolar-transistors (IBGTs), capable of switching at 20 kHz is reported. The base drive circuit for the IGBT, incorporating short circuit protection is presented. The inverter uses Undeland snubber together with a simple energy recovery circuit, which ensures reliable and efficient operation even for 20 kHz switching. The front-end for the system is a regenerative single phase full-bridge IGBT inverter along with an ac reactor. Steady-state design considerations are explained and control techniques, for unity power factor operation and fast current control of the front-end converter, in a rotating as well as a stationary reference frame, are discussed.

#### 3. P.N. Tekwani, Dhaval Patel

In the paper titled "Design and Simulation of a PWM Regenerative Front-End Converter" authors presented the simulation results of a new control scheme for a pulse width modulation (PWM) rectifier which provides unity power factor as well as very low percentage of total harmonic distortion (THD) in ac supply side current. The design considerations for the proposed control scheme and the method of obtaining the PI controller tuning parameters are discussed. For the proposed control scheme, simulation results are obtained for various levels of loading, observing the output dc voltage ripple, unity power factor condition and harmonic content in ac side supply current. Both motoring (forward power flow) as well as regenerative (reverse power flow) mode of operation of the rectifier have been considered.

#### 4. Swami H.

In the paper titled **"Harmonic resistance emulator technique for single phase unity power factor correction"** author suggested a new technique (to be called as Harmonic Resistance Emulator) for single-phase power factor correction using the typical full-bridge active front-end converter is proposed. Unlike conventional single-phase power factor correction circuits, which make use of a single switch boost converter, this technique employs the full bridge converter to be operated in sine-triangle PWM (pulse width modulation) mode. Two schemes of the proposed technique are discussed. One is the input-current sensor less scheme and the other is input-voltage-sensor less scheme.

#### 5. Deur J., Peric N., stajic D.

In the paper titled "**Design of reduced-order feed forward controller**" authors presented the design of a linear, reduced-order, continuous or discrete-time feed forward controller (FFC) is presented. The FFC is located in the reference value branch of a linear feedback system of any order which is designed according to the damping optimum. The aim of the FFC is to decrease the control system reference response: time, while retaining a low overshoot and a well-damped form of the reference step response. This is achieved by locating the FFC zeros with the aid of the extended magnitude optimum, which is provided in the continuous or discrete-time variant. The influence of a sub optimally designed feedback system with a reduced-order feedback controller on feed forward control is analyzed.

#### 6. Ya-Gang Wang, Hui-He Shao

In the paper titled "Automatic tuning of optimal PI controllers" authors explains that the PI controller is unquestionably the most commonly used control algorithm in the process control industry. PI controllers have traditionally been tuned empirically, e.g. by the method described in Ziegler and Nichols. This method has the great advantage of requiring very little information about the process. There is, however, a significant disadvantage because the method inherently gives very poor damping. Hang modified Ziegler-Nichols tuning formula, which improve the performance of PI controllers. A method for auto tuning optimal PI controllers is proposed. The PI auto tuner first introduce relay feedback experiments to identify a second-order plus dead time mode1, PI controller is then designed based on the proposed robustness specification and integrated error optimum. Simulation examples show that the proposed PI auto tuner gives satisfactory performance for different types of processes.

#### 7. Hang, C.C. Astrom, K.J. Ho, W.K.

In the paper titled **"Refinements of the Ziegler-Nichols tuning formula"** authors reviewed the accuracy Ziegler-Nichols method in context of PID and PI auto tuning. For PID auto tuning, it will be shown that, for excessive overshoot in the set-point response, set-point weighting can be reduced the overshoot to the specific value, and the original Ziegler-Nichols tuning formula can be retrained. It will be also shown that set-point weighting is superior to the conventional solution of reducing large overshoot by gain detuning or set-point filtering. However, for excessive set-point under shoot, the tuning formula will have to be modified. For PI tuning it will be shown that the Ziegler-Nichols tuning formula is inadequate and has to be completely revised. The application of set-point weighting and modification of the tuning formula can be based simply on the knowledge of the normalized gain or normalized dead time of the process. These heuristic refinements, when incorporated, will give appreciable improvement in the performance of auto tuners.

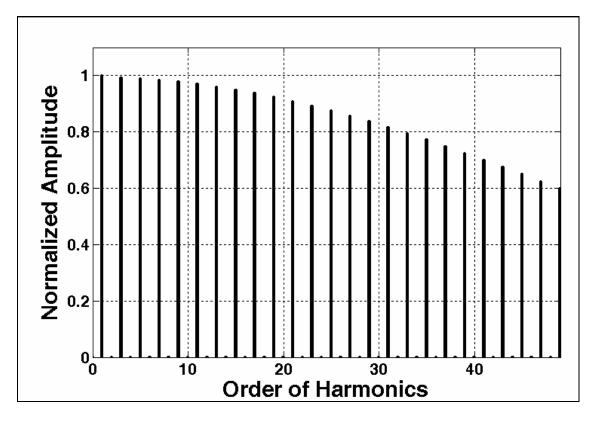

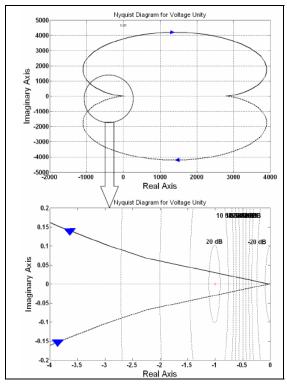

# CHAPTER-2 PROPOSED FRONT-END CONVERTER

The proposed front-end converter [3] with 8 IGBT structure is shown in fig.2.1. Two single-phase converters are connected in parallel. This is to reduce the harmonic currents in the mains as well as to improve the ripple contents at the dc link. Sine-triangular PWM is used for the control of the converters. Same sine reference waveform is used for both the converters. For each converter, leg-B triangular waveform is 180° phase shifted compared to that of leg-A for the same converter. Resultant converter output voltage for each converter is the subtracted PWM voltage waveform from the two converter legs ( $V_{AB} = V_{A0}-V_{B0}$ ). The outcome of that is fundamental gets added and the harmonics at the carrier frequency and its odd multiple get cancelled. Now the next higher harmonics are at the two times the carrier frequency.

For leg-A of converter-2 triangular wave is phase shifted by 90° compared to that of converter-1 so that harmonic frequencies around the second multiple of carrier wave gets cancelled. This is because harmonics at two times the carrier frequencies will be 180° phase shifted and hence flux produced by these cancel each other at the input transformer secondary side. So harmonic currents of two times the carrier frequency will not flow at the primary side and hence the higher order harmonic present at the primary side will be at the side bands of four times the carrier frequency (i.e., 4 x 11 x 60 Hz = 2640 Hz), with much reduced amplitudes as compared to the fundamental component.

#### 2.1 Design Specification for the Proposed Front-End Converter

- Input Voltage = 1432 Volts

- Output Voltage = 2800 Volts

- Supply Frequency = 50 Hz

- Switching Frequency, fsw = 60\*11 = 660 Hz

- $\blacktriangleright$  Rated Power = 1400 Kw

- > DC Link Capacitor = 9600  $\mu$ F

From the above details the detailed specifications can be given as, Input rms voltage, Vs (rms) = 1432 Volts

Fig.2.1 Proposed Front-End Converter

Input peak Voltage, Vs (peak) =  $\sqrt{2} \times Vs$  (rms) =  $\sqrt{2} \times 1432$ = 2025.1538Volts  $\cong$  2025Volts

Rated load current, Idc (Max) =  $\frac{P}{Vdc}$ =  $\frac{1400 \times 10^3}{2800}$ = 500 Amp

Assuming efficiency of the converter,  $\eta = 98 \%$ Rated rms input current, Is (max) rms  $= \frac{P}{Vs (rms) \times \eta}$  $= \frac{1400 \times 10^3}{1432 \times 0.98}$ = 997.61 Amp

Rated peak input current, Is(max)  $pk = \sqrt{2} \times Is(max) rms$ =  $\sqrt{2} \times 997.61$ = 1410.83 Amp

Assuming modulation index, m(max) = 0.8,

Maximum peak converter input voltage,

$$Vr (\max) pk = m (\max) \times Vdc$$

$$= 0.8 \times 2800$$

$$= 2240 Volts$$

Maximum rms converter input voltage,

$$Vr(\max) rms = \frac{Vr(\max) pk}{\sqrt{2}}$$

$$= \frac{2240}{\sqrt{2}}$$

$$= 1583.92 Volts$$

$$\cong 1584 Volts$$

Peak-to-peak ripple voltage,

$$\Delta V = 5\% of V dc = \frac{5}{100} \times 2800$$

$$= 140 Volts (p - p)$$

#### **2.2 Theoretical Considerations**

From the power schematic of proposed front-end converter shown in the fig.2.1, power balance equation at unity power factor is [4],

$$Vs Is = Vdc Id \tag{2.1}$$

As Id is summation of the current of converter -1 & 2, equation (2.1) can be re – written as

$$Vs Is = Vdc (Id1 + Id2)$$

$$(2.2)$$

$$\therefore Vdc = \frac{Vs \, Is}{Id1 + Id2} \tag{2.3}$$

From equation (2.3) it can observe that the Vdc is proportional to Is i.e. input current should be controlled to control the output voltage.

For the single phase system the voltage equation is,

$$Vs(t) = Ls \frac{di_s(t)}{dt} + Vr(t)$$

$$\therefore \frac{di_s(t)}{dt} = \frac{Vs(t) - Vr(t)}{Ls}$$

(2.4)

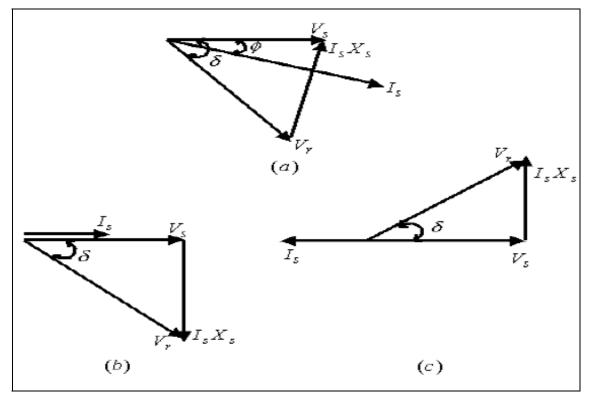

The input and output power must be balanced for dc link voltage should be remained constant. As shown in fig.2.2 taking three different cases for lagging and unity power factor for forward and reverse flow, it is observed that power flow depends on phase angle displacement between Vs & Vr.

Fig.2.2 Phasor diagram of front-end converter (a) Lagging PF (b) UPF forward power flow (c) UPF reverse power flow

From the fig. 2.2 (a),

$$Is\cos\Phi = \frac{Vr\sin\delta}{Xs}$$

(2.5)

$$Is\sin\Phi = \frac{(Vs - Vr\cos\delta)}{Xs}$$

(2.6)

If reactive power drawn by the system is zero, then power factor must be unity. Hence from the equation (2.5) & (2.6),

$$Is Xs = Vr \sin \delta$$

$$Vs = Vr \cos \delta$$

(2.7)

(2.8)

Where,

- Vr = RMS value of the fundamental component of voltage generated at the ac terminal of the inverter.

- Vs = RMS value of the ac supply voltage.

$\delta$  = Phase displacement angle between voltage phasor Vr & Vs.

$\Phi$  = Power factor angle.

Squaring the equations (2.7) & (2.8) and adding them,

$$Vr = \sqrt{Vs^2 + (Is\,Xs)^2} \tag{2.9}$$

Under the full load condition,

$$Vr_{fl} = Vs \sqrt{1 + \left(\frac{Is Xs}{Vs}\right)^2}$$

(2.10)

$$Vr_{fl} = Vs\sqrt{1 + X^2 p.u.}$$

(2.11)

Where

$$Xp.u. = \frac{Is_{fu} Xs}{Vs}$$

Equation (2.11) indicates that Vr > Vs by the factor  $\sqrt{1 + X^2 p.u.}$ , which is known as boost factor. So, the range of variation of value of Vr can be given as,

$$Vs \le Vr \le Vs\sqrt{1 + X^2 p.u.} \tag{2.12}$$

Value of  $L_s$  is selected in such a way that the maximum modulation index at which the inverter operates is as close to one. This is because under this condition  $V_r$  varies over a wide range making the control less sensitive to errors in the controller gains, components etc. The minimum value of modulation index m is decided by the fact that the minimum value of  $V_r$  is equal to  $V_s$ ; i.e.

$$m_{\min} = \frac{Vs}{Vdc / \sqrt{2}}$$

$$m_{\min} = \frac{\sqrt{2} Vs}{Vdc}$$

(2.13)

Value of Ls is selected in such a way that the maximum modulation index at which the inverter operates is as close to one. This is because under this condition Vr varies over a wide range making the control less sensitive to errors in the controller gains, components etc. If a very low value of Ls selected than variation of Vr becomes very sensitive to the above errors.

Input source inductance Ls from equation (2.9) is,

$$mVdc = Vr_{pk}$$

$$= \sqrt{Vs_{pk}^{2} + (Is_{pk} Xs)^{2}}$$

$$= \sqrt{Vs^{2} + Is_{pk}^{2} \omega^{2} Ls^{2}}$$

$$\therefore Ls = \sqrt{\frac{Vr_{pk}^{2} - Vs_{pk}^{2}}{Is_{pk}^{2} \omega^{2}}}$$

(2.14)

Substituting the various values in equation (2.14) to find the value of Ls,

$$Ls = \sqrt{\frac{(2240)^2 - (2025)^2}{(2 \times \Pi \times 60)^2 (1410)^2}}$$

$$\therefore Ls = 1.8015 \, mH$$

For the analysis of control, converter is modeled as a first order lag. Converter transfer

function can be given as;  $\frac{G}{1+sTr}$  where,  $Tr = triangular carrier period = <math>\frac{1}{11 \times 60} = 1.515 \times 10^{-3} ms$ . G = mVdc = 2240 m = 0.8 (::  $m = mod \, ulation \, index$   $= max \, i. \, amplitude \, of \, \sin r \, reference / \, amplitude \, of \, triangular \, carrier$  = 1/1.25)  $Vdc = \frac{2240}{0.8} = 2800 \, Volts$

# CHAPTER-3 DESIGN OF CONTROL LOOPS

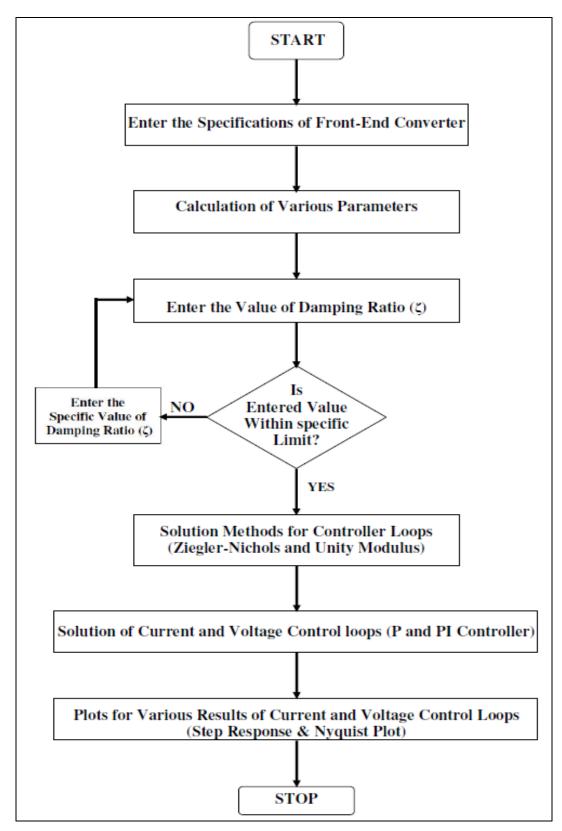

There are two control loops i.e. current control loop and voltage control loop. In the control strategy there is a faster inner current control loop and outer voltage control loop. The output dc voltage is controlled by matching the input power from the converter to the output power demand from the load, while maintaining unity power factor at all the loads. Another technique named Harmonic Resistance Emulator can also be used for the single phase power factor correction [5]. A stationary reference frame model is used for the simulation study, as it involves with only fixed frequency operation. The outer voltage loop is working with DC quantities and the inner current loop is working with sinusoidal quantities. The reference sine wave for the inner current control is derived from the input mains.

While designing the control loops the two methods are used for finding the gain of current control loop and gain and integration time of PI controller in voltage control loop. The cases are taken for the under damped, critically damped and over damped system. The considered methods are:

- (1) Unity modulus method

- (2) Ziegler- Nichols method

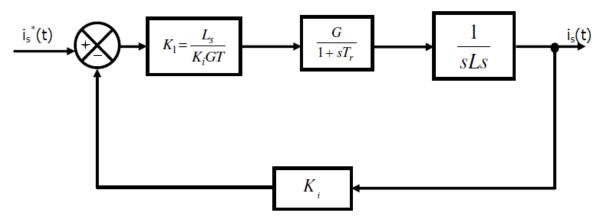

#### 3.1 Current Control Loop Design

If the desired response of current loop is a first order lag of T, then the dynamics of current loop can be described by,

$$T\left(\frac{d\,i_s(t)}{dt}\right) + i_s(t) = \frac{i_s *(t)}{ki}$$

(3.1)

Where,

T = lag of the converter according to the switching frequency

Ki = current feed back gain

\* = Reference value

Equation (15) can be re-written as,

$$\left(\frac{di_s(t)}{dt}\right) = \frac{\frac{i_s *(t)}{ki} - i_s(t)}{T}$$

(3.2)

This phase lag can be compensated for by introducing a corresponding phase lead for the current reference, is\*(t). In our design it comes out to be  $\arctan\omega T = \arctan(2x\pi x 60x2x1.515X10-3) = 0.85$  radian.

Comparing equations (2.4) & (3.2),

$$\frac{Vs(t) - Vr(t)}{Ls} = \frac{\frac{i_s *(t)}{ki} - i_s(t)}{T}$$

$$Vs(t) - Vr^*(t)G = \frac{Ls}{KiT} [is^*(t) - is(t) \cdot Ki]$$

$$Vr^*(t) = \frac{Vs(t)}{G} - \frac{Ls}{KiGT} [is^*(t) - is(t) \cdot Ki]$$

(3.3)

As inner current loop should be operating faster (i.e., respond to change in is (t)),  $\frac{Vs(t)}{G}$  should be a feed forward component in the current control loop.

Fig.3.1 Block schematic of current control loop

(3.4)

Fig.3.1 shows the block diagram representation of the current control loop. Current control loop transfer function can be given as:

$$\frac{is}{is^*} = \frac{\frac{1}{Ki}}{S^2 T Tr + S T + 1}$$

$$\frac{is}{is^{*}} = \frac{\frac{1}{Ki}}{S^{2} + \frac{1}{Tr}S + \frac{1}{TTr}}$$

(3.5)

The standard form of second order equation is given by,

$$\frac{C(s)}{R(s)} = \frac{\omega n^2}{S^2 + 2\xi \omega n + \omega n^2}$$

(3.6)

Comparing equations (3.5) & (3.6),

$$\omega n^2 = \frac{1}{T \, Tr} \tag{3.7}$$

$$2\xi\omega n = \frac{1}{Tr}$$

(3.8)

If considered reference current amplitude = 1, then

$$Ki = \frac{1}{Rated Peak Current}$$

$$\therefore Ki = \frac{1}{1410}$$

(3.9)

From the above the gain of the current control loop for various cases of the system can be obtained. The equation for finding the same is,

$$K1 = \frac{Ls}{Ki \, G \, T} \tag{3.10}$$

#### **3.2 PI Controller**

The PI controller is unquestionably the most commonly used control algorithm in the control industry. In the control strategy of the proposed converter the parameters of the PI controller have been found with the help of traditional Ziegler-Nichols method and Unity Modulus (Magnitude optimum method).

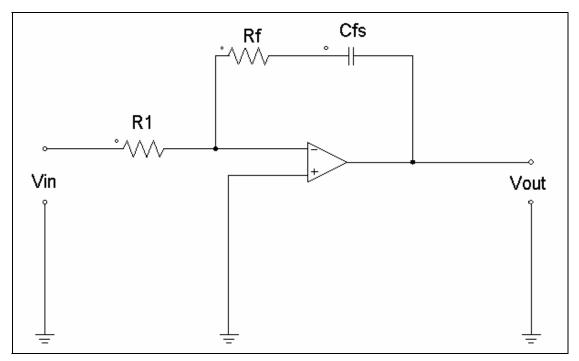

The fig.3.2 shows the model of the PI controller [6] for the proposed converter. The block diagram representation of the same is shown in fig.3.3.

Fig.3.2 PI Controller in S domain

Fig.3.3 Block diagram of PI controller

From the model and block diagram representation, the transfer function for the PI controller can be written as,

$$\frac{Vo(s)}{Vin(s)} = \frac{R_f}{R_1} + \frac{1}{R_1 C_F s}$$

$$= Kn + \frac{1}{Ti s}$$

Where,

$Kn = Proportional \ gain = R_f/R_1$

$Ti = Time \ constant = R_1 C_f$

$$\therefore \frac{Vo(s)}{Vin(s)} = Kn \left[ 1 + \frac{1}{Kn Ti s} \right]$$

$$= Kn \left[ 1 + \frac{1}{\frac{R_f}{R_1} R_1 C_f s} \right]$$

$$= Kn \left[ 1 + \frac{1}{R_f C_f s} \right]$$

$$= Kn \left[ 1 + \frac{1}{Tn s} \right]$$

$$\therefore \frac{Vo(s)}{Vin(s)} = Kn \left[ \frac{1 + s Tn}{s Tn} \right]$$

Where,  $Tn = R_f C_f$

By adjusting Kn and Tn, the steady state error can be controlled and the output can be obtained accordingly.

#### 3.3 Voltage Control Loop Design

As T is greater then Tr neglecting the term  $S^2TTr$  of equation (3.4). So equation (3.4) will become,

$$\frac{is}{is^*} = \frac{\frac{1}{Ki}}{1+sT}$$

(3.11)

Also considered the worst case for designing the voltage loop that is load is thrown off. From fig.3.4 the transfer function of the voltage control loop is given by,

$$\frac{Vdc}{Vdc^*} = \frac{\left(\sqrt{2} Vs Tn Kn\right)s + \sqrt{2} Vs Kn}{\left(Ki Tn T 2 Vdc C\right)S^3 + \left(Ki Tn 2 Vdc C\right)S^2 + \left(Kn Kv \sqrt{2}Vs Tn\right)S + Kn Kv \sqrt{2}Vs}$$

(3.12)

The solution of the above equation, which is a third order, is given by two methods.

#### (1) Unity Modulus Method:

The unity modulus method is also known as the magnitude optimum method. The aim of this method is to decrease the rise time of the control system reference step response, while retaining a low overshoot and well-damped form of the reference step response and also retaining its optimal quasia periodic form. In such method it is assumed that all the zeros of the feedback system transfer function is stable and well dumped and therefore be cancelled by the poles [7].

For a general third order transfer function equation, as given below, to get the modulus of the transfer function as unity, to arrive on some conditions.

Fig.3.4 Block schematic of Voltage control loop

$$F(j\omega) = \frac{b_0 + j\omega b_1}{a_0 + j\omega a_1 + (j\omega)^2 a_2 + (j\omega)^3 a_3}$$

(3.13)

For low frequencies following two conditions considered for getting unity modulus of the transfer function.

$$b_0 = a_0$$

(3.14)

$$b_1 = a_1$$

(3.15)

Equation (27) can be rewritten as,

$$F(j\omega) = \frac{a_0 + j\omega a_1}{a_0 + j\omega a_1 - \omega^2 a_2 - j\omega^3 a_3}$$

(3.16)

$$\therefore F(j\omega) = \frac{a_0 + j\omega a_1}{a_0 - \omega^2 a_2 + j\omega(a_1 - \omega^2 a_3)}$$

$$\therefore |F(j\omega)| = \sqrt{\frac{a_0^2 + \omega^2 a_1^2}{a_0^2 + \omega^2 (a_1^2 - 2a_0 a_2) + \omega^4 (a_2^2 - 2a_1 a_3) + \omega_6 a_3^2}}$$

(3.17)

So here to satisfy the requirement of unity modulus, from equation (3.17), two more conditions are obtained in addition to equation (3.14) and (3.15). The conditions are:

$$a_1^2 = 2a_0 a_2 \tag{3.18}$$

$$a_2^2 = 2a_1 a_3 \tag{3.19}$$

Ultimately the following equation is obtained for modulus of transfer function.

$$|F(j\omega)| = \sqrt{\frac{1 + \omega^2 \left(\frac{a_1}{a_0}\right)^2}{1 + \omega^6 \left(\frac{a_3}{a_0}\right)^2}}$$

(3.20)

Now, from equations (3.12), and (3.19) the relation between the PI controller gain and time parameters for the voltage control loop can be obtained.

$$\left( Kn \ Kv \ \sqrt{2} \ Vs \ Tn \right)^2 = 2 \left( \sqrt{2} \ Vs \ Kn \ Kv \right) (2 \ Vdc \ Ki \ Tn \ C)$$

$$\therefore \ Kn = \frac{4 \ Vdc \ Ki \ C}{\sqrt{2} \ Kv \ Tn \ Vs}$$

$$\therefore \ Kn = \frac{0.11}{Tn}$$

(3.21)

And from equations (3.12), (3.18), and (3.21) the PI controller gain and time parameters for the voltage control loop are calculated.

$$(2Vdc \ Ki \ Tn \ C)^2 = 2 \left(2Vdc \ Ki \ Tn \ T \ C\right) \left(Kn \ Kv \ \sqrt{2} \ Vs \ Tn\right)$$

$$\therefore Kn = \frac{0.02746}{T}$$

(3.22)

#### (2) Ziegler-Nichols Method:

PI controllers have traditionally been tuned by Ziegler-Nichols method. The method has great advantage of requiring very little information about the plant or process. There is however, a significant disadvantage because the method inherently gives poor damping [8]-[9].

In Ziegler-Nichols method first it is considered that time for the integration is infinite i.e.  $Tn = \infty$  and Td = 0. Now increase the gain of the controller, Kn from 0 to a critical value, Kcr at which the output first exhibit the sustained oscillation. Thus the value of critical gain and the corresponding period Pcr are approximately determined. Ziegler-Nichols suggested the set of values as shown in table-3.1 [10].

| Type of controller | Kn       | Tn                  | Td |

|--------------------|----------|---------------------|----|

| Р                  | 0.5 Kcr  | 0                   | 0  |

| PI                 | 0.45 Kcr | $\frac{1}{1.2}$ Pcr | 0  |

Table 3.1 Ziegler-Nichols rules for tuning the PID controller

Now as the  $K_n$  and  $T_n$  are the parameters of the PI controller of proposed converter, the relationship should be established between values coming from the Ziegler-Nichols method in required form. So a relationship is developed between the both parameters values. As per the rule Ziegler-Nichols method  $T_i = \infty$ . If  $T_i = \infty$  in PI controller than either  $R_1 = \infty$  or  $C_f = \infty$ . But assumption for  $R_1 = \infty$  is not proper because if  $R_1 = \infty$  then  $K_n = 0$ , which wrong and hence let us assume that  $C_f = \infty$ . By this assumption it is observed that  $K_n = K_p$ .

Now,

$$T_i = R_1 C_f \text{ and } T_n = R_f C_f$$

Taking the ratio of the both parameters,

$$T_n = K_n T_i$$

Which is the relationship between the integration time as per requirement.

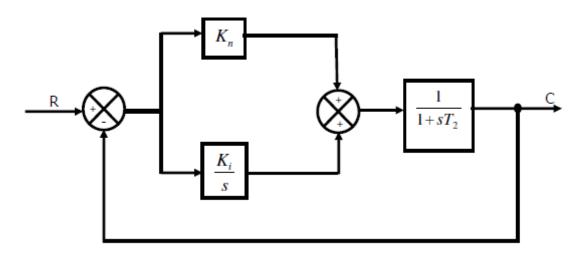

By applying such method the voltage block of the fig. 3.4 reduced as shown in fig.3.5.

Fig.3.5 Block schematic of Voltage control loop from Ziegler-Nichols Method

The solution of the voltage control loop in the form of transfer function is given as,

$$\frac{Vdc}{Vdc^*} = \frac{\sqrt{2}Vs\ Kn}{(2Vdc\ Ki\ C\ T\ )S^2 + (2Vdc\ C\ Ki\ )S + \sqrt{2}\ Vs\ Kn\ Kv}$$

(3.23)

Substituting values of known parameters in above equation,

$$0.3972 T S^{2} + 0.3972 S + 0.7233 Kn = 0$$

(3.24)

Compare equation (3.24) with standard characteristic equation.

From the equation (3.24) the critical gain of the system can be found. The gain of the voltage control loop can found as per rules of table-3.1. To find the integration time Tn, the following equation should be used,

$$Tn = \frac{1}{1.2} Pcr$$

$$\therefore Tn = \frac{1}{1.2} \left( \frac{2\Pi}{\omega_n} \right)$$

(3.25)

Taking the various values of the damping ratio, § and accordingly find the various parameters for current and voltage control loop from equations (3.7), (3.8), (3.10), (3.23), (3.24) & (3.25). The results obtained for the different values of damping ratio and different values of parameters from both methods are tabulated in table-3.2.

| Type Of the System                       | Values of PI Controller Parameters |                |                           |                |

|------------------------------------------|------------------------------------|----------------|---------------------------|----------------|

|                                          | Unity Modulus<br>Method            |                | Ziegler-Nichols<br>Method |                |

|                                          | K <sub>n</sub>                     | T <sub>n</sub> | K <sub>n</sub>            | T <sub>n</sub> |

| Under Damped System ( $\zeta = 0.707$ )  | 9.06                               | 0.01214        | 4.08                      | 0.0914         |

| Critically Damped System ( $\zeta = 1$ ) | 4.5307                             | 0.02428        | 1.1989                    | 0.0647         |

| Over Damped System ( $\zeta = 1.2$ )     | 3.1463                             | 0.03496        | 0.4917                    | 0.0539         |

Table 3.2 Comparison of PI controller parameters for voltage control Loop

In proposed converter the value of capacitor is taken as 9600  $\mu F\approx 10000~\mu F.$  Value of the capacitor can be calculated as shown below:

From the power balance equation,

$$V_{r}(t)i_{s}(t) = V_{dc}I_{d}$$

$$\therefore I_{d} = \frac{V_{r}(t)i_{s}(t)}{V_{dc}}$$

$$\therefore I_{d} = \frac{V_{r}\sin(\omega t - \delta)i_{s}\sin(\omega t)}{V_{dc}}$$

$$\therefore I_{d} = \frac{V_{r}i_{s}}{2V_{dc}}\left[\cos\delta - \cos(\omega t - \delta)\right]$$

(3.26)

The equation (3.26) has a dc component and a fluctuating component. This second harmonic current should pass through the filter capacitor such that the voltage ripple  $\Delta V$  should be 5 % of V<sub>dc</sub>. Hence,

$$\Delta V \ge \frac{Vr Is}{2Vdc \ 2 \ \omega C}$$

$$\therefore C \ge \frac{Vr Is}{4 \times 2\pi f \times Vdc \ \Delta V}$$

$$\ge \frac{mVdc Is}{4 \times 2\pi f \times Vdc \ \Delta V}$$

$$\ge \frac{m Is}{4 \times 2\pi f \times \Delta V}$$

$$\ge \frac{0.81410}{4 \times 2\pi \times 60 \times 140}$$

C is taken as =  $10000 \ \mu F$

Fig. 3.6 shows the block schematic of voltage regulation scheme with current control in stationary co-ordinates.

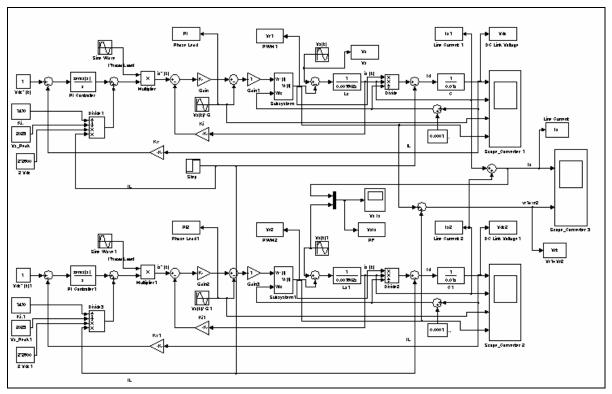

# CHAPTER-4 SIMULATION AND MATLAB PROGRAMMING RESULTS OF PROPOSED CONVERTER

The simulation for the proposed front-end converter is performed by using mathematical model in Matlab Simulink. The results are obtained with the help of both the methods i.e. Unity Modulus (Magnitude Optimum) method and Ziegler-Nichols method under transient and dynamic conditions considering under damped, critically damped and over damped system. The simulation results are obtained for motoring (forward) mode of operation, regenerative (reverse) mode and under the fault condition. The

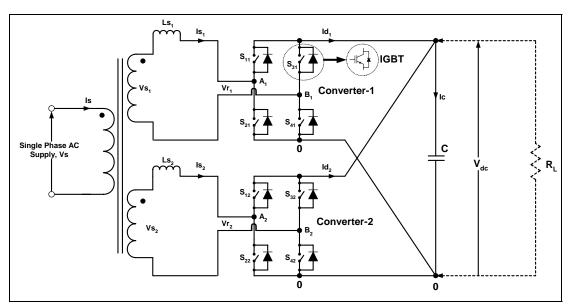

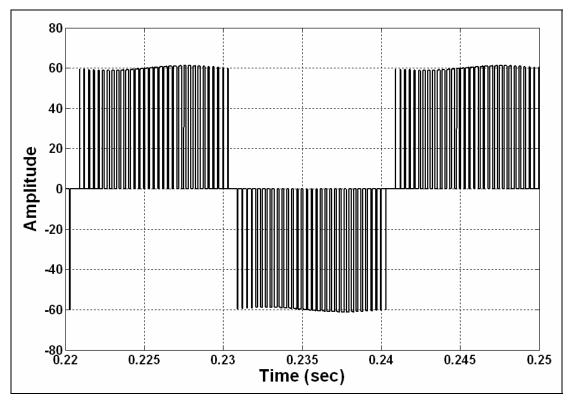

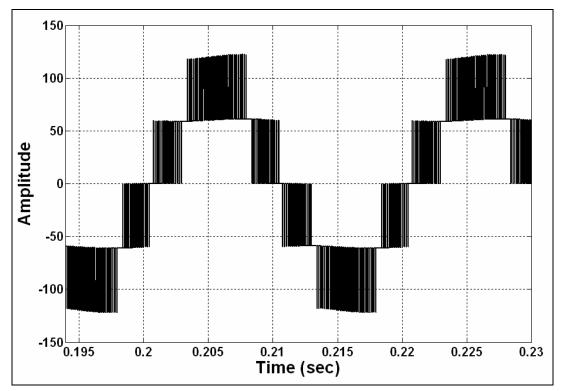

### 4.1 Simulation Results for PWM Switching

The proposed front-end converter mathematical model of simulation and PWM switching waveforms for one converter and for both the converters are shown in fig. 4.1, 4.2 and 4.3 respectively. Sine-triangular PWM is used for the control of the converters. Same sine reference waveform is used for both the converters. For each converter, leg-B triangular waveform is 180° phase shifted compared to that of leg-A for the same converter. For leg-A of converter-2 triangular wave is phase shifted by 90° compared to that of converter-1 so that harmonic frequencies around the second multiple of carrier wave gets cancelled.

Fig.4.1 Simulation blocks of mathematical model for front-end converter

Fig.4.3 Voltage waveform  $V_{AB} = V_{A1B1} + V_{A2B2}$  (i.e.  $V_r$ ) (scale: X-axis:1div. = 0.005 s, Y-axis: 1div. = 2000 V)

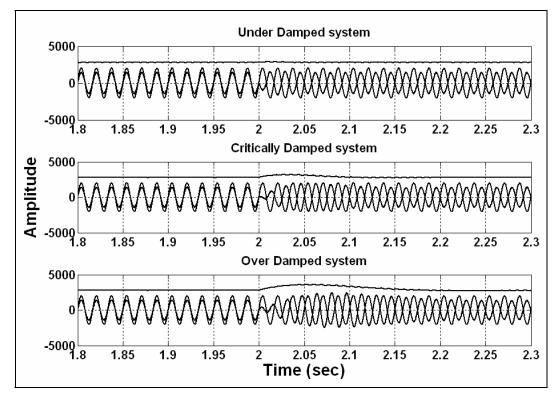

### 4.2 Simulation Results for Transient Condition

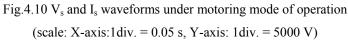

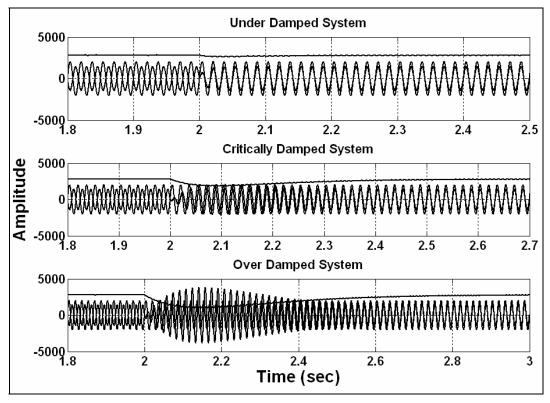

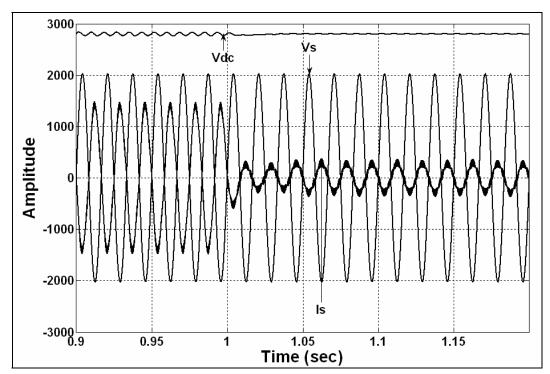

The simulation results are obtained for the transient condition for motoring and regenerative mode of operation as shown in fig. 4.4 to fig. 4.11. It can be observed that during the motoring and regenerative operation the unity power factor is maintained for under damped, critically damped and over damped system. The results obtained from both the methods are shown below.

# A) Unity Modulus Method:

Fig.4.4  $V_{dc}$ ,  $I_s \& V_r$  (total) waveforms of the proposed converter for under damped system (Unity Modulus

Fig.4.5  $V_{dc}$ ,  $I_s \& V_r$  (total) waveforms of the proposed converter for critically damped system (Unity Modulus method)

Fig.4.6  $V_{dc}$ ,  $I_s$  &  $V_r$  (total) waveforms of the proposed converter for over damped system (Unity Modulus

method)

#### **B)** Zeigler-Nichols Method:

Fig. 4.7 V<sub>dc</sub>, I<sub>s</sub> & V<sub>r</sub> (total) waveforms of the proposed converter for under damped system (Ziegler-Nichols method)

Fig. 4.8  $V_{dc}$ ,  $I_s \& V_r$  (total) waveforms of the proposed converter for critically damped system (Ziegler-Nichols method)

Fig. 4.9  $V_{dc}$ ,  $I_s \& V_r$  (total) waveforms of the proposed converter for over damped system (Ziegler-Nichols method)

Fig.4.11 V<sub>s</sub> and I<sub>s</sub> waveforms under regenerative mode of operation (scale: X-axis:1div. = 0.05 s, Y-axis: 1div. = 5000 V)

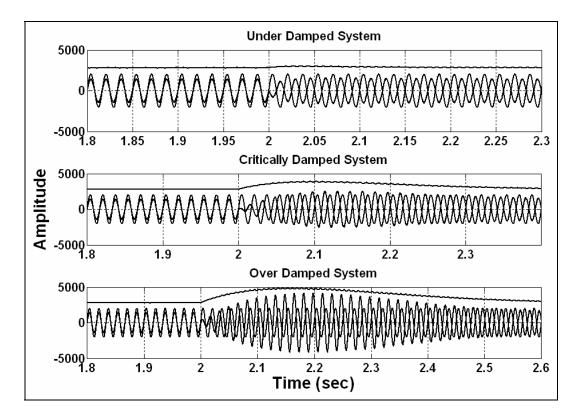

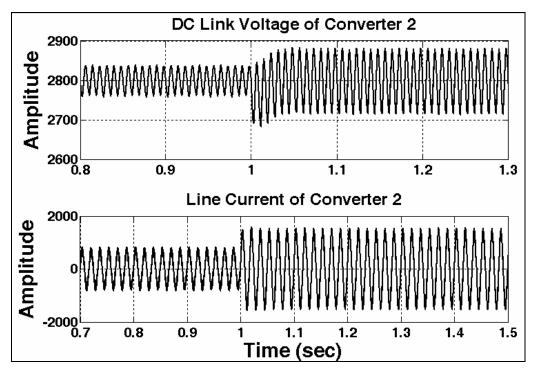

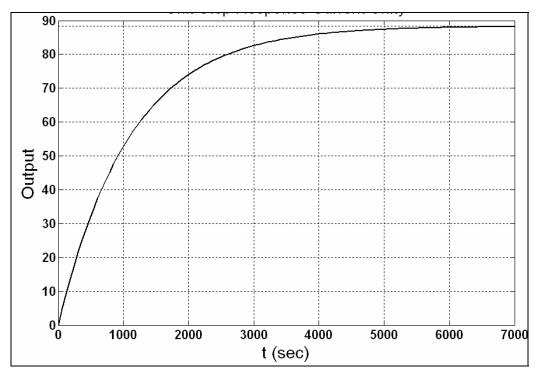

### 4.3 Simulation Results for Dynamic Condition

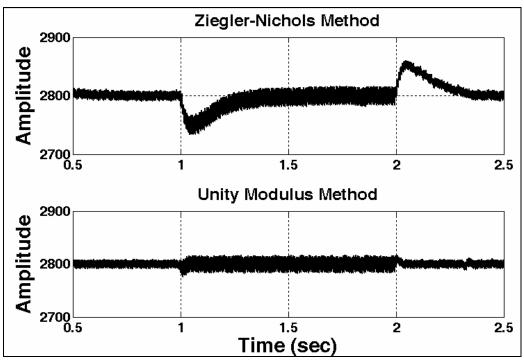

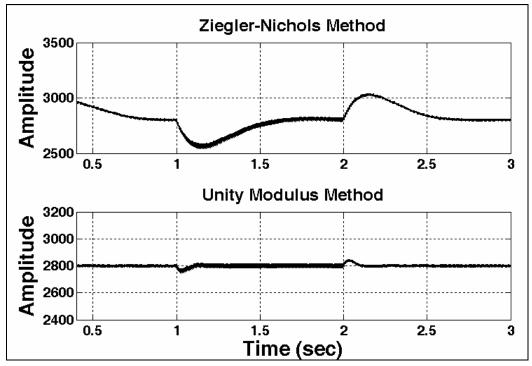

The simulation results are obtained for the dynamic condition having under damped, critically damped and over damped conditions. The results are compared for the Ziegler-Nichols and Unity Modulus method. The obtained results are shown in fig. 4.12 to fig.4.15. From the comparison it is quite evident that under the dynamic condition the stability of dc link voltage from Unity Modulus method is better than the Ziegler-Nichols method.

Fig.4.12 Waveforms of dc link voltage for under damped system (scale: X-axis:1div. = 0.5 s, Y-axis: 1div. = 100 V)

Fig.4.13 Waveforms of dc link voltage for critically damped system (scale: X-axis:1div. = 0.5 s, Y-axis: 1div. = 200 V)

Fig.4.15  $V_{dc}$ ,  $V_s$  and  $I_s$  waveforms for under motoring to regenerative mode of operation (scale: X-axis:1div.= 0.05 s, Y-axis: 1div. = 1000 V)

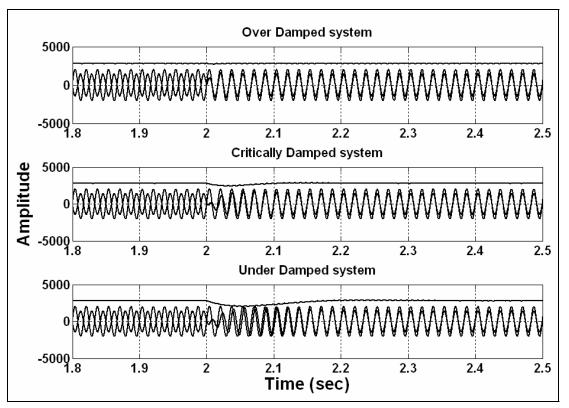

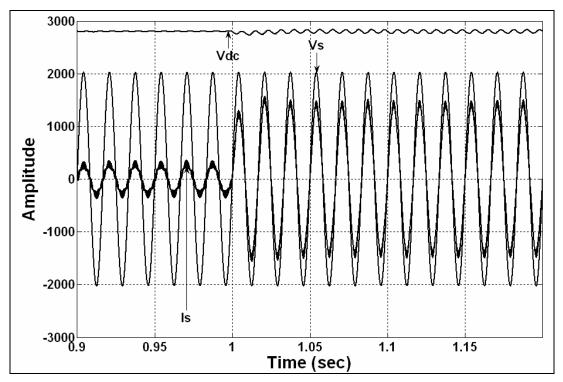

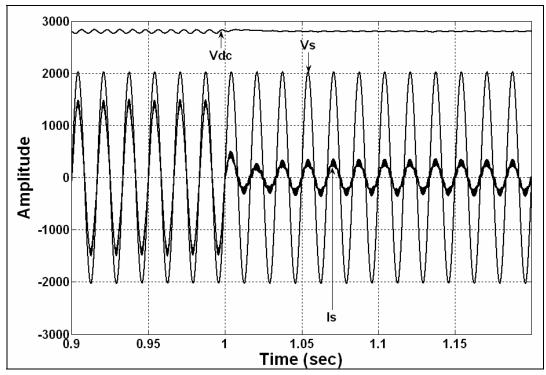

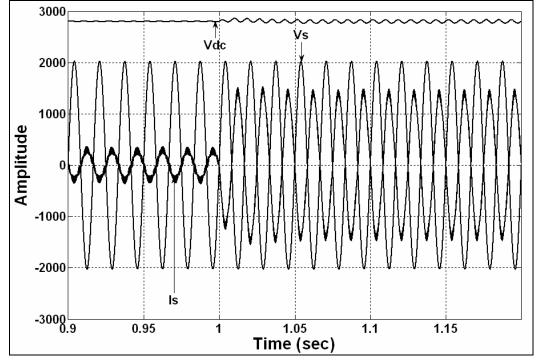

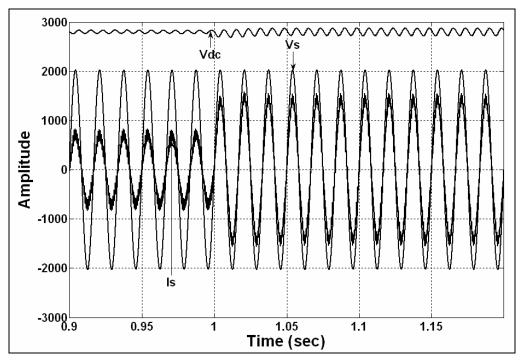

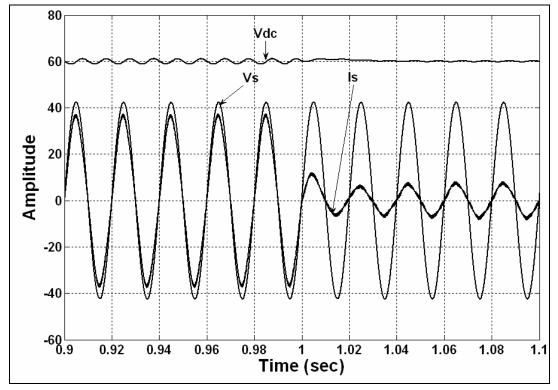

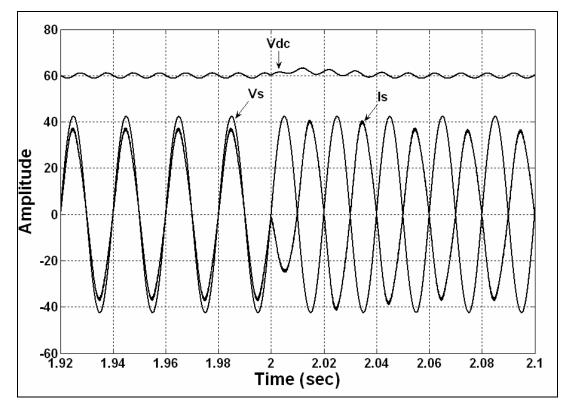

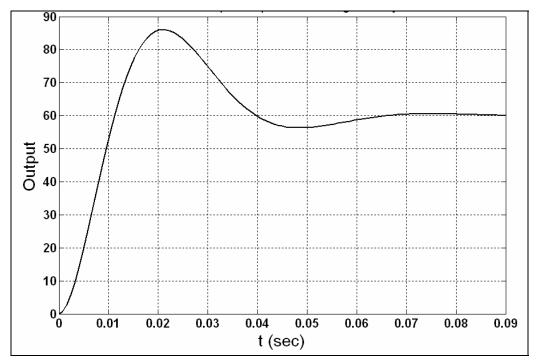

#### 4.4 Simulation Results for Transition Mode of Operation

The simulation results for proposed front-end converter for the transition mode of operation i.e. motoring to regenerative and vice-versa under transient condition are obtained form both the methods i.e. Zeigler-Nichols method and Unity Modulus method. The obtained results are shown in fig. 4.16 to 4.19. The results are indicating that the unity power factor is maintained during all the conditions for motoring mode of operation and the results of the Unity Modulus method are better than the Ziegler-Nichols method.

Fig. 4.16 Vdc, Vs and Is waveforms for transition from motoring to regenerative mode of operation (Unity Modulus Method) (scale: X-axis:1div. = 0.05 s, Y-axis: 1div. = 5000 V)

Fig. 4.17 Vdc, Vs and Is waveforms for transition from motoring to regenerative mode of operation (Zeigler-Nichols Method) (scale: X-axis:1div. = 0.1 s, Y-axis: 1div. = 5000 V)

Fig. 4.18 Vdc, Vs and Is waveforms for transition from regenerative to motoring mode of operation (Unity Modulus Method) (scale: X-axis:1div. = 0.1s, Y-axis: 1div. = 5000 V)

Fig. 4.19 Vdc, Vs and Is waveforms for transition from regenerative to motoring mode of operation (Zeigler-Nichols Method) (scale: X-axis:1div. = 0.1s, Y-axis: 1div. = 5000 V)

#### 4.5 Simulation Results for Different Load Conditions

The simulation results are obtained for the different load conditions for the proposed front-end converter. The simulation results are obtained for both the methods i.e. Unity Modulus are Ziegler-Nichols, here only results from Unity Modulus method is shown, as from the above results it is evident that the results from the unity modulus method is method is much better and stable then the Ziegler-Nichols method. The results for the same are shown in fig. 4.20 to 4.23.

Fig. 4.20  $V_{dc}$ ,  $V_s$  and  $I_s$  waveforms from no load to full load under forward (motoring) mode of operation (scale: X-axis: 1div. = 0.05s, Y-axis: 1div. = 1000 V)

Fig. 4.21  $V_{dc}$ ,  $V_s$  and  $I_s$  waveforms from full load to no load under motoring mode of operation (scale: X-axis: 1div. = 0.05s, Y-axis: 1div. = 1000 V)

Fig. 4.22  $V_{dc}$ ,  $V_s$  and  $I_s$  waveforms from no load to full load under reverse (regenerative) mode of operation (scale: X-axis: 1div. = 0.05s, Y-axis: 1div. = 1000 V)

Fig. 4.23  $V_{dc}$ ,  $V_s$  and  $I_s$  waveforms from full load to no load under regenerative mode of operation (scale: X-axis: 1div.= 0.05 s, Y-axis: 1div. = 1000 V)

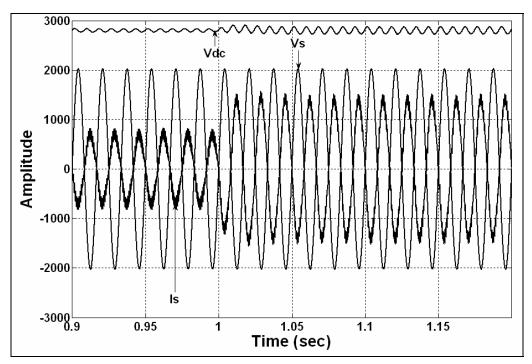

#### 4.6 Simulation Results for Fault Condition

For the proposed front-end converter simulation results are also obtained under the fault condition. The simulation result for the transient condition of the system and considering Unity Modulus method only. The obtained simulation results are shown in fig. 4.24 to 4.26. The results are indicating that the unity power factor is maintained during fault condition. The simulation results are obtained for the motoring mode of operation and regenerative mode of operation, considering the transient condition of the system and Unity Modulus method. From the simulation result it is observed that the during the fault condition for both the motoring and regenerative mode of operation the unity power factor is maintained at the supply side.

Fig. 4.24 Waveforms of dc link voltage and line current for under damped system during fault condition