## Development of Firmware Support Package BIOS for Next Generation Processors

#### **Major Project Report**

Submitted in partial fulfillment of the requirements

For the degree of

**Master of Technology**

in

Electronics & Communication Engineering (Communication Engineering)

> By Niravkumar T. Rajpara (14MECC17)

Electronics & Communication Engineering Branch Electrical Engineering Department Institute of Technology Nirma University Ahmedabad - 382 481 May 2016

## Development of Firmware Support Package BIOS for Next Generation Processors

#### **Major Project Report**

Submitted in partial fulfillment of the requirements

for the degree of

**Master of Technology**

in

Electronics & Communication Engineering (Communication Engineering)

By

Niravkumar T. Rajpara

#### (**14MECC17**)

Under the Guidance of

Mr. Satya P. Yarlagadda Sr. BIOS Engineer, Intel Technology Pvt. Ltd., Bangalore Dr. D. A. Pujara Elec. & Comm. Department, Nirma University, Ahmedabad

Electronics & Communication Engineering Branch Electrical Engineering Department Institute of Technology Nirma University Ahmedabad - 382 481 May 2016

# Declaration

This is to certify that,

- 1. The thesis comprises my original work towards the degree of Master of Technology in Communication Engineering at Institute of Technology,Nirma University and has not been submitted elsewhere for a degree.

- 2. Due acknowledgement has been made in the text to all other material used.

Rajpara Niravkumar T.

# Certificate

This is to certify that the major project entitled "Development of Firmware Suppport Package BIOS for Next Generation Processors" submitted by Rajpara Niravkumar T. (Roll No: 14MECC17), towards the partial fulfillment of the requirements for the award of degree of Master of Technology in Electronics and Communication Engineering of Nirma University, Ahmedabad, is the record of work carried out by him under my supervision and guidance. In my opinion, the submitted work has reached a level required for being accepted for examination. The results embodied in this major project, to the best of my knowledge, haven't been submitted to any other university or institution for award of any degree or diploma.

Date:

Guide

Place: Ahemdabad

**Program Coordinator**

Dr. D. A. Pujara (Professor, EC) Dr. D. K. Kothari (Professor, EC)

#### **HOD & Director**

Dr. P. N. Tekwani (Head of EE Department, Director, IT-NU)

# Certificate

This is to certify that the major project entitled "Development of Firmware Suppport Package BIOS for Next Generation Processors" submitted by Rajpara Niravkumar T. (Roll No: 14MECC17), towards the partial fulfillment of the requirements for the award of degree of Master of Technology in Electronics and Communication Engineering of Nirma University, Ahmedabad, is the record of work carried out by him under my supervision and guidance. In my opinion, the submitted work has reached a level required for being accepted for examination. The results embodied in this major project, to the best of my knowledge, haven't been submitted to any other university or institution for award of any degree or diploma.

Date:

Place: Bangalore

Guide

Mr. Satya P. Yarlagadda (Guide, Intel Technology Pvt. Ltd.) Manager

Mr. Bimod Narayanan (Manager, Intel Technology Pvt. Ltd

# Acknowledgements

I would like to express my heartedly thanks to following peoples who were able to give their willingness to help, for their unwavering and undying support, encouragement and precious time for accomplishment of this report.

First of all I would like to thank **Prof. Dr. D. A. Pujara (Internal Guide)**, M.Tech. Communication and **Mr. Satya P. Yarlagadda (External Guide)**, **Sr. BIOS Engineer**, **Intel Technology Pvt. Ltd.** for support, advice, guidance, valuable comments, suggestions that benefited in the success of this project. I would also like to thank **Prof. Dr. P. N. Tekwani, Head of Electrical Engineering Department** and **Prof. D. K. Kothari (Program Coordinator)**, M.Tech. Communication for allowing me to this thesis work and for giving me encouragement. I would like to thank **Prof. Dr. P. N. Tekwani, Director, Institute of Technology, Nirma University** for his encouragement during project work.

I am extremely thankful to Mr. Bimod Narayanan (Manager), Component BIOS Engineering, Intel Technology Pvt. Ltd. who allowed me to enrich my skills in Intel Technology Pvt. Ltd.

Last but not the least, I would also like to give credit to my all BIOS development team members, my family and my friends who helped me a lot by giving guidance and support throughout this project training.

> - Niravkumar T. Rajpara 14MECC17

## Abstract

This thesis mainly presents a discussion about the Firmware Support Package BIOS. In broader view, Firmware Support Package Basic Input Output System is the binary distribution of necessary Intel Silicon initialization code which provide access to programming information which is not publicly available. The research work described in the thesis is mainly focused on improving the performance of BIOS and flexibility to the users to use any open source boot loaders.

Basically the BIOS in modern PCs is to initialize and test the system hardware components, and to load a boot loader or an operating system from a mass memory device which is used for silicon initialization. It act as a layer between OS and hardware to initialize and interface and finally loads boot loader to give control to OS and BIOS played supporting hardware role for the devices. The FSP provides chipset and processor initialization in a format that can easily be incorporated into many existing boot loaders. The first design goal of FSP is to provide access to the key programming information that is open source. The second design goal is to abstract the complexities of Intel Silicon initialization and expose a limited number of well-defined interfaces. A fundamental design philosophy is to provide the ubiquitously required silicon initialization code. As such, FSP will often provide only a subset of the products features.

The next generation processors for FSP used to give better performance to the customers are Kabylake, Broxton and Apollolake which will release at the end of 2016. Mainly Kabylake and Apollolake are for PCs and Broxton is for tablet. So, by using FSP for next generation processors, Intel provides best solution to that customers who want to use open source bootloaders for particular BIOS.

KEYWORDS: BIOS, Boot loader, FSP, Initialization, Next generation processors

# Contents

| De | eclara  | tion                           | iii |

|----|---------|--------------------------------|-----|

| Ce | ertific | ate                            | iv  |

| Ce | ertific | ate                            | v   |

| Ac | cknov   | vledgements                    | vi  |

| Ał | ostrac  | t                              | vii |

| Co | onten   | ts                             | ix  |

| Li | st of ' | Tables                         | X   |

| Li | st of l | Figures                        | xii |

| Ał | obrev   | iations                        | 1   |

| 1  | Intr    | oduction                       | 2   |

|    | 1.1     | Background                     | 2   |

|    | 1.2     | Motivation                     | 4   |

|    | 1.3     | Problem Statement              | 5   |

|    | 1.4     | Thesis Organization            | 6   |

| 2  | Lite    | rature Survey                  | 8   |

|    | 2.1     | Intel Platform Architecture    | 8   |

|    | 2.2     | Platform Software Architecture | 10  |

|    | 2.3     | BIOS Overview                  | 11  |

|    | 2.4     | Legacy and EFI BIOS            | 13  |

|    | 2.5     | UEFI Specifications            | 15  |

|    | 2.6     | UEFI BIOS Boot Phases          | 16  |

|    | 2.7     | EDK and EDK II Platform        | 24  |

| 3  | Firn    | nware Support Package          | 26  |

|    | 3.1     | Overview                       | 26  |

|    | 3.2     | FSP Usage Model                | 27  |

|    | 3.3     | FSP Code Delivery Model        | 28  |

|    | 3.4     | FSP Integration                | 29  |

|    | 3.5     | FSP Boot Flow                  | 30  |

|    | 3.6     | FSP Versions                   | 31  |

| 4  | FSP   | P Implementation Strategy 39              |

|----|-------|-------------------------------------------|

|    | 4.1   | POST and Phase Code                       |

|    |       | 4.1.1 Why POST Code Required              |

|    |       | 4.1.2 How POST Status Code Works          |

|    |       | 4.1.3 Types of POST Code                  |

|    |       | 4.1.4 Implementation                      |

|    |       | 4.1.5 Phase Code                          |

|    |       | 4.1.6 Implementation                      |

|    | 4.2   | FSP Separation from Source Code           |

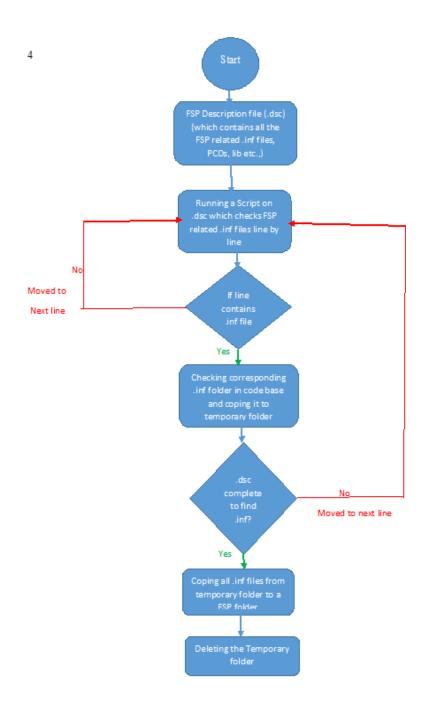

|    |       | 4.2.1 Flow Chart of Script                |

|    | 4.3   | FSP 2.0                                   |

|    | 4.4   | Firmware Configuration for FSP            |

|    | 4.5   | Responsiveness Infrastructure of FSP      |

|    |       | 4.5.1 What is Responsiveness?             |

|    |       | 4.5.2 Why Responsiveness?                 |

|    |       | 4.5.3 Implementation                      |

|    | 4.6   | eMMC Boot Flow for FSP                    |

|    |       | 4.6.1 Overview                            |

|    |       | 4.6.2 Implementation                      |

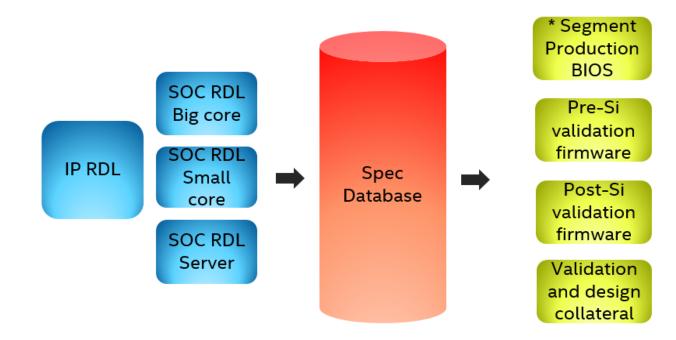

| 5  | Aut   | omated BIOS generation using System RDL 6 |

|    | 5.1   | Overview                                  |

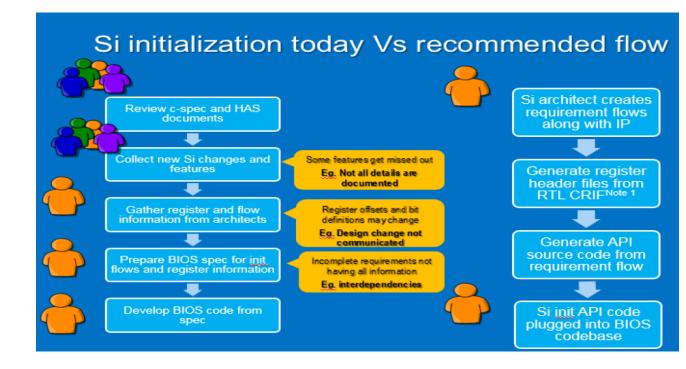

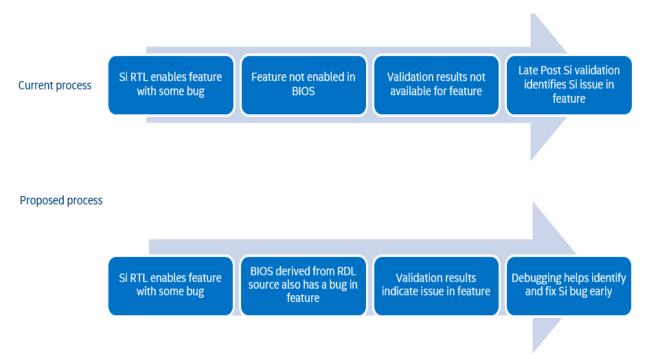

|    | 5.2   | Firmware Developement Model               |

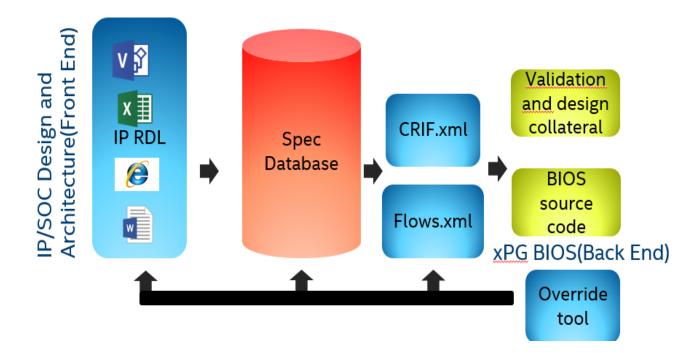

|    | 5.3   | System RDL Usage Model                    |

|    | 5.4   | Implementation                            |

| 6  | Con   | clusions and Future Scope 69              |

| 6  |       | · · · · · · · · · · · · · · · · · · ·     |

|    | 6.1   |                                           |

|    | 6.2   | Future Scope                              |

| Bi | bliog | raphy 72                                  |

# **List of Tables**

| 2.1 | Legacy BIOS and EFI BIOS [4]       | 14 |

|-----|------------------------------------|----|

| 2.2 | EFI Boot Phases and Services [4]   | 17 |

| 2.3 | PEI Services and its Functions [4] | 20 |

| 4.1 | POST Code Classes [6]              | 42 |

| 4.2 | EDK II Reference Code Packages [4] | 49 |

# **List of Figures**

| 2.1  | Intel Platform Architecture [4]                                 | 9  |

|------|-----------------------------------------------------------------|----|

| 2.2  | High Level Diagram of BIOS Space [4]                            | 12 |

| 2.3  | UEFI Interface between BIOS and OS Loader [4]                   | 14 |

| 2.4  | UEFI Interface [4]                                              | 16 |

| 2.5  | Phases of BIOS Execution [4]                                    | 17 |

| 2.6  | PEI Phase Flow [4]                                              | 20 |

| 2.7  | PEI to DXE Foundation [4]                                       | 22 |

| 2.8  | DXE Phase Flow [4]                                              | 23 |

| 2.9  | BDS Phase Flow [4]                                              | 24 |

| 3.1  | FSP Usage Model [5]                                             | 27 |

| 3.2  | Code Delivery Model for FSP A) 2012 B) 2013 C) 2014 D) 2015 [5] | 28 |

| 3.3  | FSP Boot Flow [5]                                               | 30 |

| 3.4  | FSP Boot flow Versions (a) 1.0 (b) 1.1[5]                       | 31 |

| 3.5  | TempRamInit API prototype [5]                                   | 33 |

| 3.6  | FspInit API Prototype [5]                                       | 33 |

| 3.7  | NotifyPhase API Prototype [5]                                   | 34 |

| 3.8  | FspMemoryInit API Prototype [5]                                 | 35 |

| 3.9  | TempRamExit API Prototype [5]                                   | 35 |

| 3.10 | FspSiliconInit API Prototype [5]                                | 36 |

| 3.11 | FSP Boot Flow Version 2.0 [6]                                   | 37 |

| 4.1  | BIOS POST Code in Board [6]                                     | 41 |

| 4.2  | Proposed Method for Phase Code                                  | 43 |

| 4.3  | Finalized Implementation of Phase Code                          | 44 |

| 4.4  | (a) Regular BIOS Execution (b) FSP Execution                    | 45 |

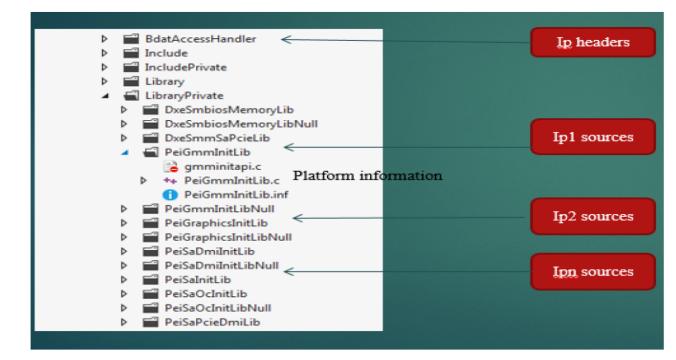

| 4.5  | Flow Chart of Script                                            | 46 |

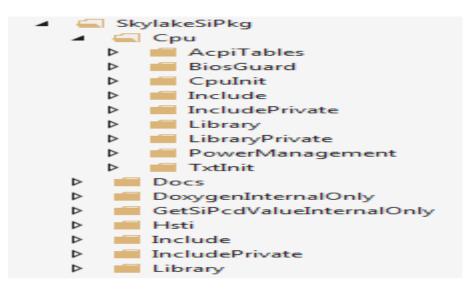

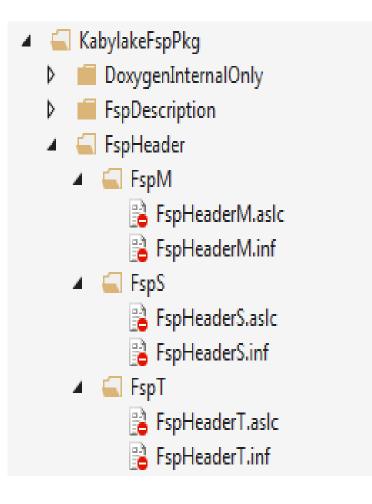

| 4.6  | Silicon Folder before Python Script                             | 47 |

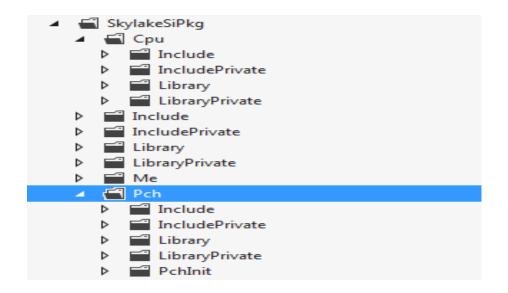

| 4.7  | Silicon Folder after Python Script                              | 48 |

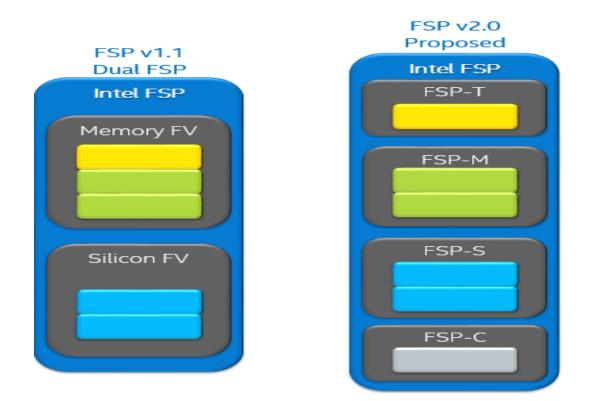

| 4.8  | Firmware Volume for (a)FSP 1.1 (b) FSP 2.0 [5]                  | 50 |

| 4.9  | FSP 2.0 Implementation [5]                                      | 51 |

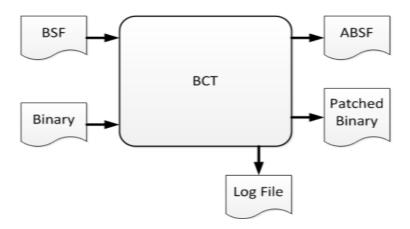

| 4.10 | High Level Diagram of BCT [6]                                   | 52 |

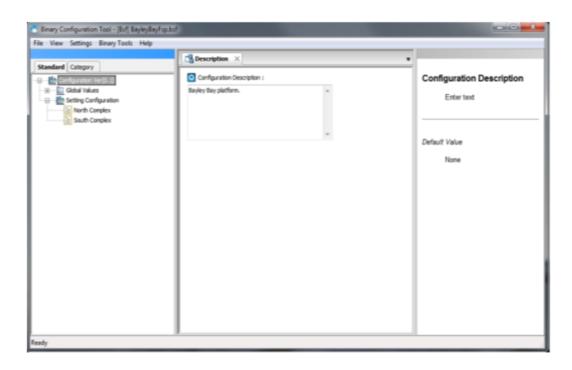

|      | GUI of BCT [6]                                                  | 53 |

|      | API called to UPD [6]                                           | 54 |

| 4.13 | Definition of UPD                                               | 54 |

|      | FV's of FSP for responsiveness [7]                              | 56 |

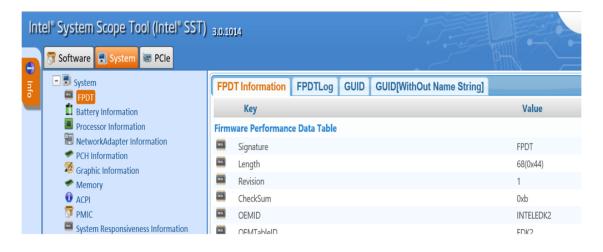

|      | Intel's System Scope Tool                                       | 57 |

|      | Result of Responsiveness                                        | 57 |

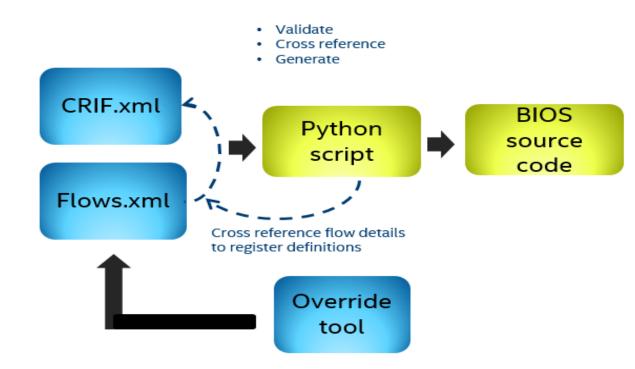

| 5.1  | High Level Diagram of Proposed Solution[11]                     | 61 |

| 5.2 | Firmware Development Model [11] | 62 |

|-----|---------------------------------|----|

| 5.3 | System RDL Usage Model [8]      | 63 |

| 5.4 | Back End Overviewn [8]          | 65 |

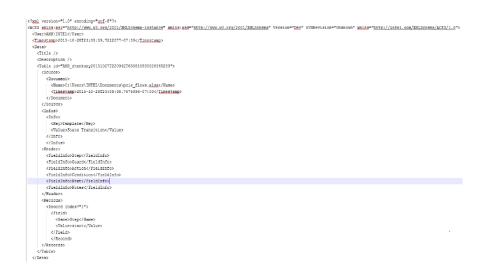

| 5.5 | Snippet of XML file             | 66 |

| 5.6 | Snippet of Source file          | 67 |

| 5.7 | Integration of BIOS code        | 68 |

| 6.1 | Re usability Structure [12]     | 71 |

# Abbreviations

| ACPI   | Advanced Configuration and Power Interface                   |

|--------|--------------------------------------------------------------|

| API    | Application Programming Interface                            |

| BCT    | Binary Configuration Tool                                    |

| BDS    | Boot Device Selection                                        |

| BIOS   |                                                              |

| CRB    | Basic Input Output System<br>Customer Reference Board        |

|        |                                                              |

| CSM    | Compatibility Support Module                                 |

| DXE    | Driver Execution Environment                                 |

| ECP    | EFI Compatibility Package                                    |

| EFI    | Extensible Firmware Interface                                |

| FPDT   | Firmware Performance Data Table                              |

| FSP    | Firmware Support Package                                     |

| FV     | Firmware Volume                                              |

| GUID   | Globally Unique Identifier                                   |

| НОВ    | Hand Off Block                                               |

| IPL    | Initialization Program Load                                  |

| ME     | Management Engine                                            |

| OEM    | Original Equipment Vendor                                    |

| OS     | Operating System                                             |

| OSPM   | Operating System-directed configuration and Power Management |

| PC     | Personal Computer                                            |

| PCD    | Platform Configuration Database                              |

| РСН    | Peripheral Cotroller Hub                                     |

| PEIM   | PEI Module                                                   |

| PEI    | Pre EFI Initialization                                       |

| PI     | Platform Initialization                                      |

| POST   | Power On Self-Test                                           |

| PPI    | PEIM to PEIM Interface                                       |

| ROM    | Read Only Memory                                             |

| SMBIOS | System Management Basic Input Output System                  |

| UEFI   | Unified Extensible Firmware Interface                        |

| UPD    | Updatable Product Data                                       |

| VPD    | Vital Product Data                                           |

|        |                                                              |

# Chapter 1

## Introduction

## 1.1 Background

Initially, computers had no boot firmware. Instead, the user had to enter a boot program by hand using switches on the front panel of the computer. This was happen for so long time but was so tough, error prone, slow and very laborious. At the later stage, when the change became mandatory, the initial switch positions were encoded as diodes on cards and were treated as peripheral and all important programs are started to enter into RAM. For small computers, programs were also not more than 256 words long at that time peoples started stored in ROM which gave access of boot from very few devices if you want to access booting from more devices from ROM then you have to change the ROM. After some time a major change came into process in early 1970 by Gary Kildall who was owner of digital research. He proposed that boot firmware provides an abstraction layer between the system hardware and operating system. This layer was to be used both to boot the system and to provide low level communication with the basic peripherals. When PCs are came into market developers implemented same concept called Basic Input Output System [1].

The BIOS consisted of two main pieces mainly Power On Self Test and the run time, which is worked as an abstraction layer for early PC based operating systems. POST is activated by the BIOS. It runs series of checks and diagnostics on motherboard. When BIOS executes, it is checking for registers of CPU, check the unification of the BIOS with itself, check the different peripheral components, check for main memory and select devices which are able to booting. Actually BIOS starts its POST when the reset is given to CPU. When reset occurs then first memory location which CPU tries to execute is called as reset vector. During re boot, the CPU saves this code fetch to the BIOS stored on the system flash memory [1].

Before run time phase one more phase is occuring called Boot phase. The main functionality of the boot phase is to load the boot loader from memory into portion of operating system. It should execute immediately after POST phase but it can execute by operating system or it can be invoked multiple times in a attempt to find a valid boot media. When boot phase completes, run time phase will execute. Objective of this phase is to support these legacy calling interfaces and compatibility with BIOS standards. These legacy setting are used to set up CPU register state, called BIOS and returned CPU register state. After this resume and reboot will occur where it will called by software request to reboot the machine [1].

The basic goal of the BIOS was to test and initialize the system, to find an input device which in general we can say keyboard, an output device that would be like monitor and a boot device, usually called hard disk. After that BIOS start executing boot process by loading 512 bytes loader from hard drive and give control to it. After that BIOS played a supporting hardware abstraction role for the devices which it was aware. The abstraction layer provided by the BIOS were extremely primitive and provided no synchronization. Due to the synchronization problem, the BIOS abstractions were polled rather than interrupt driven. The abstractions have allowed for implementation of numerous underlying architectures, all of which are compatible with one another [2].

There is another abstraction in firmware provided by the PC BIOS which is called option ROMs. An option ROM is a BIOS extension that resides on an add-in card. The option ROM serves the same purpose as device driver in a operating system which allow the base software to access peripherals that it does not intrinsically known. Early many companies producing BIOS noted that BIOS was the only software that actually ran and required to boot the system. The second point that noted is firmware was the only piece of software that was absolutely tied to platform [2].

The BIOS discussed here is implemented in two different environment for Intels next Generation Processors. The two different environments are EDK I and EDK II (also called as Native). The detail about the EDK I and EDK II will be discussed later. The implementation with EDK I and EDK II is done with the help of a flag defined in the code. Also the driver is implemented in two different modes in which one is with the complete package of the driver which contains all the source files, header files, dependency files if any, information files etc.. while the other mode is a binary implementation of the driver in which the drivers binary file will directly used in the firmware so no need to build the driver again as it it already a built in driver with the .efi image. Binary mode will contain only .efi file of the driver and information file for that. This is also implemented by defining a flag for that [2].

At last, like BIOS has been operating system neutral throughout its life, enabling remarkable innovation in the operating system community for platform sellers. A platform developed by the same company as the operating system, allowing close, often seamless, integration between software and firmware [2].

### **1.2** Motivation

It is always good to do something productive which can be considered as a beneficial thing in any area for an organization. Here the objective behind the work done in the thesis is to give more flexibility to the Intel clients by giving choices on boot loaders for FSP. Whenever user will use that FSP at that time users can use any open source boot loader to boot the system and Intel will provide only that part for which it is known. BIOS comes before OS booting so for booting any OS, boot loader is required after BIOS execution. In regular BIOS, it is not possible to change or add any functionality of silicon initialization code because of legal terms. So, to give more access to customers FSP comes into frame which is a one type of binary which provide key programming information of silicon initialization code. It provides chipset and processor initialization in a format that can be easily incorporated into many existing boot loaders. So, by using FSP customers can use any open source boot loaders like coreboot, Linux and Yacto.

Different Intel hardware devices may have different Intel FSP binary instances, so a platform user needs to choose the right Intel FSP binary release. The FSP binary should be independent of the platform design but specific to the Intel CPU and chipset complex. We refer to the entities that create the FSP binary as the FSP Producer and the developer who integrates the FSP into some platform firmware as the FSP Consumer.

So, the motivation behind this thesis work is to develop FSP such that any limitation of boot loader from customer side should not be there. From customers side, they should change any functionality by its own and they should use any open source bootloaders in upcoming processors like Kabylake and Broxton.

#### **1.3 Problem Statement**

In general, BIOS provides all the important information to the platform for initialization of silicon which is very crucial for initializing any platform, there is some information which is not directly available but if anyone want to use that it will be available with legal agreements because of proprietary information. In the case of FSP, it is a binary distribution code for particular silicon initialization code. FSP provides ready access of all the key programming information mainly which is not publicly available. The second point of FSP is just to abstract the all complexities of the initialization of Intel silicon and will give you a required number of defined interfaces. So the design goal is to provide necessary required initialization code as FSP provides only some part of products features.

The limitation of EFI BIOS is that it allows to use particular boot loader for booting the system and it becomes hard point to follow rules when one has to implement another features. So FSP contains only silicon initialization code so users can add any other functionality inside their product without much problem.

Another objective is BIOS contain complete reference code so it requires larger memory to store when FSP have very small footprint like near about 200 KB. Because of small footprint its execution time is so fast compared to regular BIOS. Whenever user want to integrate boot loader with FSP it will integrate very easily and most important thing is it is supported among all Intel Atom, Core and Xeon processors.

So as per the thesis work, we developed the FSP among all the Intel next generation processors like Kabylake and Broxton which will be release at the end of 2016. We fulfilled the clients requirement of FSP for these processors and developed an excellent and stable FSP.

### **1.4 Thesis Organization**

The thesis work carried out during the course of time has been presented in total six chapters as follows:

**Chapter 1 Introduction**, in this chapter, importance of the thesis and a brief background about BIOS like how BIOS is working, how it is implementing, its pieces as POST and run time phases is presented.

The motivation and problem statement of the thesis is also mentioned in this chapter.

**Chapter 2 Literature Survey**, It describes the basic about Intel platform architecture, basics about BIOS, Different phases of BIOS, Different boot modules, software architecture overview, UEFI specification, about legacy BIOS and EFI BIOS. It also gives idea about EDK and EDK II platforms.

**Chapter 3 Firmware Support Package**, It describes what is FSP, Boot flow of FSP, Different versions of FSP, Modification in FSP for reference code in every year, Different firmware volumes of FSP, Basics about different APIs as well as functionality of that APIs.

**Chapter 4 FSP Implementation Strategy**, This chapter contain the execution of FSP in reference code, POST and Phase code implementation, Implementation of python script for FSP driver separation, How to execute the FSP in platform, FSP 2.0 implementation and the result produced by FSP, How to configure the platform firmware at the run time and statically, Responsiveness infrastructure of FSP for getting execution time of all drivers and at the last how to boot the OS for firmware from eMMC.

**Chapter 5 Automated BIOS generation using System RDL**, This is another project on which i am working. This chapter contains the overview of the automation of BIOS generation, Firmware Development Model of systemRDL, It's usage model and implementation of the project which can help at every aspect.

Chapter 6 Conclusion and Future Scope, It contains all the conclusions related

to FSP execution and how important automated BIOS generation from system RDL. In future scope, there are some thoughts which we discussed with architects can be help more on FSP to give the flexibility to customers. From advancement side of automation for BIOS, which can give more flexibility to developers.

# Chapter 2

# **Literature Survey**

## 2.1 Intel Platform Architecture

Platform encompasses all required ingredients, features, capabilities, initiatives and technologies. Total four major components of platform are as follows [3]:

#### 1. Hardware:

Processors, chipsets, Communication devices, Memory, Boards, and Systems [3].

#### 2. Software:

Operating systems, Applications, Firmware and Compilers [3].

#### 3. Technologies:

Hyper Threading Technology(HTT), Intel virtualization Technology, Intel Active Management Technology(AMT) [3].

#### 4. Standard and Initiatives:

Wi-Fi, WiMAX, The Wireless Verification Program [3].

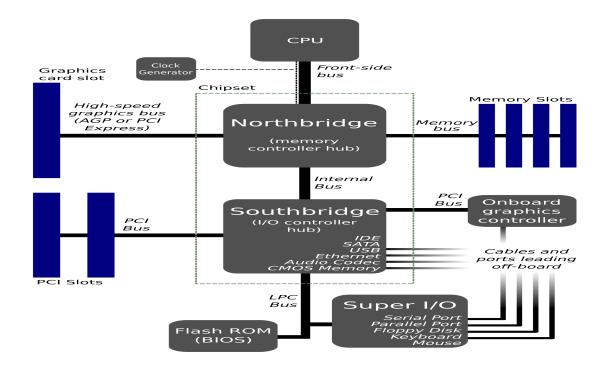

Intel platform architecture is complex with lots of components on it. Every component must work as designed and there shouldnt be any conflicts between the devices on it. Now a days it is come up with single chip solution which means CPU and PCH are in single die. Intel platform architecture is shown in Fig. 2.1. From Fig. 2.1, it is very clear there are many components connected with platform. Mainly at higher level there are two divisions called Northbridge and Southbridge. These two components are connected by a bus which is known as DMI. It is mostly Intel link for this bridge

connection on motherboard. By using this DMI bus north bridge and south bridge will communicate with each other [4].

Northbridge is usually a one type of hub which is used to control the high end devices like memory controller. Because of this high performance demand, north bridge is directly connected to CPU. Here shown in figure all the high end devices like graphics bus and memory bus are connected to Northbridge. High speed graphics bus and memory bus are connected by PCI Express bus with north bridge. PCI Express bus is one type of serial bus which has very high performance in terms of data transfer. In earlier Intel platform architecture, it was used PCI bus which was parallel bus so its data rate was so low which was not suit for Northbridge thats why PCI is replaced by PCI Express which gives very high speed because of point to point technology [4].

Fig. 2.1: Intel Platform Architecture [4]

Bridge which is connected by DMI with Northbridge is called Southbridge. Southbridge implements the slower performance speed compared to Northbridge because unlike Northbridge it is not directly connected to CPU. In Intel platform it is also called as I/O controller hub. It handles all of the computers I/O functions such as USB, audio, serial, the system BIOS, Interrupt controller, and the IDE channels. As shown in Fig. 2.1, all the pots like serial port, parallel port, keyboard, Mouse, etc. all ports are connected with south bridge. There are PCI slots also available with Southbridge which can be used to connect more devices.

Now a days in modern platform architecture, Intel did a major change like instead of Southbridge, they put PCH block which is directly connected with CPU in a single die. PCH was found to overcome the bottleneck between processor and motherboard. As speed of processor is increasing, the data transfer rate between the CPU and motherboard would achieve full bandwidth. So by PCH it overcome because it took most of the task of the Southbridge and few roles of north bridge too by front side bus that have not been incorporated into the CPU package [4].

### 2.2 Platform Software Architecture

The definition of firmware on PC is instructions (with data) that are consumed by non-IA execution engines associated with a non-CPU hardware device. There are three main categories of firmware as follows [4]:

- Fixed embedded firmware: contained in ROM and hidden from platform view

- Upgradeable embedded firmware: contained in built-in non-volatile memory with default image (code/data); upgradable during life cycle

- Externally stored firmware: storage of the code/data is outside of the device package that executes the firmware. The external storage is likely in non-volatile memory form. Patches for embedded firmware falls into this category

No action is required on platform SW to support fixed embedded firmware. Examples of embedded firmware components are [4]:

- CPU microcode, uncore firmware

- ME ROM code

Upgradeable embedded firmware is presumed to be functional at platform build time. Discrete graphics card firmware is in this category. Upgrade tool is expected to be available for at least one of the users SW environment. There is no known ingredient with firmware in this category [4].

Firmware code or data is contain by physical repository of firmware device. A physical firmware device may be divided into smaller pieces to form a multiple logical firmware device. This logical firmware device is called firmware volume. Each volume is arranged into a bunch of files. As we know the file unit is the basic unit of storage for firmware space. Many formats of files have quite different and discrete parts within it. These parts are called file sections, otherwise just sections for short. All the sections begin with one type of header that declares the type as well as the length of that section. The headers for this section must be 4 bytes aligned within the parent files image [4]. Mainly there are large number of sections, they fall into the main two big categories as follows [4]:

- Encapsulation sections

- Leaf sections

First section is encapsulation section which is essentially container that hold other sections. The sections which contained inside an encapsulation section is called as child sections. Leaf section directly contain data and mainly do not contain other sections unlike encapsulation sections [4].

## 2.3 **BIOS Overview**

BIOS is the first code run by a PC when powered on. It acts as a layer between OS and Hardware. BIOS initialize the various platform components like CPU initialization, core initialization, memory and chipset initialization etc. The BIOS must do its job before your computer can load its operating system and applications. The basic input/output system (BIOS), also known as the System BIOS or ROM BIOS, is a de facto standard defining a firmware interface.

The BIOS software is built into the PC, and is the first code run by a PC when powered on like boot firmware. The primary function of the BIOS is to set up the hardware and load and start a boot loader. When the PC starts up, the first job for the BIOS is to initialize and identify system devices such as the video display card, keyboard and mouse, hard disk drive, optical disc drive and other hardware [4]. The BIOS then locates software held on a peripheral device (designated as a boot device), such as a hard disk or a CD/DVD, and loads and executes that software, giving it control of the PC. This process is known as booting, or booting up, which is short for bootstrapping [4].

BIOS software is stored on a non-volatile ROM chip built into the system on the motherboard. The BIOS software is specifically designed to work with the particular type of system in question, including having knowledge of the workings of various devices that make up the complementary chipset of the system. In modern computer systems, the BIOS chip's contents can be rewritten, allowing BIOS software to be upgraded. BIOS features are as follows [4]:

- It acts as a layer between OS and Hardware

- It gets your computer up and running

- Initializes the hardware like Microprocessor, memory, chipset, devices, peripherals etc

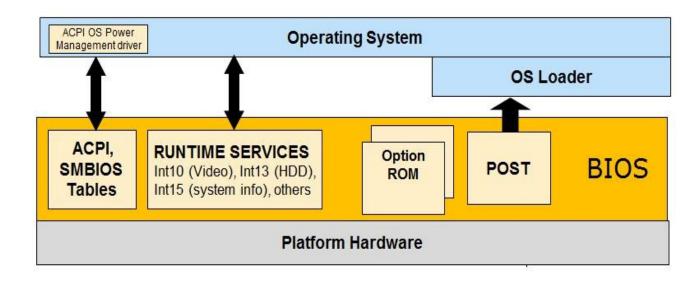

BIOS is communicating with platform and operating system when it is doing its task and after finishing its task it will work as supporting code as shown in Fig. 2.2 as follows [4]:

Fig. 2.2: High Level Diagram of BIOS Space [4]

From Fig. 2.2, it is clear that BIOS is medium to communicate between operating system and platform hardware. BIOS is the only software in the platform that knows all the details of the motherboard. POST is the responsible for testing system which will use OS loader to load operating system whereas ACPI and SMBIOS tables are useful for power management and to control it. Runtime services are services which generates interrupt for particular service to OS then OS give return back notification by executing that services.

Basically BIOS will provide services like:

- It gives all the power related management functionality through ACPI

- It loads and take care of control over to the OS boot loader

- It give a set of standardized regularities for the OS to use

- It fetch the motherboard and silicon environment from the OS

- It build the system to work an OS

- It give runtime services to the OS e.g. disk and video

The Advanced Configuration and Power Interface (ACPI) is one kind of a specification which was prepared to structured most of the industry related interfaces which gives robust operating system (OS)-directed motherboard configuration as well as management related to the power of both devices as well as entire systems. This is the heart for an Operating System-directed configuration and Power Management (OSPM).

Power-On Self-Test (POST) routines run very quickly after power is giving to system, by nearly all electronic devices. It includes regularities to set an primary value for internal as well as output signals and to execute all internal tests, as found by the device manufacturer. These initial conditions are also referred to as the devices state.

### 2.4 Legacy and EFI BIOS

Currently, Industry has migrated from Legacy BIOS to a standard and modular EFI BIOS. EFI BIOS offers new improved features and flexibility for code developers. The difference between Legacy BIOS and EFI BIOS is shown in Table 2.1.

| Legacy BIOS                                  | UEFI BIOS                                      |  |

|----------------------------------------------|------------------------------------------------|--|

| This is traditional BIOS                     | New architecture based on EFI spec             |  |

| Written in assembly code, initially designed | C based, initially designed for itanium server |  |

| for IBM PC-AT                                | systems                                        |  |

| Interface is per-BIOS spaghetti code, not    | Well defined module environment and inter-     |  |

| modular                                      | face based on EFI specification                |  |

| Lives within the first 1MB of system mem-    | Can live anywhere in the 4GB system mem-       |  |

| ory                                          | ory space                                      |  |

| Uses 16bit memory access. Requires hacks     | Allow direct access of all memory via(32 bit   |  |

| to access above 1MB memory                   | and 64 bit) pointers                           |  |

| Supports 3rd party modules in the form of 16 | Supports 3rd party 32/64 bit drivers           |  |

| bit option ROMs                              |                                                |  |

| Examples: AMI core 8, Phoenix legacy         | Examples: Aptio (AMI), H20 (Insyde),           |  |

| BIOS                                         | Tiano (Intel)                                  |  |

Table 2.1: Legacy BIOS and EFI BIOS [4]

Legacy BIOS is able to run different operating system, like MS-DOS, equally well on computers other than IBM. Additionally Legacy BIOS has defined OS independent interface for hardware that enables interrupts to communicate with video, disk and keyboard devices along with BIOS ROM loader and bootstrap loader. Now a days legacy BIOS is not used that much then also its two functions called system configuration and setup are using now.

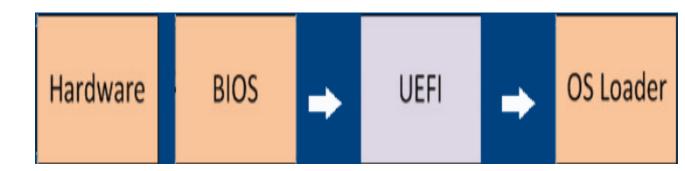

UEFI was created to change the Legacy BIOS to streamline the process of booting, and it behave as the interface between operating system of computer and its platform firmware. It not only changes the most functions of BIOS, but also offers a rich extensible pre-OS environment which will give advanced boot and runtime services [4].

Fig. 2.3: UEFI Interface between BIOS and OS Loader [4]

UEFI to BIOS accomplishes the same basic task as it is act as common interface between system firmware and operating system. It has same size and performance measures as it has boot faster in less flash environment. It should be operating system neutral like it should work in variety of system including Linux and windows. Major change in between this access method of ACPI and SMBIOS are different[7].

BIOS code whatever we are using today enable for legacy BIOS as well as EFI BIOS by means of a module called CSM. Some OS not support the EFI BIO, so for that CSM module is used to run necessary BIOS code. When this mode is ON, system will boot for legacy BIOS and if this mode is OFF, system will boot to native EFI BIOS [4].

The CSM module is used to translates all the data generated under the EFI environment into the data or information required by the legacy environment as well as it will makes the legacy BIOS services available such that it will booting to the operating system and for use in runtime [4].

### 2.5 UEFI Specifications

Unified Extensible Firmware Interface (UEFI) is grounded in Intel initial Extensible Firmware Interface(EFI) specification, which defines a software interface between an operating system and platform firmware. The UEFI architecture allows users to execute applications on a command line interface. It has intrinsic networking capabilities and is designed to work with multi processors systems.

The interface inside the UEFI is in the form of data tables which contains platformrelated all information, after that boot as well as runtime service calls which are available to the OS loader and to the OS. By all this, it provides a complete environment for booting an OS. This specification is designed only as a pure specification for interface. As we know, the specification defines the all the set of interfaces as well as structures of that platform firmware must implement. Similarly, another way specification defines all the set of interfaces as well as structures that the OS may use in booting. The interface of UEFI and compatibility of UEFI specification is shown in Fig. 2.4 as follows [4]:

Fig. 2.4: UEFI Interface [4]

The intent of the specification is to define a way for the OS and platform firmware to communicate only information necessary to support the OS boot process. This is accomplished through a formal and complete abstract specification of the software visible interface presented to the OS by the platform and firmware. Furthermore, an abstract specification opens a route to replace legacy devices and firmware code over time. New device types and associated code can provide equivalent functionality through the same defined abstract interface, again without impact on the OS boot support code [4]. The specification is applicable to a full range of hardware platforms from mobile systems to servers. The specification provides a core set of services along with a selection of protocol interfaces. The selection of protocol interfaces can evolve over time to be optimized for various platform market segments. At the same time, the specification allows maximum extensibility and customization abilities for OEMs to allow differentiation. In this, the purpose of UEFI is to define an evolutionary path from the traditional PC-AT-style boot world into a legacy-API free environment [4].

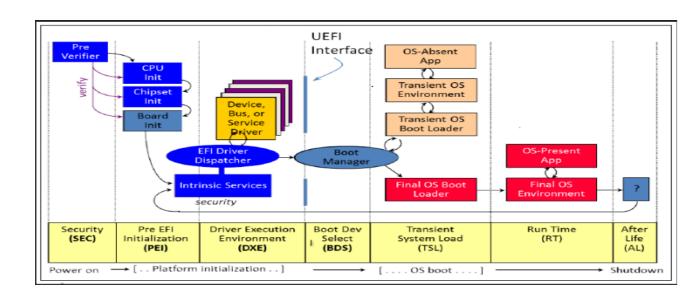

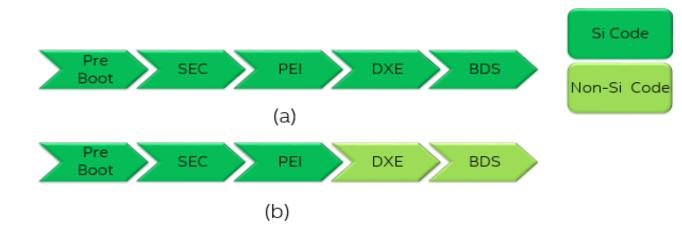

## 2.6 UEFI BIOS Boot Phases

When platform initialization occurs, at that time BIOS will pass through different four phases called Security, Pre EFI initialization, Driver execution environment and Boot device select. BIOS starts execution once power will be on. After that it execute the phases step by step for initialization and during BDS phase, it gives the control to OS after that by using boot loader OS takes care the system and BIOS work as supporting code. As shown the flowchart in Fig. 2.5 [4].

Fig. 2.5: Phases of BIOS Execution [4]

EFI BIOS is a modular code and it boots in a manner such that each phase will execute correctly. EFI Boot process is dived into four main phases which are:

- Security Phase

- PEI Phase

- DXE Phase

- BDS Phase as shown in Table 2.2.

| SEC                     | PEI                      | DXE                     | BDS               |

|-------------------------|--------------------------|-------------------------|-------------------|

| Provides processor boot | Initializes processor    | Initializes processor,  | Run down list of  |

| strap vector            |                          | cache, chipset and      | selected devices. |

|                         |                          | SMM                     |                   |

| Initializes temporary   | Detect corrupted flash   | Execute PCI enumer-     | Load boot image   |

| RAM using CPU cache     | and recover if corrupted | ation and initializes   | into memory       |

|                         |                          | video, keyboard, mouse  |                   |

|                         |                          | and USB legacy          |                   |

| Provides optional secu- | Find and initializes     | Initializes drivers and | Jump to boot im-  |

| rity features           | RAM                      | create table interfaces | age and try for   |

|                         |                          |                         | next image        |

Table 2.2: EFI Boot Phases and Services [4]

#### 1. SEC Phase:

The Security phase or we can say SEC phase is the first phase in the PI Architectue and is used for the following:

- It handles all platform related restart events

- It creates a memory store for temporary base

- It serves as the root of trust in the system

- It passes information related to handoff to the PEI Core

This phase contains the first code executed after power-on or reset. Not only have peripherals not been initialized, but memory may not be available. The SEC phase is not particularly suitable for software-based performance measurement. For most platforms, SECs total elapsed time can be determined by measuring from the beginning of time to the start of PEI. This is the mechanism used by EDK II. Apart from the minimum required architecturally information about handoff, this phase can also pass optional information to the next phase called PEI Core, such as the SEC Platform will give Information PPI or may be information about the health status of the processor [4].

#### 2. PEI Phase:

The above phase called the PEI phase of the PI Architecture is invoked quite early in the phase of boot flow. Specifically, after some initial processing in the Security (SEC) phase, any restarting event will called by the PEI phase. The PEI phase will operate with the platform in a nascent state at the starting phase, leveraging only on processor resources, like the cache of processor as a call stack, to release Pre-EFI Initialization Modules (PEIMs). These PEIMs are responsible for the following [4]:

- Initializing most of original memory complement

- Describing the memory stack data in Hand-Off Blocks (HOBs)

- Describing the location of volume for firmware in HOBs

- Giving control into the next phase called Driver Execution Environment (DXE) phase

Ideally, this phase is intended to be the smallest amount of code chunk to achieve the ends listed above. As such, any other reliable algorithms as well as processing should be deferred to the DXE phase of execution. This phase actually consists of two sub-phases: Prememory and Postmemory. PreMem is the state before main memory is available for use and PostMem refers to the state after main memory is usable [4].

After SEC phase transitions to PEI phase, the firmware is in the PreMem state. At this point, some temporary memory is usually available. On some IA platforms the temporary memory is actually a portion of the processors cache that has been placed in a special mode. While operating in this special mode a number of restrictions exist:

- Temporary memory may only be used for data storage, not instruction execution

- The size of temporary memory is usually small

- Temporary memory will not survive enabling of caching

- Initialized external or static variables cannot be used since they will reside within the read-only firmware device, not temporary memory. Global constants can be used, but they must be declared as CONST and treated as read-only

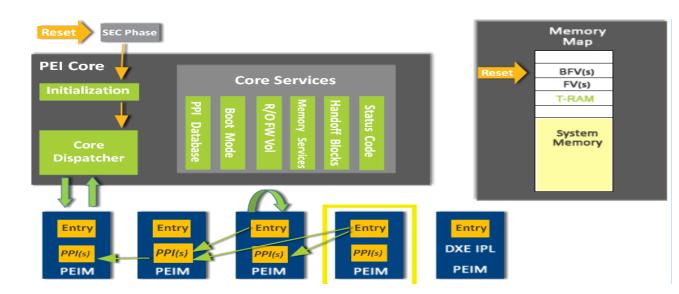

The PEI phase flow is shown in Fig. 2.6.

Fig. 2.6: PEI Phase Flow [4]

As shown in Fig. 2.6, it is high level flow of PEI execution in which when power on will happen SEC phase will occur and execute from memory map. During this phase T-RAM should also initialize. After that SEC invokes the PEI initialization which will call different PEI services. In next phase core dispatcher comes which finds firmware volume to execute PEIM which execute PPIs. After all PEIM execution system memory will initialize and at last final PEIM executes called DXE IPL which will do transaction into DXE phase. Table 2.3 is PEI service table as follows [4]:

| Services     | Functions                                           |

|--------------|-----------------------------------------------------|

| PPI          | InstallPpi() LocatePpi() NotifyPpi() ReInstallPpi() |

| Boot Mode    | GetBootMode() SetBootMode()                         |

| HOB          | GetHobList() CreateHob()                            |

| Flash Volume | FfsFindNextFile()                                   |

| PEI Memory   | InstallPeiMemory() AllocatePool()                   |

| Status Code  | PeiReportStatusCode()                               |

| Reset        | PeiResetSystem                                      |

Table 2.3: PEI Services and its Functions [4]

As soon as memory has been initialized and is ready for use, these HOBs, and other PEI data stored in temporary memory, are copied into main memory and the PEI phase continues on in the PostMem state. Due to memory restrictions during the PreMem state, some differences exist between performance measurements made during PEI and measurements made later.

This phase is used for crisis recovery as well as resuming from the S3 sleep state. For the crisis recovery, this phase should be there reside in some small, faultavoidance block of the firmware store. Because of that, it is imperative to keep the footprint of the PEI phase as small as possible. Apart from that, for a successful resume for S3, the resume speed is of utmost importance, so the code path which will be through the firmware should be minimized. Above two boot flows also speak to the need to keep the processing as well as code paths in the PEI phase to a minimum. The implementation of this phase will be more dependent on the architecture of the processor than any other phase. In particular, behind this idea, the more resources the processor provides at its initial or nearby initial state, the richer the interface between the PEI Foundation and PEIMs [4].

#### 3. DXE Phase:

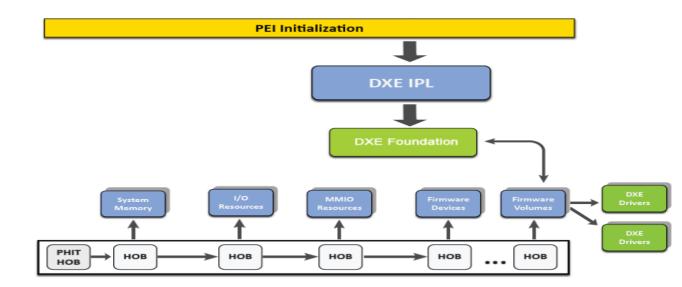

This phase also called as Driver Execution Environment is where most of the system will perform initialization. Pre-EFI Initialization which is the phase comes before DXE, is used for initializing main memory in the platform so that the this phase can be loaded and can be executed. The control of the system at the end of the PEI phase is passed to the this phase through a list of data structures created based on position-independent called Hand-Off Blocks (HOBs). By using DXE phase the amount of complexity become decrease and enable to write a code in more modular fashion. Lets see how PEI to DXE transition will happen by Fig. 2.7 [4].

Fig. 2.7: PEI to DXE Foundation [4]

When PEI initialize it calls to DXE IPL which store the HOBs. After DXE IPL complete its initialization, it call to DXE foundation which calls firmware volumes to extract the DXE drivers. HOBs are the only blocks which pass from PEI to DXE phase. DXE foundation populate the architecture protocols. Architecture protocols are the only DXE drivers that can access the hardware directly. It means whichever DXE drivers want to communicate with hardware has to go through the architecture protocols.

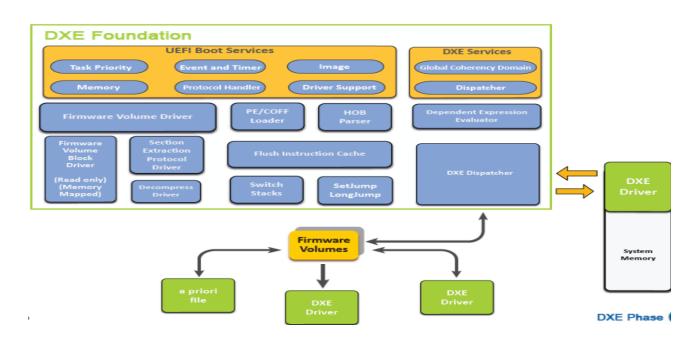

There is particular DXE phase flow is also there in order to execute the particular services of DXE phase as shown in Fig. 2.8. In this DXE phase overview, DXE foundation will initialize the DXE services, once this services initializes foundation begins to dispatch the DXE drivers. DXE dispatcher looks for firmware volume which will find a priori file. A priori file contain DXE drivers which have peak of image. DXE drivers should execute in exact order what they mentioned because each DXE driver is loaded into system memory specified by DXE dispatcher. Once dispatcher complete a priori file the it will look for more firmware volumes until all DXE drivers will execute. Once all the drivers are execute then DXE dispatcher will look for a priori file and check wheather any driver still need time to execute otherwise it will leave the DXE phase and will give the control to next phase [4].

Fig. 2.8: DXE Phase Flow [4]

#### 4. BDS Phase:

During Driver Execution Environment, the Boot Manager executes the DXE drivers by using DXE Dispatcher only after all the DXE drivers whose dependencies have been satisfied. After this process, control is given to the BDS phase of execution. The BDS phase is used for implementing the boot policy of platform. This boot policy gives flexibility which allows system vendors to optimize the user experience during BDS phase of execution. The Boot Manager will also support booting from a short-form device path which will starts with the first node and being a firmware volume device path.

The boot manager should must use the GUID in the volume of firmware device node to match it to a firmware volume inside the system. The GUID in the volume of firmware device path is compared with the firmware volume name GUID. If both match is made, then the volume for firmware device path can be appended to the device path of the matching volume for firmware and normal boot behavior can now be used. The BDS phase is implemented as part of the BDS Architectural Protocol.

The Driver Execution Environment Foundation gives control to this phases Architectural Protocol after all of the Driver Execution Environment drivers who have dependencies satisfied as well as loaded and executed by the DXE Dispatcher. The BDS phase is responsible for the following [4]:

- It will initialize the console devices

- It will load the device drivers

- It will trying to attempt load and execute boot selections

If the BDS phase will not be able make progress, it goes for executing the DXE Dispatcher to see if the dependencies of any additional DXE drivers have been satisfied or not since the last time the DXE Dispatcher was invoked.

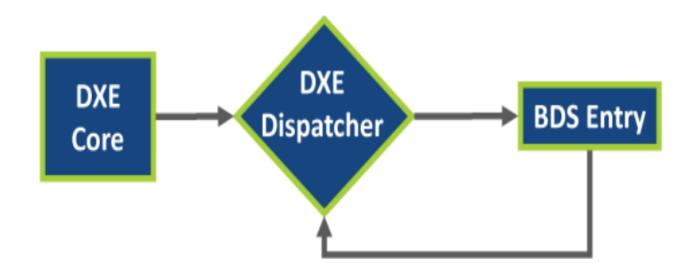

DXE dispatcher calls last DXE driver called BDS driver. In general DXE core call DXE dispatcher which first complete all the DXE and UEFI drivers and then it completes BDS entry which is implemented as driver. BDS entry could require other driver to dispatch so that BDS might recall DXE dispatcher. This scenario is shown in Fig. 2.9 [4].

Fig. 2.9: BDS Phase Flow [4]

### 2.7 EDK and EDK II Platform

EDK (Extensible Firmware Interface Developer Kit) was the first generation of the open source EFI development kit. EDK was a development environment designed with a functional arrangement of the components to support windows development. EDK provides access to the outside of Intel who did not have a direct license agreement with

Intel with more robust development environment. EDK was directed at companies who develop both the firmware and the drivers. EDK was eventually upgraded to EDK II which expands operating system support.

EDK II is the second generation development environment. It has two main objectives which were lacking in the first generation EDK as follows [4]:

- EDK II organizes the content in whole chunk which are added and removed as a whole

- EDK II allows compiling under multiple operating systems, including windows, Linux, Apple OS

# **Chapter 3**

# **Firmware Support Package**

## 3.1 Overview

Intel Firmware Support Package (FSP) provides key programming information for initializing Intel silicon including the processor, memory controller, chipset and certain bus interface as needed. It can be easily integrated into a firmware boot environment of the developers choice such as core boot, Wind River Vxworks, RTOS, Linux and open source firmware.

Intel found that it keeps the necessary information of programming which is crucial for silicon initialization. Some important information of programming is treated as secret information and if anyone wants then only be accessible with legal agreements. The first point for design of FSP is to provide easy access to the important information of programming that is not available everywhere. The second point of FSP is just to abstract the all complexities of the initialization of Intel silicon and will give you a required number of defined interfaces. So main design goal is to provide necessary required initialization code as FSP will provide us only some part of products features [5].

FSP is easy to adopt, economical to build and scalable to design thereby reducing time to market. As it is not a standalone boot loader, it must be integrated with host boot loader infrastructure to carry out other functions such as [5]:

- Initializing non Intel components

- Conducting bus enumeration and discovering devices in the system

• Industry Standards

When FSP will create it gives package in which it contains following:

- FSP binary

- Guide for Integration

- Updatable Product Data (UPD) or Vital Product Data (VPD) structure definitions

- File for Boot Settings (BSF)

The utility required for FSP configuration called Binary Configuration Tool (BCT) is available as a different package. By using this tool FSP configuration data can be easily changed which is there in UPD and we can change that data run time. So, by using this tool FSP can modify the setting at the run time [5].

# 3.2 FSP Usage Model

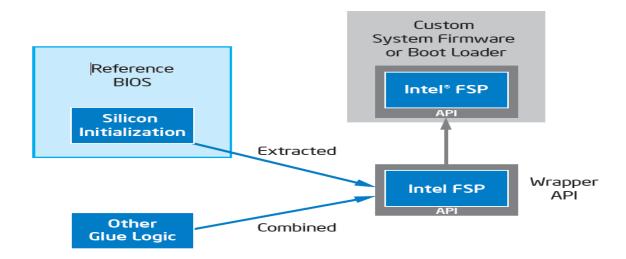

FSP is basically creating from complete reference BIOS only which is shown in Fig. 3.1 as follows:

Fig. 3.1: FSP Usage Model [5]

As per Fig. 3.1, it is clear that first only silicon initialization code is require from complete reference BIOS by extracting from Intel boot loader development kit. This

Silicon initialization code is combined with FSP glue logic which contain different architecture protocols which makes wrapper API. After that we have to put that wrapper into custom system boot loader to load that FSP in the system. Basically FSP is incorporated into many existing boot loader frameworks without exposing the Intellectual Property (IP) of Intel. FSP is distributed as single binary package to the customer. In FSP, all the silicon initialization PEIMs are packaged into one single package and make one separate package which will work as FSP. After making as single package it can plugs into existing firmware frameworks which is suit for all platform because of no need of any modification required to support the FSP. Main objective of FSP is to do a binary customization of regular silicon initialization code so that anyone can use very freely without much modification with whatever existing boot loader which gives more freedom to customers [5].

## **3.3 FSP Code Delivery Model**

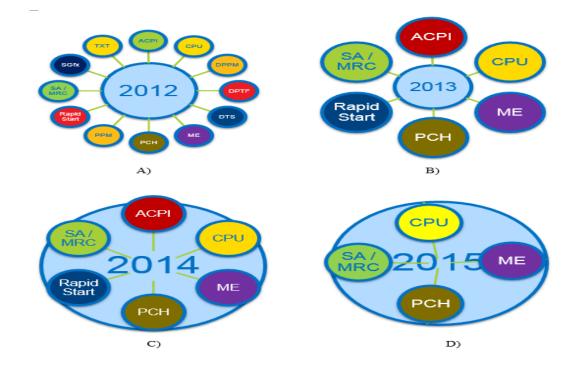

At every year Intel modified its FSP code delivery model by giving change in code structure of complete reference BIOS in silicon initialization as shown in Fig. 3.2 [5].

Fig. 3.2: Code Delivery Model for FSP A) 2012 B) 2013 C) 2014 D) 2015 [5]

In 2012, Intel started to implement FSP from reference code of silicon initialization. From Ivybridge platform FSP is started to execute. In this time Intel was providing total 12 different reference code packages for binary enabling strategy as well as at that time all reference code packages were individual. In the 2013, when Haswell platform came at that time Intel gave a FSP implementation as a 6 reference code packages as all are separate only. In the 2014, Intel did major changed in a FSP code format at the time of Broadwell where they made a single RC package which single RC package is of binary package but the number of reference code packages are same as of 2013. In Braswell at 2014 and Skylake at 2015, Intel gave more reduction in reference code packages as they gave only for silicon package namely South Agent, PCH, ME and CPU as a single RC package and gave platform package as sample code [5].

# **3.4 FSP Integration**

The FSP binary can be integrated into many different boot loaders and embedded OS. Below are some required steps for the integration [5].

#### 1. Customizing:

The FSP has some sets of configuration parameters that are part of the FSP binary and can be customized by external tools provided by Intel [5].

2. Rebasing:

The FSP is not Position Independent Code (PIC) and the whole FSP has to be rebased if it is placed at a location which is different from the preferred base address specified during the FSP build [5].

- 3. **Placing:** Once the FSP binary is ready for integration, the bootloader needs to be modified to place this FSP binary at the specific base address identified above [5].

- 4. **Interfacing:** The bootloader needs to add code to setup the operating environment for the FSP, call the FSP with the correct parameters and parse the FSP output to retrieve the necessary information returned by the FSP [5].

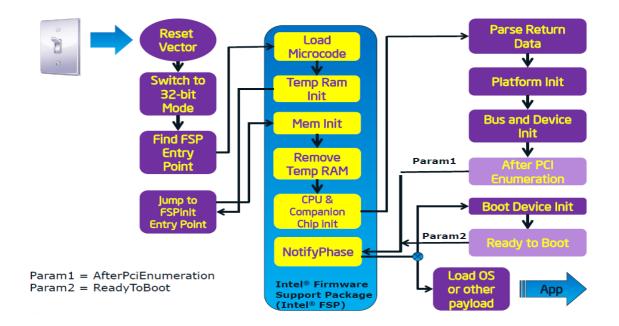

# 3.5 FSP Boot Flow

When binary enabling strategy completed then the next step will be the flow of booting for FSP. During FSP, we have to decide which API will come at which position and based on that have to decide design flow. There are different APIs for memory, silicon and temporary memory to execute that we should have to follow for particular execution of FSP. In boot flow every step of API is very important to execute correctly because every API is dependent on next API to work for so when previous API will execute at that time next API will start to initialize. FSP boot flow is shown in Fig. 3.3 as follows [5]:

Fig. 3.3: FSP Boot Flow [5]

From Fig. 3.3, which is flow of FSP, with the FSP binary from the FSP Producer in blue and the platform code that integrates the binary, or the FSP Consumer, in purple. The FSP EAS describes both the API interface to the FSP binary that the consumer code invokes, but it also describes the hand off state from the execution of the FSP binary. The latter information is conveyed in Hand-Off Blocks. When FSP started executing it find for entry point from where it can start. After that it will initialize cache as RAM. At the next phase it initializes memory and remove temporary memory as well. After memory portion it comes to chipset initialization and initialize platform and gives control to OS after ready to boot event.

### **3.6 FSP Versions**

Day by day when FSP becomes more popular then changes in boot flow was also required. According to demand of board or customer boot flow should be like more appropriate for customers which should give good performance. So, initially FSP had version 1.0 at the time of FSP started. After that Intel started to work on FSP 1.1 which was giving more control and flexibility to the boot loader which ultimately was good for customers. At later stage now Intel invent FSP 2.0 which have many changes over FSP 1.1 which is implemented in latest platforms and giving good performance over other versions [5].

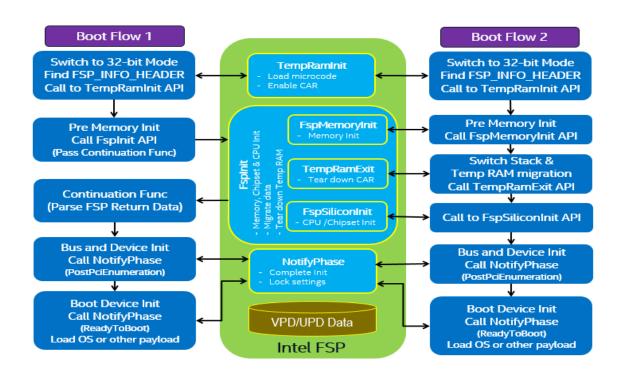

#### a) FSP 1.0 and 1.1:

Fig. 3.4: FSP Boot flow Versions (a) 1.0 (b) 1.1[5]

From Fig. 3.4, one can see FSP 1.0 and 1.1 boot flow. As simple way its look like a same flow but changed many things. From the figure it is clear that at the TempRamInit API both are same but when we see at the next step which is MemoryInit API at that point both version are changed. In FSP 1.0 when control comes at FSPInit API then it will go to FSP package and execute all three API called FspMemoryInit, TempRamInit and FspSiliconInit. After executing this all only control come back to boot loader. Whereas we can see that in FSP 1.1 after every API execution control come back to boot loader means after FspMemoryInit, TempRamInit and FspSiliconInit API control come back and search for boot loader and after that it will execute other phases. So by this method FSP upgraded from 1.0 to 1.1. By doing this change in FSP 1.1, Intel gave more access to boot loader over FSP so that if any change wants to do then can do it easily and give it to FSP.

In the FSP boot flow all the APIs are playing very important role during execution. Every API should call in order to execute FSP correctly by method. So now we can see one by one every API as follows [5]:

#### 1) TempRamInit API:

The above API which is TempRamInit is called immediately after coming out of reset as well as before the memory and cache are available. This API also loads the microcode updation, enables code cache for a region which is specified by the boot loader and it sets up a temporary memory stack to be used prior to main memory stack being initialized. To execute this API, a hardcoded stack memory must be set up with the following values [5]:

- The return address of this API where the TempRamInit returns control

- A pointer for the input parameter for this API

A prototype of this API is define as shown in Fig. 3.5.

```

typedef

EFI_STATUS

(EFIAPI *FSP_TEMP_RAM_INIT) (

IN FSP_TEMP_RAM_INIT_PARAMS *TempRamInitParamPtr

);

```

Fig. 3.5: TempRamInit API prototype [5]

#### 2) FspInit API:

The above API is called after TempRamInit. This API mainly initializes the memory stack, the processors and the chipset to which is required to enable normal operation of these devices. This API accepts a pointer from the data structure that will be dependent on a platform and defined for each FSP binary. The boot loader mainly provides a continuation function as a input parameter when calling this API. After this API completes its execution, it will not return to the boot loader from where it was called but rather it will returns control to the boot loader by calling the same function which is passed to this API as an argument.

A prototype of this API is shown in Fig. 3.6 [5].

```

typedef

EFI_STATUS

(EFIAPI *FSP_INIT) (

IN OUT FSP_INIT_PARAMS *FspInitParamPtr

);

```

Fig. 3.6: FspInit API Prototype [5]

#### 3) NotifyPhase API:

The above API is used to notify the FSP about the all phases in the boot phases. This allows the FSP to take necessary actions as needed whenever different initialization

phases will execute. The phases will be dependent on platform and will be documented with the release of FSP. Recently FSP supports mainly two notify phases [5]:

- Post PCI enumeration

- Ready To Boot

A prototype of NotifyPhase API is as shown in Fig. 3.7 [5].

```

typedef

EFI_STATUS

(EFIAPI *FSP_NOTIFY_PHASE) (

IN NOTIFY_PHASE_PARAMS *NotifyPhaseParamPtr

);

```

Fig. 3.7: NotifyPhase API Prototype [5]

#### 4) FspMemoryInit API:

The above API is called after TempRamInit and initializes mainly the memory stack. This API accepts a pointer to a structure of data which will dependent on platform and defined for each and every FSP binary. This API initializes the memory subsystem portion, initializes the pointer to the HobListPtr, and returns from other to the boot loader from where it was called. Still the memory of system has been initialized in this API, the boot loader should be migrate its stack memory and data from memory to memory of system after this API.

A prototype of this API is shown in Fig. 3.8 [5].

```

typedef

EFI_STATUS

(EFIAPI *FSP_MEMORY_INIT) (

IN OUT FSP_MEMORY_INIT_PARAMS *FspMemoryInitParamPtr

);

```

Fig. 3.8: FspMemoryInit API Prototype [5]

#### 5) TempRamExit API:

The above API is called after FspMemoryInit. This API will release the temporary memory arranged by TempRamInit. This API accepts a pointer to a structure of data that dependent on platform and defined for each and every FSP binary. FspMemoryInit, TempRamExit as well as FspSiliconInit API provide an alternate method to finish the silicon initialization and provides boot loader an opportunity to get control whenever system memory is available and before the temporary memory is release. A prototype of this API is shown in Fig. 3.9 [5].

```

typedef

EFI_STATUS

(EFIAPI *FSP_TEMP_RAM_EXIT) (

IN OUT VOID *TempRamExitParamPtr

);

```

Fig. 3.9: TempRamExit API Prototype [5]

#### 6) FspSiliconInit API:

The above API is called after TempRamExit. FspMemoryInit, TempRamExit as well as FspSiliconInit API provide an different method to complete the silicon initialization. This API initializes the processor and the chipset which including the IO controllers in the chipset required to enable normal operation of such a devices. This API accepts a pointer to a structure of data that dependent on platform and defined for each FSP binary.

A prototype of this API is shown in Fig. 3.10 [5].

```

typedef

EFI_STATUS

(EFIAPI *FSP_SILICON_INIT) (

IN OUT VOID *FspSiliconInitParamPtr

);

```

Fig. 3.10: FspSiliconInit API Prototype [5]

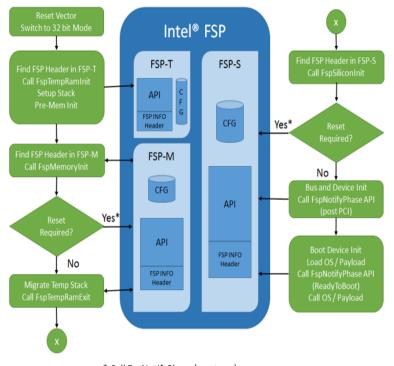

b) FSP 2.0:

\* Call FspNotifyPhase (reset req)

Fig. 3.11: FSP Boot Flow Version 2.0 [6]

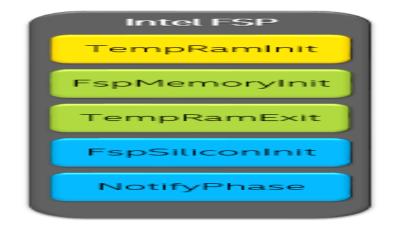

From Fig. 3.11, It is the proposed boot flow of FSP 2.0. Here we can see that major change compared to FSP 1.0 and FSP 1.1 is it divided into main three parts called FSP-T, FSP-M and FSP-S. FSP-T contain API related to temporary memory initialization like TempRamInit API. FSP-M contain API related to main memory initialization and to come out from temporary memory like MemoryInit API and TempRamExit API. FSP- S contains information related to silicon initialization and to notify OS phase as SiliconInit API and NotifyPhase API. Forth portion is like optional which mainly used for backware compatibility with FSP 1.0 and FSP 1.1 specifications. If this component will present it comes first as first component in FSP binary. This component have an FSP\_INFO\_HEADER with header revision 1 or 2 and may provide the interfaces required for backward compatibility with previous FSP specifications.

Now from boot flow, when powered on first control find for TempRamInit from FSP-T and it will look for FSP\_INFO\_HEADER. After completion of this API control back to find FspMemoryInit API from FSP-M and control goes to this APIs header. During this phase, it checks for reset, if it required then it will come again in the same API otherwise it migrates to next API. Next to FspMemoryInit comes FspTempRamExit API which comes in FSP-M which is used to remove temporary memory. After that FSP-S will come which have FspSiliconInit API which will initialize the silicon. After that raise a request for reset, if yes then control goes back to FspSiliconInit otherwise control goes to next phase called FspNotifyPhase API. In this API, FSP gives control to OS and check for two event called PCI enumeration and Ready to boot. Next to that payload will come and OS will boot by using boot loader [6].

# **Chapter 4**

# **FSP Implementation Strategy**

## 4.1 **POST and Phase Code**

The Power On Self Test is activated by the BIOS. It runs a series of checks and diagnostics on your motherboard. The objectives of the BIOS during POST are as follows [6]:

- It check for registers of CPU

- Check the unification of the BIOS with itself

- Check the different peripheral components

- Check the main memory of system

- Check and execute BIOS

- Identify, organize, and select which devices are available for booting

Actually BIOS start its POST when the reset is given to CPU. When reset will occur then first memory location which CPU tries to execute is called as reset vector. During reboot, the CPU will save this code fetch to the BIOS stored on the system flash memory. For Warm boot BIOS will come from stored location called RAM [6].

## 4.1.1 Why POST Code Required

The POST runs very quickly, it hardly takes 2-3 mins to boot to OS and user will normally not even noticed that its happening unless it stops in between because presence of some faulty or some hardware is missing, When turned on the PC, it may happen system starts beeping sounds and then stopped without booting up. That is the POST telling something is wrong with the machine. Here the speaker is used because this test happens so early on, that the video is not even activated yet! Its hard to finds out where actually execution is stopped in which phase or which hardware is faulty or missing in the system.

If execution is stops in between. Some debug boards also doesnt contain serial interface which is used to take serial dumb of POST, In this situation also its really hard to find out where the execution is if its hangs in between, with help of last executed POST code its easy to debug execution is in which phase. So, by this code one can easily determine the problem by using board and we not have to give much effort for finding any error during booting process. POST code itself will tell the error for code [6].

#### 4.1.2 How POST Status Code Works

POST look out the information present by displaying a number to the port 80 (a screen display was not possible with some failure modes). Both the number mainly one is progress indication and second is error codes were generated. If suppose failure is occurred then it will not generate a code, at that time code which was available on last POST will come to aid in diagnosing the problem. There are add-on cards also available that can be placed in to PCI slot and on which post codes can be seen else now a days with this comes inbuilt with debug board. BIOS POST code is shown in Fig. 4.1 [6].

Fig. 4.1: BIOS POST Code in Board [6]

#### 4.1.3 Types of POST Code

POST status codes are mainly divided in to following categories:

- Debug codes

- Error codes

- Progress codes

Firstly for debug codes required for operations related to the basic nature of the information about debug. Second one is error codes which is required for operations related to exception conditions. Next one comes Progress codes which is for operations related to activities of the component classification. The values 0x000x0FFF are in general operations that are common by all subclasses in a class. After class, there are also subclass-specific operations. Out of the all subclass-specific operations, the values 0x10000x7FFF are occupied by this specification. The remaining values (0x80000xFFFF) are not defined by any of this specification and this value can assign for that range by OEMs. The merging of class and subclass operations provides the full set of operations that is given by an entity.

Table 4.1 gives the class for POST code as follows:

| 1)Hardware | 1)Computing Unit             | 1)EFI_COMPUTING_UNIT |

|------------|------------------------------|----------------------|

|            | 2)User accessible peripheral | 2)EFI_PERIPHERAL     |

|            | 3)I/O bus                    | 3)EFI_IO_BUS         |

| 2)Software | 1)Host Software              | 1)EFI_SOFTWARE       |

| Table 4.1: | POST | Code | Classes | [6] |

|------------|------|------|---------|-----|

|------------|------|------|---------|-----|

### 4.1.4 Implementation

Each postcode is falls into specific subclass and class, each class has its unique value which is predefined. There are four main classes as follows:

- Software Host Software

- I/O Bus

- User-Accessible Peripherals

- Computing Unit

For Progress code,

Progress code for execution reached to DXE phase.

PEI\_CPU\_AP\_INIT, 0x35,

This status falls into computing unit class and host processor subclass.

#define PEI\_CPU\_AP\_INIT

(EFI\_COMPUTING\_UNIT\_HOST\_PROCESSOR EFI\_CU\_HP\_PC\_AP\_INIT)

For this status code function call is:

REPORT\_STATUS\_ CODE

(EFI\_PROGRESS\_CODE,

EFI\_COMPUTING\_UNIT\_HOST\_PROCESSOR EFI\_CU\_HP\_PC\_AP\_INIT )

Which will show value 35 on the status codes display.

For error code,

Error code for memory is installed or not:

PEI\_MEMORY\_NOT\_INSTALLED, 0x55,

This status code is falls into software class and PEI foundation subclass.

#define PEI\_MEMORY\_NOT\_INSTALLED

$(EFI\_SOFTWARE\_PEI\_SERVICE\:EFI\_SW\_PEI\_CORE\_EC\_MEMORY\_NOT\_INSTALLED)$

For this status code function call is:

```

REPORT_STATUS_CODE

```

```

(EFI_ERROR_CODE,

```

EFI\_SOFTWARE\_PEI\_SERVICE\_EFI\_SW\_PEI\_CORE\_EC\_MEMORY\_NOT\_INSTALLED

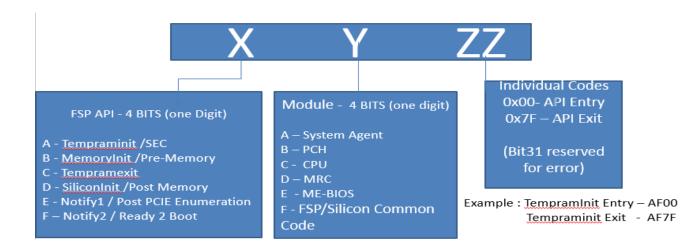

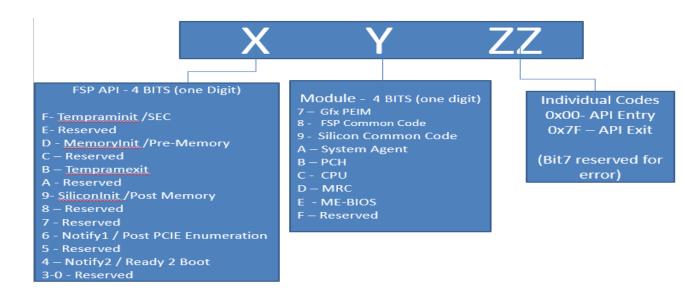

#### 4.1.5 Phase Code

As we show that POST code is required for BIOS, when BIOS gives some error during booting at the same method in FSP when particular code will give error or when FSP will hang at that time it is quite difficult to find where system stucked because there are many API and its phases where system may hang and it will not boot. So, Phase code is such a utility by which we can find very easily that at which point system hang. When Phase code started applying at that time we found that higher nibble is free during BIOS POST code except Memory Reference Code which will take complete 16 bit as DD00 to DD7F. So, we planned to put this into higher nibble API wise so that it will combine for both POST code and Phase code.

#### 4.1.6 Implementation

When Phase code started to implement at that time first of all they give one proposal which is used to set phase code along with the POST code as shown in Fig. 4.2.

Fig. 4.2: Proposed Method for Phase Code