## Highly Optimized 2-Step Design Validation and Integration System Delivery to a Multicore Project

Major Project Report

Submitted in partial fulfillment of the requirements for the degree of

Master of Technology in Electronics & Communication Engineering (VLSI Design)

By

Poornima Khullar (14MECV24)

Electronics & Communication Engineering Branch Electrical Engineering Department Institute of Technology Nirma University Ahmedabad-382 481 May 2016

## Highly Optimized 2-Step Design Validation and Integration System Delivery to a Multicore Project

Major Project Report

Submitted in partial fulfillment of the requirements for the degree of

Master of Technology in Electronics & Communication Engineering (VLSI Design)

By

## Poornima Khullar (14MECV24)

Under the guidance of

**External Project Guide:**

Internal Project Guide:

Mr.Sandip U Rajput Component Design Engineer, Intel India Technology Pvt. Ltd., Bangalore. **Dr. N. M. Devashrayee** Professor, EC Department, Institute of Technology, Nirma University, Ahmedabad.

Electronics & Communication Engineering Branch Electrical Engineering Department Institute of Technology Nirma University Ahmedabad-382 481 May 2016

## Certificate

This is to certify that the Major Project entitled "Highly Optimized 2-Step Design Validation and Integration System Delivery to a Multicore Project" submitted by Poornima Khullar (14MECV24), towards the partial fulfillment of the requirements for the degree of Master of Technology in VLSI Design, Nirma University, Ahmedabad is the record of work carried out by him under our supervision and guidance. In our opinion, the submitted work has reached a level required for being accepted for examination. The results embodied in this major project, to the best of our knowledge, haven't been submitted to any other university or institution for award of any degree or diploma.

Date:

Internal Guide

Place: Ahmedabad

**Program Coordinator**

**Dr. N. M. Devashrayee** (Professor EC ,VLSI)

HOD

**Dr. N. M. Devashrayee** (Professor EC ,VLSI)

Director

**Dr.P.N.Tekwani** (Head of EE Dept.)

**Dr.P.N.Tekwani** (Head of EE Dept.)

## **Project Completion**

This is to acknowledge that Project entitled "Highly Optimized 2-Step Design Validation and Integration System Delivery to a Multicore Project" submitted by Poornima Khullar (14MECV24), towards partial fulfillment of requirements for the degree of Master of Technology in VLSI Design, Nirma University, Ahmedabad is the record of work carried out by her under my supervision and guidance. In my opinion, the submitted work has reached a level required for being accepted for examination.

for Intel Technology India Pvt. Ltd.,

**Project Manager**

Mr.Venkatesh K Elayavalli (Engineering TD Manager)

Date:

Place: Bangalore

## Declaration

This is to certify that

- 1. The thesis comprises my original work towards the degree of Master of Technology in VLSI Design at Nirma University and has not been submitted elsewhere for a degree.

- 2. Due acknowledgment has been made in the text to all other material used.

- Poornima Khullar 14MECV24

## Disclaimer

"The content of this paper does not represent the technology, opinions, beliefs, or positions of Intel Technologies India Pvt. Ltd. Company, its employees, vendors, customers, or associates."

## Acknowledgements

I take immense pleasure in thanking my Mentor Mr. Sandip U Rajput, Component Design Engineer, Mr. Venkatesh K Elayavalli, Engineering Manager Intel Technologies India Pvt. Ltd., Bangalore, for having permitted me to carry out this project work. Through-out the training, they had given me much valuable advice on project work which I am very lucky to benefit from.

I also wish to express my deep sense of gratitude to my guide Dr. N. M. Devashrayee, Institute of technology, Nirma University for being a source of inspiration and for timely guidance during the project.

I would like to express my gratitude and sincere thanks to our Director Dr. P. N. Tekwani, Head of Electrical Engineering Department for allowing me to undertake this thesis work and for his guidelines during the review process.

I would like to express my gratitude and sincere thanks to Mrs. Ruttika Jaju, Component Design Engineer, Intel technologies India Pvt. Ltd., for guiding me throughout my thesis work at Intel, and for making project at Intel more enjoyable.

I wish to thank my classmates for their delightful company which kept me in good humor throughout the journey. Last, but not the least, there are no words to thank my family for their constant support and sacrifices, because of which I'm able to complete the M.Tech. degree successfully.

> - Poornima Khullar 14MECV24

### Abstract

With the rapid growth in semiconductor technology, always in alignment with Moore's prediction, the designers face large integration capacity than they can consume. Furthermore, the cut throat competition in electronic innovation is constraining the designers more and more to minimise the time and meet the "time to-market" window. Without change and evolution in the design process and testing process, it will not be able to simply reduce reasonable amount of time. One possible methodology to reduce this productivity problem is the "design-reuse", which consists in the re-exploitation of the already designed modules in different context, well-known under the name of IP-reuse. In the concept of IP reuse, the IP module is once compiled individually and then with the entire SoC modules, thus it is being validated twice, leading to the concept of 2-step compilation. This report details about compilation flow used for front end design and verification through which time required and the complexity of front end process can be reduced.

In Intel earlier different design teams used their own legacy flows. A new flow was proposed which was a mixture of all the flows and can be used many design teams. Advanced Streamlined System (AS-2) is a mixture of the legacy flows used for validation of the SoC or design modules. It also provides a common environment to many projects while providing project-specific customization. Flows that were used earlier for validation of the IP's were not compatible with today's generation SOC's. Advanced Streamlined System is converged, 2-step but it has performance gap and integration bottlenecks. Performance analysis of the current system is done to reduce the time for validation in best possible ways and finally flow migration to the new highly optimized system.

# Contents

| Ce       | ertifi | cate                                        | i            |

|----------|--------|---------------------------------------------|--------------|

| С        | ertifi | $\operatorname{cate}(\operatorname{Intel})$ | ii           |

| D        | eclar  | ation                                       | iii          |

| Di       | isclai | mer                                         | iv           |

| A        | ckno   | wledgements                                 | $\mathbf{v}$ |

| A        | bstra  | ct                                          | vi           |

| Li       | st of  | Tables                                      | ix           |

| Li       | st of  | Figures                                     | x            |

| Li       | st of  | Abbreviation                                | 1            |

| 1        | Intr   | oduction                                    | <b>2</b>     |

|          | 1.1    | Motivation                                  | 2            |

|          | 1.2    | Problem Statement                           | 3            |

|          | 1.3    | Thesis Organization                         | 3            |

|          | 1.4    | VLSI Design Flow                            | 3            |

|          | 1.5    | Front End VLSI Flow                         | 5            |

| <b>2</b> | Lite   | erature Review                              | 7            |

|          | 2.1    | Behavioral v/s Structural Modeling          | 7            |

|          | 2.2    | 2-Step Compilation                          | 8            |

|          | 2.3    | Legacy and SoC Integration Flow             | 9            |

|          |        | 2.3.1 Legacy Flow                           | 10           |

|          |        | 2.3.2 Advanced flow or SoC Integration Flow | 10           |

|          | 2.4    | Advanced Streamlined System (AS-2)          | 11           |

|          |        | 2.4.1 Flow Mechanism                        | 11           |

|          |        | 2.4.2 Integration Bottlenecks               | 12           |

|    |       | 2.4.3  | Summary                                                                | 13        |

|----|-------|--------|------------------------------------------------------------------------|-----------|

| 3  | Per   | formar | nce Analysis                                                           | 14        |

|    | 3.1   | Impor  | tance of Performance Analysis                                          | 14        |

|    | 3.2   | Perl P | rofiling Tool – NYTProf                                                | 15        |

|    |       | 3.2.1  | Statement Profiler                                                     | 15        |

|    |       | 3.2.2  | Subroutine Profiler                                                    | 16        |

|    | 3.3   | Perfor | mance Analysis of AS-2                                                 | 16        |

|    |       | 3.3.1  | Experiments                                                            | 16        |

|    |       | 3.3.2  | Critical Observation in AS-2                                           | 22        |

| 4  | Des   | ign Pr | ototyping and Results                                                  | <b>24</b> |

|    | 4.1   | Impor  | tance of AS-2 Prototype                                                | 24        |

|    | 4.2   | Perl T | esting Module                                                          | 26        |

|    | 4.3   | Test C | Cases added to AS-2 Prototype                                          | 27        |

|    |       | 4.3.1  | Test for loading various checks for the SoC or IP                      | 28        |

|    |       | 4.3.2  | Test to check attributes being passed from parent to child design con- |           |

|    |       |        | figuration for the SoC or IP                                           | 30        |

|    |       | 4.3.3  | Test for Flow Equivalence Checking for the SoC or IP                   | 31        |

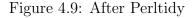

|    |       | 4.3.4  | Test for checking whether AS-2 modules are Perltidy compatible         | 31        |

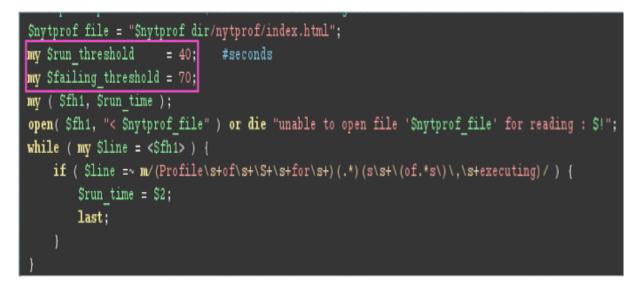

|    |       | 4.3.5  | Test for Performance Checking of AS-2 prototype                        | 33        |

|    |       | 4.3.6  | Improvement in Test                                                    | 34        |

|    |       | 4.3.7  | Unit Test for Environment setup for AS-2 Flow                          | 37        |

|    | 4.4   |        | ary                                                                    | 39        |

|    | 1.1   | o anni |                                                                        | 00        |

| Co | onclu | sion   |                                                                        | 40        |

|    |       |        |                                                                        |           |

#### References

**41**

# List of Tables

| 2.1 | Flow Comparison Table           | 11 |

|-----|---------------------------------|----|

| 3.1 | Results of Performance Analysis | 20 |

# List of Figures

| 1.1  | VLSI Design Flow                                                                                        | 4              |

|------|---------------------------------------------------------------------------------------------------------|----------------|

| 1.2  | Front End VLSI Design Flow                                                                              | 6              |

| 2.1  | Behavioral Modeling Example                                                                             | $\overline{7}$ |

| 2.2  | Structural Modeling Example                                                                             | 8              |

| 2.3  | IP Classification                                                                                       | 9              |

| 2.4  | Implementation of AS-2                                                                                  | 10             |

| 2.5  | Flow of AS-2                                                                                            | 12             |

| 2.6  | Integration Flow of AS-2                                                                                | 13             |

| 3.1  | Statement Profile Example                                                                               | 15             |

| 3.2  | Experiment 1A                                                                                           | 17             |

| 3.3  | Flow Graph of Experiment 1A                                                                             | 17             |

| 3.4  | Experiment 1B                                                                                           | 18             |

| 3.5  | Experiment 1C $\ldots$ | 18             |

| 3.6  | Experiment 1D                                                                                           | 19             |

| 3.7  | Experiment 1E $\ldots$ | 20             |

| 3.8  | Reoccurring Loop                                                                                        | 21             |

| 3.9  | Experiment 2A                                                                                           | 21             |

| 3.10 | Experiment 2B                                                                                           | 22             |

| 3.11 | Color Coding in NYTProf                                                                                 | 23             |

| 3.12 | Call Tree in NYTProf                                                                                    | 23             |

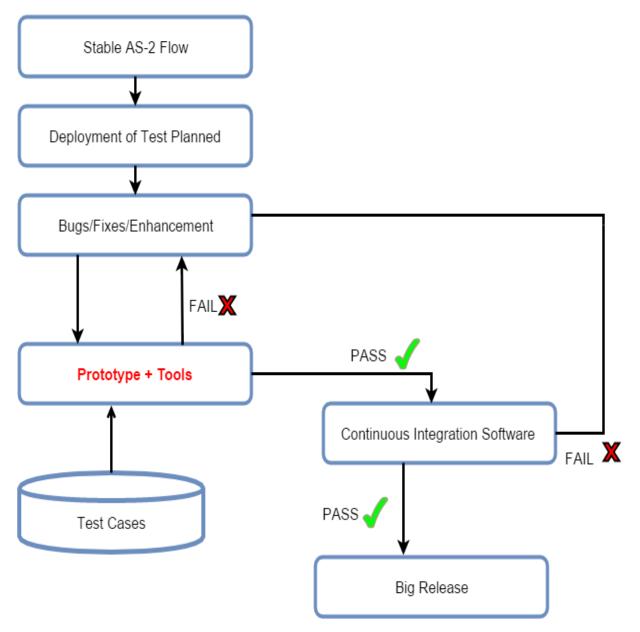

| 4.1  | AS-2 Work Flow with IP                                                                                  | 25             |

| 4.2  | AS-2 Work Flow with Prototype                                                                           | 26             |

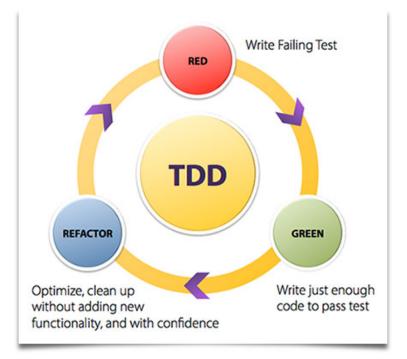

| 4.3  | Test Driven Development                                                                                 | 28             |

| 4.4  | Test for loading checks on SoC 1                                                                        | 29             |

| 4.5  | Test for loading checks on SoC 2                                                                        | 29             |

| 4.6  | Test for checking attributes                                                                            | 30             |

| 4.7  | Test for Comparing Flow Specification                                                                   | 31             |

| 4.8  | Before Perltidy                                                                                         | 32             |

| 4.9  | After Perltidy                                                                                          | 32             |

| 4.10 | Test for Performance Checking of AS-2 prototype[1] | 33 |

|------|----------------------------------------------------|----|

| 4.11 | Test for Performance Checking of AS-2 prototype[2] | 33 |

| 4.12 | Test for Performance Checking of AS-2 prototype[3] | 34 |

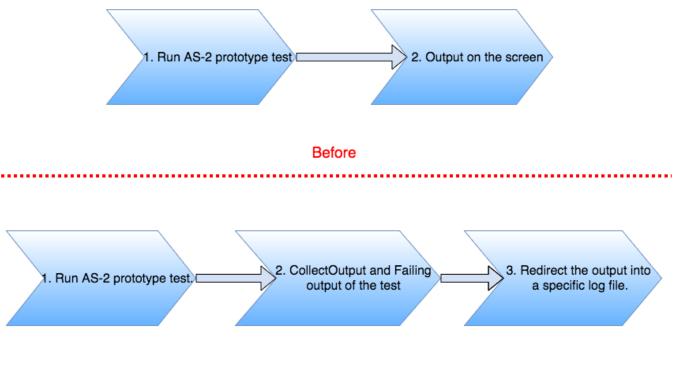

| 4.13 | Logging of AS-2 Flow test                          | 35 |

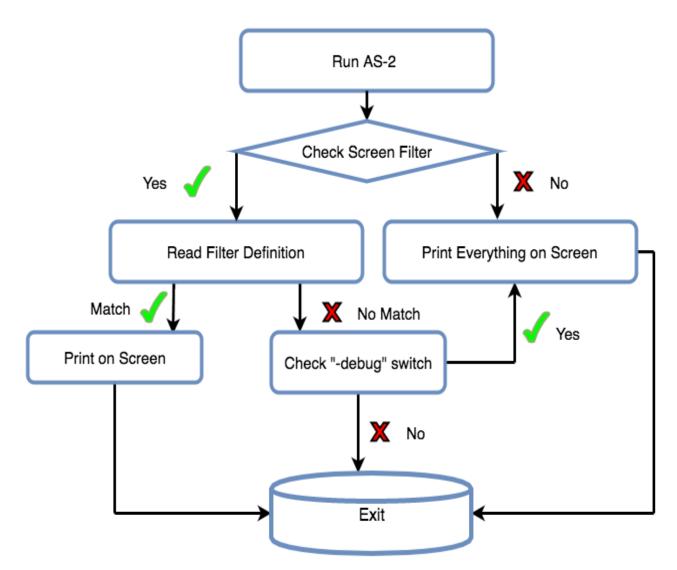

| 4.14 | Function of Screen Filter                          | 36 |

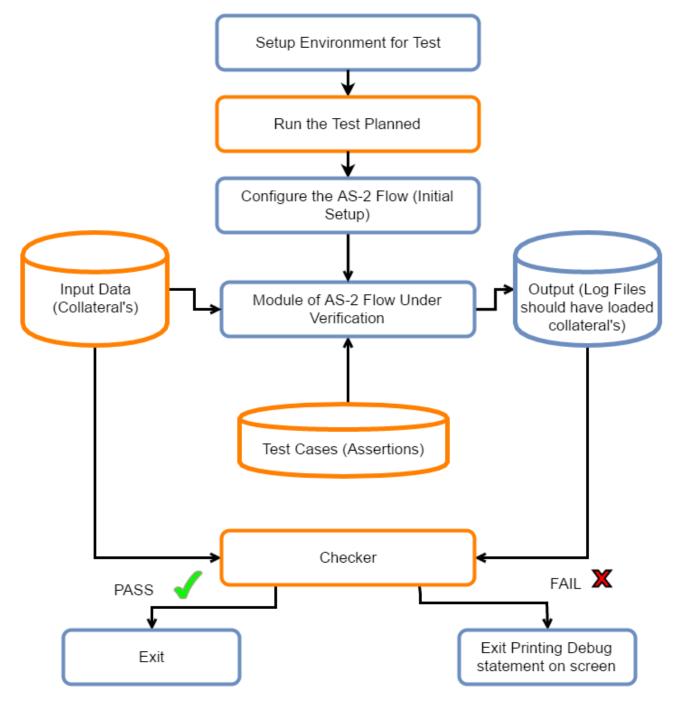

| 4.15 | Function of Unit Test                              | 38 |

# List of Abbreviation

| RTL  | Register Transfer Logic                  |

|------|------------------------------------------|

| SoC  | System on Chip                           |

| CAD  | Computer Aided Design                    |

| HDL  | Hardware Description Language            |

| AS-2 | Advanced Streamlined System              |

| FEDV |                                          |

| PERL | Practical Extraction and Report Language |

| EDA  | Electronic Design Automation             |

| DUT  | Design Under Test                        |

## Chapter 1

## Introduction

All practical VLSI circuit are very, very large or very, very complex in nature like a processor, which are large and very complex applications. A complex circuit may have hundreds of inputs, outputs and millions of gates, in order to create complex circuit consisting of millions of transistors manually, can be difficult. For such problem a CAD tool is required which will help to automate the design for given specification.

CAD tools provide several advantages like it has an ability to assess complex conditions in which solving a single problem which may creates other problems. It use analytical methods to evaluate the cost of a decision and uses synthesis methods to provide a solution for the same. It concede the process of introducing and investigating the solutions at the same time.

### 1.1 Motivation

The entire project covers working on AS-2 which is a front end design IP validation system. It is converged, 2-step, and based on next generation build flows. It is a common solution used for both big and small IP. This project gives a good idea of methodology used in front end IP validation. It involves development and enhancing features required in the front end part of complex SoC integration. It reduces the design time, time to market and can handle design complexity easily.

Performance analysis of the current system is done to find the integration bottlenecks and enhancement can be done accordingly. With that developing a prototype for AS-2 as it was running on an IP which runs maximum qualification checks but not all. The prototype would imitate the design and contain test case for different IP blocks and perform all qualification checks.

### **1.2** Problem Statement

Designing a module which can be an SOC or IP that are optimized along the three axis of area, power and time is a difficult task. Achieving optimum balance along any two axis is a simpler task than across the three. To handle the rising time to market pressure and increasing design complexities we need efficient validation methodologies that can give maximum coverage check of the design in less amount of time. AS-2 is very efficient in the concept of IP reuse and compiling an entire soft SoC design.

But AS-2 has performance gap and integration bottlenecks which hinders the goal of reduction in time drastically. Performance analysis of AS-2 reveals the various gaps which when removed can enhance performance and finally moving to optimized AS-2 which would be much faster n efficient.

### **1.3** Thesis Organization

The thesis is organized in 5 chapters, the details of each chapter is as follows:-

- \* Chapter 1: This chapter gives information about VLSI flow and the front end flow used in SoC design process.

- \* Chapter 2: It describes the various legacy flow that are used for soft IP validation.

- \* Chapter 3: This chapter explains the performance analysis results of the AS-2 system in detail along with its advantages and fault.

- \* Chapter 4: Implementation of Prototype which is used to save the compile time of the design.

- \* Chapter 5: Conclusion

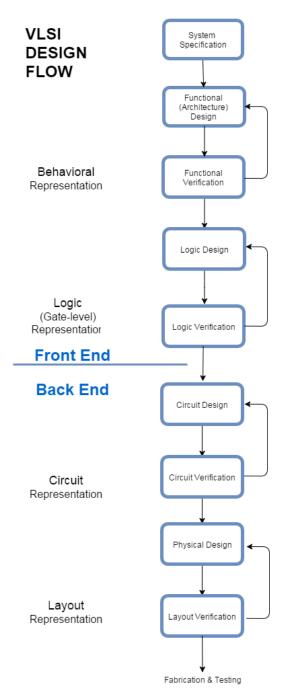

### 1.4 VLSI Design Flow

The design process of any integrated circuit at various levels is evolutionary in nature. The VLSI design flow generalizes the step, which in itself are complex task and require various tools at different design level. The VLSI design flow is partitioned into two parts: Frontend design flow and Backend design flow. With the two flows together, a functional chip could be created from scratch to fabrication.[5]

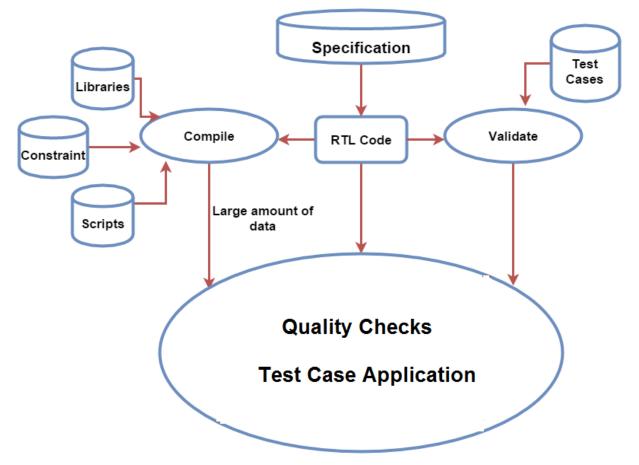

Specification describes abstractly the functionality, architecture, and the interface of the digital IC circuit to be designed. Here, vendors get feedback from potential customers on their requirement. When this is completed, a final specification sheet with all major technical details is constructed. Behavioral description is then build to evaluate the design in terms of performance, functionality, compliance to given standards, and other needs specified. RTL description is done using HDLs. RTL level analysis is then reformed to a gate-level netlist with the help of logic synthesis tools. A gate-level netlist is a description of the design in terms of gates and connections between them, which fulfils the timing, power and area specifications. These parameters of timing are checked by performing static time analysis. Finally a physical layout is created, which will be verified and validated and then sent to fabrication or production.

Figure 1.1: VLSI Design Flow

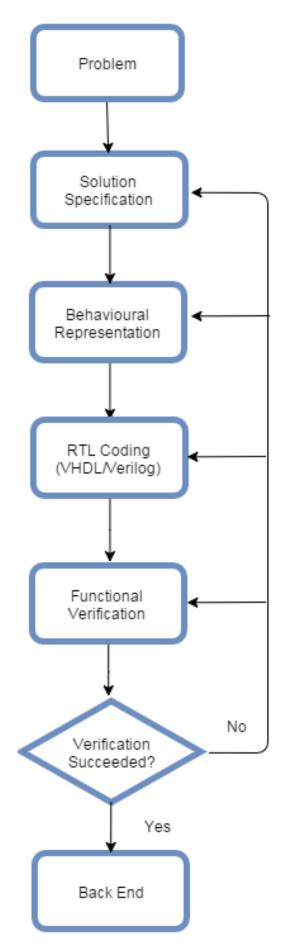

## 1.5 Front End VLSI Flow

The frontend flow obtain a solution for a user problem or it converts specification into an RTL circuit description. The flow starts from specification, and mostly involves verification at each step to achieve good initial design confidence. Later on the process is handled over to back end flow, where a number of process required for physical implementation of design are carried out. (Figure 1.2)

The design complexities are growing day by day so a single tool is unable to provide good remedy for all the design, compilation and verification related issues. With increasing System-on-Chip (SoC) complexity, the software content combined with it and the rising time-to-market pressures are increasing the need for an advance automated system for design, compilation and verification solution which saves time as well as efforts, during the designing period. The term different VLSI flows means the different design, compilation verification flows of tools by different CAD tool provider companies.[5]

The AS-2 gives higher degree of design confidence and bringing down the risk of re-spin or repeated efforts is the main aim of the system, which ultimately contributes for less time to market. The system is:-

- \* Converged: Used by almost all front end flows.

- \* Amalgam: It makes design compilation and validation of SoC easier and faster and takes all the advantages of the earlier used legacy flow.

- \* Streamlined: It is a new generation build flow compatible with today's SoC and IP block validation.

My work goes around the different periphery of the AS-2, performance analysis of AS-2 and enhancing features of the system.

Figure 1.2: Front End VLSI Design Flow

## Chapter 2

## Literature Review

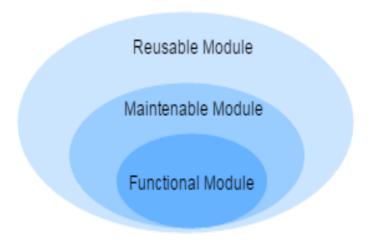

One possible methodology to increase productivity of design is to accept the "design-reuse" concept, which require re-exploitation of the already designed modules in different context. This idea meant building up new IP or modules using the existing ones. This results in a new concept well-known under the name of IP-reuse. Moreover, an IP is nothing other than a module implemented with reuse capabilities (IP = Module + Reuse Capabilities), which leads to the concept of 2-step compilation.[2].

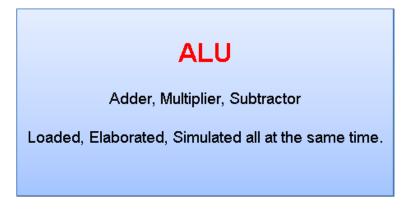

## 2.1 Behavioral v/s Structural Modeling

When you are modeling hardware, you can write code in different ways, independent on the HDL you are using (i.e., either VHDL or Verilog). Behavioral modeling refers to a way to write code (more precisely, to model your hardware design) based on its functionality: it's like writing the algorithm that solves your problem. Certain disadvantages of behavioral modeling are that it does not support the concept of component re-usability. The entire design is loaded, elaborated and simulated at the same time which takes large amount of compile time hence increasing time to market. Moreover it gives a non-modular design description which is low quality and not optimized.

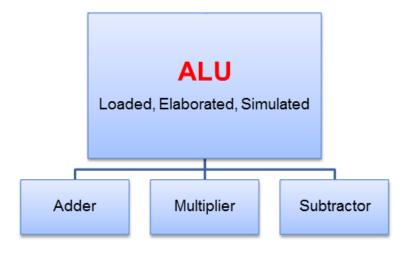

Figure 2.1: Behavioral Modeling Example

With structural code, on the other hand, you are connecting different parts together to get the final design. In some way you will generally use a mixture of the two: if you think to bottom-up approach, you first create behavioral/algorithmic code for lowest-level blocks (e.g., flip-flop) and once you move up across the abstraction levels you mix different blocks together and connect them in a structural code (e.g., shift register). Structural modeling gives modular design description and support the concept of design re-usability. It's a well-known fast that it's easier to optimize small design rather than big ones. As it's a modular design technique optimized small modules that can be inherited in larger modules, thus giving a more optimized overall design and brings the concept of 2-step compilation.

Figure 2.2: Structural Modeling Example

## 2.2 2-Step Compilation

In the concept of IP reuse, the IP module is once compiled individually and then linked with entire SoC modules, thus it is validated twice leading to the concept of 2-step compilation. The 2-step support parallelization of process and linking easily with SoC easier. Here the IP reuse is only for the RTL collateral not for the Validation collateral. Moreover, to be reusable, a module must be:-

- \* Configurable- constructed to solve a general user problem.

- $\ast\,$  Portable- designed independent of technology and CAD tools.

- \* Debugable- verified and validated with a high degree of confidence "bug free ".

- \* Readable- clearly documented on the basis of applicability, restrictions, and defined interfaces.

An IP or module can be classified as a reusable module by these of quality:

- \* Functional- it is the lowest level of a module which can be reached to be able to use it.

- \* Maintainable- it means being functionally correct, a maintainable module which is well documented, with clean and commented coding.

- \* Reusable- A reusable module would have many improvement on a maintainable module or IP.

"For the purpose of module re-usability, an industrial corporation called VSIA (Virtual Socket Interfaces Alliance) was established in 1997. It's aim is to create a set of standards for making IP reusable. These standards are well defined, described and accepted in today's semiconductor world".[2].

Figure 2.3: IP Classification

## 2.3 Legacy and SoC Integration Flow

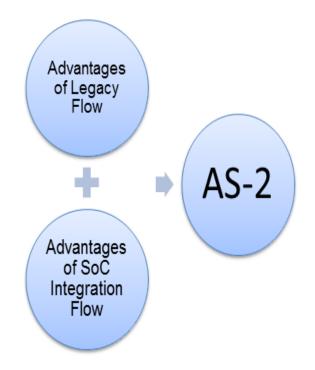

Flows that are being used for validation of Soft IP's are not compatible with today's generation SoC's and IP's. The two flows that were used earlier are **Legacy Flow** and **SoC Integration Flow or Advanced Flow**. Both had certain advantages and disadvantages, but the common disadvantage of them was the time taken to compile the entire SoC design which was large, thus increasing time to market.

#### 2.3.1 Legacy Flow

It worked on the concept of behavioral modeling design description (Figure 2.1) i.e. nonmodular design description. It didn't supported the concept of IP reuse and thus no 2-step compilation. As the design is not optimized thus limiting the quality of the checks done on it. The compilation time was very high thus limiting the performance of the flow.[6].

#### 2.3.2 Advanced flow or SoC Integration Flow

It supported modular design concept, IP reuse, saved design time also but didn't had a proper qualification step. It has high maintenance cost and difficult to deploy or proliferate to different segment of design system. If the flow failed on certain checks it was difficult to debug the cause of failure. It was not manageable either and cannot be extended to the growing technology because of its incompatibility.[6]

Solution to the above problem is AS-2 which takes all the advantages of the above flows and reduces the compilation time drastically thus reducing time to market and increasing the performance drastically

Figure 2.4: Implementation of AS-2

| S.no. | Legacy Flow                      | SoC Integration Flow        | AS-2                       |

|-------|----------------------------------|-----------------------------|----------------------------|

| 1.    | Behavioral Modelling             | Partial Structural Mod-     | Structural Modelling       |

|       |                                  | elling                      |                            |

| 2.    | No IP Reuse (Cannot be           | IP reuse possible(not       | IP reuse possible (com-    |

|       | extended to new technol-<br>ogy) | completely)                 | pletely)                   |

|       |                                  |                             |                            |

| 3.    | Suitable for small designs       | Not scalable for larger de- | Scalable for high capacity |

|       |                                  | signs                       | designs                    |

| 4.    | No 2-Step Compilation            | Flow not modular, thus      | Enabled 2-Step Compi-      |

|       |                                  | not easy to proliferate     | lation (For new technol-   |

|       |                                  |                             | ogy)                       |

| 5.    | Performance Limiter              | Performance Limiter         | Performance Limiter        |

|       | (Slower)                         | (Slower)                    | (Slower)                   |

## 2.4 Advanced Streamlined System (AS-2)

AS-2 is a mixture of both legacy flow and SoC integration flow. Taking advantages of both flows and having some new features of itself, it reduces the compile time drastically. It also support the concept of IP reuse and thus it is converged, does 2-step compilation and is much more advanced as compared to other system. AS-2 is facilitated both for small as well as complex IP's. As AS-2 is a mixture of various legacy flow it supports all earlier flow used by different design system at Intel.

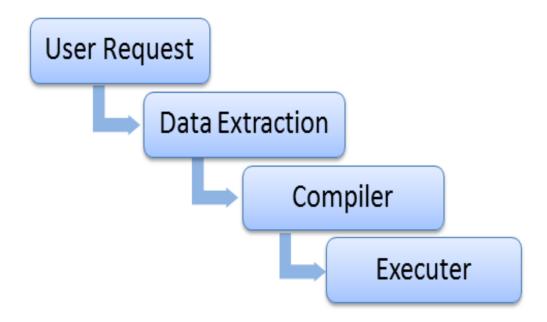

### 2.4.1 Flow Mechanism

The various step of hybrid flow are as following:-

- \* User Specification Request –This stage specifies what action the user wants to perform on the design. It can be running only a particular test, compiling a certain part of the design, compiling a certain library etc., using command line interface. Validation of the user commands is also done in this step.

- \* **Data Extraction** Based on the user request the AS-2 decided the input configuration, the design data which would be multiple RTL source code, library needed to compile for the design and the constraints given by the user and according to the environment set. Design reuse in one of the feature of the system which is done in this step. A large numbers of algorithms are used in this step, which makes the data extraction easy and fast.

- \* **Compilation** the actual sets of commands are executed on the design. Various checks and test cases are also deployed on the design.

\* **Execution** - The output of the compiler is fed into the executor that generates the output log files which can be looked if anything fails.

Figure 2.5: Flow of AS-2

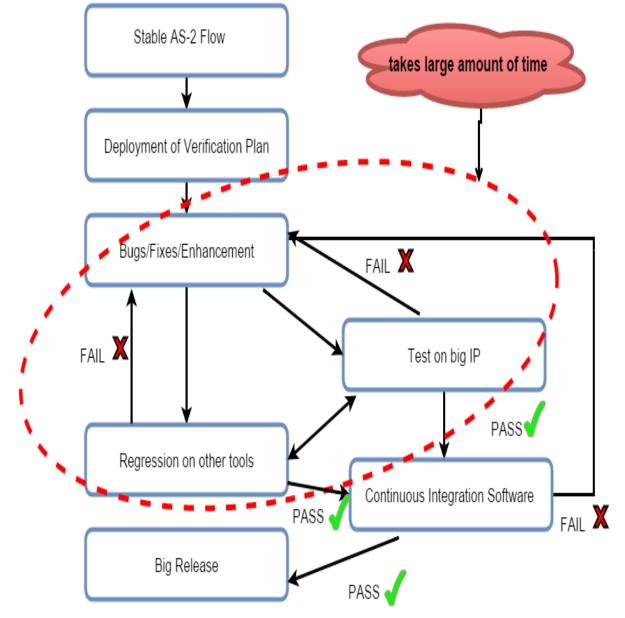

#### 2.4.2 Integration Bottlenecks

Besides having various advantages AS-2 still has some problem. It does not address the integration problem as per requirement. On the data extraction step of the flow mechanism it fails to pass data to different compiler. Moreover it produces large amount of data for analysis while running complex algorithm and are time consuming and hence increases time to market. It had no provision of flow testing and prototyping.

Figure 2.6: Integration Flow of AS-2

### 2.4.3 Summary

In order to find the performance and integration gap performance analysis of the current system needs to be done and finally migration to Optimized AS-2 system.

## Chapter 3

## **Performance Analysis**

Testing, verification and validation problems are generally consigned by separate communities - VLSI testing is generally assumed to belong to the Electrical Engineering domain, while verification and validation are assumed of as Computer Science subjects. While in industry, the methodologies deployed by testing, verification and validation engineers are also different. While the application area of these problems is surely not same, there is one similarity among all of them - and that is the underlying mathematical build or framework.

## 3.1 Importance of Performance Analysis

Performance analysis constitutes certain part of verification. Coverage is a measure to evaluate the progress of functional verification. This gives a clear picture on how well the design has been verified and also gives away the design corners still left uncovered. Code coverage and functional coverage are the different coverage methods used in functional verification. Besides having various advantages AS-2 still has some problem. It does not address the integration problem as per requirement.

- \* On the data extraction step of the flow mechanism it fails to pass data to different compiler.

- \* Moreover it produces large amount of data for analysis while running complex algorithm and are time consuming and hence increases time to market.

- \* It had no provision of flow testing and prototyping.

- \* Code quality checks are slower compared to other flow.

- \* While doing the analysis of the flow it had many recursive flows or flow hierarchy which need proper convergence to have proper dependent flow hierarchy.

The profiling analysis on the AS-2 is done by Perl profiling tool NYTProf which is being introduced in the next segment. It's a very accurate and efficient system.

## 3.2 Perl Profiling Tool – NYTProf

For sequential code, it is important to collect statistical data of the programs and certain run-time characteristic like time spent in each functions, number of times the function is called and code lines. This is called Profiling. The design or system is run under the control of a profiling tool, which at the run end gives the summary of an execution.[7].

- \* NYTProf is effectively does the work of two profilers. It acts both as statement profiler, and a subroutine profiler.

- \* It has resolution of nanosecond.

- \* It generates HTML report which included code coverage, statement flow and interactive Tree Maps. (Figure 3.12)

- \* NYTProf maintains extra information in the data file to capture each and every detail of the run that may be useful when evaluating the performance.

- \* It also records all the file-name and number of calls of all the subroutines.

- \* NYTProf can profile applications and system that fork between different processes, and does it with so efficiency so that there is no loss of performance. (Figure 3.3)

- \* nytprofhtml only works with a single output profile file. So in order to merge with multiple files use nytprofmerge.

- \* It also reveals the code coverage of entire flow part by part.

#### 3.2.1 Statement Profiler

The statement profiler evaluates the time between entering one Perl statement and entering the next statement. It is similar to Statement coverage. The number of times statement is executed can be calculated to enclosing block and enclosing function.

Figure 3.1: Statement Profile Example

Looping for the first time around the loop, the more time spent analysing the condition would be recorded as the time spent on the last statement executed in the loop!

#### 3.2.2 Subroutine Profiler

The subroutine profiler evaluates the time between entering a subroutine and leaving it. When the subroutine is called the call count is incremented and the duration is noted. Each time the subroutine is called, separate counts and durations are recorded for every location where the subroutine is called.

### 3.3 Performance Analysis of AS-2

- \* Step 1- The first step to carry out performance analysis of AS-2 is to deploy it on some design or IP Block, while running NYTProf on it simultaneously.

- \* Step 2- The NYTProf run gives a number of nytprof.out files which need to be analyzed further. The nytprof.out file is read by nytprof.html. If there is more than one nytprof.out file we could use nytprof.merge. Next step is thus analysis.

- \* Step 3-During the analysis we need to track Master Violation that consumes large amount of time during compile.

- \* Step 4- Look the code of **Master Violation**. Reproduce the same violation using a test case in prototype and re-run the flow.

- \* Step 5- Optimize the flow part and re-run to see the reduction in time. The optimization can be anything either reducing number of calls or removing a reoccurring loop.

- \* Step 6 Analyze the HTML report again. Track, look and optimize the flow. Repeat the above to get maximum reduction in time.

The branch taking large amount of time should be tracked down and unnecessary code should be optimized. For the optimization in the actual flow, some experiments were done locally before applying to flow. While optimization we need to make sure the functionality is completely restored, like a mistake that generally done when the actual purpose of keyword is not known, eg. : Croak can be misunderstood by print but both have different meaning. Experiments done are as follow.

#### 3.3.1 Experiments

From a given design file, I have to extract given tags that is given as input by the user and display the information for the user input in optimized way.

\* Using three loop - Wrote a script to read a design file using three nested loop and then acting along user's wish. Profiling results are as follow:

#### Performance Profile Index For ./exp1\_1.pl

Profile of ./exp1\_1.pl for 15.4s (of 15.4s), executing 14582 statements and 3752 subroutine calls in 9 source files.

| Top 15 | Top 15 Subroutines |   |                   |                   |                                                |  |  |

|--------|--------------------|---|-------------------|-------------------|------------------------------------------------|--|--|

| Calls  | Ρ                  | F | Exclusive<br>Time | Inclusive<br>Time | Subroutine                                     |  |  |

| 6      | 2                  | 1 | 15.4s             | 15.4s             | main:: <u>CORE:readline</u> (opcode)           |  |  |

| 1      | 1                  | 1 | 2.69ms            | 2.72ms            | Config::BEGIN@10                               |  |  |

| 10     | 2                  | 1 | 2.26ms            | 2.26ms            | List::MoreUtils:: <mark>firstidx</mark> (xsub) |  |  |

| 1      | 1                  | 1 | 2.10ms            | 15.0ms            | main::BEGIN@2                                  |  |  |

| 5      | 1                  | 1 | 1.95ms            | 1.95ms            | DynaLoader:: <u>CORE:ftdir</u> (opcode)        |  |  |

| 1      | 1                  | 1 | 1.88ms            | 7.50ms            | List::MoreUtils::BEGIN@6                       |  |  |

| 3537   | 1                  | 1 | 1.11ms            | 1.11ms            | main:: <u>CORE:match</u> (opcode)              |  |  |

| 1      | 1                  | 1 | 1.02ms            | 5.58ms            | DynaLoader:: <mark>BEGIN@22</mark>             |  |  |

| 1      | 1                  | 1 | 1.00ms            | 1.00ms            | List::MoreUtils::BEGIN@5                       |  |  |

| 1      | 1                  | 1 | 852µs             | 1.75ms            | Config::BEGIN@11                               |  |  |

| 1      | 1                  | 1 | 760µs             | 803µs             | List::MoreUtils::BEGIN@4                       |  |  |

| 1      | 1                  | 1 | 740µs             | 813µs             | vars:: <mark>BEGIN@7</mark>                    |  |  |

| 1      | 1                  | 1 | 707µs             | 707µs             | DynaLoader:: <u>CORE:ftfile</u> (opcode)       |  |  |

| 88     | 3                  | 1 | 670µs             | 670µs             | main:: <u>CORE:print</u> (opcode)              |  |  |

| 1      | 1                  | 1 | 436µs             | 436µs             | main:: <u>CORE:open</u> (opcode)               |  |  |

See <u>all 82 subroutines</u>

You can view a treemap of subroutine exclusive time, grouped by package. NYTProf also generates call-graph files in <u>Graphviz</u> format: <u>inter-package calls</u>, <u>all inter-subroutine calls</u>.

You can hover over some table cells and headings to view extra information. Some table column headings can be clicked on to sort the table by that column.

Figure 3.2: Experiment 1A

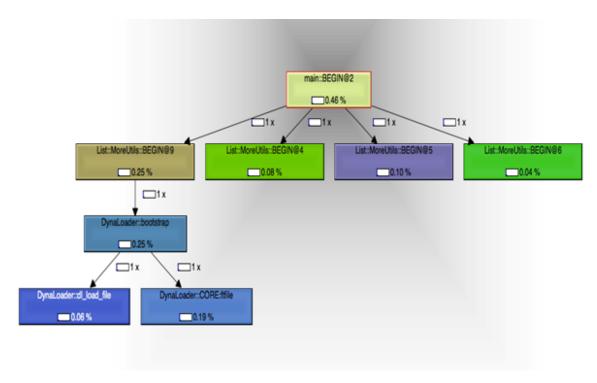

Figure 3.3: Flow Graph of Experiment 1A

\* Using Array – Wrote a script to read a design file using array and then acting along user's wish. Profiling results are as follow:

| Jbroutines                                              |

|---------------------------------------------------------|

| Calls P F Exclusive Inclusive Subroutine                |

| 7 3 1 14.4s 14.4s main:: <u>CORE:readline</u> (opcode)  |

| 602 2 1 1.50ms 1.50ms main:: <u>CORE:match</u> (opcode) |

| 92 4 1 990µs 990µs main:: <u>CORE:print</u> (opcode)    |

| 1 1 1 517μs 517μs main:: <u>CORE:open</u> (opcode)      |

| Source Code Files — ordered by exclusive time then name |       |                    |                  |  |  |

|---------------------------------------------------------|-------|--------------------|------------------|--|--|

| Stmts Exclusive<br>Time                                 |       | Reports            | Source File<br>▼ |  |  |

| 6773                                                    | 14.5s | line • block • sub | exp1_1a.pl       |  |  |

Report produced by the NYTProf 4.08 Perl profiler, developed by Tim Bunce and Adam Kaplan.

Figure 3.4: Experiment 1B

\* Using Hashes - Wrote a script to read a design file using hashes and then acting along user's wish. Profiling results are as follow:-

| Performance Profile Index   |                      |                       |                                    |                                           |                                                                                                                                                                            |                                                            |  |  |

|-----------------------------|----------------------|-----------------------|------------------------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--|--|

| For ./exp1_1b.pl            |                      |                       |                                    |                                           |                                                                                                                                                                            |                                                            |  |  |

| Profile                     | of .                 | /exp                  | 1_1b.pl fo                         | or 12.0s (o                               | f 12.0s), executing 6767 state                                                                                                                                             | ments and 3847 subroutine calls in 1 source files.         |  |  |

| Subro                       | utin                 | es                    |                                    |                                           |                                                                                                                                                                            |                                                            |  |  |

| Calls                       | P                    | F                     | Exclusive<br>Time                  | Inclusive<br>Time                         | Subroutine                                                                                                                                                                 |                                                            |  |  |

| 7                           | 3                    | 1                     | 12.0s                              | 12.0s                                     | main:: <u>CORE:readline</u> (opcode)                                                                                                                                       |                                                            |  |  |

| 3598                        | 2                    | 1                     | 1.76ms                             | 1.76ms                                    | main:: <u>CORE:match</u> (opcode)                                                                                                                                          |                                                            |  |  |

| 241                         | 4                    | 1                     | 1.45ms                             | 1.45ms                                    | main:: <u>CORE:print</u> (opcode)                                                                                                                                          |                                                            |  |  |

| 1                           | 1                    | 1                     | 556µs                              | 556µs                                     | main:: <u>CORE:open</u> (opcode)                                                                                                                                           |                                                            |  |  |

| VYTPro<br>You car<br>Some t | of a<br>n ho<br>tabl | lso (<br>over<br>e co | generates<br>over som<br>olumn hea | s call-graph<br>le table cel<br>dings can | tine exclusive time, grouped b<br>files in <u>Graphviz</u> format: inter<br>Is and headings to view extra<br>be clicked on to sort the table<br>v exclusive time then name | package calls, all inter-subroutine calls.<br>information. |  |  |

| Stmts                       |                      | clus                  | ive Repo                           | rts                                       | Source File                                                                                                                                                                |                                                            |  |  |

| 6767                        | Ti                   |                       | Oc line                            | block - ci                                | v avai ib al                                                                                                                                                               |                                                            |  |  |

| 6767                        |                      | 12                    | us <u>line</u> •                   | • <u>block</u> • <u>s</u> u               | ib exp1_1b.pl                                                                                                                                                              |                                                            |  |  |

|                             |                      |                       |                                    |                                           |                                                                                                                                                                            |                                                            |  |  |

|                             |                      |                       |                                    |                                           |                                                                                                                                                                            |                                                            |  |  |

Figure 3.5: Experiment 1C

\* Using Regular Expression - Wrote a script to read a design file using regular expressions and then acting along user's wish. Profiling results are as follow:-

#### **Performance Profile Index** For ./exp1\_1c.pl

Profile of ./exp1\_1c.pl for 222ms (of 272ms) executing 64321 statements and 102876 subroutine calls in 14 source files

| Top 15 | Top 15 Subroutines |   |                                  |        |                                     |  |  |  |  |

|--------|--------------------|---|----------------------------------|--------|-------------------------------------|--|--|--|--|

| Calls  | Calls P F          |   | Exclusive Inclusive<br>Time Time |        | Subroutine                          |  |  |  |  |

| 53006  | 3                  | 1 | 19.0ms                           | 19.0ms | main:: <u>CORE:match</u> (opcode)   |  |  |  |  |

| 49408  | 1                  | 1 | 12.7ms                           | 12.7ms | main:: <u>CORE:regcomp</u> (opcode) |  |  |  |  |

| 1      | 1                  | 1 | 8.60ms                           | 17.0ms | main::BEGIN@3                       |  |  |  |  |

| 1      | 1                  | 1 | 5.97ms                           | 16.3ms | main::BEGIN@2                       |  |  |  |  |

| 1      | 1                  | 1 | 3.68ms                           | 7.03ms | Data::Dumper::BEGIN@20              |  |  |  |  |

| 1      | 1                  | 1 | 2.36ms                           | 2.39ms | Carp:: <b>BEGIN@4</b>               |  |  |  |  |

| 1      | 1                  | 1 | 2.35ms                           | 2.97ms | Getopt::Long::BEGIN@208             |  |  |  |  |

| 1      | 1                  | 1 | 2.00ms                           | 2.08ms | Exporter:: <b>as_heavy</b>          |  |  |  |  |

| 1      | 1                  | 1 | 1.49ms                           | 1.49ms | XSLoader:: <mark>load</mark>        |  |  |  |  |

| 1      | 1                  | 1 | 1.35ms                           | 1.73ms | Getopt::Long::BEGIN@19              |  |  |  |  |

| 130    | 4                  | 1 | 1.30ms                           | 1.30ms | main:: <u>CORE:print</u> (opcode)   |  |  |  |  |

| 1      | 1                  | 1 | 965µs                            | 1.08ms | overload::BEGIN@147                 |  |  |  |  |

| 1      | 1                  | 1 | 786µs                            | 831µs  | Carp:: <b>BEGIN@3</b>               |  |  |  |  |

| 7      | 7                  | 2 | 666µs                            | 823µs  | vars:: <u>import</u>                |  |  |  |  |

| 1      | 1                  | 1 | 630µs                            | 634µs  | Data::Dumper::BEGIN@683             |  |  |  |  |

See all 210 subroutines

You can view a treemap of subroutine exclusive time, grouped by package. NYTProf also generates call-graph files in Graphviz format: inter-package calls, all inter-subroutine calls (probably too cor

You can hover over some table cells and headings to view extra information. Some table column headings can be clicked on to sort the table by that column.

Figure 3.6: Experiment 1D

\* Using Hashes and Regular Expression - a script to read a design file using hashes and regular expressions and then acting along user's wish. Profiling results are as follow:-

#### Performance Profile Index For ./exp1\_1d.pl

Profile of ./exp1\_1d.pl for 37.7ms (of 41.0ms) executing 6930 statements and 2307 subroutine calls in 10 source files.

| Top 15 Subroutines |    |   |                   |                   |                                             |  |  |

|--------------------|----|---|-------------------|-------------------|---------------------------------------------|--|--|

| Calls              | Ρ  | F | Exclusive<br>Time | Inclusive<br>Time | Subroutine                                  |  |  |

| 1                  | 1  | 1 | 8.02ms            | 22.0ms            | main::BEGIN@2                               |  |  |

| 1                  | 1  | 1 | 5.12ms            | 5.31ms            | vars::BEGIN@7                               |  |  |

| 1991               | 3  | 1 | 3.53ms            | 3.53ms            | main:: <u>CORE:match</u> (opcode)           |  |  |

| 1                  | 1  | 1 | 1.82ms            | 1.90ms            | Exporter:: <b><u>as_heavy</u></b>           |  |  |

| 1                  | 1  | 1 | 1.17ms            | 1.31ms            | Getopt::Long::CallBack::BEGIN@1489          |  |  |

| 1                  | 1  | 1 | 1.13ms            | 1.43ms            | Getopt::Long::BEGIN@208                     |  |  |

| 1                  | 1  | 1 | 1.02ms            | 1.11ms            | Getopt::Long::BEGIN@17                      |  |  |

| 1                  | 1  | 1 | 859µs             | 6.29ms            | Getopt::Long::BEGIN@19                      |  |  |

| 1                  | 1  | 1 | 827µs             | 857µs             | Getopt::Long::BEGIN@25                      |  |  |

| 2                  | 2  | 1 | 770µs             | 770µs             | main:: <u>CORE:readline</u> (opcode)        |  |  |

| 1                  | 1  | 1 | 571µs             | 571µs             | main:: <u>CORE:open</u> (opcode)            |  |  |

| 9                  | 2  | 1 | 416µs             | 416µs             | main:: <u>CORE:print</u> (opcode)           |  |  |

| 7                  | 7  | 2 | 311µs             | 384µs             | vars:: <u>import</u>                        |  |  |

| 13                 | 13 | 1 | 293µs             | 371µs             | constant:: <u>import</u>                    |  |  |

| 3                  | 1  | 1 | 225µs             | 252µs             | warnings:: <mark>register_categories</mark> |  |  |

See <u>all 137 subroutines</u>

You can view a treemap of subroutine exclusive time, grouped by package. NYTProf also generates call-graph files in <u>Graphviz</u> format: inter-package calls, all inter-subroutine calls.

You can hover over some table cells and headings to view extra information. Some table column headings can be clicked on to sort the table by that column.

#### Figure 3.7: Experiment 1E

- \* Exclusive Time It is best for Bottom Up Approach

- It gives the amount of time spent "in the code of the subroutine".

- It gives the location where the time actually gets spent.

- It is appropriate for localized optimization. (Figure 3.11)

- \* Inclusive Time It is suited for Top Down Approach

- It gives the amount of time spent "in and below this sub".

- It is appropriate to prioritize structural optimizations.

| S.no | Experiment                           | Before | After |

|------|--------------------------------------|--------|-------|

| 1.   | Using Three Loop                     | -      | 15.4s |

| 2.   | Using Array                          | 15.4s  | 14.5s |

| 3.   | Using Hashes                         | 14.4s  | 12s   |

| 4.   | Using Regular Expressions            | 12s    | 222ms |

| 5.   | Using Regular Expressions and Hashes | 222ms  | 41ms  |

Table 3.1: Results of Performance Analysis

#### Percentage Reduction in time is 98.55% reduction.

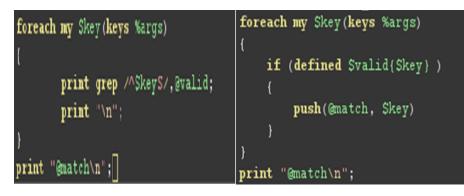

\* **Removal of recurring loop** - This Loop was taking a long time as it used to go each and every element of array. But after the optimization the array was converted into hash and going through it keys takes less time. Earlier the time was 47.3ms and now its 13ms with a reduction of 86.37% in time. The Actual reduction in AS-2 flow because of this was 9.37% but is significant. Profiling results of the above experiments are as follows:-

Figure 3.8: Reoccurring Loop

|                                             |                                                       |                                                   |                                                                                                 | ice P                                                                                           | rofile Index                                                                                                                                                                                                                                           |                                                                             |

|---------------------------------------------|-------------------------------------------------------|---------------------------------------------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| For                                         | ./ex                                                  | ф2 <sub>.</sub>                                   | _1.pl                                                                                           |                                                                                                 |                                                                                                                                                                                                                                                        |                                                                             |

| Profile                                     | e of                                                  | f ./e                                             | exp2_1.pl f                                                                                     | or 47.3ms                                                                                       | (of 47.5ms), executing 77 stateme                                                                                                                                                                                                                      | nts and 374 subroutine calls in 3 source files.                             |

|                                             |                                                       |                                                   |                                                                                                 |                                                                                                 |                                                                                                                                                                                                                                                        | Flame Graph                                                                 |

|                                             |                                                       |                                                   |                                                                                                 |                                                                                                 |                                                                                                                                                                                                                                                        |                                                                             |

|                                             |                                                       |                                                   |                                                                                                 |                                                                                                 |                                                                                                                                                                                                                                                        |                                                                             |

| main                                        | i::B                                                  | EGI                                               | N@2                                                                                             |                                                                                                 |                                                                                                                                                                                                                                                        | main::BEGIN@3                                                               |

|                                             |                                                       |                                                   |                                                                                                 |                                                                                                 |                                                                                                                                                                                                                                                        |                                                                             |

|                                             |                                                       |                                                   |                                                                                                 |                                                                                                 |                                                                                                                                                                                                                                                        |                                                                             |

|                                             |                                                       |                                                   |                                                                                                 |                                                                                                 |                                                                                                                                                                                                                                                        |                                                                             |

|                                             |                                                       |                                                   |                                                                                                 |                                                                                                 |                                                                                                                                                                                                                                                        |                                                                             |

| he F                                        | lan                                                   | ne (                                              | Graph abo                                                                                       | ve is a vis                                                                                     | sualization of the time spent in <i>distir</i>                                                                                                                                                                                                         | oct call stacks. The colors and x-axis position are not meaninoful.         |

| he <mark>F</mark>                           | lan                                                   | ne (                                              | <mark>Graph</mark> abo                                                                          | ve is a vis                                                                                     | sualization of the time spent in distin                                                                                                                                                                                                                | nct call stacks. The colors and x-axis position are not meaningful.         |

|                                             |                                                       |                                                   |                                                                                                 | ve is a vis                                                                                     | sualization of the time spent in <i>distir</i>                                                                                                                                                                                                         | ct call stacks. The colors and x-axis position are not meaningful.          |

|                                             |                                                       |                                                   |                                                                                                 | ve is a vis                                                                                     | sualization of the time spent in <i>distir</i>                                                                                                                                                                                                         | nct call stacks. The colors and x-axis position are not meaningful.         |

| Subr                                        | out                                                   | tine                                              | S                                                                                               | Inclusive                                                                                       | sualization of the time spent in <i>distir</i><br>Subroutine                                                                                                                                                                                           | nct call stacks. The colors and x-axis position are not meaningful.         |

| Subr                                        | out<br>P                                              | tine                                              | S<br>Exclusive<br>Time                                                                          |                                                                                                 | ·                                                                                                                                                                                                                                                      | nct call stacks. The colors and x-axis position are not meaningful.         |

| Subr<br>Calls                               | out<br>P                                              | tine<br>F                                         | Exclusive<br>Time<br>23.8ms                                                                     | Inclusive<br>Time                                                                               | Subroutine                                                                                                                                                                                                                                             | nct call stacks. The colors and x-axis position are not meaningful.         |

| Subr<br>Calls                               | out<br>P                                              | F<br>1                                            | Exclusive<br>Time<br>23.8ms                                                                     | Inclusive<br>Time<br>23.9ms                                                                     | Subroutine<br>main:::BEGIN02                                                                                                                                                                                                                           | nct call stacks. The colors and x-axis position are not meaningful.         |

| Subr<br>Calls<br>1<br>168                   | out<br>P<br>1                                         | F<br>1<br>1                                       | Exclusive<br>Time<br>23.8ms<br>21.5ms                                                           | Inclusive<br>Time<br>23.9ms<br>21.6ms                                                           | Subroutine<br>main::: <u>BEGIN#2</u><br>main::: <u>BEGIN#3</u>                                                                                                                                                                                         | nct call stacks. The colors and x-axis position are not meaningful.         |

| Subr<br>Calls<br>1<br>168                   | P<br>1<br>1                                           | F<br>1<br>1<br>1                                  | Exclusive<br>Time<br>23.8ms<br>21.5ms<br>279µs                                                  | Inclusive<br>Time<br>23.9ms<br>21.6ms<br>279µs                                                  | Subroutine<br>main:: <u>BEGIN@2</u><br>main:: <u>BEGIN@3</u><br>main:: <u>CORE:regcomp</u> (opcode)                                                                                                                                                    | nct call stacks. The colors and x-axis position are not meaningful.         |

| Subr<br>Calls<br>1<br>168<br>168            | Out<br>P<br>1<br>1<br>1<br>3                          | F<br>1<br>1<br>1                                  | Exclusive<br>Time<br>23.8ms<br>21.5ms<br>279µs<br>139µs                                         | Inclusive<br>Time<br>23.9ms<br>21.6ms<br>279µs<br>139µs                                         | Subroutine<br>main::BEGIN#2<br>main::BEGIN#3<br>main::CORE:regcomp (opcode)<br>main::CORE:match (opcode)                                                                                                                                               | nct call stacks. The colors and x-axis position are not meaningful.         |

| Subr<br>Calls<br>1<br>168<br>168<br>29      | Out<br>P<br>1<br>1<br>1<br>3<br>1                     | F<br>1<br>1<br>1<br>1                             | Exclusive<br>Time<br>23.8ms<br>21.5ms<br>279µs<br>139µs<br>91µs                                 | Inclusive<br>Time<br>23.9ms<br>21.6ms<br>279µs<br>139µs<br>91µs                                 | Subroutine           main::BECIN#2           main::CORE:regcomp (opcode)           main::CORE:match (opcode)           main::CORE:print (opcode)                                                                                                       | nct call stacks. The colors and x-axis position are not meaningful.         |

| Subr<br>Calls<br>1<br>168<br>168<br>29<br>1 | out<br>P<br>1<br>1<br>1<br>1<br>3<br>1<br>1           | F<br>1<br>1<br>1<br>1<br>1                        | Exclusive<br>Time<br>23.8ms<br>21.5ms<br>279µs<br>139µs<br>91µs<br>50µs                         | Inclusive<br>Time<br>23.9ms<br>21.6ms<br>279µs<br>139µs<br>91µs<br>50µs                         | Subroutine<br>main::BEGIN#2<br>main::BEGIN#3<br>main::CORE:regcomp (opcode)<br>main::CORE:print (opcode)<br>main::CORE:print (opcode)<br>strict::CORE:regcomp (opcode)                                                                                 | nct call stacks. The colors and x-axis position are not meaningful.         |

| Subr<br>Calls<br>1<br>168<br>168<br>29<br>1 | Out<br>P<br>1<br>1<br>1<br>1<br>1<br>3<br>1<br>1<br>1 | F<br>1<br>1<br>1<br>1<br>1<br>1<br>1              | Exclusive<br>Time<br>23.8ms<br>21.5ms<br>279µs<br>139µs<br>91µs<br>50µs<br>38µs                 | Inclusive<br>Time<br>23.9ms<br>21.6ms<br>279µs<br>139µs<br>91µs<br>50µs<br>38µs                 | Subroutine<br>main::BEGIN&2<br>main::BEGIN&3<br>main::CORE:reqcomp (opcode)<br>main::CORE:print (opcode)<br>strict::CORE:reqcomp (opcode)<br>warnings::CORE:reqcomp (opcode)                                                                           | <i>nct call stacks</i> . The colors and x-axis position are not meaningful. |

| Subr<br>Calls<br>1<br>168<br>168<br>29<br>1 | Out<br>P<br>1<br>1<br>1<br>1<br>1<br>3<br>1<br>1<br>1 | tine<br>F<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | Exclusive<br>Time<br>23.8ms<br>21.5ms<br>279µs<br>139µs<br>91µs<br>50µs<br>38µs<br>30µs         | Inclusive<br>Time<br>23.9ms<br>21.6ms<br>279μs<br>139μs<br>91μs<br>50μs<br>38μs<br>30μs         | Subroutine<br>main:: <u>BEGIN#2</u><br>main:: <u>BEGIN#3</u><br>main:: <u>CORE:regcomp</u> (opcode)<br>main:: <u>CORE:regcomp</u> (opcode)<br>strict:: <u>CORE:regcomp</u> (opcode)<br>warnings:: <u>CORE:regcomp</u> (opcode)<br>strict:: <u>bits</u> | <i>nct call stacks</i> . The colors and x-axis position are not meaningful. |

| Subr<br>Calls<br>1<br>168<br>168<br>29<br>1 | Out<br>P<br>1<br>1<br>1<br>1<br>1<br>3<br>1<br>1<br>1 | tine<br>F<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | Exclusive<br>Time<br>23.8ms<br>21.5ms<br>279µs<br>139µs<br>91µs<br>50µs<br>38µs<br>30µs<br>11µs | Inclusive<br>Time<br>23.9ms<br>21.6ms<br>279μs<br>139μs<br>91μs<br>50μs<br>38μs<br>30μs<br>41μs | Subroutine<br>main::BEGIN@2<br>main::BEGIN@3<br>main::CORE:regcomp (opcode)<br>main::CORE:regcomp (opcode)<br>main::CORE:regcomp (opcode)<br>strict::CORE:regcomp (opcode)<br>strict::bits<br>strict::bits                                             | <i>nct call stacks</i> . The colors and x-axis position are not meaningful. |

Figure 3.9: Experiment 2A

| For .                                                                                                                              |      |       | rman<br>_2.pl                                                                                     | ice P                                                                                       | rofile Index                                                                                                                                                                                                     |                                                               |

|------------------------------------------------------------------------------------------------------------------------------------|------|-------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| Profile                                                                                                                            | e of | f ./e | xp2_2.pl f                                                                                        | or 13.0m                                                                                    | s (of 13.1ms), executing 63 stateme                                                                                                                                                                              | ents and 10 subroutine calls in 3 source files.               |

|                                                                                                                                    |      |       |                                                                                                   |                                                                                             |                                                                                                                                                                                                                  | Flame Graph                                                   |