# Delayed Locked Loops For High Speed Serial Interface

# Major Project Report

Submitted in partial fulfillment of the requirements for the degree of

Master of Technology in Electronics & Communication Engineering (VLSI Design)

By

Ramani Ashish V. (14MECV25)

Electronics & Communication Engineering Branch Electrical Engineering Department Institute of Technology Nirma University Ahmedabad-382 481 May 2016

# Delayed Locked Loops For High Speed Serial Interface

## Major Project Report

Submitted in partial fulfillment of the requirements for the degree of

Master of Technology in Electronics & Communication Engineering (VLSI Design)

By

# Ramani Ashish V. (14MECV25)

Under the guidance of

#### **External Project Guide:**

Internal Project Guide:

#### Mr. Venkatesh Rao Circuit Design Manager, Intel India Technology Pvt. Ltd., Bangalore.

**Dr. Amisha Naik** VLSI Design, Institute of Technology, Nirma University, Ahmedabad.

Electronics & Communication Engineering Branch Electrical Engineering Department Institute of Technology Nirma University Ahmedabad-382 481 Dec 2015

ii

14MECV25

Certificate

This is to certify that the Major Project entitled "Delay locked loop for high speed serial interface" submitted by Ramani Ashish V. (14MECV25), towards the partial fulfillment of the requirements for the degree of Master of Technology in VLSI Design, Nirma University, Ahmedabad is the record of work carried out by him under our supervision and guidance. In our opinion, the submitted work has reached a level required for being accepted for examination. The results embodied in this major project, to the best of our knowledge, haven't been submitted to any other university or institution for award of any degree or diploma.

Date:

**Internal Guide**

Dr. N. M. Devashrayee (Professor, EC)

**Program Co-ordinator**

Director

Prof. P. N. Tekwani (Head of EE Dept.) (Director, IT-NU)

Dr. Amisha Naik

(VLSI Design)

Place: Ahmedabad

# Intel Technology India Pvt. Ltd.

## Certificate

This is to certify that the Major Project entitled "Delay locked loop for highspeed serial interface" submitted by Ramani Ashish V. (14MECV25), towards the partial fulfillment of the requirements for the degree of Master of Technology in VLSI Design, Nirma University, Ahmedabad is the record of work carried out by him under my supervision and guidance. In my opinion, the submitted work has reached a level required for being accepted for examination. The results embodied in this major project, to the best of my knowledge, haven't been submitted to any other university or institution for award of any degree or diploma.

Date:

Place: Bangalore

Mr. Giridhar Bajpe IPG-MIG India Intel Technology India Pvt. Ltd., Bangalore.

# Declaration

This is to certify that

- 1. The thesis comprises my original work towards the degree of Master of Technology in VLSI Design at Nirma University and has not been submitted elsewhere for a degree.

- 2. Due acknowledgment has been made in the text to all other material used.

- Ramani Ashish V. 14MECV25

# Acknowledgements

First and foremost, sincere gratitude to my managers Mr. Venkatesh Rao and Mr. Shivraj Thakare. Also I want to thank Intel Technology India Private Limited, Bangalore for assigning me such project and guide me through.

I would like to express my gratitude and sincere thanks to my mentor Mrs. Bheemisetti Chakravarti at Intel Technology India Private Limited, Bangalore for his valuable guidance throughout this period. he has given me valuable advices and support for my project work which I am very lucky to benefit from.

I would like to express my gratitude and sincere thanks to our Director Dr. P. N. Tekwani, Head of Electrical Engineering Department for allowing me to undertake this thesis work and for his guidelines during the review process.

I would like to thank my Program Coordinator, Dr. N. M. Devashrayee, Professor, EC (VLSI Design), Institute of Technology, Nirma University, Ahmedabad for giving valuable support and motivation throughout the academic period.

I would also thank to my Project Guide, Dr. Amisha Naik, Professor, VLSI Design, Institute of Technology, Nirma University, Ahmedabad for being a source of inspiration, giving valuable support and timely guidance for the project work.

I take immense pleasure to thank my team member Mr. Mallikarjuna Rao, Bheemisetti Chakravarti and other colleagues in the Intel, special thanks for helping me on this path and for making project at Intel more enjoyable.

I wish to thank my classmates for their delightful company which kept me in good humor throughout the journey.

Last, but not the least, no words are enough to acknowledge constant support and sacrifices of my family members because of whom I am able to complete the degree program successfully.

> - Ramani Ashish V. 14MECV25

## Abstract

The performance of high-speed wire-line data links depend crucially on the quality and precision of their clocking infrastructure. with aggressive scaling of device susceptibility of signal to process, voltage, and temperature variation increase tremendously. because of high speed and low power design timing and voltage margin reduce respectively. For future applications, such as microprocessor systems that require terabytes/s of aggregate bandwidth, signaling system designers will have to become even more aware of detailed clock design trade offs in order to jointly optimize I/O power, bandwidth, reliability, silicon area and testability. Digital communications technology as well as integrated circuit scaling trends has enabled the industry to dramatically scale the bandwidth of high-loss networks such as DSL and Ethernet. Many of these networks are channel bandwidth limited and have had to leverage sophisticated equalization techniques to push well beyond the uncompensated channel bandwidth. Proper clocking architecture dramatically reduce burden on sophisticated equalization technique for generating a high bandwidth on and off chip link .so trade off between power, performance and area (complexity) can solve by proper handling of clock through distribution. Delay locked looped provide easy means of phase synchronization of sampling clock and data. Due to optimum sampling point in time-domain decision threshold get extra tolerance against noise, inter symbol interferences, jitter, and skew. All digital delay locked is presented here with wide frequency range, small locking time, less jitter and stable phase of delayed clock. two types of delay line coarse delay unit and fine delay unit together provide a wide delay regulation range and finer delay resolution. bang-bang phase detector with delay less than clock period enable us to update delay value at each clock cycle hence time to lock improved.

# Contents

| С             | ertifi | cate (N | Nirma)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ii  |

|---------------|--------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| D             | eclar  | ation   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | iv  |

| A             | cknov  | wledge  | ments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | v   |

| A             | bstra  | ict     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | vi  |

| $\mathbf{Li}$ | ist of | Figure  | es                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | xi  |

| A             | bbre   | viation | s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | xii |

| 1             | Intr   | oducti  | on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1   |

|               | 1.1    | Challe  | enges for high speed clock and data recovery circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1   |

|               | 1.2    | Jitter  | • • • • • • • • • • • • • • • • • • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4   |

|               |        | 1.2.1   | Jitter peaking by channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5   |

|               |        | 1.2.2   | Jitter analysis in analog delay locked loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7   |

|               |        | 1.2.3   | Jitter analysis in digital delay locked loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 8   |

|               | 1.3    | Appli   | cation of delay locked loop $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 11  |

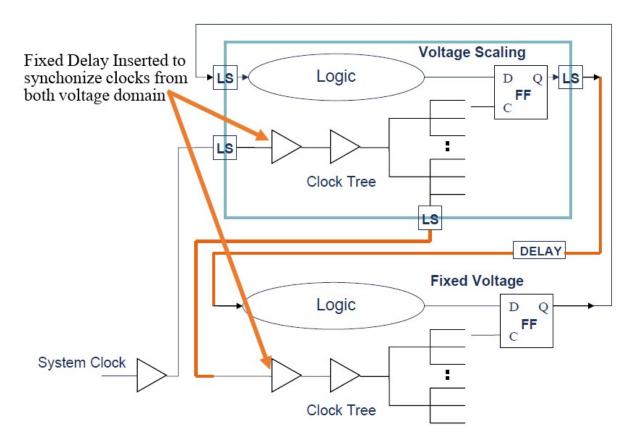

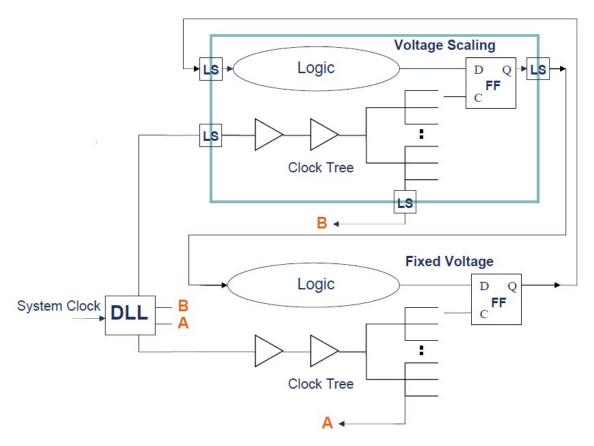

|               |        | 1.3.1   | clock tree synthesis in multi-voltage domain $\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\$ | 11  |

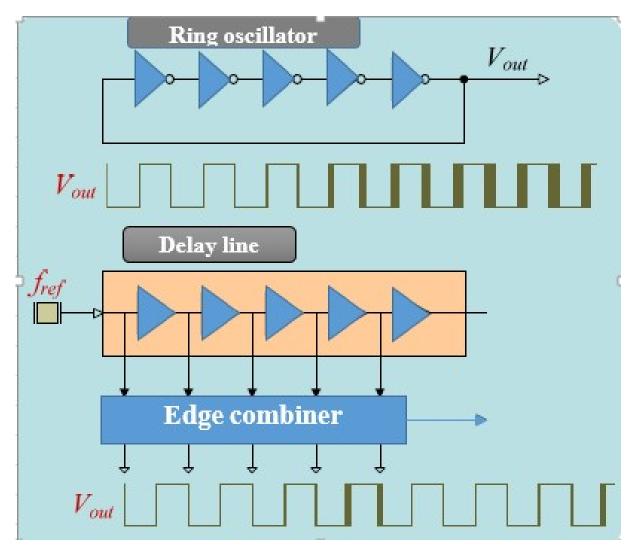

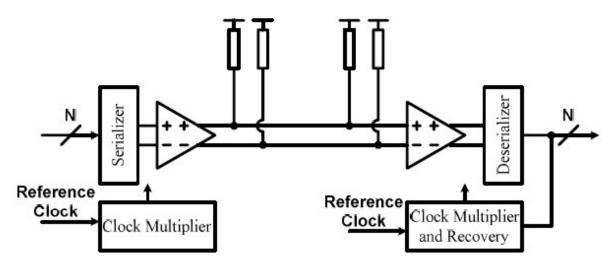

|               |        | 1.3.2   | Frequency multiplication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 13  |

|               |        | 1.3.3   | DDR-DRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 14  |

|               |        | 1.3.4   | Delay compensation and multiphase clock generation $\ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 16  |

| <b>2</b>      | Lite   | erature | Review                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 17  |

|               | 2.1    | Types   | of DLL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 17  |

|               |        | 2.1.1   | digital delay locked loop-performance parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 17  |

|               |        | 2.1.2   | analog delay locked loop-performance parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 19  |

|               |        | 2.1.3   | performance summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 22  |

|               | 2.2    | Analog  | g delay locked loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 23  |

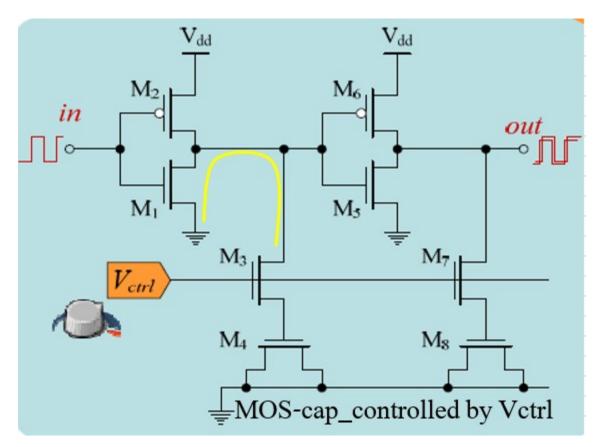

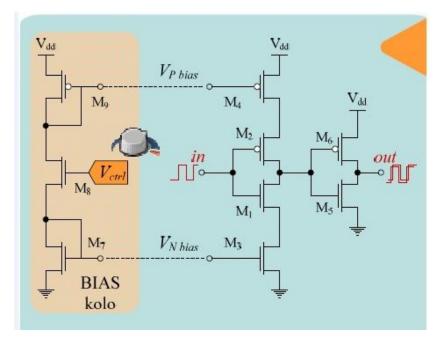

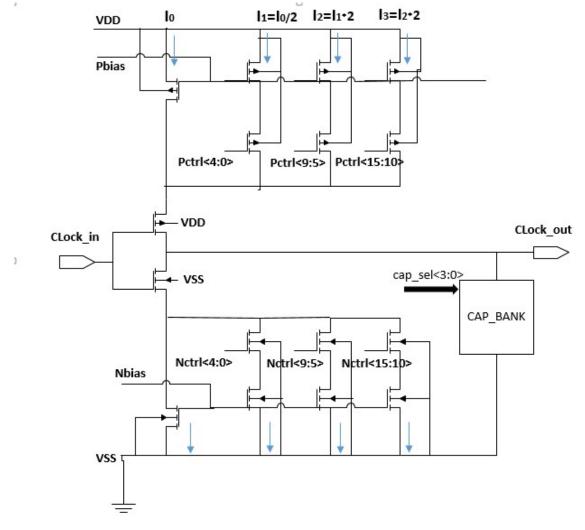

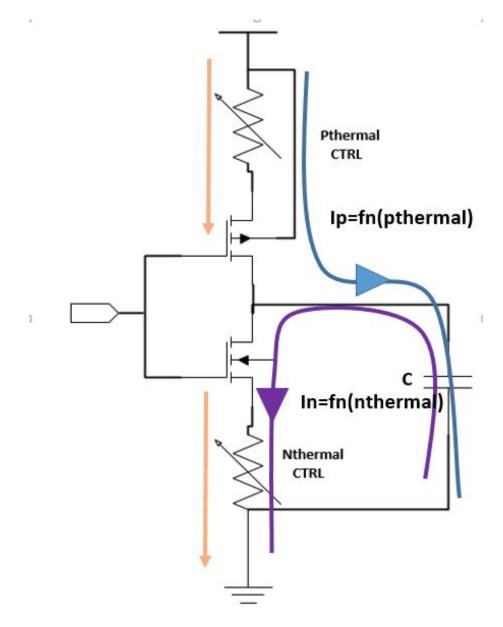

|               |        | 2.2.1   | Voltage control delay line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 23  |

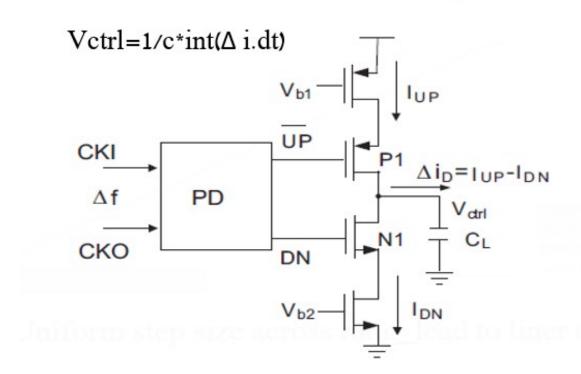

|               |        | 2.2.2   | charge pump                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 26  |

| 3        | All                  | digital | l delay locked loop                                                                           | 27   |

|----------|----------------------|---------|-----------------------------------------------------------------------------------------------|------|

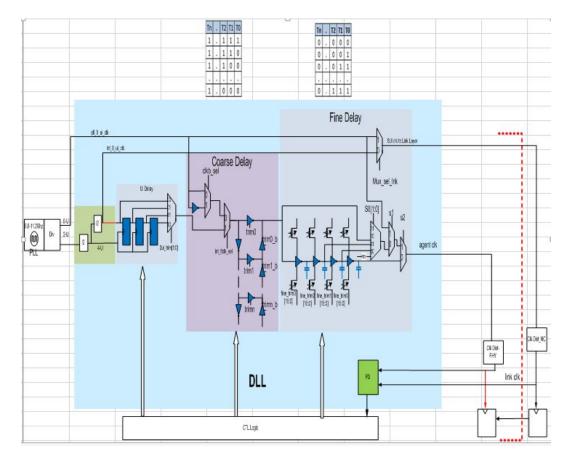

|          | 3.1                  | Archit  | cecture of all digital delay locked loop                                                      | . 27 |

|          |                      | 3.1.1   | frequency divider                                                                             | . 28 |

|          |                      | 3.1.2   | Coarse delay line                                                                             | . 30 |

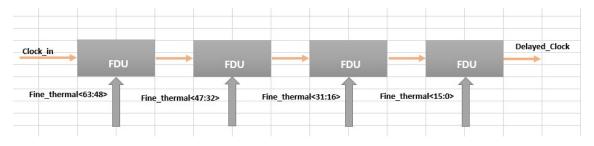

|          |                      | 3.1.3   | Fine delay line                                                                               | . 33 |

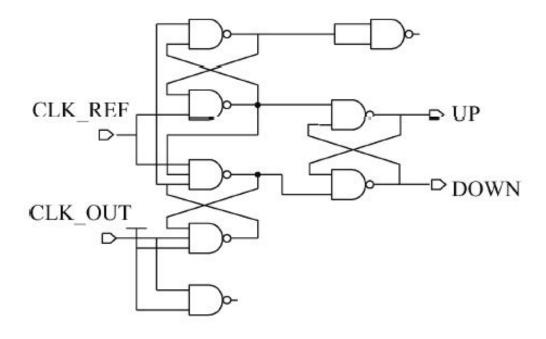

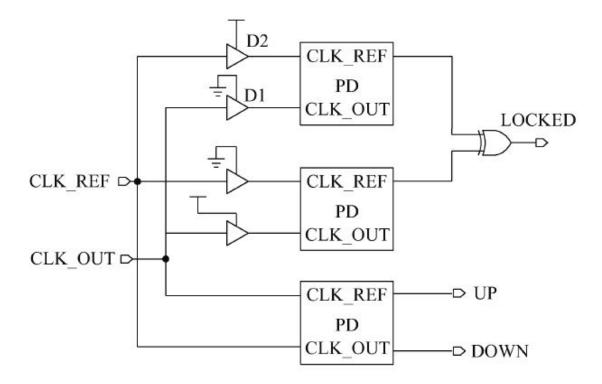

|          |                      | 3.1.4   | Phase Detector                                                                                | . 37 |

|          |                      | 3.1.5   | Digital control logic (FSM)                                                                   | . 42 |

| 4        | $\operatorname{Res}$ | ults ar | nd Observations                                                                               | 44   |

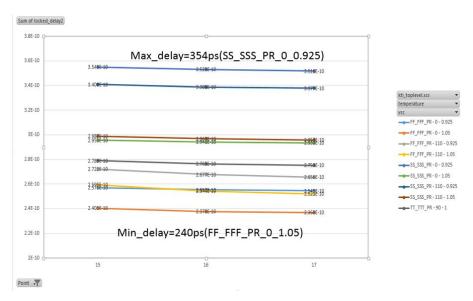

|          | 4.1                  | Delay   | line                                                                                          | . 44 |

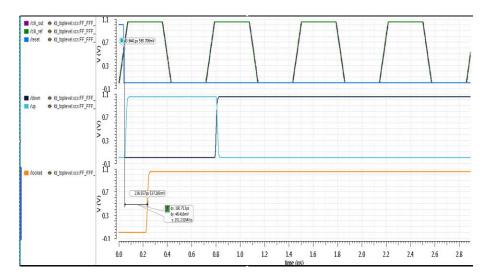

|          |                      | 4.1.1   | Coarse delay line                                                                             | . 45 |

|          |                      | 4.1.2   | Fine delay line                                                                               | . 47 |

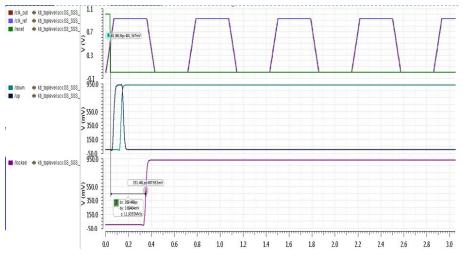

|          | 4.2                  | Jitter  | · · · · · · · · · · · · · · · · · · ·                                                         | . 49 |

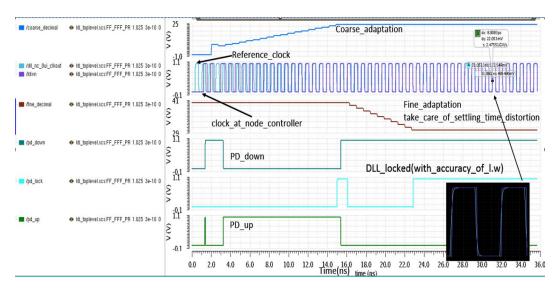

|          | 4.3                  |         | ng time                                                                                       |      |

|          | 4.4                  |         | $e$ detector $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ |      |

|          | 4.5                  | Close   | d loop calibration                                                                            | . 55 |

| <b>5</b> | Cor                  | clusio  | n                                                                                             | 58   |

| Re       | efere                | nces    |                                                                                               | 59   |

# List of Figures

| 1.1  | Timing budget of CDR                                                                  | 3  |

|------|---------------------------------------------------------------------------------------|----|

| 1.2  | a) The role of a CDR circuit in re-timing data; b) an example of CDR im-              |    |

|      | plementation                                                                          | 3  |

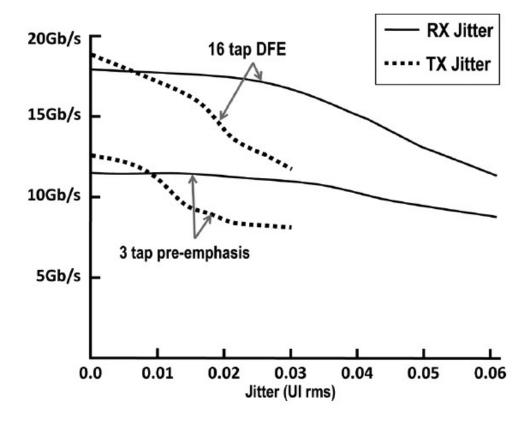

| 1.3  | Maximum data rate as a function of TX jitter magnitude for a data link                |    |

|      | with varying amounts of equalization complexity. Baseline parameters for              |    |

|      | link simulation include: Channel loss 15 dB@5 GHz, BER= 1e-12. 16 tap                 |    |

|      | DFE link includes 3 tap TX pre-emphasis. Rx input-referred noise $1 \text{ mV rms}$ . |    |

|      | TX jitter $1/2$ ps rms, RX jitter 1ps rms unless otherwise specified. Jitter is       |    |

|      | normally distributed                                                                  | 4  |

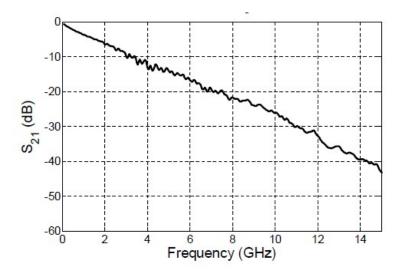

| 1.4  | Channel Response[3]                                                                   | 5  |

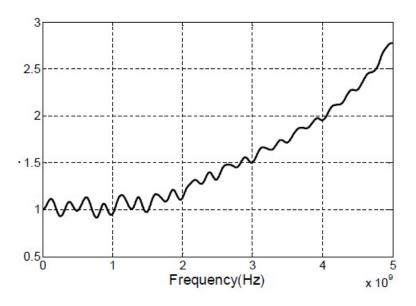

| 1.5  | Jitter Transfer/Amplification[3]                                                      | 6  |

| 1.6  | Jitter representation                                                                 | 6  |

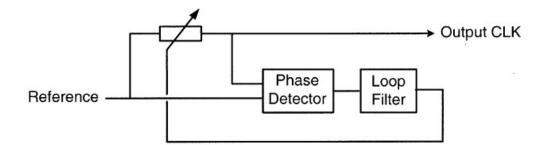

| 1.7  | simplified type-1 analog DLL                                                          | 7  |

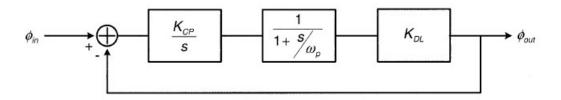

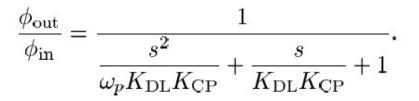

| 1.8  | S-domain model for Analog DLL                                                         | 7  |

| 1.9  | jitter transfer function for Analog DLL                                               | 7  |

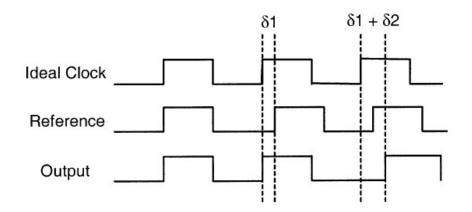

| 1.10 | Timing diagram illustration of jitter peaking                                         | 8  |

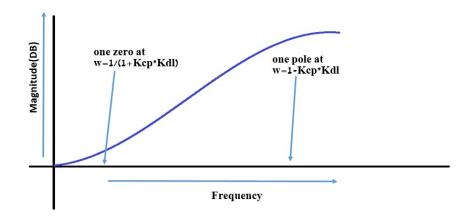

| 1.11 | Bode plot for jitter transfer characteristics of first order analog DLL               | 8  |

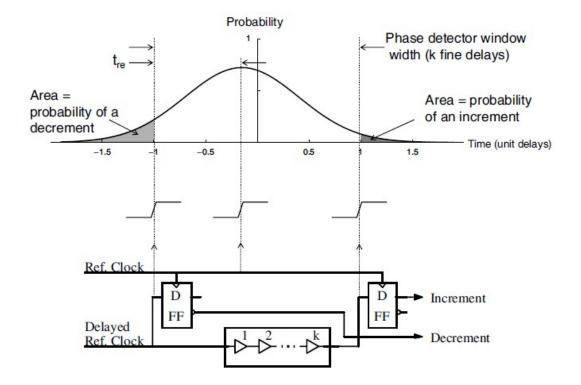

| 1.12 | phase detector and probability distribution function of reference clock               | 9  |

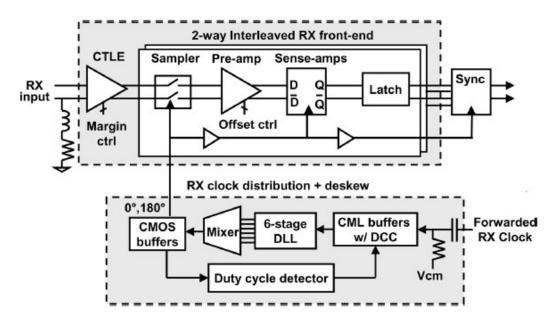

| 1.13 | DLL based forwarded clock architecture                                                | 9  |

| 1.14 | Jitter in PLL and DLL                                                                 | 10 |

| 1.15 | pseudo synchronization at voltage scaling domain boundary $\ldots \ldots \ldots$      | 11 |

| 1.16 | DLL synchronization at voltage scaling domain boundary                                | 12 |

| 1.17 | Basic block diagram of high speed serial I/O                                          | 13 |

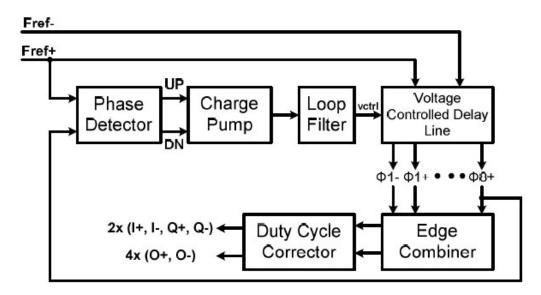

| 1.18 | basic DLL based clock multiplier                                                      | 13 |

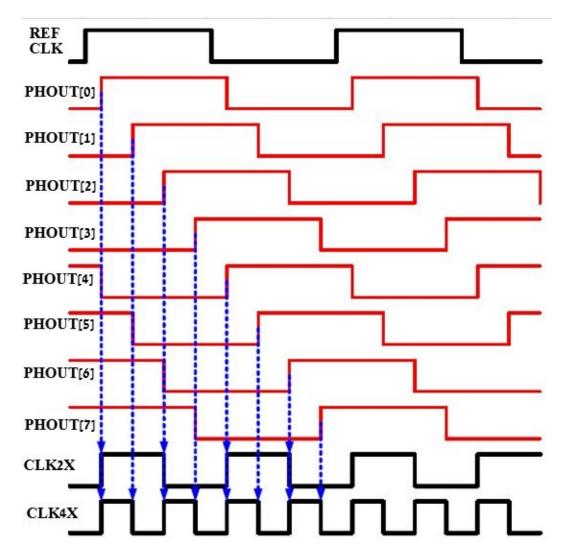

| 1.19 | frequency multiplication by processing the output phases of DLL                       | 14 |

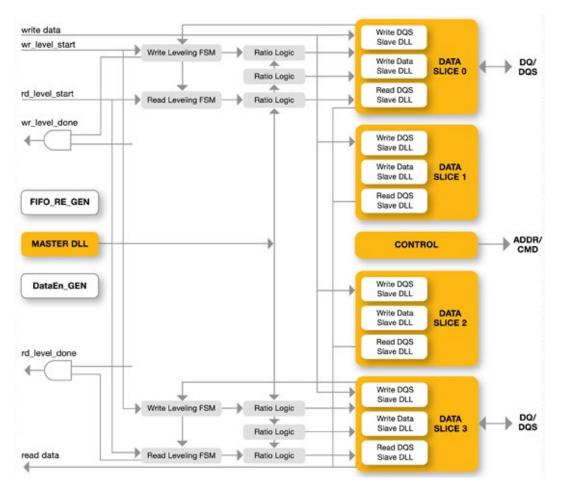

| 1.20 | All digital high performance DDR PHY/DLL implementation                               | 15 |

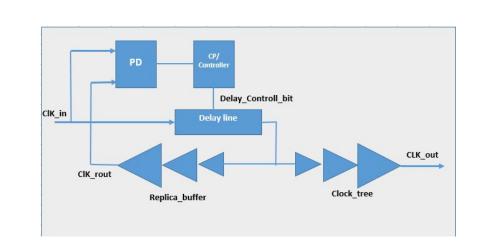

| 1.21 | delay compensation by DLL                                                             | 16 |

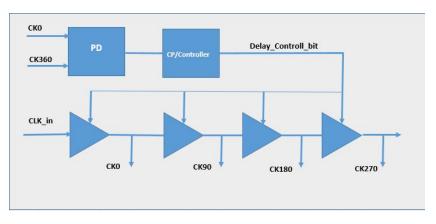

| 1.22 | Multi phase clock generation                                                          | 16 |

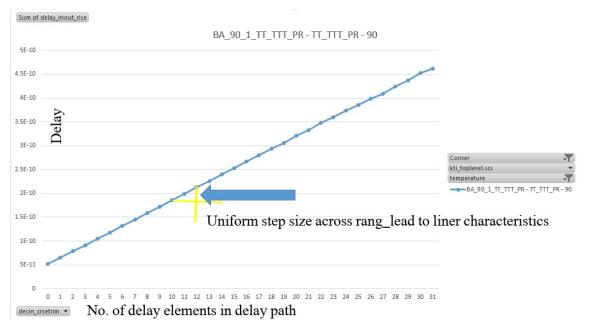

| 2.1  | Linear delay characteristics                                                          | 18 |

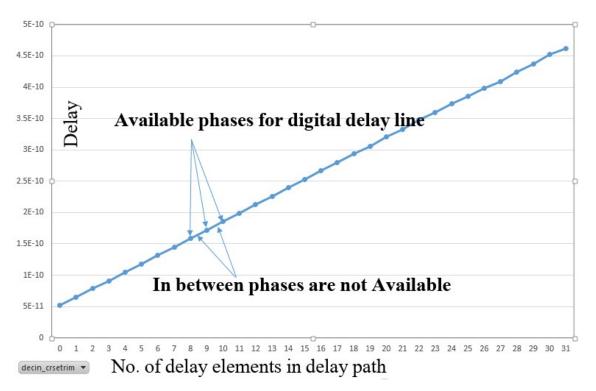

| 2.2  | delay resolution for digital delay line                                               | 19 |

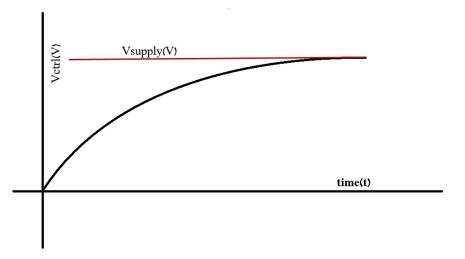

| 2.3  | Vctrl generation in analog delay locked loop                                             | 20 |

|------|------------------------------------------------------------------------------------------|----|

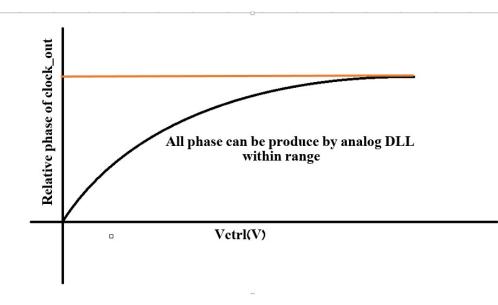

| 2.4  | nonlinear characteristics of Vctrl VS relative phase difference between two              | 20 |

| 25   | clocks                                                                                   | 20 |

| 2.5  | power dissipation in voltage control delay in analog delay locked loop                   | 21 |

| 2.6  | Delay resolution for analog delay locked loop                                            | 22 |

| 2.7  | SUMMARY OF PERFORMANCE PARAMETER FOR DIFFERENT DLL                                       | 22 |

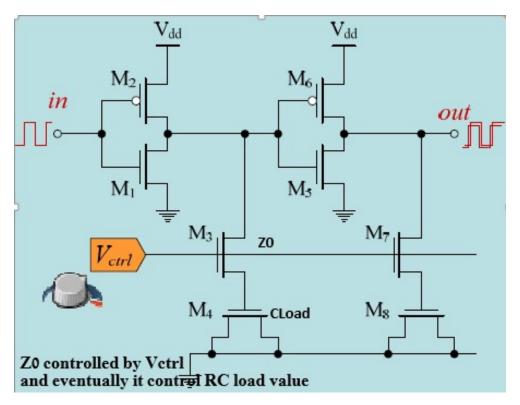

| 2.8  | current starve delay elements                                                            | 23 |

| 2.9  | capacitive load delay elements                                                           | 24 |

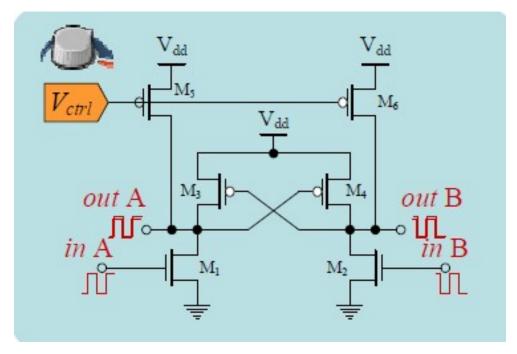

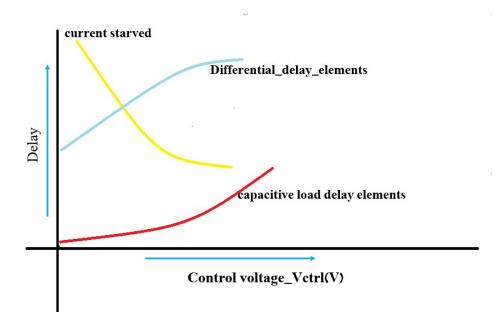

| 2.10 | delay elements with differential Input/output                                            | 25 |

| 2.11 | relative delay transfer characteristics                                                  | 25 |

| 3.1  | Block diagram of proposed digital delay locked loop                                      | 28 |

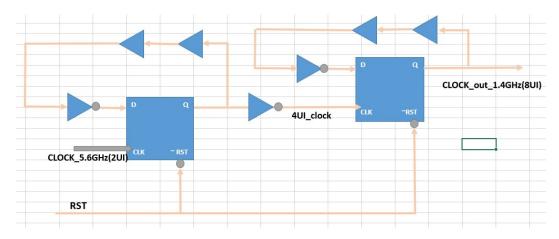

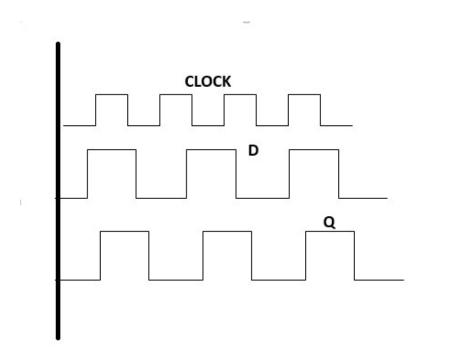

| 3.2  | basic block diagram of frequency divider                                                 | 29 |

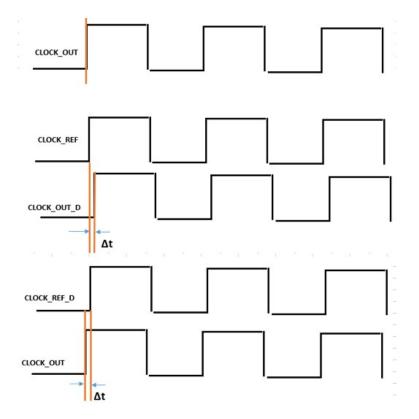

| 3.3  | delay adjustment in frequency divider                                                    | 29 |

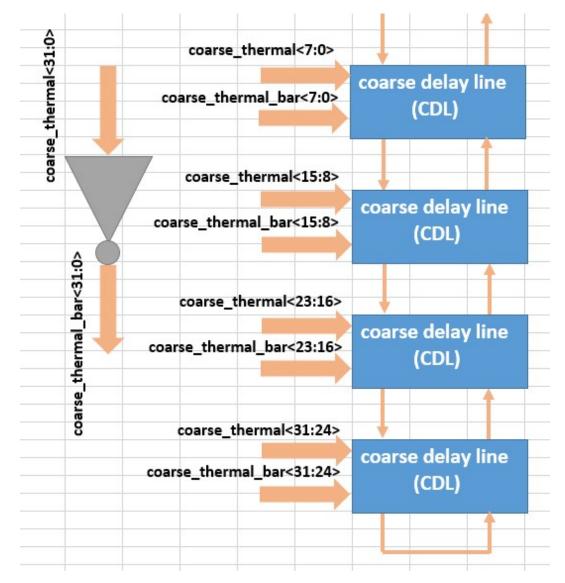

| 3.4  | top level block diagram of coarse delay line                                             | 31 |

| 3.5  | coarse delay line                                                                        | 32 |

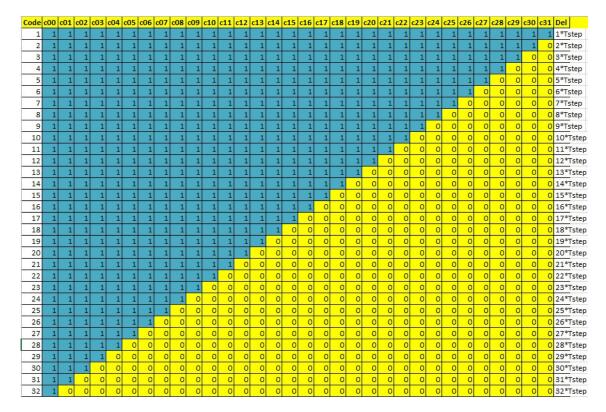

| 3.6  | mapping of thermal code in coarse delay line                                             | 33 |

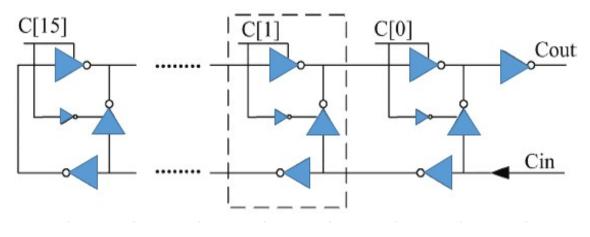

| 3.7  | - basic block diagram of fine delay line                                                 | 34 |

| 3.8  | Binary weighted delay relation                                                           | 34 |

| 3.9  | Top level block diagram of fine delay line                                               | 35 |

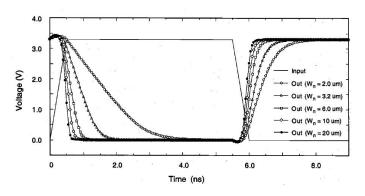

| 3.10 | Propagation delay model of cmos inverter                                                 | 36 |

| 3.11 | W/L vs Propagation delay[10]                                                             | 36 |

| 3.12 | inverter delay model                                                                     | 37 |

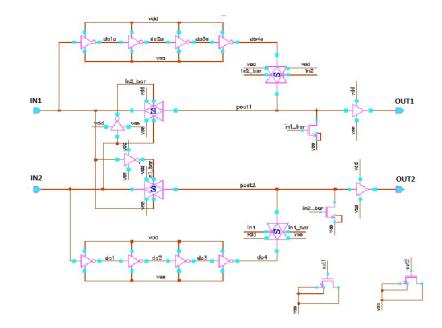

| 3.13 | block diagram of two state bang-bang phase detector $\ldots \ldots \ldots \ldots \ldots$ | 38 |

| 3.14 | block diagram of three state bang-bang phase detector                                    | 39 |

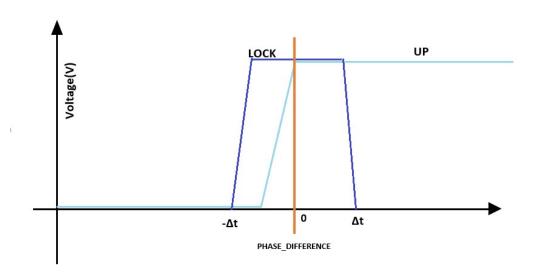

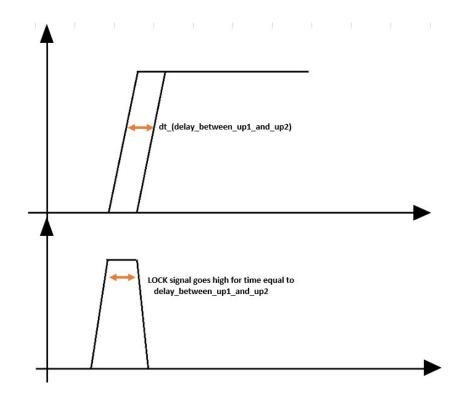

| 3.15 | locked window of phase detector                                                          | 40 |

| 3.16 | pre lock signal of phase detector                                                        | 40 |

| 3.17 | Glitch on LOCK signal                                                                    | 41 |

| 3.18 | Rising edge synchronizer to avoid glitches on LOCK signal                                | 41 |

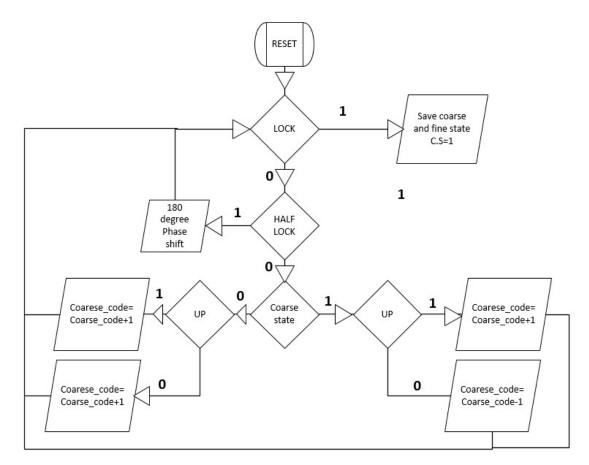

| 3.19 | Digital control flow chart of DLL                                                        | 43 |

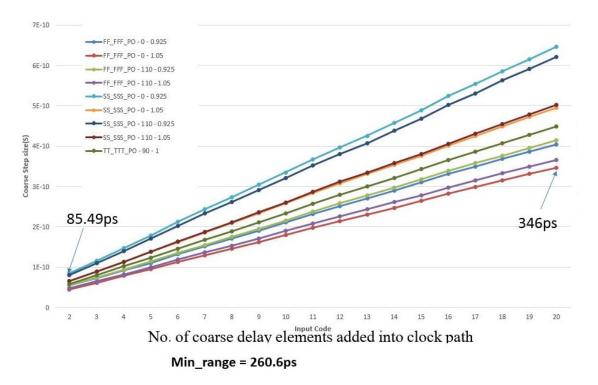

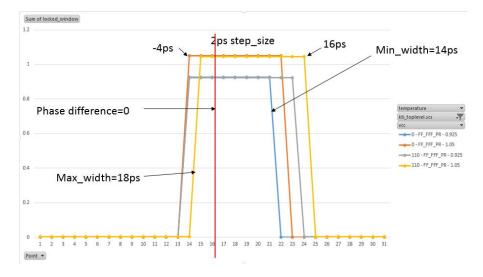

| 4.1  | Coarse delay line range across PVT                                                       | 45 |

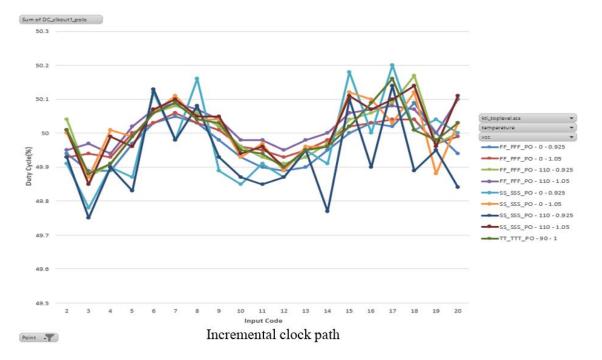

| 4.2  | Coarse delay step size                                                                   | 45 |

| 4.3  | Coarse delay line output duty cycle                                                      | 46 |

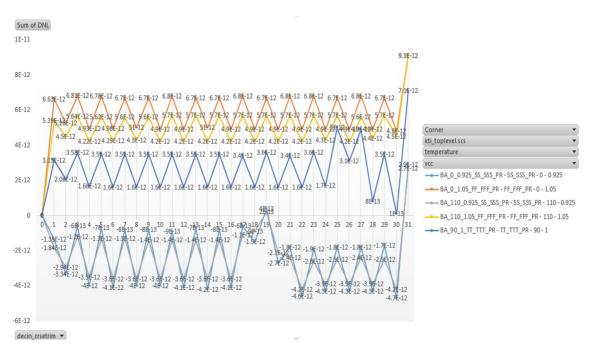

| 4.4  | Differential non-linearity of coarse delay line                                          | 46 |

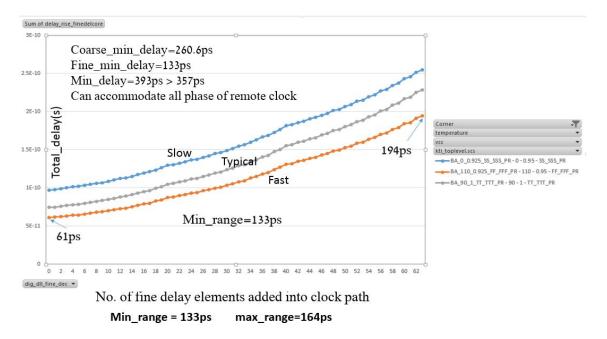

| 4.5  | Fine delay line range across PVT                                                         | 47 |

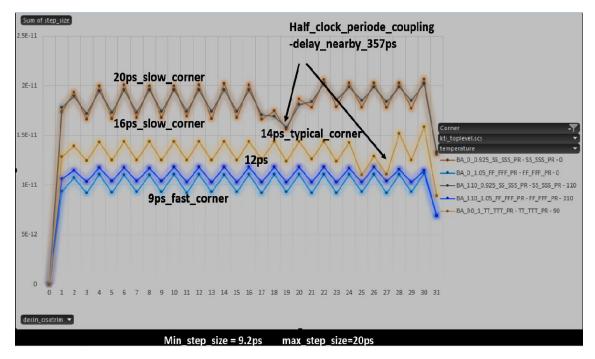

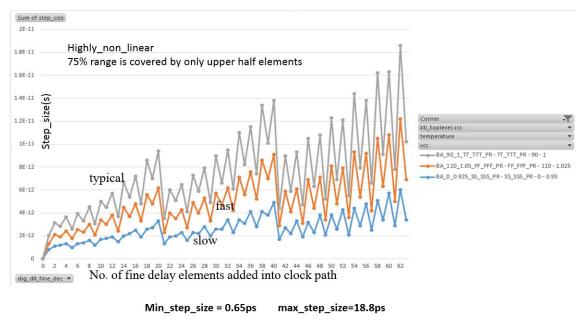

| 4.6  | Fine delay line step size across PVT                                                     | 47 |

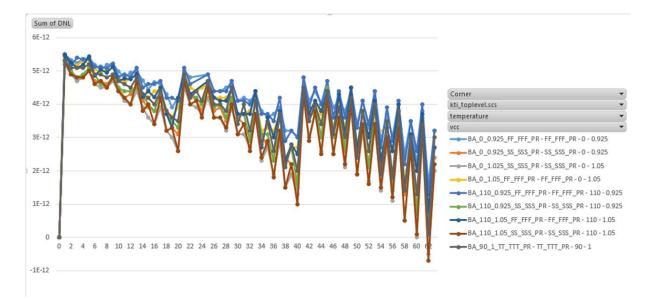

| 4.7  | Differential non-linearity of fine delay line                                            | 48 |

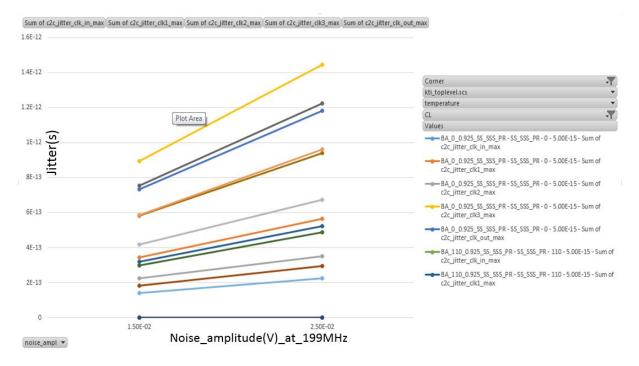

| 4.8  | Jitter contribution by individual fine delay elements                                    | 48 |

| 4.9  | Jitter number for different architecture                                                 | 49 |

|      |                                                                                          | -  |

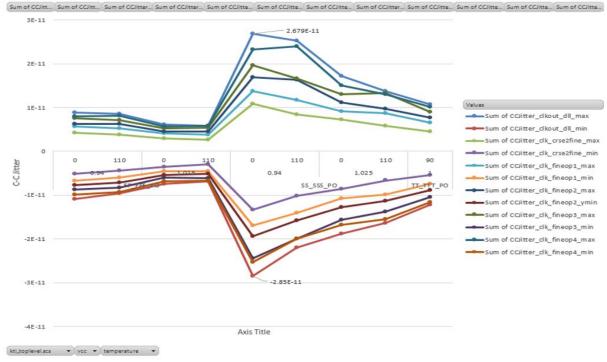

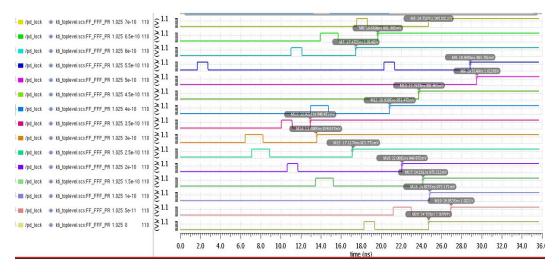

| 4.10 | DLL TOP stage wise C-C Jitter across PVT                                                                          | 49 |

|------|-------------------------------------------------------------------------------------------------------------------|----|

| 4.11 | Settling time summary                                                                                             | 50 |

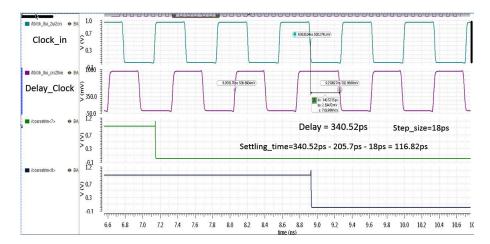

| 4.12 | Delay decin creative transition 7to8                                                                              | 51 |

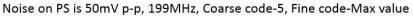

| 4.13 | Settling time fine delay line                                                                                     | 51 |

| 4.14 | LOCK window across fast corner                                                                                    | 52 |

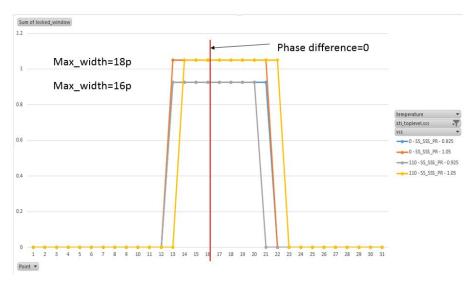

| 4.15 | LOCK window across slow corner                                                                                    | 52 |

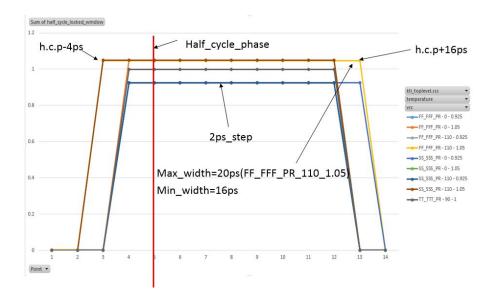

| 4.16 | Half cycle locked window across pvt                                                                               | 53 |

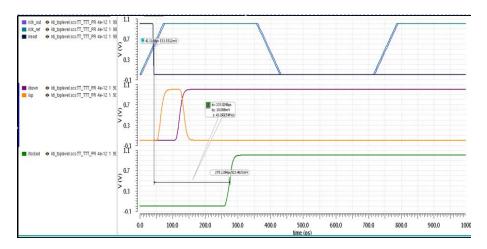

| 4.17 | Clock to locked delay typical                                                                                     | 53 |

| 4.18 | Clock to locked delay fast                                                                                        | 54 |

| 4.19 | Clock to locked delay slow                                                                                        | 54 |

| 4.20 | Clock to locked delay                                                                                             | 55 |

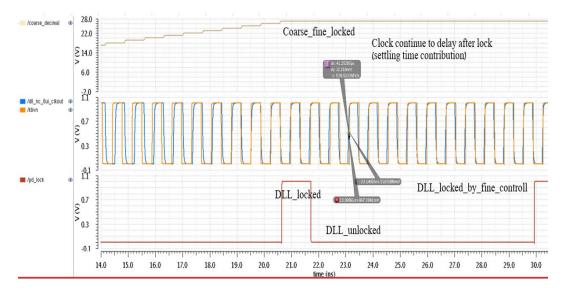

| 4.21 | Closed loop calibration $\ldots$ | 55 |

| 4.22 | Lock time for different phase skew                                                                                | 56 |

| 4.23 | Settling time compensation by fine tuning                                                                         | 56 |

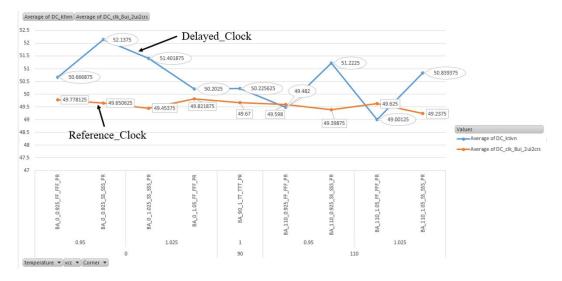

| 4.24 | Duty cycle variation across PVT                                                                                   | 57 |

# Abbreviations

| DLL           | Delayed locked loop                           |

|---------------|-----------------------------------------------|

| ADDLL         | All digital delayed locked loop               |

| CDU           | Coarse delay unit                             |

| FDU           | Fine delay unit                               |

| PD            | phase detector                                |

| PVT           | Process voltage temperature                   |

| DC            | Duty cycle                                    |

| DRAM          | Dynamic random access memory                  |

| DDR-DRAM      | Double data rate dynamic random access memory |

| UI            | Unit interval                                 |

| СР            | charge pump                                   |

| CSTRV         | Current starved                               |

| CDN           | Clock                                         |

| DQS           | Data strobe                                   |

| FSM           | Finite state machine                          |

| VCDL          | Voltage controlled delay line                 |

| DCC           | Duty cycle correction circuit                 |

| $\mathbf{LS}$ | Level shifter                                 |

| MVD           | Multi voltage domain                          |

| CTLE          | Continuous time linear equalization           |

| CML           | Current mode logic                            |

| MGT           | Multi-Gigabit Transceiver                     |

| CRC           | Clock recovery circuit                        |

| CTS           | Clock Tree Synthesis                          |

# Chapter 1

# Introduction

Demand for multi Gb/s serial I/O has placed a great challenge to clock and data recovery architecture and circuit design. Due to great improvement in semiconductor technology along with device scaling has created high speed interface capability in microprocessor and memory. All high speed and performance benefits are enjoyable in high bandwidth communication link but scenario in low bandwidth communication is slight different. Various additional factor came into picture when we switch from on chip to off chip communication. Some of them are link bandwidth, jitter, noise and skew. This factor are limiting factor for off chip serial link's power, performance and complexity. Its demand extra functionality and novel design for clock and data recovery circuit to mitigate an additional challenges specifically imposed by off chip communication application. Various additional effort made in section of channel equalization, channel coding, proper link termination has improved off chip communication capacity very far from link bandwidth. But by doing so the tradeoffs triangle has not optimize. Calculated approach toward high speed I/O should include each and every possible optimization to improve a tradeoff triangle which is power, performance (speed) and area (complexity). So novel clock distribution is critical for further capacity improvements. Improved clocking methods have played a central role in the widespread adoption of multi-gigabit data links.

# 1.1 Challenges for high speed clock and data recovery circuit

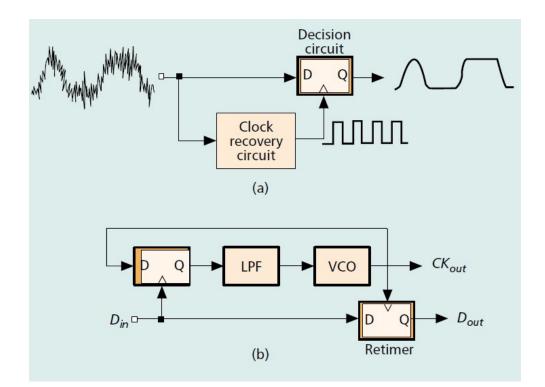

In high speed transceiver system clock and data recovery (CDR) is a critical function. Optical communication, backplane routing, and chip-to-chip interconnects are the main application area of CDR. Due to high speed operation allowed by asynchronous communication, clock must be recovered from noisy data to allow a synchronous operation to reduce a bit error rate in communication. Data retiming is necessary to remove jitter which is accumulated during transmission to allow a high timing margin. Clock get extracted from noisy data by clock recovery circuit and data retiming operation is performed by data recovery circuit.

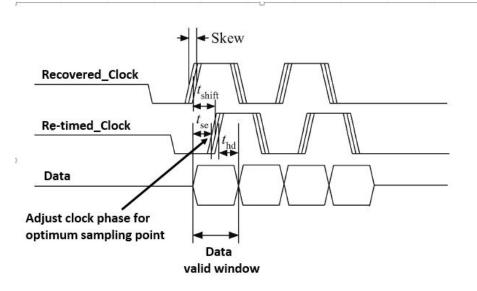

Communication standard impose a stringent specification on CDR which it must satisfy. To design a CDR within communication standard boundary create a difficult challenges to circuit designer and system designer. Figure show clock recovery circuit, clock is require to perform a synchronous operation such as data retiming and de-multiplexing of random data, receiver must generate a clock. Clock recovery circuit generate a periodic clock from noisy data. This recovered periodic clock then drive a D-flip-flops to retime a data. D-flip-flop here act as a sampler so we can called it a decision circuit.

Clock generated by this circuit must satisfy below three condition for proper operation of CDR.

- 1. Frequency of extracted clock must be equal to the incoming data rate. For example, clock frequency of 10 GHz (with a period of 100 ps) must be extracted from data rate of 10 GB/s (each bit 100 ps wide).

- 2. Received data possess a significant amount of noise because of transmission loss and noise coupling. So clock recovered from this noisy data should replicate all noise component of data onto itself. If it happens then clock always bear phase relationship with data, and it can achieve an optimum sampling point in decision circuit. If sampling occur at midpoint of data valid window then we can achieve a maximum timing and voltage merging for jitter and other uncertainty in time domain as well as in voltage domain.