# RTL Design of SpaceWire Protocol and AMBA-Interface with LEON Processor

By

CHINTAN PATEL (07MEC020)

Department of Electronics & Communication Engineering INSTITUTE OF TECHNOLOGY NIRMA UNIVERSITY OF SCIENCE & TECHNOLOGY, AHMEDABAD 382481

# RTL Design of SpaceWire Protocol and AMBA-Interface with LEON Processor

**Major Project Report**

Submitted In Partial Fulfillment of the Requirement

For

MASTER OF TECHNOLOGY IN ELECTRONICS & COMMUNICATION ENGG. (VLSI DESIGN)

> By Chintan Patel (07MEC020)

> > Guided By:

Prof. N.P.Gajjar

Department of Electronics & Communication Engineering INSTITUTE OF TECHNOLOGY NIRMA UNIVERSITY OF SCIENCE & TECHNOLOGY, AHMEDABAD 382481

## CERTIFICATE

This is to certify that the Major Project Report entitled "RTL Design of SpaceWire **Protocol & AMBA Interface with LEON Processor**" submitted by Chintan Patel (07MEC020) towards the partial fulfillment of the requirement for the Master of Technology (Electronics & Communication Engineering) in the field of VLSI Design of Institute of Technology, Nirma University of Science and Technology, Ahmedabad is the record of the work carried our under our supervision and guidance. The work submitted has in our opinion reached a level required for being accepted for examination. The results embodied in this dissertation-project work to the best of our knowledge have not been submitted to any other University or Institute for the award of any degree or diploma.

Date:

Place: Ahmedabad

Project Guide Prof. N. P. Gajjar Institute of Technology Nirma University, Ahmedabad P.G Co-ordinator Dr.N.M.Devashrayee VLSI Design Institute of Technology Nirma University, Ahmedabad

HOD Prof. A. S. Ranade Dept. of EE Engineering Institute of Technology Nirma University, Ahmedabad Director Dr. K Kotecha Institute of Technology Nirma University, Ahmedabad

## ACKNOWLEDGEMENT

A fruitful effort in a new work needs a direction and guiding hands that shows the way. It is proud privilege and pleasure to bring out indebt ness and warm gratitude to respect **Dr. N. M. Devashrayee**, P.G. Co-coordinator, M.Tech VLSI Design, Nirma University, Ahmedabad for their support during our project work.

We would like to express our profound gratitude to **Prof N. P. Gajjar** and all other team members for outstanding support and time to time guidance during our project work.

Finally we would like to thank Arunkumar, Umang Joshi for their continuous support and constant encouragement during the project work. We would like to thank each and everyone who directly or indirectly helped us in the accomplishment of the project.

> Chintan Patel (07MEC020)

## ABSTRACT

With the progressive increase in the use of FPGAs for prototyping the embedded systems on a chip, the designing of IPs (Intellectual property) has also been increasing which are used to enhance the features of the designs. To attach an IP with one of the buses in the design, the designer has to create an interface for it. Some open source processors available like LEON and buses like AMBA bus.

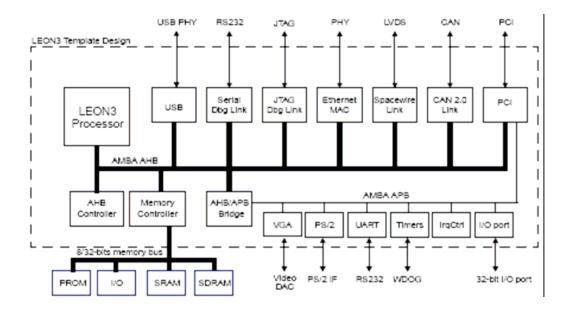

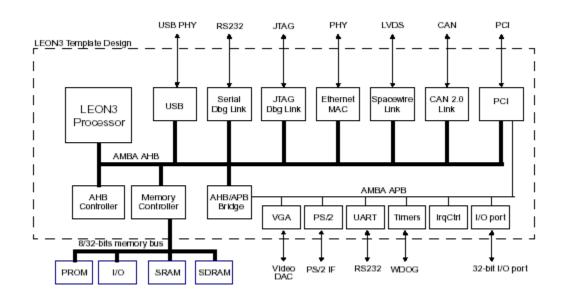

This Project reports the designing of SpaceWire Protocol and AMBA interface with LEON3 processor used as a platform for application specification SoC. The European Space Agency (ESA) proposed the SpaceWire standards for reliable satellite on-board networking at high speed upto hundreds of Mbits/sec. LEON Processor supports radiation tolerant therefore used in most of the Space application. AMBA Bus is used to interface the on chip peripheral with processor. This project report covers the theory of the SpacWire Protocol, its simulation work, theory of LEON processor, implementation of LEON3 core and AMBA AHB interface on Virtex 4 FPGA board and testing of LEON3 based SoC design.

# **List of Figures**

| Figure 2.1 LEON3 processor core block diagram         | . 10 |

|-------------------------------------------------------|------|

| Figure 2.2 Grlib Library IPs                          |      |

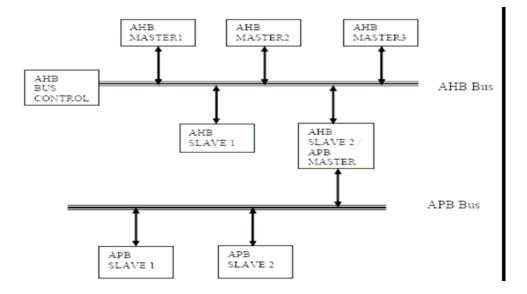

| Figure 2.3 AHB - A conceptual view                    | . 11 |

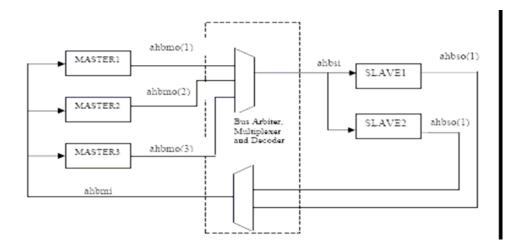

| Figure 2.4 AHB- Detailed View                         | . 12 |

| Figure 2.5 APB - A conceptual view                    | . 13 |

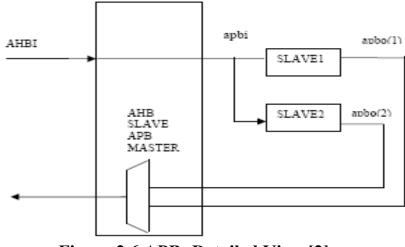

| Figure 2.6 APB- Detailed View                         |      |

| Figure 2.7 Leon Flow                                  | . 14 |

| Figure 3.1 LVDS Operation                             | . 18 |

| Figure 3.2 Data-Strobe (DS) Encoding                  | . 19 |

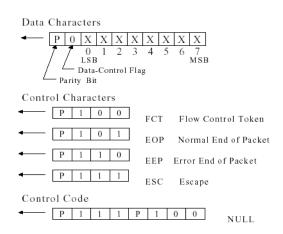

| Figure 3.3 Data and Control Characters                |      |

| Figure 3.4 Link Restart                               | . 22 |

| Figure 3.5 Packet Format                              | . 22 |

| Figure 3.6 SpaceWire Link Interface Block Diagram     | . 24 |

| Figure 3.7 State Diagram for SpaceWire Link Interface | . 26 |

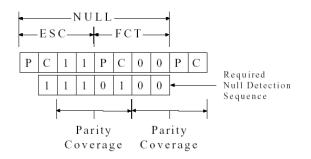

| Figure 3.8 Null Detection                             | . 30 |

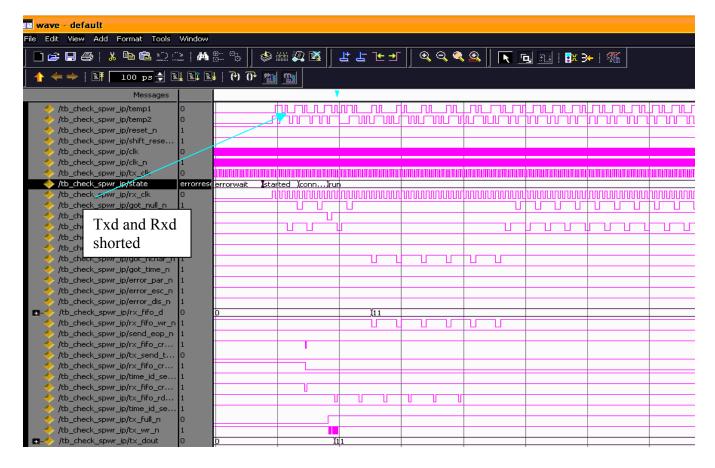

| Figure 4.1 SpaceWire in loopback mode                 | . 38 |

| Figure 4.2 IP1 to IP2 data transfer                   |      |

| Figure 4.3 Data Transfer in duplex mode               |      |

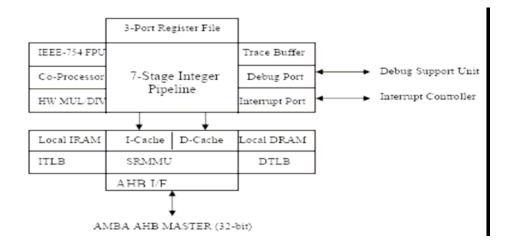

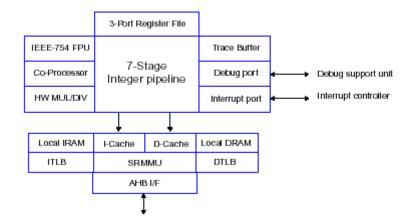

| Figure 5.1 LEON3 processor core block diagram         | . 41 |

| Figure 5.2 LEON3 based SoC                            | . 42 |

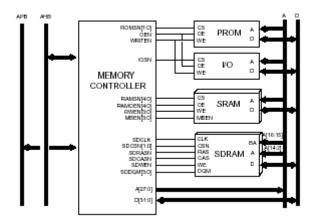

| Figure 5.3 PROM/IO/SRAM/SDRAM Memory controller       |      |

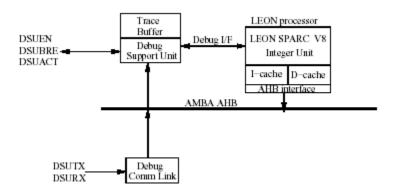

| Figure 5.4 Debug Support Unit and communication link  | . 47 |

| Figure 6.1 Cygwin Process Wizard                      | . 53 |

| Figure 6.2 GRLIB TOOL                                 |      |

| Figure 6.3 GRLIB Avnet Virtex LX60 Design             | . 54 |

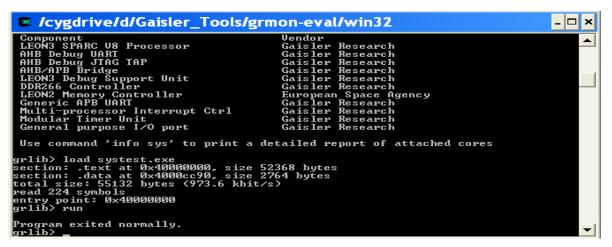

| Figure 6.4 GRMON result                               | . 54 |

| Figure 6.5 Loading application on LEON system         | . 61 |

| Figure 6.6 HyperTerminal Result                       | . 62 |

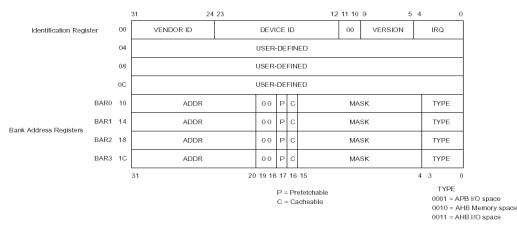

| Figure 7.1 AHB plug & play configuration layout       | . 68 |

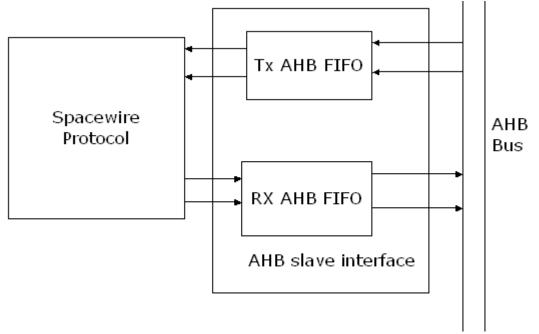

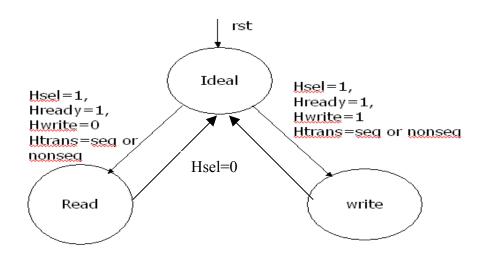

| Figure 7.2 AHB slave interface                        |      |

| Figure 7.3 Read/Write Logic                           |      |

| Figure 7.4 AHBFIFO interface with LEON                |      |

| Figure 7.5 AHBFIFO read/write result on hyperterminal | . 72 |

# List of Tables

| Table 7.1 AHB signals | .69 |

|-----------------------|-----|

|-----------------------|-----|

# Abbreviation

| GRLIB | Gaisler Research Library               |

|-------|----------------------------------------|

| AMBA  | Advance Microcontroller Bus Controller |

| AHB   | Advance High Speed Bus                 |

| APB   | Advance Peripheral Bus                 |

| FPGA  | Field Programmable Gate Array          |

| SoC   | System on Chip                         |

| SPARC | Scalable Processor Architecture        |

| IP    | Intellectual Property                  |

| LVDS  | Low Voltage Differential Signaling     |

| ESA   | European Space Agency                  |

| FCT   | Flow Control Token                     |

| EOP   | End of Packet                          |

| EEP   | Error end of Packet                    |

| ESC   | Escape                                 |

|       |                                        |

# Contents

| 1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2 Literature Survey                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 9  |

| 2.1. SpaceWire                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

| 2.1. Space whe are a space whe are a space when a space w |    |

| 2.3. GRLIB IP Library                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

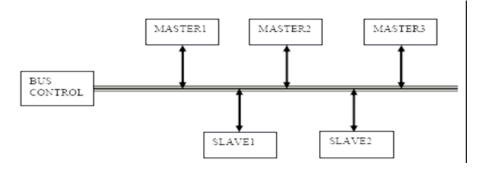

| 2.4 AMBA AHB/APB buses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

| 2.4 AMBA AHB on-chip bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| 2.4.2 AMBA APB on-chip bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

| 2.5 LEON flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

| 2.6 Environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| 3 SpaceWire Protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

| 3.1 Introduction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

| 3.2 Scope                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

| 3.3 Description.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

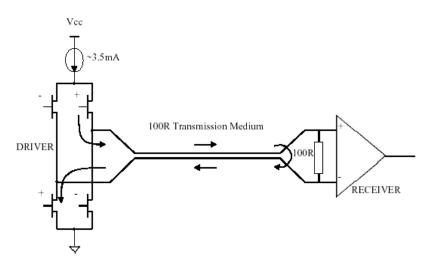

| 3.3.1 Physical Level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

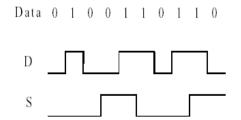

| 3.3.2 SIGNAL LEVEL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

| 3.3.3 Character Level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

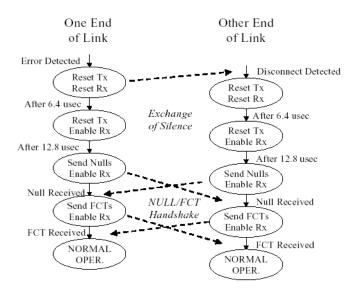

| 3.3.4 Exchange Level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

| 3.3.5 PACKET LEVEL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

| 3.3.6 NETWORK LEVEL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

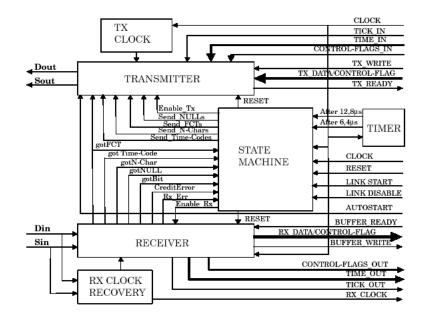

| 3.4 ENCODER/DECODER BLOCK DIAGRAM (INFORMATIVE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| 3.4.1 Transmitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

| 3.4.2 Receiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

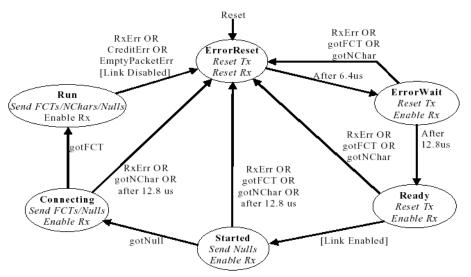

| 3.4.3 STATE MACHINE (NORMATIVE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| 3.5 Definition of States                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| 3.6 LINK INITIALISATION (INFORMATIVE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

| 4 SpaceWire Protocol Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 38 |

| 4.1 Spacewire in loopback mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

| 4.2 SpaceWire IP1 to IP2 data transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

| 4.3 SpaceWire IP1 to IP2 data transfer in duplex mode:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 40 |

| 5 LEON3 Processor: An Embedded Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

| 5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

| 5.2 Salient features of LEON are given below                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

| 5.3 Compliance with SPARC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

| 5.3.1 SPARC System Components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |