## POWER OPTIMIZATION FOR GEOGRAPHIC ROUTING ALGORITHM IN WIRELESS SENSOR NETWORK USING TI MSP430

By

MITUL PATEL 07MCE015

## INSTITUTE OF TECHNOLOGY DEPARTMENT OF COMPUTER SCIENCE & ENGINEERING NIRMA UNIVERSITY OF SCIENCE & TECHNOLOGY AHMEDABAD-382481

MAY 2009

## Power Optimization For Geographic Routing Algorithm in Wireless Sensor Network using TI MSP430

## **Major Project**

Submitted in partial fulfillment of the requirements

For the degree of

#### Master of Technology in Computer Science and Engineering

By

Mitul Patel 07MCE015

## INSTITUTE OF TECHNOLOGY DEPARTMENT OF COMPUTER SCIENCE & ENGINEERING NIRMA UNIVERSITY OF SCIENCE & TECHNOLOGY AHMEDABAD-382481

May 2009

## Certificate

This is to certify that the Major Project entitled "Power Optimization For Geographic Routing Algorithm in Wireless Sensor Network using TI MSP430" submitted by Mitul Patel (07MCE015), towards the partial fulfillment of the requirements for the degree of Master of Technology in Computer Science and Engineering of Nirma University of Science and Technology, Ahmedabad is the record of work carried out by him under my supervision and guidance. In my opinion, the submitted work has reached a level required for being accepted for examination. The results embodied in this major project, to the best of my knowledge, haven't been submitted to any other university or institution for award of any degree or diploma.

Dr. S.N. Pradhan Guide and Professor, Department of Computer Engineering, Institute of Technology, Nirma University, Ahmedabad Prof. D. J. PatelProfessor and Head,Department of Computer Engineering,Institute of Technology,Nirma University, Ahmedabad

Dr K Kotecha Director, Institute of Technology, Nirma University, Ahmedabad

### Abstract

A wireless sensor Network consists of a small battery operated sensors. After successful deployment of sensor nodes, it is often unfeasible to re-charge sensor nodes or replace batteries. Another major problem in wireless sensor network is the broken connectivity between sensor nodes due to power sources that drain out of power. To overcome these major drawbacks, optimized power consumption strategies need to be developed either by doing optimization in hardware or by using efficient software techniques.

Power consumption constraints in WSNs require efficient task distribution among various components of wireless sensor node (i.e. radio transceiver, sensing device and computation device). Most techniques use method that will switch off transmitter & receiver according to some strategy to save power but they do not consider power saving in the processor. This project proposes novel approach for routing algorithm of wireless sensor network that will optimize the power using ultra low power micro controller. This ultra low power micro controller works in different low power modes which have different power consumption statistics. The different routing algorithms have different requirements for execution on various sensor node components so based on requirements, the processor need to schedule the code so that processor will use best low power mode to execute that code on different nodes.

In real application like routing in sensor network, most of the time sensor node has only one or few components that are in active state. So the power of the remaining components that are inactive will simply be wasted. The proposed routing method will put the processor into low power mode whenever it finds the components in the inactive state. When component is once again in the active state, that component will generate an interrupt which will change the mode of the processor from low power mode to regular mode.

### Acknowledgements

The successful completion of a project is generally not an individual effort. It is an outcome of the cumulative efforts of a number of persons, each having own importance to the objective. This session is a vote of thanks and gratitude towards all those persons who have directly or indirectly contributed in their own specials way towards the completion of this project.

It gives me great pleasure in expressing thanks and profound gratitude to my project guide Dr. S. N. Pradhan, M.Tech (CSE) Program Coordinator, Department of Computer Science & Engineering, Institute of Technology, Nirma University, Ahmedabad for his valuable guidance and continual encouragement throughout the project.

I would like to give my special thanks to Prof. D. J. Patel, Head, Department of Computer Engineering, Institute of Technology, Nirma University for allowing to do project work under the university campus.

I extend my sincere thanks to my family members and my friends who have always been my source of inspiration and motivation.

> - Mitul Patel 07MCE015

# Contents

| icate                                | iii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Abstract iv                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| Acknowledgements v                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| List of Tables vii                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| List of Figures ix                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| eviations                            | x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| roduction         General            | <b>1</b><br>1<br>2<br>3<br>4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| 2 Literature Survey                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| Sources of power consumption         | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| Energy Saving At Node Level          | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| 2.2.1 Overall design of sensor node  | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|                                      | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|                                      | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|                                      | 11<br>15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|                                      | 15<br>16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| о о                                  | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|                                      | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| 01                                   | $\frac{20}{20}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|                                      | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| 2.5.3 Comparison between AVR and PIC | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|                                      | act weledgements f Tables f Tables f Figures eviations roduction General Motivation Organization of work Thesis Report Organization erature Survey Sources of power consumption Energy Saving At Node Level 2.2.1 Overall design of sensor node Energy Efficient MAC protocols 2.3.1 Contention Free Protocols 2.3.2 Contention Based Protocols 2.3.2 Contention Based Protocols 2.4.1 Sensor Network Routing Challenges 2.4.2 Routing Protocols Contention Free Survey Sources Survey Survey Survey Survey Survey Survey Surves Survey Surves Survey Surves Survey Surves Surves Survey Surves |  |  |  |  |  |

| 3            | P430 micro controller & development tools | <b>28</b>                                                |    |

|--------------|-------------------------------------------|----------------------------------------------------------|----|

|              | 3.1                                       | MSP430 Architecture                                      | 28 |

|              |                                           | 3.1.1 Low power operating modes                          | 29 |

|              |                                           | 3.1.2 Watchdog Timer                                     | 31 |

|              | 3.2                                       | MSP430 Development Tools                                 | 32 |

|              |                                           | 3.2.1 eZ430-F2013 Development Toolkit                    | 32 |

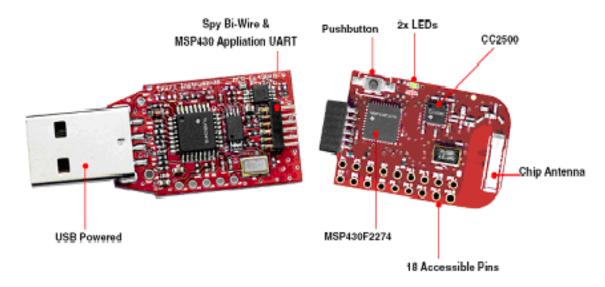

|              |                                           | 3.2.2 eZ430-RF2500 Development Toolkit                   | 33 |

| 4            | Pos                                       | ition Based Routing                                      | 36 |

|              | 4.1                                       | Unit Graph Representation of Multi-hop Wireless Network  | 36 |

|              | 4.2                                       | Position Based Routing Taxonomy                          | 36 |

|              | 4.3                                       | Geographic Routing                                       | 38 |

|              |                                           | 4.3.1 Definition                                         | 38 |

|              |                                           | 4.3.2 Greedy Routing(GR) $\ldots$                        | 39 |

|              |                                           | 4.3.3 Face $\operatorname{Routing}(\operatorname{FR})$ . | 40 |

|              |                                           | 4.3.4 Adaptive Face Routing                              | 41 |

| 5            | Imp                                       | plementation, Results & Analysis                         | 43 |

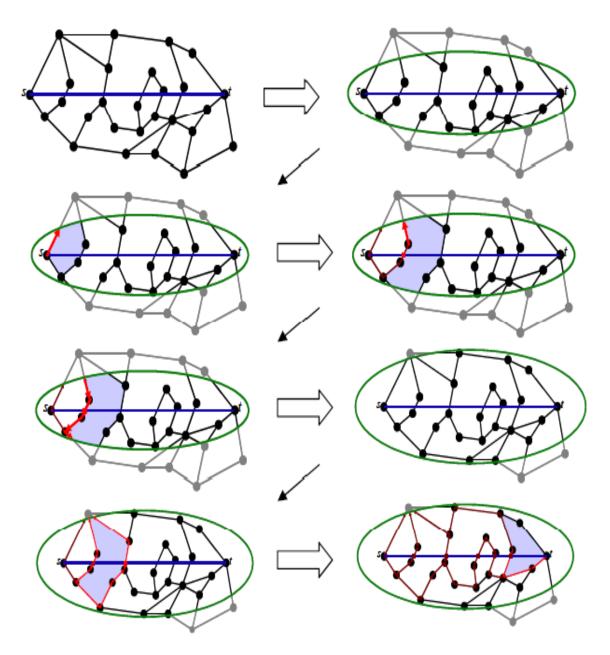

|              | 5.1                                       | Texas Instrument Virtual Lab                             | 43 |

|              |                                           | 5.1.1 IAR Embedded Workbench for MSP430                  | 43 |

|              |                                           | 5.1.2 Intrinsic Functions used for MSP430                | 45 |

|              | 5.2                                       | Proposed Design Methodology                              | 46 |

|              | -                                         | 5.2.1 Proposed Geographic Distance Routing Algorithm     | 48 |

|              | 5.3                                       | Results                                                  | 49 |

|              |                                           | 5.3.1 Result Analysis                                    | 51 |

| 6            | Conclusion and Future Scope               |                                                          |    |

|              | 6.1                                       | Conclusion                                               | 53 |

|              | 6.2                                       | Future Scope                                             | 53 |

| $\mathbf{A}$ | $\mathbf{MS}$                             | P430 Micro controller                                    | 55 |

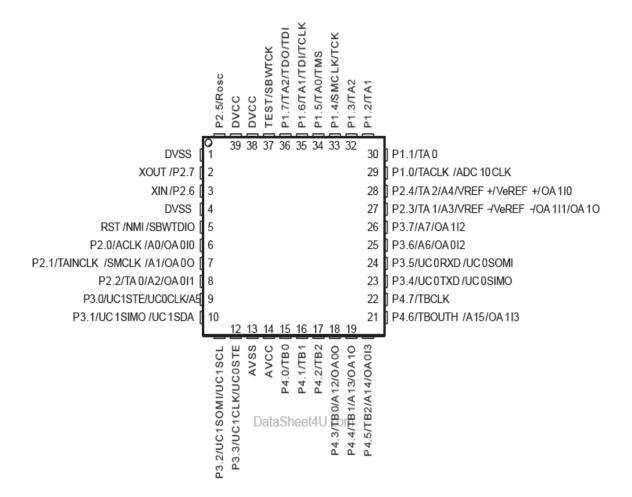

|              | A.1                                       | MSP430x22x4 device pinout, DA Packages                   | 55 |

|              | A.2                                       | MSP430x22x4 Micro controller Features                    | 56 |

|              | A.3                                       | MSP430x22x4 device pinout, RHA Packages                  | 57 |

|              | A.4                                       |                                                          | 58 |

|              |                                           | A.4.1 Address Space                                      | 58 |

|              |                                           | A.4.2 Interrupts                                         | 60 |

|              |                                           | A.4.3 CPU Introduction                                   | 61 |

|              | A.5                                       | Watchdog Timer Operation                                 | 62 |

|              |                                           | A.5.1 Watchdog Timer Counter                             | 63 |

| Re           | efere                                     | nces                                                     | 65 |

| In           | dex                                       |                                                          | 66 |

|              |                                           |                                                          |    |

# List of Tables

| Ι | Various low power operating modes                                           | 30 |

|---|-----------------------------------------------------------------------------|----|

| Ι | Various Intrinsic Functions                                                 | 45 |

|   | Difference between RISC and CISC Architecture      Watchdog Timer Registers |    |

# List of Figures

| 1.1 | Sensor Node Architecture                                                                                                                                             |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.1 | Power Consumption of Sensor [2]                                                                                                                                      |

| 2.2 | An example of slot based protocol $[2]$                                                                                                                              |

| 2.3 | Time slot organization $[2]$                                                                                                                                         |

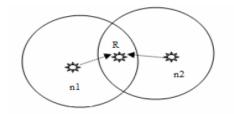

| 2.4 | Hidden Node Problem $[2] \dots \dots$                          |

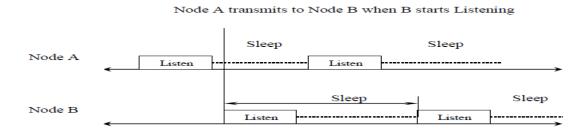

| 2.5 | S-MAC listen/Sleep Module [2] $\ldots \ldots \ldots$ |

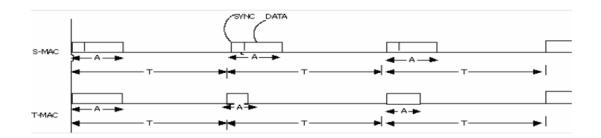

| 2.6 | Comparison of S-MAC and T-MAC                                                                                                                                        |

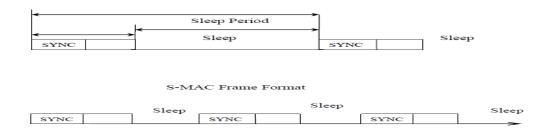

| 2.7 | DS-MAC Frame Format 15                                                                                                                                               |

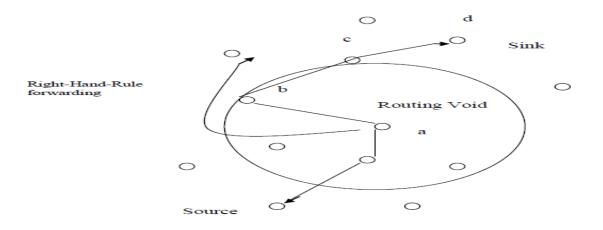

| 2.8 | Greedy and Perimeter Forwarding $[2]$                                                                                                                                |

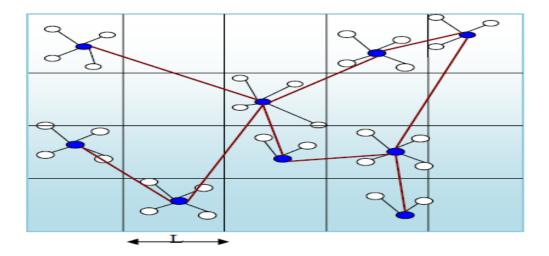

| 2.9 | Outlines GAF grid partitioning $[2]$                                                                                                                                 |

| 3.1 | MSP430F2013 Development Toolkit                                                                                                                                      |

| 3.2 | MSP430RF2500 Development Toolkit                                                                                                                                     |

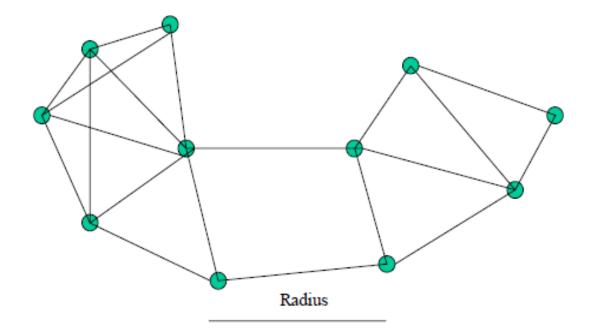

| 4.1 | Unit Graph Representation of Multi-hop Wireless Network[8] 37                                                                                                        |

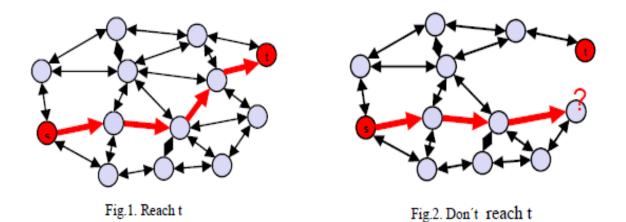

| 4.2 | Two different scenario in geographic routing[9]                                                                                                                      |

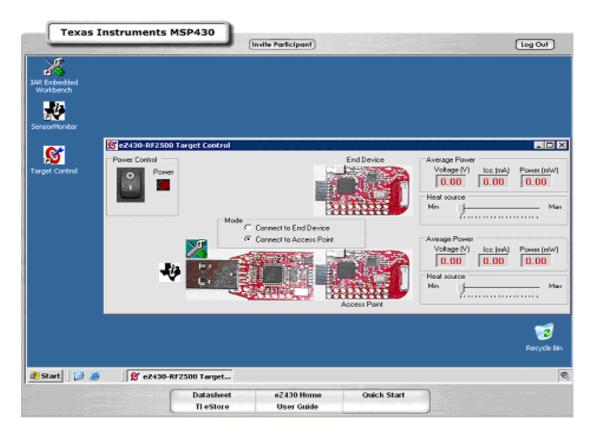

| 4.3 | Face Routing 40                                                                                                                                                      |

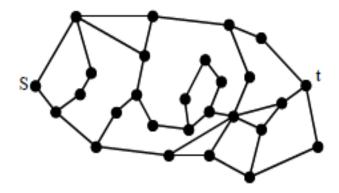

| 4.4 | Adaptive Face Routing    42                                                                                                                                          |

| 5.1 | Texas Instrument Online Virtual Lab[10]                                                                                                                              |

| 5.2 | IAR Embedded Workbench[11]                                                                                                                                           |

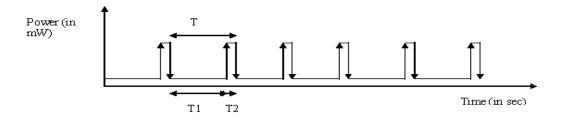

| 5.3 | Micro controller Timer Interrupt                                                                                                                                     |

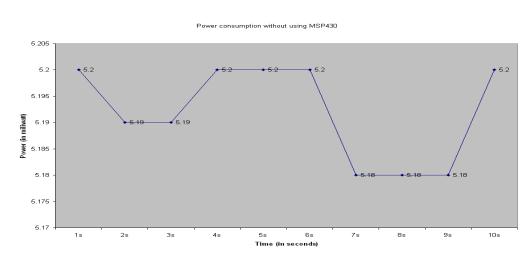

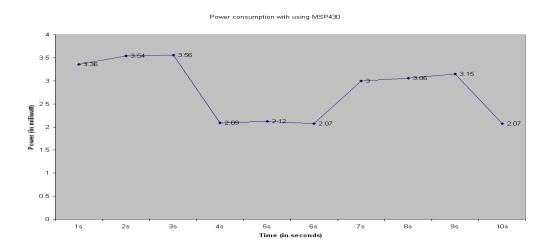

| 5.4 | Power consumption without using MSP430 micro controller                                                                                                              |

| 5.5 | Power consumption with using MSP430 micro controller                                                                                                                 |

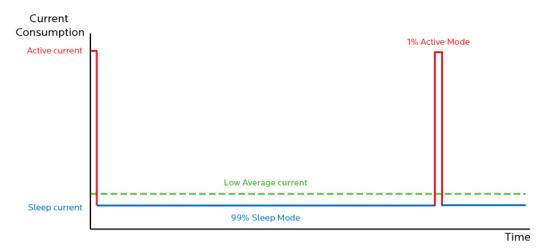

| 5.6 | Current consumption of MSP430 using watchdog timer in timer mode 51                                                                                                  |

| A.1 | MSP430x22x4 Architecture [12]                                                                                                                                        |

| A.2 | $Memory Map[13] \dots \dots$                                   |

## Abbreviations

| ACLK                 | Auxiliary Clock                   |

|----------------------|-----------------------------------|

| ADC                  | Analog-to-Digital Converter       |

| CPU                  | Central Processing Unit           |

| CISC                 | Complex Instruction Set Computing |

| DCO                  | Digitally Controlled Oscillator   |

| GIE                  | General Interrupt Enable          |

| GUI                  | Graphical User Interface          |

| ISR                  | Interrupt Service Routine         |

| LPM                  | Low Power Mode                    |

| MAB                  | Memory Address Bus                |

| MCU                  | Micro Controller Unit             |

| MCLK                 | Master Clock                      |

| MDB                  | Memory Data Bus                   |

| NMI                  | Non Maskable Interrupt            |

| PC                   | Program Counter                   |

| RISC                 | Reduced Instruction Set Computing |

| SCG                  | System Clock Generator            |

| $\operatorname{SFR}$ | Special Function Register         |

| SMCLK                | Sub-system Clock Generator        |

| $\operatorname{SR}$  | Status Register                   |

| WDT                  | Watchdog Timer                    |

|                      |                                   |

## Chapter 1

## Introduction

### 1.1 General

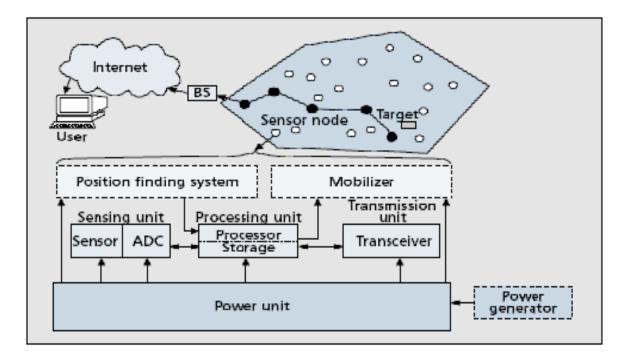

Wireless sensor network(WSN) technology is promising and is therefore gaining popularity day by day in a wide area of different applications. The WSN nodes operates on battery power which is often deployed in a rough physical environment; changing the batteries is therefore a complicated task, as some networks may consists of hundreds to thousands of nodes. Such large physically distributed networks increase the difficulty of changing batteries and makes recharging almost impossible during operations. This problem has forced node, network and system developers to make changes in the basic WSN architecture to minimize the energy consumption especially of the nodes in order make the network and overall system application more energy efficient. The sensor node architecture is given in 1.1.

As shown in 1.1, there are main three components: Sensing unit, Processing unit and Transceiver unit. So the first step in order to reduce the power consumption is to decide which component is consuming how much power. The main task of the processing unit is to control the sensing parts and to do computation on data coming from sensor and produce output. It is also associated with executing of

Figure 1.1: Sensor Node Architecture

communication protocol. Radio transceiver consumes maximum power in idle state because it has mainly three states in which it is working: active, idle and sleep. In idle state it will consume as much power as in reception state. So whenever there is no need for radio transmission then completely switch of the radio instead of putting it in an idle state.

## 1.2 Motivation

Wireless sensor network is a network of typically small battery powered wireless devices. Once deployed, it is often infeasible or undesirable to re-charge sensor nodes or replace their batteries. Thus, energy conservation becomes crucial for sustaining a sufficiently long network lifetime. Due to the nature of wireless communication, one performance metric of the network can be affected by various factors across layers. So there is a need to work upon different layer simultaneously that will help in reducing the power consumption and increasing the network lifetime.

#### CHAPTER 1. INTRODUCTION

The second major issue in wireless sensor network is the connectivity between various sensor nodes. As the connectivity is needed to transfer information from various sensor nodes to the sink node, so to increase the network lifetime nodes has to do energy efficient computation and communication in order to reduce the power consumption of individual node. As in wireless sensor network, each end device will generally communicate with another end device through access point in a centralized architecture so the power consumption of an access point is more. Therefore connectivity between the access point and number of end devices is a crucial task to do.

### **1.3** Organization of work

The power consumption of wireless sensor node can be optimized either by using energy efficient algorithms or by using special hardware devices which have ultra low power consumption characteristics. Rather then focusing on addressing the problems related with increasing the amount of available power this thesis focuses on design techniques for minimizing the amount of power required by the wireless sensor system.

The goal of this thesis is to design novel approach for routing algorithm that will efficiently use the low power and power switching characteristics of micro controller. As there are many choices available for processors like PIC micro controller, AVR micro controller and MSP430 micro controller from Texas Instruments. Among these micro controllers, Texas Instrument's MSP430 micro controller has the ultra low power consumption in terms of miliwatt(mW)

In this project, architecture of MSP430 micro controller is discussed and try to understand power consumption characteristics by using simple communication protocol that will use to transfer information between sensor nodes. The main focus of this project is to design novel approach for routing algorithm used in wireless sensor network that will use this micro controller. The tool that is to be used to develop and test the power consumption of this routing algorithm is the virtual lab provided by Texas Instruments.

## 1.4 Thesis Report Organization

- **Chapter 2**, *Literature Survey*, In it discussion about different techniques which includes various MAC layer protocol and routing techniques that has been suggested in order to optimize power by various researchers is provided.

- Chapter 3, MSP430 micro controller & development tools, presents explains general architecture of MSP430 Ultra Low Power Micro controller with some detail information about various low power operating modes and instruction set. This chapter also describes detail description of various development tools for MSP430 micro controller.

- Chapter 4, Position Based Routing, detail description of position based routing taxonomy is discussed. It also includes discussion of geographic routing algorithm.

- Chapter 5, Implementation, Results and Analysis, It describes new routing method and also describes a new way of using micro processor various low power modes. The simulation results along with the performance analysis of the proposed algorithm are presented.

- Chapter 6 concluding remarks and scope for future work is presented.

## Chapter 2

## Literature Survey

As energy saving of wireless sensor network is one of the hot topics in the Wireless Sensor Network field much research has already been done and more is expected. Much of the recent works has targeted a single factor influencing energy consumption of a network either at hardware or communication level. This project however has been done by identifying and collecting the most influential of the factors effecting energy efficiency in Wireless Sensor Network.

### 2.1 Sources of power consumption

The sources of power consumption, with regard to network operations, can be classified into two types: communication-related and computation-related.

Communication involves usage of the transceiver at the source, intermediate (in the case of ad hoc networks), and destination nodes. The transmitter is used for sending control, route request, and response messages, as well as data packets originating at or routed through the transmitting node. The receiver is used to receive data and control packets, some of which are destined for the receiving node and some of which are forwarded.

Understanding the power characteristics of the mobile radio used in wireless devices is important for the efficient design of communication protocols. A typical mobile radio may exist in three modes: transmit, receive, and standby. Maximum power is consumed in the transmit mode, and the least in the standby mode. Thus, the goal of protocol development for environments with limited power resources is to optimize the transceiver usage for a given communication task.[1]

## 2.2 Energy Saving At Node Level

The energy saving methods can be affected or can be classified under two heads:

- **Device Level** Hardware component selection and their configuration to achieve low energy consumption in a wireless sensor node.

- **Network Level** Choice of communication methods and protocols to minimize energy consumption.

#### 2.2.1 Overall design of sensor node

In a Sensor node there are four essential parts: processing unit, sensing unit, transceiver unit and, power unit. This part of Wireless sensor mote (WSM) is built on the Integrated Chip (IC). One needs to choose proper Peripheral of WSM and configure the entire network which will be more energy efficient. The basic diagram of wireless sensor mote is shown in 1.1.

Processing unit is a part of micro controller unit which can read sensor data, perform some minimal computations and make a packet ready for transfer in the wireless communication channel. The local memory requirements will not be high and emphasis will be placed on the modes of operation to facilitate low-power operation. The Communication module/unit is typically an RF transceiver that should support the 802.15.4. This unit helps in collecting information and to exchange or control data acquisition. The maximum amount of energy is used in communication module when compared to the two other modules. Sharing information between sensor nodes will consume more amount of energy than implementing the calculation within individual

#### CHAPTER 2. LITERATURE SURVEY

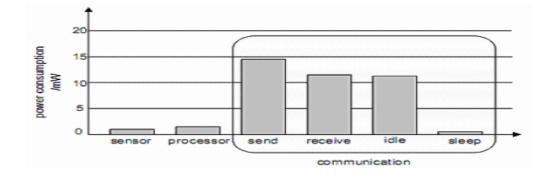

node. In Sensing unit, sensors are literally used for sensing temp, images, gas etc. Sensors to sense different things require different amount of energy. In Power unit, base stations are more often connected to main power supply, whereas nodes in the network depend on batteries to supply power. Hence there is a requirement to choose power efficient hardware and various efficient-operation modes to make the network more power efficient[2]. Figure 2.1 reflects power consumption of WSN in various states.

Figure 2.1: Power Consumption of Sensor [2]

### 2.3 Energy Efficient MAC protocols

Medium Access Control (MAC) synchronizes the channel access in an environment where numerous nodes access a shared communication medium. The MAC Layer provides an interface between the data-link layer and the PHY layer. Furthermore it can handle data service and MAC management service like generating networks beacons if the device is a coordinator, as well as GTS allocation and synchronizing to the beacons which is important for data polling and energy saving purposes. The MAC layer has a major role in making the network more power- efficient. Basically MAC is responsible for the coordination between neighbors. MAC protocol must not only be an energy constrain protocol but should also be able to address scalability issues (handling dynamic changing topology of WSNs, unaffected by node density etc) and take into account the timing constraints of the applications. A large amount of energy can be saved at this layer. Some of the causes behind energy wastage in wireless sensor networks related to this layer are mention in the short description below.

- **Collision** Once a collision of packets occurs there is re-transmission of the collided packets that were discarded, resulting in wastage of energy due to retransmission. This can be saved by avoiding collisions in the first place resulting in conserving network energy.

- Idle listening In contention-based MAC protocols when nodes are neither transmitting nor receiving data, channel still tries to sense data in which results in the wastage of energy.

- **Control packet overhead** The number of control-packet should be reduced to save energy since the transmission, reception and listening of these packets will result in energy consumption.

- **Overhearing** When node receives a packet which is addressed to some other node, overhearing occurs. This takes place during high traffic loads. Overhearing unwanted packets is wastage of energy.

All these factors must be taken into account by an energy aware MAC protocol in order to minimize the energy wastage in WSN.

#### 2.3.1 Contention Free Protocols

Many nodes are present in sensor network, and they are most likely distributed in non - uniform direction. When two sensor nodes attempt to access the communication channel at the same time, contention occurs. Due to contention messages could collide

Figure 2.2: An example of slot based protocol [2]

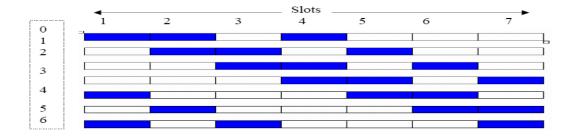

when traffic is frequent. As a result collision has an effect on the network life time of a sensor network A MAC protocol is believed to be contention-free if it does not allow collision. All accessible contention free MAC protocol assumes that the sensor nodes are time-synchronized in some way. In contention-free protocols, the channel is most often divided into time slots. To send the data, each node uses the time slot and thus it provides collision free communication.

#### Slot-based protocols

The main idea of this protocol [2] is that the time is divided into periods which has a certain number of fixed slots, where some active slot are assigned to keep the nodes active, send the beacons to neighbors and to listen for message acknowledgement or listen to requests from neighbor nodes. In slot-based protocol, beacon helps to communicate with any two nodes of a network. Figure 2.2 demonstrate that time is divided in seven periods. Any two neighbors can eventually hear each other if they use an 1101000 activation schedule since they always have at least one overlapping slot.

Schedule of the form 1101000 where 1 stand for active stage and 0 for inactive. Nodes are first communicated with each other through beacons and wait for one of them propel data to neighbors. There are no pre-defined activation schedules for slots. But it has been already proved that the number of active slots is k, then k  $= \mu + 1$ , where k stand for active slots, M for number of overlapping and  $\mu$  is prime number, as a result if . M = 1(minimum overlapping) and number of slots in the period is t then active schedule exits for t =  $\mu^2 + \mu + 1$ , if number of overlapping is increased then latency will be less, where as energy consumption will be high.

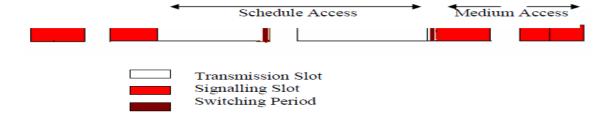

#### Time Division Multiple Access (TDMA) Protocol

TDMA is a channel access method that is used to share a radio link. In this technology, different users can share the same frequency channel by dividing the signal into different time slots. Idle listening can be avoided by using TDMA protocol and MAC layer contention issue can be fixed by scheduling transmissions earlier, so that the nodes can have information in advance when the radio should be turned on and doing so they can stay away from collision. Figure 2.3 shows time slot scheme in TDMA protocol where time is organized as sections of signalling slots and transmission slots. In classical TDMA protocols all the nodes can see each other while master node initiates the super frame in specific time interval for network operation. This technology is most suitable for single hop but for multi hop it is very difficult for multiple simultaneous transmissions.

Figure 2.3: Time slot organization [2]

One of the energy efficiency TDMA protocol is Traffic-Adaptive Medium Access (TRAMA) [1] that was developed based on Node Activation Multiple Access (NAMA) for WSN. In that proposal, time is divided into time slot and each nodes

channel access is organized over a fraction of time. In this mechanism each node has information of other two hop neighborhood and transmits data freely without interferences according to their winning slots, which mean the neighbors who have highest precedence according to their slot number and node ID. TRAMA assume low data rate compared to the time slot. Random access periods are used for time synchronization to exchange the information of the neighbors. First hop neighborhood information is broadcast in contention-based slots but the actual data transfer takes place according to a contention-free schedule.

To make this protocol energy efficient, TRAMA change nodes to sleep state whenever possible and attempt to reuse transmission slot which are not use in transmission. It is quite possible when one selected node allow his transmission slot to be used by another node if it does not have any packet to send. To make use of low power, idle mode and reuse the transmission slot nodes can share existing traffic with their neighbors.

#### 2.3.2 Contention Based Protocols

In contention-based protocols, a given transmit chance towards a receiver node can in principle be taken by any of its neighbors. If two or more neighbors try their luck at the same time, they have to compete with each other. In this case a collision might occur, wasting energy for both transmitter and receiver. In Contention-based protocol, stress is made on minimizing collisions rather than avoiding it completely (Schedule-based or collision free protocols). In this technology all node shared single radio channel according to their demand. To reduce the probability of collision or to avoid collision distributed algorithm is used which allocates the channel between nodes. In this mechanism nodes listen to the channel before sending a message just to ensure that channel status is free before transmission. If all channel are busy then node continuously listen until the medium is free to send data.

However a CSMA-based protocol in multi-hop wireless networks guides towards

hidden node problem. Due to insufficient radio coverage such as in figure 2.4, node n1 is not able to talk directly to node n2, n1 then tries to send data to its immediate neighbor R but node n2 will be unaware about this transmission and in the mean time n2 can also initiate to send data to R. As a result collision will occur on the receiving node R.

Figure 2.4: Hidden Node Problem [2]

To handle this problem additional signalling control messages have been proposed. One of them is out of bound signalling which relies on sending busy tone when transmission is in progress hence preventing other nodes from initiating transmissions. This system is known as Busy Tone Multiple Access which eradicates the hidden terminal problem. Busy tone radio is cheaper than other methods and consumes less power.

#### Sensor MAC(S-MAC)

S-MAC supports multi-hop operation. Its key features are:

- Periodic listen and sleep

- Collision avoidance

- Overhearing avoidance

- Fixed duty cycle

#### CHAPTER 2. LITERATURE SURVEY

Sensor MAC (S-MAC) uses three new procedures to decrease energy consumption and support self-configuration. It is a contention-based protocol with low duty cycle. For SMAC, energy consumption in idle listening is to be reduced by allowing neighbouring nodes of transceiver and receiver to sleep periodically during transmission, by doing so this scheme put nodes into low duty cycle. Figure 2.5 reflects SMAC listen sleep schedule. S-MAC is based on contention. Periodically sleeping is good in low traffic cases. If a node can sleep for longer time it consumes less energy. For example, if the duty cycle is trimmed down to 50can sleep half a second and be active for the other half, which results in 50

Figure 2.5: S-MAC listen/Sleep Module [2]