### POWER PERFORMANCE ANALYSIS OF EMBEDDED BLOCK CODING FOR OPTIMIZED TRUNCATION OF JPEG2000

By

JIGAR K SHAH 07MCE019

### INSTITUTE OF TECHNOLOGY DEPARTMENT OF COMPUTER SCIENCE & ENGINEERING NIRMA UNIVERSITY OF SCIENCE & TECHNOLOGY AHMEDABAD-382481

MAY 2009

### POWER PERFORMANCE ANALYSIS OF EMBEDDED BLOCK CODING FOR OPTIMIZED TRUNCATION OF JPEG2000

**Major Project**

Submitted in partial fulfillment of the requirements

For the degree of

Master of Technology in Computer Science and Engineering

By

JIGAR K SHAH 07MCE019

### INSTITUTE OF TECHNOLOGY DEPARTMENT OF COMPUTER SCIENCE & ENGINEERING NIRMA UNIVERSITY OF SCIENCE & TECHNOLOGY AHMEDABAD-382481

May 2009

#### Certificate

This is to certify that the Major Project entitled "POWER PERFORMANCE ANALYSIS OF EMBEDDED BLOCK CODING FOR OPTIMIZED TRUN-CATION OF JPEG2000" submitted by JIGAR K SHAH (07MCE019), towards the partial fulfillment of the requirements for the degree of Master of Technology in Computer Science and Engineering of Nirma University of Science and Technology, Ahmedabad is the record of work carried out by him under my supervision and guidance. In my opinion, the submitted work has reached a level required for being accepted for examination. The results embodied in this major project, to the best of my knowledge, haven't been submitted to any other university or institution for award of any degree or diploma.

Prof. (Dr.) S.N. PradhanGuide and Professor,Department of Computer Engineering,Institute of Technology,Nirma University, Ahmedabad

Prof. D. J. PatelProfessor and Head,Department of Computer Engineering,Institute of Technology,Nirma University, Ahmedabad

Dr K.Kotecha Director, Institute of Technology, Nirma University, Ahmedabad

DATE: / /

#### Abstract

The increasing popularity of power constrained mobile computers and embedded computing applications drives the need for analyzing and optimizing power in all the components of a system. Recent years have witnessed a rapid growth in research activity targeted at reducing energy consumption in microprocessor based systems. However, this research has by and large not recognized the potential energy savings achievable through optimization of software running on the microprocessor. Some research work suggested the energy efficient techniques at basic gate and architecture level, but not at the instruction level. Some software optimization techniques and compiler techniques are also suggested for that.

Software constitutes a major component of today's systems, and its role is projected to grow even further. Thus, an ever increasing portion of the functionality of today's systems is in the form of instructions, as opposed to gates. This motivates the need for analyzing power consumption from the point of view of instructions something that traditional circuit and gate level power analysis tools are inadequate for.

This study describes an alternative, measurement based software level power analysis approach that provides an accurate and practical way of quantifying the power cost of software for the ARM processor based architecture. For that,try to analyze power consumption of the JPEG2000 codec.For that Simplescalar Toolset (simplesim/ARM) which gives architecture performance analysis and Sim-Panalyzer which gives power performance analysis are used.The main source of power and memory access of JPEG2000 is EBCOT (Embedded Block Coding for Optimized Truncation) part. In this study analysis of the EBCOT algorithm and its relation in terms of power consumption are presented.

#### Acknowledgements

The successful completion of a project is generally not an individual effort. It is an outcome of the cumulative efforts of a number of persons, each having own importance to the objective. This session is a vote of thanks and gratitude towards all those persons who have directly or indirectly contributed in their own specials way towards the completion of this project.

It gives me great pleasure in expressing thanks and profound gratitude to **Dr**. **S. N. Pradhan,** PG Coordinator, Department of Computer Science & Engineering, Institute of Technology, Nirma University of Science & Technology, Ahmedabad for his valuable guidance and continual encouragement throughout the project. I heartily thankful him for his time to time suggestions and the clarity of the concepts of the topic that helped me a lot during the project and without his guidance, this project would have been an uphill task.

I would like to thank **Dr. K. Kotecha**, Director, Institute of Technology, Nirma University of Science & Technology, Ahmedabad for providing me the facilities in the Nirma campus.

I am thankful to all the faculty members of Computer Science and Engg department, Nirma University of Science & Technology, Ahmedabad for providing me needed suggestions with crucial feedback that influenced me to complete this work.

The blessings of God, my Guruji and my parents make the way for completion of major project. I am very much grateful to them.

Last but not the least, I am equally thankful to all my classmates for their support and everything.

> - JIGAR K SHAH 07MCE019

# Contents

| Ce            | ertifi                           | cate                                                                                                                                                                                                                        | iii                          |

|---------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| Al            | bstra                            | ıct                                                                                                                                                                                                                         | iii                          |

| A             | ckno                             | wledgements                                                                                                                                                                                                                 | v                            |

| Li            | st of                            | Tables                                                                                                                                                                                                                      | viii                         |

| $\mathbf{Li}$ | st of                            | Figures                                                                                                                                                                                                                     | ix                           |

| A۱            | bbre                             | viation                                                                                                                                                                                                                     | x                            |

| 1             | Intr<br>1.1<br>1.2<br>1.3<br>1.4 | coduction         General                                                                                                                                                                                                   | <b>1</b><br>1<br>3<br>4<br>6 |

| 2             | Lite<br>2.1<br>2.2<br>2.3<br>2.4 | erature Survey         General         Power Optimization Techniques         Software Power Consumption         Software Power Estimation                                                                                   | 7<br>7<br>8<br>13<br>16      |

| 3             | <b>JPI</b><br>3.1<br>3.2<br>3.3  | EG2000 Architecture & Design         Image Compression Basics         JPEG2000         JPEG2000         JPEG2000 overview                                                                                                   | <b>19</b><br>19<br>21<br>22  |

| 4             | <b>EB</b><br>4.1<br>4.2<br>4.3   | COT Design & Analysis         Introduction          Embedded Block Coding with Optimized Truncation(EBCOT)          EBCOT Algorithm and Analysis          4.3.1       Concepts for Bitplane, Scanning order and Significant | 26<br>26<br>26<br>28<br>29   |

|    |                 | 4.3.2 Fractional Bitplanes Coding: Three Coding Passes 31                                                                                     |  |  |  |

|----|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|    | 4.4             | Four Types Coding Operations                                                                                                                  |  |  |  |

| 5  | Sim             | lation Environment 36                                                                                                                         |  |  |  |

| 0  | 5.1             | The SimpleScalar Tool Set                                                                                                                     |  |  |  |

|    | 5.2             | 1                                                                                                                                             |  |  |  |

|    | 5.3             | Sim-Panalyzer Tool37Compilation of Sim-Panalyzer38                                                                                            |  |  |  |

|    | 5.4             | How to run the simulator                                                                                                                      |  |  |  |

|    | 5.5             | Estimation Procedure                                                                                                                          |  |  |  |

|    | 5.6             | ARM-LINUX Cross compiler                                                                                                                      |  |  |  |

|    | 5.7             | SimItARM Simulator                                                                                                                            |  |  |  |

|    | 0.1             | 5.7.1 SimIt-ARM features:                                                                                                                     |  |  |  |

|    |                 |                                                                                                                                               |  |  |  |

| 6  | The             | Proposed Design 43                                                                                                                            |  |  |  |

|    | 6.1             | Efficient C Programming Techniques for ARM                                                                                                    |  |  |  |

|    |                 | 6.1.1 BASIC C VARIABLE TYPES                                                                                                                  |  |  |  |

|    |                 | 6.1.2 Global variables                                                                                                                        |  |  |  |

|    |                 | 6.1.3 Local variables                                                                                                                         |  |  |  |

|    |                 | 6.1.4 Function Argument Types                                                                                                                 |  |  |  |

|    |                 | $6.1.5  \text{Using Aliases}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                |  |  |  |

|    |                 | 6.1.6 REGISTER ALLOCATION                                                                                                                     |  |  |  |

|    |                 | 6.1.7 Use of access types $\dots \dots \dots$ |  |  |  |

|    |                 | 6.1.8 Other tips $\ldots \ldots 47$                       |  |  |  |

|    | 6.2             | EBCOT Modifications 48                                                                                                                        |  |  |  |

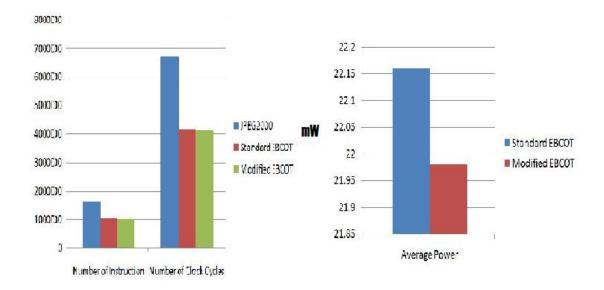

| 7  | Resi            | ilts 52                                                                                                                                       |  |  |  |

|    | 7.1             | Experienced Result                                                                                                                            |  |  |  |

|    |                 | 7.1.1 By SimIt-ARM                                                                                                                            |  |  |  |

|    |                 | 7.1.2 By Sim-panalyzer $\ldots \ldots 54$                        |  |  |  |

| 8  | Con             | clusion and Future Scope 57                                                                                                                   |  |  |  |

| 0  |                 | Conclusion                                                                                                                                    |  |  |  |

|    | 8.2             | Future Scope   59                                                                                                                             |  |  |  |

| Δ  | Sim             | bleScalar Simulator 60                                                                                                                        |  |  |  |

| Π  | -               | SimpleScalar Tool set                                                                                                                         |  |  |  |

| в  | $\mathbf{List}$ | of Useful Web sites 62                                                                                                                        |  |  |  |

| Re | eferer          | aces 63                                                                                                                                       |  |  |  |

|    |                 |                                                                                                                                               |  |  |  |

# List of Tables

| Power Reduction Techniques                                                                                                                   | 8                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Run time profile for JPEG2000<br>(Image 1792 x 1200,5 wavelet decomposition,<br>profile at PIII-733 128M RAM,<br>visual C++ and windows ME)* | 25                                                                                                                                                                                                                                                                                                                                                   |

| Context assignment table for zero coding                                                                                                     | 33                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                              | 34                                                                                                                                                                                                                                                                                                                                                   |

| Context assignment table for sign coding                                                                                                     | 34                                                                                                                                                                                                                                                                                                                                                   |

| Context assignment table for magnitude refinement $\ldots \ldots \ldots$                                                                     | 35                                                                                                                                                                                                                                                                                                                                                   |

| Complexity estimation (execution time) for JPEG2000 encoder <sup>*</sup>                                                                     | 52                                                                                                                                                                                                                                                                                                                                                   |

| Average Power Dissipation for EBCOT on StrongARM-1110                                                                                        | 55                                                                                                                                                                                                                                                                                                                                                   |

| Average Power Consumption for EBCOT on Strong<br>ARM-1110 $\hdots$                                                                           | 55                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                              | Run time profile for JPEG2000(Image 1792 x 1200,5 wavelet decomposition, profile at PIII-733 128M RAM, visual C++ and windows ME)*<br>Context assignment table for zero coding Sign contribution of the horizontal and vertical neighbors for sign coding Context assignment table for sign coding Context assignment table for magnitude refinement |

# List of Figures

| 3.1 | A Typical Lossy Signal/Image Encoder                                                               | 20 |

|-----|----------------------------------------------------------------------------------------------------|----|

| 3.2 | The JPEG2000 encoding block diagram                                                                | 23 |

| 3.3 | Codec structure. The structure of the (a) encoder and (b) decode $\ . \ .$                         | 24 |

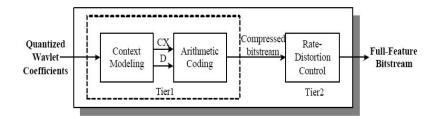

| 4.1 | Two tiered coding in EBCOT                                                                         | 27 |

| 4.2 | CX-D pair in EBCOT                                                                                 | 27 |

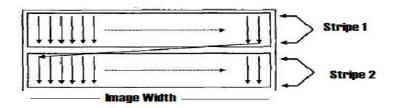

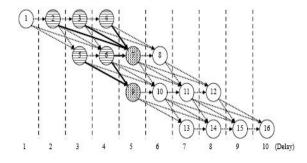

| 4.3 | Scanning order of context formation in every pass                                                  | 28 |

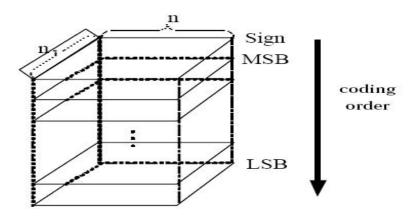

| 4.4 | The bitplane views for quantized coefficients with code block size n x n                           | 29 |

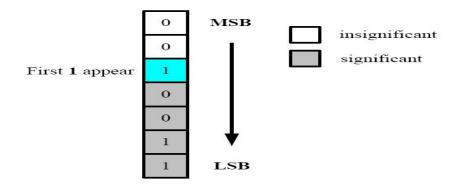

| 4.5 | Context modeling scanning sequence for one bitplane in each pass                                   | 30 |

| 4.6 | An example for the significant state transition                                                    | 30 |

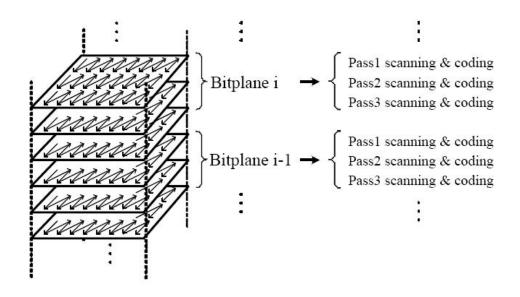

| 4.7 | Fractional bitplanes coding                                                                        | 31 |

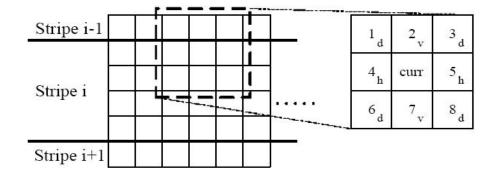

| 4.8 | The current coding bit and its eight neighbors                                                     | 32 |

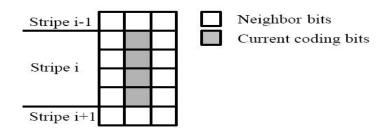

| 4.9 | Current coding bits and their neighbors for RLC operation                                          | 35 |

| 5.1 | Example of cmd file                                                                                | 39 |

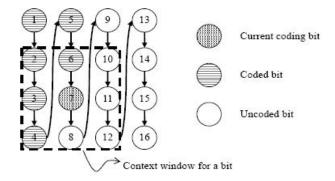

| 6.1 | Scanning order                                                                                     | 49 |

| 6.2 | Data dependency within sixteen bits                                                                | 49 |

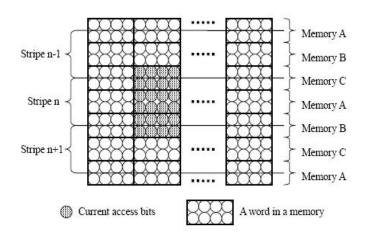

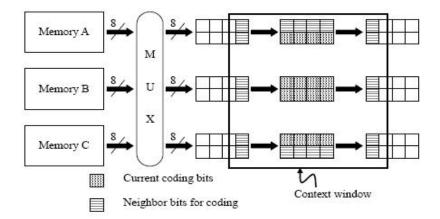

| 6.3 | Memory arrangement                                                                                 | 50 |

| 6.4 | Context window and memory bandwidth                                                                | 50 |

| 8.1 | (a). Comparison in terms of Total Instruction and Clock Count (b).<br>Comparison in terms of Power | 58 |

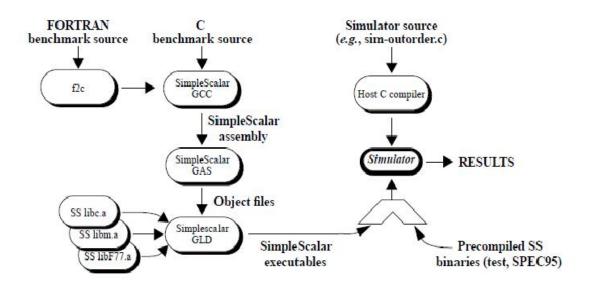

| A.1 | SimpleScalar tool set overview                                                                     | 60 |

### Abbreviation

| EBCOT               | Embedded Block Coding for Optimized Truncation        |

|---------------------|-------------------------------------------------------|

| DWT                 | Discrete Wavelet Transform                            |

| DCT                 | Discrete Cosine Transform                             |

| SoC                 | System on Chip                                        |

| AIO                 | Address Input Output                                  |

| DIO                 | Data Input Output                                     |

| ITLB                | Instruction Table Look-aside Buffer                   |

| DTLB                | Data Table Look-aside Buffer                          |

| IL1 Cache           | Address Input Output                                  |

| DL1 Cache           | Address Input Output                                  |

| AIO                 | Address Input Output                                  |

| IRF                 | Instruction Register File                             |

| PSNR                | Peak Signal to Noise Ratio                            |

| MSE                 | Mean Swuare Error                                     |

| ICT                 | Irreversible Component Transform                      |

| RCT                 | Reversible Component Transform                        |

| EZW                 | Embedded Zero-Tree Wavelet Compression                |

| SPIHT               | Spatial Partitioning of Image into Hierarchical Trees |

| MSB                 | most significant bit-plane                            |

| LSB                 | least significant bit-plane                           |

| RLC                 | Run Length Coding                                     |

| $\mathbf{SC}$       | Sign Coding                                           |

| $\operatorname{ZC}$ | Zero Coding                                           |

| MR                  | Magnitude Refinement                                  |

| CF                  | Context Formation                                     |

| AE                  | Arithmetic Encoder                                    |

## Chapter 1

### Introduction

### 1.1 General

Until recently, power dissipation was an issue that primarily concerned designers of embedded portable computer systems. However, power issues are becoming some of the primary design constraints for even very high-end microprocessors. Power consumption analysis is the basis of high-level power reduction techniques because they do not rely on actual physical design. High-level power reduction of microprocessorbased systems saves power consumption by changing energy-sensitive factors such as instruction fetch addresses, opcode encoding, register encoding, data fetch addresses, immediate operands, etc. Some of the energy-sensitive factors have great degrees of freedom while others are more restrictive. Under certain circumstances, even data and instructions can be changed as far as the original semantic is preserved. Consequently, it is important to be informed of power consumption variations with respect to the energy-sensitive factors for setting up proper power reduction strategies.

Power analysis can be performed by "simulation-based" or "measurement- based" approaches. [1] Simulation-based power analysis is convenient as far as a simulation model is available because it does not necessitate a prototype. Simulation is preferable to avoid system dependent bias as power consumption is also variable to bus configuration and peripheral devices. Measurement-based power consumption analysis is sometimes more feasible due to the availability of existing models even if a prototype is necessary. Even with a prototype, correct measurements are not easily obtainable because digital systems consume power in a spiky manner with over hundreds MHz in the power spectrum.

Instruction-level power studies of ARM ISA processors have been performed earlier. However, none of these accurately characterize or model external memory accesses or stalls. While this is acceptable for small benchmarks, a real OS and application can spend a significant number of cycles in such states. We accurately model both instructions and events such as stalls and memory accesses, in order to create a power model that is sufficiently accurate for modeling a full-featured OS and complete applications running over billions of clock cycles.

The intricacy involved by these new electronic appliances imposed a new design paradigm to cope with the specific requirements, e.g., low cost with fast time to market, and restrictions they have. Also, energy consumption is a critical factor in system-level design of embedded portable appliances. A hardware-software co-design framework must be employed to proceed with the design from the software applications intended to run on these appliances to the final specifications of the hardware that implements the desired functionality given the above-mentioned constraints. Studies have demonstrated that circuit- and gate-level techniques have less than a 2x impact on power, while architecture- and algorithm-level strategies offer savings of 10x - 100x or more. Hence, the greatest benefits are derived by trying to assess early in the design process the merits of the potential implementation. Architecture optimization corresponds to searching for the best design that optimizes all objectives. Since the optimization problem involves multiple criteria (power consumption, throughput, and cost) to reach the global optimum a set of desicive points in the design space have to be found. Ideally, when designing an embedded system, a designer would like to explore a number of architectural alternatives and test functionality, energy consumption, and performance without the need to build a prototype.

#### **1.2** Motivation

The increasing popularity of power constrained mobile computers and embedded computing applications drives the need for analyzing and optimizing power in all the components of a system. This has forced an examination of the power consumption characteristics of all modules - ranging from disk-drives and displays to the individual chips and interconnects. Focusing solely on the hardware components of a design tends to ignore the impact of the software on the overall power consumption of the system. Software constitutes a major component of systems where power is a constraint. Its presence is very visible in a mobile computer, in the form of the system software and application programs running on the main CPU. But software also plays an even greater role in general digital application, since an ever growing fraction of these applications are now being implemented as embedded systems. Embedded systems are characterized by the fact that their functionality is divided between hardware and a software component. The software component usually consists of application-specific software running on a dedicated processor, while the hardware component usually consists of application-specific circuits. In light of the above, there is a clear need for considering the power consumption in systems from the point of view of software. Software impacts the system power consumption at various levels of the design. At the highest level, this is determined by the way functionality is partitioned between hardware and software. The choice of the algorithm and other higher level decisions about the design of the software component can affect system power consumption in a big way. The design of system software, the actual application source code, and the process of translation into machine instructions - all of these determine the power cost of the software component. In order to systematically analyze and quantify this cost, however, it is important to start at the most fundamental level. This is at the level of the individual instructions executing on the processor. Just as logic gates are the fundamental units of computation in digital hardware circuits, instructions can be thought of as the fundamental unit of software. This motivates the need for analyzing

power consumption from the point of view of instructions. Accurate modeling and analysis at this level is the essential capability needed to quantify the power costs of higher abstractions of software, and to search the design space in software power optimizations.

Instruction level analysis of a processor helps in the development of models for power consumption of software executing on that processor. The ability to evaluate software in terms of power consumption makes it feasible to search for low power implementations of given programs. In addition, it can guide the development of general tools and techniques for low power software. Several ideas in this regard as motivated by the power analysis of the subject processors are also described.[2, 3]

As advance in computer technology continues, use of internet, 3G, 4G techniques also increases and so Battery-powered devices such as mobile cellular phones, personal multimedia player, and personal digital assistants have recently become prevalent platforms to run image and video compression applications. Image and Video compression applications require high computational complexity, which means battery powered devices need high operating clock rate and large battery. And so these battery supported devices need techniques that reduces power requirement of the devices.

And last but not least, as use of environment aware system, use of "GREEN" system and its use in technology increases. This study will help to advance the technology in terms of power study.

### 1.3 Scope of Work

Software power analysis can help in reducing power consumption of battery supported system and also there are other several additional applications of this analysis and it is instructive to list the important ones here:

• The information provided by the analysis is useful in assigning an accurate power cost to the software component of a system. For power constrained embedded systems, this can help in verifying if the overall system meets its specified power budget.

- The most common way of specifying power consumption in processors is through a single number - the average power consumption. Instruction level analysis provides additional resolution about power consumption that cannot be captured through just this one number. This additional resolution can guide the careful development of special programs that can be used as power benchmarks for more meaningful comparisons between processors.

- The measurement based instruction level analysis methodology has the novel strength that it does not require knowledge of the lower level details of the processor. However, if micro-architectural details of the CPU are available, they can be related to the results of the analysis. This can lead to more refined models for software power consumption, as well as power models for the micro-architecture that may potentially be more accurate than circuit or logic simulation based models.

- The additional insight provided by an instruction-level power model also provides directions for modifications in processor design that lead to the most effective overall power reduction. Instructions can be evaluated both in terms of their power cost as well as frequency of occurrence in typical compiler or even hand-generated code. This combined information can be used to prioritize instructions that should be re-implemented to be less expensive in terms of power.

This paper describes that with power analysis of Embedded Block Coding for Optimized Truncation (EBCOT), we can decide power budget for embedded system of EBCOT. And also Enable us to Design its specific SoC based VLSI chips that can be efficiently work in Digital cameras.

#### 1.4 Thesis Organization

The rest of the thesis is organized as follows.

- Chapter 2, Literature Survey, In it different power aware techniques at all level is described. And software power consumption and estimation research is described.

- Chapter 3, JPEG2000 Architecture & Design, presents the JPEG2000 architecture and its basics.

- chapter 4, EBCOT Design & Analysis, presents part of JPEG2000, EBCOT architecture and its algorithm.

- Chapter 5, Simulation Environment, describes the different simulator and cross compiler for power analysis.

- Chapter 6, Proposed Design, In it C programming power aware techniques and EBCOT algorithm modification techniques for power aware are described.

- Chapter 7, Results, In it experienced results are shown.

- chapter 8, Conclusion and Future Scope concluding remarks and scope for future work is presented.

## Chapter 2

## Literature Survey

### 2.1 General

Power is dissipated in various forms:

- a. Interconnect Power

- Resistances and Parasitic Capacitances

- Transitions because of change in data results in charging and discharging

- b. Memory power

- Depends on type of memory

- Depends on the number of access, the size of the memory (code and data), the number of ports used.

- c. CPU power

- Instruction fetch, decode and execution results in power consumption

- Depends on current withdrawn by each instruction

#### CHAPTER 2. LITERATURE SURVEY

Power is the basic constraint for the embedded environment and computer architecture.Power optimization can be done by mainly two approaches:

- Hardware Power Management

- Software Power Management

A lot research has been done in both Hardware and Software approaches. Power optimization can be done at different levels as shown in Table I.

| Levels        | Techniques for power reduction                                     |  |

|---------------|--------------------------------------------------------------------|--|

| System        | Design partitioning, Power Down                                    |  |

| Algorithm     | Complexity, Concurrency, Locality, Regularity, Data representation |  |

| Architecture  | Voltage scaling, Parallelism, Instruction-set, Signal correlations |  |

| Circuit/logic | Transistor Sizing, Logic optimization, Activity Driven Power Down, |  |

| Technology    | Threshold Reduction, Multi thresholds                              |  |

Table I: Power Reduction Techniques

#### 2.2 Power Optimization Techniques

- a. At System Level

- Design partitioning

- Power Down

Detect and shut down unused units.

To reduce the power in synchronous designs, it is important to minimize switching activity by powering down execution units when they are not performing "useful" operations. This is an Important concern since logic modules can be switching and consuming power even when they are not being actively utilized. • Scheduling:

Hardware allocation and task assignment.

• HW/SW co-design

#### b. At Algorithm Level

• The choice of an algorithm is the most highly leveraged decision in meeting the power constraints. The power consumption is strongly correlated to of a number of properties that a given algorithm may have.

• Some algorithmic properties which are critical for selection an algorithm for low power design:

- Size measures includes quantities such as the number of nodes, the bit width, the number of I/O operations, the number of operations, and the number of memory accesses.

- (2) Concurrency measures the number of operations and interconnect accesses that can be executed concurrently.

- (3) Temporality captures information about the lifetimes of variables in the computation. A computation is considered to be temporally local if the expected lifetimes of the variables are short. It is temporally dense if the measured maximum expected number of variables alive at any time is large.

- (4) Spatial locality characterizes the degree to which the algorithm has natural clusters of computation, within which significant amounts of computation can be done independently.

- (5) Regularity captures the degree to which common patterns appear.

- c. At Architecture Level

• The architectural level is the design entry point for the large majority of digital designs and design decisions at this level can have dramatic impact on the power budget design.

• Perhaps the most important strategy for reducing power consumption involves employing concurrent processing at the architecture level. This is a direct tradeoff of area and performance for power.

• Power Reduction Techniques.

- Low system clocks High frequencies are generated with on-chip PLLs.

- High-level of integration (single chip) Avoid off-chip components

- Power management: shutdown unused blocks

- Memory partitioning Selectively enabled blocks

- Parallelism, pipelining

- Reduction of global busses

- Simplification of instruction coding and execution

- Component minimization Arithmetic Memories/registers

- Scheduling and allocation

- Data/number coding

- Voltage reduction

- To use this technique a designer should follow the next rules: Repeat the data path hardware n times.

Use clock rate of 1/nT.

Use a multiplexer to produce the output stream.

The input and output stream should have the same throughput rate.

- Depending on the data path architecture, a typical estimation of the voltage reduction of 40% can be achieved. Although the use of parallelism leads to large power reduction, the penalty is increased area occupation.

- Parallel processing and pipelining

- Parallel processing can be an important technique for reducing power consumption in CMOS systems.

- Pipelining does not share this advantage because it achieves Concurrency by increasing the lock frequency, which limits the ability to scale the voltage.

- This is an interesting reversal because pipelining is simpler that Parallel processing;

- Therefore, pipelining is traditionally the first choice to speed up Execution. In practice, the trade-off between pipelining and parallelism is not so distinct:

- Replicating function units rather than pipelining them has the negative effect of increasing area and wiring, which in turn can increase power consumption.

- The degree to which designers can parallelize computations varies widely. Although some computations are "embarrassingly parallel," they are usually characterized by identical operations on array data structures.

- Buses

- Buses are a significant source of power loss, especially interchip buses, which are often very wide.

- A chip can expend 15 percent to 20

- One approach to limiting this swing is to encode the address lines into a Gray code because address changes, particularly from cache refills, are

often sequential, and counting in Gray code switch the least number of signals.

- Transmitting the difference between successive address values achieves a result similar to the Gray code.

- Compressing the information in address lines further reduces them.

- These techniques are best suited to interchip signaling because designers can integrate the encoding into the bus controllers. At Circuit/Logic levelCode compression results in significant instruction memory savings if the system stores the program in compressed form and decompresses it on the fly, typically on a cache miss. [4]

- d. At Circuit/Logic level

- Clock gating

Widely used to turn off clock tree branches to latches or flip-flops whenever they are not used. Until recently, developers considered gated clocks to be a poor design practice because the clock tree gates can exacerbate clock skew. More accurate timing analyzers and more flexible design tools have made it possible to produce reliable designs with gated clocks

• Half-frequency and half-switching clocks

A half-frequency clock uses both edges of the clock to synchronize events half the frequency of a conventional clock. Drawbacks: the latches are more complex and occupy more area, and that the clock's requirements are more stringent. [4]

The half-swing clock swings only half of V dd. It increased the latch design's requirements and is difficult to use in systems with low V dd.

However, lowering clock swing usually produces greater gains than clocking on both edges.

- Choices between static versus dynamic topologies, conventional CMOS versus pass-transistor logic styles and synchronous versus asynchronous timing styles have to be made during the design of a circuit

- In static CMOS circuits, the component of power due to short circuit current is about the 10% of the total power consumption. However, in dynamic circuits does not appear this problem, since there is not any direct dc path from supply voltage to ground. Only in domino-logic circuits there is such a path, in order to reduce sharing, hence there is a small amount of short-circuit power dissipation. [5]

- Asynchronous logic. Because the systems do not have a clock, they save the considerable power that a clock tree requires.

- Optimizing switching activity (example from Rabaey: DIC).

- e. At Transistor level

- Physical Capacitance: Three sources of capacitance: gate capacitance, diffusion capacitance, and interconnects capacitance. If all three components can be scaled down by the same factor, then the net power dissipation will be scaled down as well.

- Transistor Sizing: To minimize the physical capacitance, all transistors should be minimum size. Exceptions:

#### 2.3 Software Power Consumption

The overall power dissipation of an embedded system does not only originate from the application - specific hardware, but also from the CPU, the memory and the address

and data buses when an embedded application is running on the platforms microprocessor, microcontroller or digital signal processor. This above power dissipation is referred to as software power dissipation. Obviously, the power is actually dissipated in the processors hardware, but it is as a consequence of executing an application program. There are a number of sources of power dissipation influenced by software and contributing to the overall power dissipation of the system, which are explained below. [6]

#### **Bus Power**

Busses in an embedded system consist of unidirectional address bus lines and instruction bus lines (opcodes to be executed) and bi-directional data bus lines. With these groups of interconnecting lines, the communication of the CPU with the memory, I/O circuits and peripheral modules is established. Each of the above lines can be modeled as an RC transmission line, where R and C are the lines resistance and capacitance, respectively. Activation of a line prompts for the charging or discharging of the capacitive load, depending on the previous value that this line had. For example, a transition in an 8-bit data bus between words 00101011 and 11100111 implies charging of 3 lines and discharging of 1 line. Usually, bus charging and discharging of I/O lines can occur up to 80% of the software execution time.

#### Memory Power

Power dissipated by memory read and write accesses is usually one of the dominating components (ranging from 10% - 25%) of the total software power dissipation for mobile devices and portable computers. In the case of DSP applications, where a significant amount of data is processed, this contribution can be substantially higher. Memory power dissipation has a number of components, namely power dissipated in the cell array, in the decode logic and sense amplifier as well as power dissipated due to charging and discharging of the address or data lines capacitances. The type of access is also significant in how much it contributes to the overall power dissipation. In the

ARM microprocessor, which is considered in our system, CPU cycles are divided in S-cycles, N-cycles, and I-cycles.

The S-cycles refer to sequential memory accesses, where the next word is returned from the same buffer, dissipating a relatively small amount of power. Power dissipation in the address lines during sequential memory accesses is also small, due to the fact that the address word changes only in one bit. If the last memory location of a page is to be accessed though, more power has to be consumed in order to access the next page.

The N-cycles refer to non-sequential memory accesses. In this kind of access, more power is dissipated relative to sequential accesses because consecutive address words are irrelevant, causing large activity in the address bus. In N-cycles usually different pages have to be accessed, contributing to more power dissipation, as explained above.

Finally, the I-cycles refer to cycles that no memory access is involved, so no power is dissipated in the memory system. One more significant contributor to the power dissipated in the memory is the memory access patterns, affecting mainly the cache hits and misses. The cache, residing closer to the CPU than main memory, dissipates less power because the address and data lines are shorter and have less internal capacitance. Inappropriate memory access patterns lead to cache misses, consequently, power expensive main memory accesses.

#### CPU Power

When instructions are executed in the CPU, they contribute significant power to the overall power dissipation. The instructions can be divided into four broad categories:

- Load / Store instructions

- Branch instructions

- Type-1 Arithmetic instructions, such as addition, subtraction, shift etc.

- Type-2 Arithmetic instructions, such as multiplication and division.

If we assume that the average power consumption to execute one instruction is  $W_j$ , where j represents one of the categories mentioned above, and  $I_j$  is the number of times this instruction is executed, we can easily derive the CPU power dissipation as:

$$P_{CPU} \alpha \frac{\sum (W_j * I_j)}{\sum I_j} \tag{2.1}$$

The power dissipated when an arithmetic instruction is executed depends primarily on the ALU or FPU data path that it instructed by software. Many different ways of optimization exist in this context, as for example replacing a division by power of two with corresponding right shifts. Finally, instruction scheduling is very important, because unsuccessful scheduling can lead to pipeline stalls, which in turn consume a considerable amount of power.

#### **Other Power Dissipation Sources**

There is a number of additional sources of power dissipation during software execution that must be taken into account, as they contribute as an overhead to the overall power dissipation. These sources are the clock distribution and the control logic and they accompany code execution in each cycle. In it was shown that short code sequences in a number of microcontrollers and DSPs always dissipated a smaller amount of power than longer sequences. The program in longer code sequences, which demanded extra execution cycles, took more time to execute so that the overhead was more than that in shorter code sequences. Despite this problem, power management techniques nowadays tend to eliminate such overhead by cleverly dealing with power dissipation that does not have a direct contribution to the involved computational tasks.

#### 2.4 Software Power Estimation

The methodology proposed by Vivek Tiwari et al[1, 2, 3]. has been adopted as starting point for analysis of software power estimation. In spite of importance of estimation

at this level of abstraction, previous work exists for analyzing power consumption from the point of view of software. In [1, 2] the authors show that the choice of the algorithm and other high level decisions about the design of the software component can affect system power consumption in a big way. They propose an instruction level power analysis technique based on a physical measurement that helps in formulating instruction level power models that provide fundamental information needed to evaluate the power cost of an entire program. The basic components of each power model are the same. The first component is a set of base costs for the instructions set. The other components is the power cost of inter-instruction effects which involve more than one instruction. The base cost of an instruction can be thought of as the cost associated with the basic processing needed to execute the instruction. Experiments to determine this cost requires a program containing a loop consisting of several instances of the given instruction. The average current drawn during the execution of this loop is measured by an ameter inserted in series with the power supply and the CPU. The simple characterization with a base cost does not take into account the power consumption due to the change of circuit state when a sequence of two different instruction is executed. The difference between the measured current and the average base costs of the two instructions is defined as the circuit state overhead for the pair. For a sequence consisting of a mix of instructions, using the base costs of instructions almost always underestimates the actual cost. Adding in the average the circuit state overhead for each pair of consecutive instructions leads to a much closer estimate. The basic idea to determine this power contribution is to write programs where these effects occur repeatedly.

#### Definition of Power and Energy

Average Power:

$$P_{avg} = I_{avg} * V_{cc} \tag{2.2}$$

Energy :

$$E = P_{avg} * T \tag{2.3}$$

$$T = N * t \tag{2.4}$$

$$E = I_{avg} * V_{cc} * t \tag{2.5}$$

- $P_{avg}$ : Average power

- $I_{avg}$ : Average current

- $V_{cc}$ : Supply voltage

- E : Energy consumption

- T : Time taken

N : Number of cycles

t : Cycle time

MOV DX, [BX] Power = 1.15 W MOV AX, CX Energy = 8.6 \* 10 - 8 J MOV AX, DX

$$Program energy cost = \sum_{i} (Base_i * N_i) + \sum_{i,j} (Ovhd_{i,j} * N_i) + \sum_{k} Energy_k \quad (2.6)$$

$N_i$ : Number of times instruction i is executed

$Base_i$ : Base energy cost of i

$Ovhd_{i,j}$ : Circuit state overhead when i, j are adjacent

$Energy_k$ : Energy overhead of stalls, cache misses

Program power cost = Energy cost / execution time

## Chapter 3

## JPEG2000 Architecture & Design

#### 3.1 Image Compression Basics

Uncompressed multimedia (graphics, audio and video) data requires considerable storage capacity and transmission bandwidth. Despite rapid progress in mass-storage density, processor speeds, and digital communication system performance, demand for data storage capacity and data-transmission bandwidth continues to outstrip the capabilities of available technologies. The recent growth of data intensive multimediabased web applications have not only sustained the need for more efficient ways to encode signals and images but have made compression of such signals central to storage and communication technology.

For still image compression, the 'Joint Photographic Experts Group' or JPEG standard has been established by ISO (International Standards Organization) and IEC (International Electro-Technical Commission). The performance of these coders generally degrades at low bit-rates mainly because of the underlying block-based Discrete Cosine Transform (DCT) scheme. More recently, the wavelet transform has emerged as a cutting edge technology, within the field of image compression. Wavelet-based coding provides substantial improvements in picture quality at higher compression ratios. Over the past few years, a variety of powerful and sophisticated wavelet-based schemes for image compression, as discussed later, have been developed and implemented. Because of the many advantages, the top contenders in the upcoming JPEG-2000 standard are all wavelet-based compression algorithms.

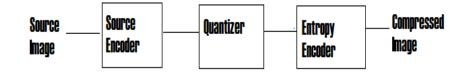

A typical lossy image compression system is shown in Fig. 3.1. It consists of three closely connected components namely (a) Source Encoder (b) Quantizer, and (c) Entropy Encoder. Compression is accomplished by applying a linear transform to decorrelate the image data, quantizing the resulting transform coefficients, and entropy coding the quantized values.

Figure 3.1: A Typical Lossy Signal/Image Encoder

The goal of this article is two-fold. First, for readers new to compression, we briefly review some basic concepts on image compression and present a short overview of the DCT-based JPEG standard and the more popular wavelet-based image coding schemes. Second, for more advanced readers, we mention a few sophisticated, modern, and popular wavelet-based techniques including one we are currently pursuing. The goal of the upcoming JPEG-2000 image compression standard, which is going to be wavelet-based, is briefly presented. For those who are curious, a number of useful references are given. There is also abundance of information about image compression on the Internet. Background

#### 3.2 JPEG2000

JPEG 2000 is an initiative that will provide an image coding system using compression techniques based on the use of wavelet technology.

Wavelet theory [7] is also a form of mathematical transformation, similar to the FT in that it takes a signal in time domain, and represents it in frequency domain. Wavelet functions are distinguished from other transformations in that they not only dissect signals into their component frequencies, they also vary the scale at which the component frequencies are analyzed. Therefore wavelets, as component pieces used to analyze a signal, are limited in space. In other words, they have definite stopping points along the axis of a graph-they do not repeat to infinity like a sine or cosine wave does. As a result, working with wavelets produces functions and operators that are "sparse" (small), which makes wavelets excellently suited for applications such as data compression and noise reduction in signals. The ability to vary the scale of the function as it addresses different frequencies also makes wavelets better suited to signals with spikes or discontinuities than traditional transformations such as the FT. JPEG 2000 is a new standard for image coding published by the JPEG committee (ISO/IEC JTC 1/SC 29/WG 1) at the turn of the millennium. It is still being enhanced. The core, defined in Part 1 of the standard (ISO/IEC 15444 1), is built around the relatively new technologies of wavelet-based compression and bit-plane coding. It enables scalability with respect to five different defined image progression orders. The idea is similar to progressive JPEG, but the packetised structure of a JPEG 2000 codestream makes it possible to convert between different progression orders by the systematic reordering of packets, without any low-level decoding.

JPEG 2000 refers to all parts of the standard: [8]

The parts are:

• Part 1, Core coding system (intended as royalty and license-fee free - NB NOT patent-free)

• Part 2, Extensions (adds more features and sophistication to the core)

- Part 3, Motion JPEG 2000

- Part 4, Conformance

- Part 5, Reference software (Java and C implementations are available)

- Part 6, Compound image file format (document imaging, for pre-press and fax-like applications, etc.)

- $\circ$  Part 7 has been a<br/>bandoned

- Part 8, JPSEC (security aspects)

- Part 9, JPIP (interactive protocols and API)

- Part 10, JP3D (volumetric imaging)

- Part 11, JPWL (wireless applications)

- Part 12, ISO Base Media File Format (common with MPEG-4)

As part of part5 there are C and Java implementation of JPEG2000 are available. And they are the acceptable standard of JPEG2000 and widely used.

- C implementation of JPEG2000 [9]

- Java implementation of JPEG2000 [10]

### 3.3 JPEG2000 overview

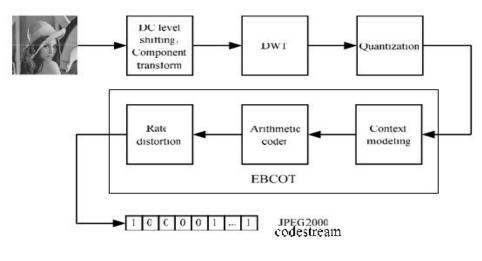

The JPEG2000 is composed of several main procedures such as DC level shifting, component transform, discrete wavelet transform, quantization and EBCOT (Context modeling, arithmetic coder and rate-distortion), as shown in Figure 3.2

Figure 3.2: The JPEG2000 encoding block diagram [11]

Each block shown in Figure 3.2 is depicted below.

• DC Shift & Component Transform

An image is usually composed of many components, for example, the R, G, B for color image. Each component is encoded by the DC shift coding so that the samples are changed from unsigned numbers to signed numbers. If the input image consists the color component, the reversible component transform (RCT) and the irreversible component transform (ICT) are enabled to improve the compression efficiency. [12]

• Discrete Wavelet Transform

DWT transfers the image information from spatial domain to frequency domain thus the spatial correlation can be removed by DWT. There are two modes for DWT in JPEG2000. The integer (5, 3) filter applied in DWT is used to enable the lossless compression. Another one is for the default mode, DWT with the Daubechies (9, 7) filter, for the lossy compression. DWT is to separate high frequency part and low frequency part from vertical and horizontal directions

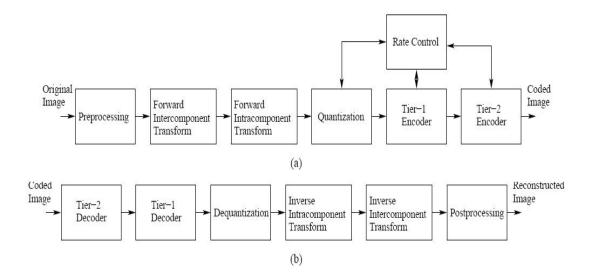

Figure 3.3: Codec structure. The structure of the (a) encoder and (b) decode

of an image respectively. [12]

• Scalar Quantization

After DWT operated, the image coefficients is quantized to achieve the target bit-rate or distortion. Notice that the quantization operation causes the distortion for reconstruction image hence the quantization operation is adopted in lossy compression only. The quantization is used to adjust compression ratio by reducing the accuracy resolution. By the way, the compression ratio in JPEG2000 also can be controlled by EBCOT so that the quantization operation can be skipped. [12]

• Embedded Block Coding with Optimized Truncation

EBCOT [13] is the entropy coder for JPEG2000 and detailed discussed in the following chapter. Comparing with the other wavelet-based entropy coding algorithms, such as the well know EZW and SPIHT, EBCOT provides better compression performance. The EBCOT coder divides each subband coefficient into code blocks.[13] Each code block is coded separately into a block based

embedded bit-stream, i.e. it doesn't need to consult other code blocks. The transformed coefficients of a code block are coded bit-plane by bit-plane from most significant bit-plane (MSB) to least significant bit-plane (LSB) instead of coefficient by coefficient with three passes called Significance Propagation Pass (Pass1), Magnitude Refinement Pass (Pass2), and Clean-Up Pass (Pass3). The arithmetic coder outputs are the sub-bit-streams of each compressed code block data. The rate-distortion block is designed to achieve progressive transmission and rate-distortion control.

EBCOT is the main base algorithm and followed in JPEG2000 as a block coder. From Table I it is sure that the main bottleneck of JPEG2000 is EBCOT, mainly tire-1. So here in this thesis performance analysis of EBCOT is described.

| operation                | Single Component(sec) | RGB Component(sec) |

|--------------------------|-----------------------|--------------------|

| Intercomponent transform |                       | 14.12              |

| Intracomponent transform | 26.38                 | 23.97              |

| Quantization             | 6.42                  | 5.04               |

| EBCOT Tier 1             | 52.26                 | 43.85              |

| pass 1                   | 14.82                 | 12.39              |

| pass 2                   | 7                     | 5.63               |

| pass 3                   | 16.09                 | 13.77              |

| arithmatic encoder       | 14.35                 | 12.06              |

| EBCOT Tier 2             | 14.95                 | 13.01              |

| layer formation          | 9.52                  | 7.95               |

| marker insertion         | 5.43                  | 5.06               |

Table I: Run time profile for JPEG2000(Image 1792 x 1200,5 wavelet decomposition,profile at PIII-733 128M RAM,visual C++ and windows ME)\* [14]

## Chapter 4

## EBCOT Design & Analysis

### 4.1 Introduction

JPEG2000 entropy coder is EBCOT (Embedded Block Coding with Optimal Truncation Points) contextual coder. It is a bit-plane block coder i.e. it codes the wavelet coefficients by blocks. It codes the wavelet coefficients by blocks. On each bit-plane, there are three coding passes: a pass of Significance Propagation, a pass of Magnitude Refinement and a Cleanup pass. Four coding primitives are used: the RL(Run-Length) primitive, the ZC (Zero Coding) primitive, the MR (Magnitude Refinement) and the SC (Sign Coding) primitive. Here is an example how those coding passes are jointly used with the coding primitives.

## 4.2 Embedded Block Coding with Optimized Truncation(EBCOT)

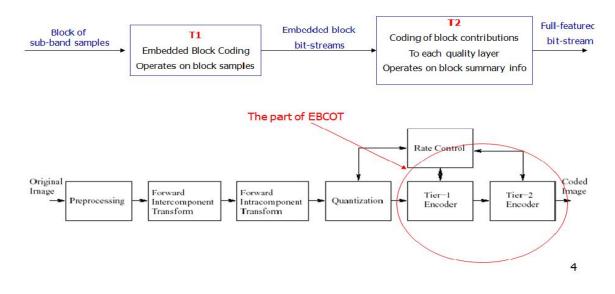

The entropy coding for JPEG2000 encoding system is a bitplane-based coding, embedded block coding with optimized truncation (EBCOT). The EBCOT algorithm consists of two major steps: EBCOT block coding and rate-distortion optimization, i.e. the tier1 and tier2 in Figure 4.1, and the block coding also include two part, context modeling and arithmetic coding. The EBCOT coder divides each subband coefficient into code blocks. Each code block is coded separately into a block-based embedded bitstream, i.e. it doesn't need to refer other code blocks. The tier2 coder organizes the bitstream to form a full-featured JPEG2000 bitstream.

Figure 4.1: Two tiered coding in EBCOT

The context modeling, the first stage of EBCOT tier-1 coding, partitions the quantizer indices for each subband into code-blocks. It scans these quantizer indices in code-block bitplane by bitplane then generates a context-decision pair Figure 4.2to arithmetic coder (MQ coder).

Figure 4.2: CX-D pair in EBCOT

### 4.3 EBCOT Algorithm and Analysis

Tier- 1 of EBCOT utilizes context-based arithmetic coding method to encode each code block into independent embedded bit-stream. Tier-1 coder can be viewed as two parts: Context Formation (CF) and Arithmetic Encoder (AE).[14] CF scans all pixels in code block in a specific order, and generates corresponding contexts for each bit. AE encodes the code block data according to their. contexts. EBCOT encodes the quantized wavelet coefficients bitplane by bitplane from MSB to LSB. Every 4 rows in a bitplane are called a stripe, and each pass in every bitplane scans in order stripe by stripe. Then in every stripe, data are scanned column by coluinn. Every column is composed of 4 bits. So the scanning hierarchy of a code block is bitplane, pass, stripe, column, bit, as shown in Fig. 4.3.

Figure 4.3: Scanning order of context formation in every pass

Contexts for all bits are generated according to their neighbors using four coding methods. Before CF, the quantized wavelet coefficients are separated into sign and magnitude (in 1s compliment). A pixel is called significant after the first 1 bit is met while encoding magnitude part from MSB to LSB, and insignificant before the first 1 bit appears. The context of each bit is determined by significant situations of its neighbors. There are four coding methods to generate context for each bit in a code block: Zero Coding, Run-Length Coding, Sign Coding, and Magnitude Refinement.Every bitplane is encoded using 3 passes in turn. Each pixel in a bitplane is encoded in one of 3 passes. Pass 1 is Significant Propagation Pass. Pixels having at least one significant neighbor are coded in this pass. Pass 2 is Magnitude-Refinement Pass. All significant pixels are coded in this pass. Pass 3 is Clean-up Pass. Pixels not coded in first two passes are coded in this pass. While coding a bitplane, every pixel is checked once in all 3 passes to detennine if this pixel should be coded. In Taubmans architecture, a straightforward method is used. Every single bit is checked and (or) coded in all 3 passes, which cost total 3 clocks. Coding a 64x64 code block with 8-bit precision will take 64x64 8 cl3oc ks. That makes tier- 1 coder become bottleneck of PEG-2000 system design.

#### 4.3.1 Concepts for Bitplane, Scanning order and Significant

The key idea of EBCOT coding is bitplane scanning, as presented in Figure 4.4, rather than coefficient scanning. Every bitplane takes three passes. The coefficient-bits scanning order in each pass is stripe-based method with stripe height of 4 compared with zigzag scan adopted in JPEG. An example code-block scan pattern of a code-block with size 8 x n is shown in Figure 4.5.

Figure 4.4: The bitplane views for quantized coefficients with code block size n x n [12]

| 0  | 4 | 8  | 12 | 16 | 20 | 24 | 28 |

|----|---|----|----|----|----|----|----|

| 1  | 5 | 9  | 13 | 17 | 21 | 25 | 29 |

| 2  | 6 | 10 | 14 | 18 | 22 | 26 | 30 |

| 3  | 7 | 11 | 15 | 19 | 23 | 27 | 31 |

| 32 |   |    | 9  |    |    |    |    |

| 33 |   |    |    |    |    |    |    |

Code-block 8 wide by n height

Figure 4.5: Context modeling scanning sequence for one bitplane in each pass [12]

Besides, the EBCOT algorithm starts coding process when the first non-zero bitplane met and skips the all- zero bitplane. The number of skipped bitplanes is record in the packet header. In the EBCOT context modeling, the significant bit is employed in the pass and coding decision. A sample became significant when the first 1 of magnitude bit is found, and this concept is illustrated in Figure 4.6, and the sign bit is coded instantly after the first significant bit coded.

Figure 4.6: An example for the significant state transition [12]

#### 4.3.2 Fractional Bitplanes Coding: Three Coding Passes

To achieve the EBCOT coding algorithm, the coefficients in a code block must be encoded from the most significant bitplane (MSB) to the least significant bitplane (LSB) in the one of three coding passes. They are Significant Propagation Pass (Pass1), Magnitude Refinement Pass (Pass2) and Cleanup Pass (Pass3) in sequence. Figure 4.7 illustrates the concept of fractional bitplanes coding.

Figure 4.7: Fractional bitplanes coding [12]

#### Significance Propagation Pass (Pass1)

This coding pass focuses on the coefficient-bits that are insignificant but have at least one of eight neighbors being significant, as shown in Figure 4.8. In another words, the most proper coefficients becoming significant are searched and encoded in Pass1. In Pass1 stage, the zero coding and sign coding operations are used.

Figure 4.8: The current coding bit and its eight neighbors [12]

#### Magnitude Refinement Pass (Pass2)

The coefficients-bits that have become significant and are not coded during coding Pass1, i.e. the coefficients-bits have become significant in previous bitplane, are found and coded in Pass2. The coding operation in Pass2 is magnitude refinement coding.

#### Clean Up Pass (Pass3)

These remained coefficients rejected by pass1 and 2 are coded in Pass3. In this pass, the zero coding, sign coding and run- length coding operations are used. Notice that only Pass3 codes the first non- zero bitplane because the coefficients are all insignificant in the beginning. Compared with other non-zero bitplanes, each coefficient-bit in a bitplane is coded by one of three coding passes. This coding property causes the context modeling to waste the most time on checking and skipping the redundant bits. The EBCOT context modeling being the bottleneck for the JPEG2000 system is expected.

### 4.4 Four Types Coding Operations

As introduced before, the EBCOT context modeling assigns the coefficients-bits a context with different coding operations depending on the pass type and the significant state of eight neighbor-bits. The eight immediate neighbor-bits as illustrated in Figure 2.13 can be classed with horizontal set (neighbor 4, 5), vertical set (neighbor 2, 7) and diagonal set (neighbor 1, 3, 6 and 8). We now introduce the four different coding operations for context modeling.

#### • Zero Coding (ZC)

Zero coding is used in Pass1 and Pass3 coding. If the coefficient-bit is insignificant, ZC uses on of 9 different contexts in Table I assigning to the coefficient-bit depending on the significant state of immediate neighbors. Note that if the current coding coefficient-bit lies beyond the boundary of code block, its neighbors are taken as insignificant for context assignment. This is due to reduce the dependence between different code blocks.

In Table I  $\Sigma$ H,  $\Sigma$ V, and  $\Sigma$ D are represented as the sum of significant neighbors in horizontal, vertical, and diagonal directions, as shown in Figure 4.8. table

| $\Sigma \mathbf{H}$ | $\Sigma \mathbf{V}$ | $\Sigma \mathbf{D}$ | $\Sigma \mathbf{H}$ | $\Sigma \mathbf{V}$ | $\Sigma \mathbf{D}$ | $\Sigma \mathbf{H} + \Sigma \mathbf{V}$ | $\Sigma \mathbf{D}$ | Context Label |

|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|-----------------------------------------|---------------------|---------------|

| 2                   | х                   | Х                   | х                   | 2                   | Х                   | X                                       | $\geq 3$            | 8             |

| 1                   | $\geq 1$            | Х                   | $\geq 1$            | 1                   | Х                   | $\geq 1$                                | 2                   | 7             |

| 1                   | 0                   | $\geq 1$            | 0                   | 1                   | $\geq 1$            | 0                                       | 2                   | 6             |

| 1                   | 0                   | 0                   | 0                   | 1                   | 0                   | $\geq 2$                                | 1                   | 5             |

| 0                   | 2                   | Х                   | 2                   | 0                   | Х                   | 1                                       | 1                   | 4             |

| 0                   | 1                   | Х                   | 1                   | 0                   | Х                   | 0                                       | 1                   | 3             |

| 0                   | 0                   | $\geq 2$            | 0                   | 0                   | $\geq 2$            | $\geq 2$                                | 0                   | 2             |

| 0                   | 0                   | 1                   | 0                   | 0                   | 1                   | 1                                       | 0                   | 1             |

| 0                   | 0                   | 0                   | 0                   | 0                   | 0                   | 0                                       | 0                   | 0             |

Table I: Context assignment table for zero coding

#### • Sign Coding (SC)

Sign coding is used in Pass1 and Pass3, which the same as ZC. When a coefficient switches from insignificant to significant, SC operation turns on and the sign bit for the coefficient is coded to one of 5 different contexts. The decision of contexts in SC is depend upon the sign and the significance of the horizontal and vertical neighbors as presented in Table II and Table III. Notices that SC is operated at most once for each coefficient. Referring to Table II, the XOR bit is employed to generate the

| Sign Contribution  | Significant, $(+)$ | Significant, (-) | Insignificant |

|--------------------|--------------------|------------------|---------------|

| Significant, $(+)$ | 1                  | 0                | 1             |

| Significant, (-)   | 0                  | -1               | -1            |

| Insignificant      | -1                 | -1               | 0             |

Table II: Sign contribution of the horizontal and vertical neighbors for sign coding

| Horizontal Contribution | Vertical Contribution | Context Label | XOR bit |

|-------------------------|-----------------------|---------------|---------|

| 1                       | 1                     | 13            | 0       |

| 1                       | 0                     | 12            | 0       |

| 1                       | -1                    | 11            | 0       |

| 0                       | 1                     | 10            | 0       |

| 0                       | 0                     | 9             | 0       |

| 0                       | -1                    | 10            | 1       |

| -1                      | 1                     | 11            | 1       |

| -1                      | 0                     | 12            | 1       |

| -1                      | -1                    | 13            | 1       |

Table III: Context assignment table for sign coding

output D of EBCOT context modeling, as defined in Equation (4.1).

$$D = sign\_bit \oplus bit \tag{4.1}$$

#### • Magnitude Refinement (MR)

The magnitude refine operation is utilized in Pass2 coding. Based on the significant state for 8 neighbors and whether or not the coefficients are first refining, MR assigns one of 3 contexts in Table IV to the coefficients-bits that have been significant in previous bitplanes.

| $\Sigma \mathbf{H} + \Sigma \mathbf{V} + \Sigma \mathbf{D}$ | First refinement for this coefficient | Context Label |

|-------------------------------------------------------------|---------------------------------------|---------------|

| X                                                           | FALSE                                 | 16            |

| $\geq 1$                                                    | TRUE                                  | 15            |

| 0                                                           | TRUE                                  | 14            |

Table IV: Context assignment table for magnitude refinement

#### • Run-Length Coding (RLC)

Run-length coding is operated in Pass3 coding. It is enabled when the following conditions are true.

- Four consecutive coefficients in the same stripe are insignificant.

- The neighbors for the consecutive four coefficients must be insignificant, too.

The coefficients-bits relate to RLC is illustrated in Figure 4.9. Compared RLC with ZC, they are used to code the insignificant coefficients-bits but the RLC assigns one context to four coefficients-bits.

Figure 4.9: Current coding bits and their neighbors for RLC operation

## Chapter 5

## Simulation Environment

### 5.1 The SimpleScalar Tool Set