# Formal Verification Using SLEC(Sequential Logic Equivalence Checker)

Major Project Report

Submitted in partial fulfillment of the requirements

for the degree of

Master of Technology

$\mathbf{in}$

**Electronics & Communication Engineering**

(Embedded Systems)

By

Shreya Panjvani (15MECE15)

Electronics & Communication Engineering Department Institute of Technology-Nirma University Ahmedabad-382481 MAY 2017

# Formal Verification Using SLEC(Sequential Logic Equivalence Checker)

### Major Project Report

Submitted in partial fulfillment of the requirements

for the degree of

### Master of Technology

in

### **Electronics & Communication Engineering**

(Embedded Systems)

By Shreya Panjvani (15MECE15)

Under the guidance of

#### **External Project Guide:**

### Mrs Swati Garg

Member Of Consulting Staff, SLEC PV,

Mentor Graphics India Pvt Ltd,

Noida.

## Internal Project Guide:

### Dr.N.P.Gajjar

Assistant Professor, EC Department Institute of Technology, Nirma University, Ahmedabad.

Electronics & Communication Engineering Department Institute of Technology-Nirma University

Ahmedabad-382 481

MAY 2017

# Declaration

This is to certify that

- a. The thesis comprises my original work towards the degree of Master of Technology in Embedded Systems at Nirma University and has not been submitted elsewhere for a degree.

- b. Due acknowledgment has been made in the text to all other material used.

- Shreya Panjvani 15MECE15

# Disclaimer

"The content of this thesis does not represent the technology,opinions,beliefs, or positions of Mentor Graphics India Pvt Ltd,its employees,vendors, customers, or associates."

# Certificate

This is to certify that the Major Project entitled "Formal Verification Using SLEC(Sequential Logic Equivalence Checker)" submitted by Shreya Panjvani (15MECE15), towards the partial fulfillment of the requirements for the degree of Master of Technology in Embedded Systems, Nirma University, Ahmedabad is the record of work carried out by her under our supervision and guidance. In our opinion, the submitted work has reached a level required for being accepted for examination. The results embodied in this major project, to the best of our knowledge, haven't been submitted to any other university or institution for award of any degree or diploma.

Date:

Place: Ahmedabad

Dr N.P.Gajjar

Internal Guide

Dr. N.P. Gajjar Program Coordinator

**Dr.N.P.Gajjar** Section Head, EC **Dr Alka Mahajan** Director, IT

# Certificate

This is to certify that the Major Project (Phase- I) entitled "Formal Verification Using SLEC(Sequential Logic Equivalence Checker)" submitted by Shreya Panjvani(15MECE15), towards the partial fulfillment of the requirements for the degree of Master of Technology in Embedded Systems, Nirma University, Ahmedabad is the record of work carried out by her under our supervision and guidance. In our opinion, the submitted work has reached a level required for being accepted for examination.

Mrs Swati Garg Member Of Consulting Staff, SLEC PV, Mentor Graphics India Pvt Ltd, Noida

### Acknowledgements

I would like to express my gratitude and sincere thanks to **Dr. N.P.Gajjar**, PG Coordinator of M.Tech Embedded Systems program for allowing me to undertake this thesis work and for his guidelines during the review process.

I take this opportunity to express my profound gratitude and deep regards to **Dr N.P.Gajjar**, guide of my major project for his exemplary guidance, monitoring and constant encouragement throughout the course of this thesis. The blessing, help and guidance given by him time to time shall carry me a long way in the journey of life on which I am about to embark.

I would take this opportunity to express a deep sense of gratitude to **Mrs Swati Garg**,Member Of Consulting Staff, SLEC PV,Mentor Graphics India Pvt Ltd. for her cordial support, constant supervision as well as for providing valuable information regarding the project and guidance, which helped me in completing this task through various stages.

I am obliged to team members of SLEC PV, Mentor Graphics India Pvt Ltd. for the valuable information provided by them in respective fields. I am grateful for their cooperation during the period of my assignment.

Lastly, I thank almighty, my parents, brother and friends for their constant encouragement without which this assignment would not be possible.

> - Shreya Panjvani 15MECE15

### Abstract

Verification of different designs using automated tools has become the widely used methodology for the Electronic Design Automation(EDA) industry. SLEC(Sequential Logic Equivalence checker) is one such tool which uses formal verification.

Formal verification is a method of proving or disproving the functionality of any design using Formal methods. Formal Verification does not require input vectors like simulation. It verifies two designs by comparing boolean equation of both the designs, generated using formal algorithms.

SLEC(Sequential Logic Equivalence Checker) is a sequential equivalence checker which compares two designs:specification design (SPEC) and Implementation design (IMPL) which may be structurally not equivalent. Formal Verification using SLEC in HLS(High Level Synthesis) is the main motto of this thesis.

The flow of HLS using Mentor's Catapult and SLEC(Sequential Logic Equivalence Checker) was studied and performed. Different features of SLEC HLS flow were tested. Bug finding and reporting was done in Bugzilla. Automation work required for the tool was done using scripting.

SLEC uses formal verification which leads to better coverage, better resource allocation, lower power consumption and lesser area. SLEC can prove two designs formally equivalent inspite of structural differences.

# Contents

| De       | eclar  | iii                                   | i |

|----------|--------|---------------------------------------|---|

| Di       | sclai  | mer iv                                | 7 |

| Ce       | ertifi | vate                                  | 7 |

| Ce       | ertifi | cate vi                               | i |

| A        | cknov  | vledgements vii                       | i |

| Al       | ostra  | ct viii                               | i |

| Li       | st of  | Figures xiii                          | i |

| 1        | Intr   | oduction 1                            |   |

|          | 1.1    | Motivation                            | L |

|          | 1.2    | Objective                             |   |

|          | 1.3    | Requirements                          | 2 |

| <b>2</b> | An     | Introduction to Formal Verification 3 | ; |

|          | 2.1    | An Introduction to verification       | } |

|          | 2.2    | Formal Verification                   | ł |

|          |        | 2.2.1 Formal Equivalence Checking     | ŀ |

### CONTENTS

| 3        | Ove  | rview of SLEC                                | 6  |

|----------|------|----------------------------------------------|----|

|          | 3.1  | Introduction to SLEC                         | 6  |

|          | 3.2  | Advantages of SLEC                           | 7  |

|          | 3.3  | Ability of SLEC                              | 8  |

|          |      | 3.3.1 Equivalence Checking Compatibility     | 8  |

|          |      | 3.3.2 Refinement Verification                | 8  |

|          |      | 3.3.3 Basic operation of SLEC                | 9  |

|          | 3.4  | Setup File                                   | 11 |

|          | 3.5  | SLEC-HLS                                     | 12 |

|          |      | 3.5.1 SLEC-HLS Flow                          | 13 |

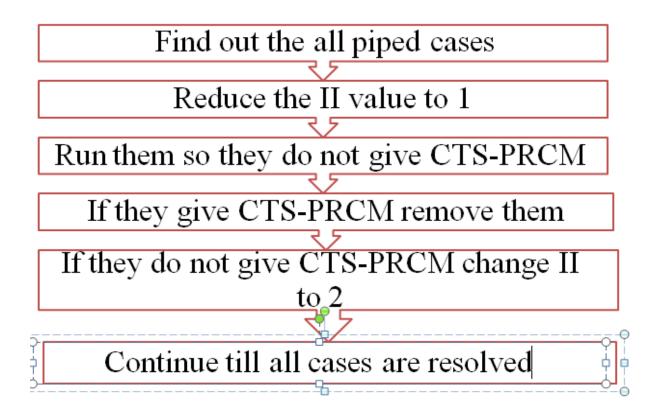

| 4        | Test | ing the all piped feature of SLEC HLS flow   | 21 |

|          | 4.1  | An Introduction to pipelining                | 21 |

|          | 4.2  | Problem Statement                            | 23 |

|          | 4.3  | Initation Interval value                     | 23 |

|          | 4.4  | Algorithm For the Problem                    | 23 |

|          | 4.5  | Problems                                     | 24 |

|          | 4.6  | Summary of the testing                       | 24 |

| <b>5</b> | Test | ing the CCORE functionality of SLEC HLS flow | 25 |

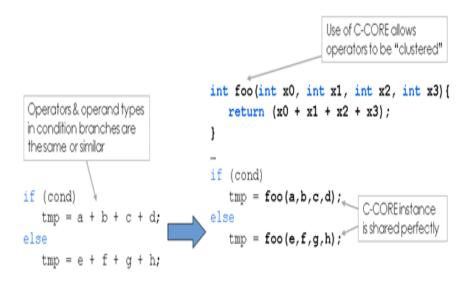

|          | 5.1  | An Introduction to CCORE                     | 25 |

|          | 5.2  | Synthesis of CCORE in Catapult               | 26 |

|          | 5.3  | Constraint on CCORE synthesis in Catapult    | 27 |

|          | 5.4  | Types of CCORE in Catapult                   | 27 |

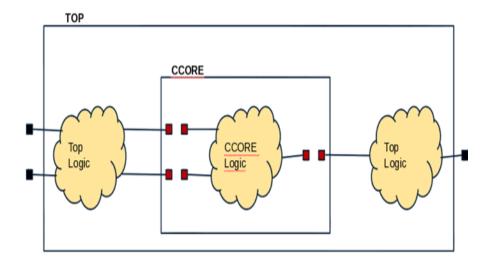

|          | 5.5  | Synthesis of CCORE in SLEC                   | 28 |

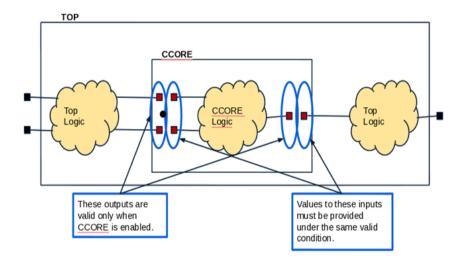

|          | 5.6  | Verification Strategy Of CCORE in SLEC       | 28 |

|          | 5.7  | SLEC setup details for CCORE                 | 30 |

|          | 5.8  | Problem statement                            | 30 |

|          | 5.9  | An introduction to Self_checks               | 30 |

|          | 5.10 | Algorithm for the problem                    | 30 |

### CONTENTS

|    | 5.11 Example                                           |  |  | • | • | • |  |   |   | • | 31 |

|----|--------------------------------------------------------|--|--|---|---|---|--|---|---|---|----|

|    | 5.12 Summary of the testing $\ldots$ $\ldots$ $\ldots$ |  |  | • | • | • |  | • |   | • | 33 |

| 6  | 6 Automation using PERL                                |  |  |   |   |   |  |   |   |   | 34 |

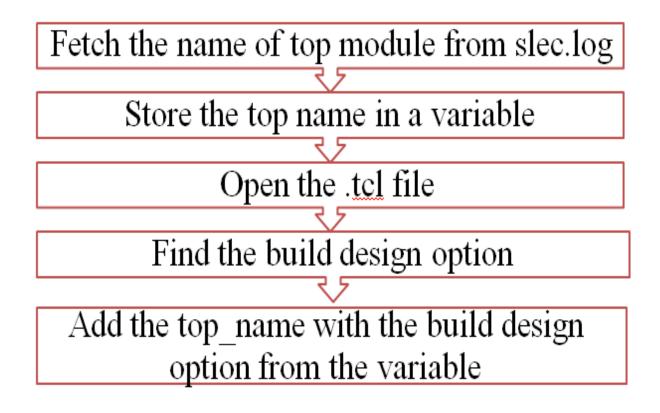

|    | 6.1 Adding the top_name feature                        |  |  | • | • |   |  |   | • | • | 34 |

|    | 6.1.1 problem statement                                |  |  | • | • |   |  |   |   | • | 34 |

|    | 6.1.2 Algorithm                                        |  |  | • | • |   |  |   |   | • | 34 |

|    | 6.2 Cleaning of skiplist                               |  |  | • | • | • |  |   | • | • | 35 |

| 7  | 7 Conclusion                                           |  |  |   |   |   |  |   |   |   | 36 |

| 8  | 8 Future Scope                                         |  |  |   |   |   |  |   |   |   | 37 |

| Bi | Bibliography                                           |  |  |   |   |   |  |   |   |   | 38 |

# List of Figures

| 2.1  | Formal Verification Using Equivalence Checking |

|------|------------------------------------------------|

| 3.1  | Overview Of SLEC [3]                           |

| 3.2  | Versions and usage of SLEC [2]                 |

| 3.3  | Basic Operation of SLEC [2]                    |

| 3.4  | Setup File [2]                                 |

| 3.5  | Sample design for the HLS flow                 |

| 3.6  | Input files                                    |

| 3.7  | Hierarchy step                                 |

| 3.8  | Library step                                   |

| 3.9  | Mapping step                                   |

| 3.10 | Architecture step                              |

| 3.11 | Resource step                                  |

| 3.12 | schedule step                                  |

| 4.1  | Design Example                                 |

| 4.2  | Algorithm For the problem                      |

| 5.1  | Implementation of CCORE functionality[4]       |

| 5.2  | Step 1 Cut at CCORE port boundaries [4]        |

| 5.3  | Step 2 Map CCORE port boundaries [4]           |

| 5.4  | snippet of a testcase                          |

| 5.5  | snippet of self_checks added for the testcase  |

| 6.1 | Algorithm 1 | For the problem | <br> |  | <br> |  |  |  | <br>• |  | 35 |

|-----|-------------|-----------------|------|--|------|--|--|--|-------|--|----|

# Chapter 1

# Introduction

## 1.1 Motivation

Verification has become an inseparable part of any design process. Formal Verification has several advantages as compared to classical verification methods. Any design if verified properly would reduce cost as well as ensure quality and time to market. Formal verification on the other hand is the widely used method in EDA(Electronic Design Automation) as it has various advantages as compared to classical simulation.

SLEC(Sequential Logic Equivalence Checker) is a formal verification tool which has several advantages as compared to traditional logic equivalence checker. SLEC uses formal verification techniques which leads to lower capacity issues, lesser power requirements and better coverage

## 1.2 Objective

Objective for the project:Formal Verification using SLEC can be distributed as follows:

• Formal verify two designs using Mentor's Catapult and SLEC.

The SLEC HLS flow uses two tools Mentor's Catapult and SLEC. C++ is given as input to Catapult and produces output as Register Transfer Level(RTL). The RTL and c++ code is formally verified by SLEC.

- Testing various features of SLEC HLS flow The SLEC HLS has various features such as pipelining, resource scheduling, resuabality.

- Validating the tool and reporting bugs whenever required.

If two designs do not prove to be formally equivalent then a falsification arrives.

The falsification exists because of two reasons. One of them is when design is not coded properly and the other is when the tool does not prove it inspite of being functionally equivalent . A bug is reported in such a case.

## **1.3** Requirements

To complete this project knowledge of formal verification tool that is Sequential Logic Equivalence checker (SLEC) ,High Level Synthesis(HLS) tool that is catapult .In addition to this knowledge of c++ as well as knowledge of scripting languages like PERL and TCL is required.

# Chapter 2

# An Introduction to Formal Verification

## 2.1 An Introduction to verification

Verification and validation are two words which are used interchangeably but technically they are quite different. Verification is the method of evaluating your design in every stage of its development in order to ensure a error free design at the end of the design process. While Validation refers to the evaluation of final design to ensure that it meets the specification and requirements. There are various kind of verification methodology such as:

- 1) Functional Verification

- 2) FPGA emulation

- 3) Assertion based verification

- 4) code coverage

- 5) Formal Verification

There are various other methods for verification.Formal Verification is more popular in HLS due to its numerous advantages. Verification is generally performed during the development of design. It ensures that the right design is being developed.Validation generally comes after verification and it ensures that the final product developed is right or not.[1]

# 2.2 Formal Verification

Formal Verification is a method to prove correctness of any algorithm using various mathematical modeling. Formal verification can be used in verification of digital circuits whether sequential or combinational as well as for software expressed as source code. Earlier simulation was a very widely used method for verification. However Formal verification has a variety of advantages as compared to classical simulation:

1)Improves verification quality

2)Reduces verification effort

3)Saves verification time since process is faster

4) code coverage is better

5)It does not require input vectors

There are two popular methods for formal verification:

1)Formal Equivalence Checking

2)Formal Property Checking [1]

### 2.2.1 Formal Equivalence Checking

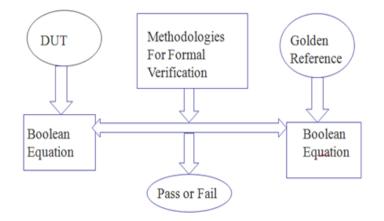

In the method of Formal Equivalence checking two designs are given as input and a output is produced by functional verification between two designs. In this method of formal verification Design Under Test(DUT) and golden reference are compared. They are reduced to boolean equations and then compared and output is produced.

Figure 2.1 shows the verification methodology for formal equivalence checking. There are two types of equivalence checking:

- 1) Combinational Equivalence Checking

- 2) Sequential Equivalence Checking

Figure 2.1: Formal Verification Using Equivalence Checking

• Combinational Equivalence Checking

In combinational checking one to one mapping of flops is done between two designs that is the golden design and Device Under Test(DUT).

• Sequential Equivalence Checking

In sequential checking two designs which are structurally different are compared without the use of one to one flop mapping.

There are variety of tools available for logic equivalence checking in field of EDA.Some of them are

- 1)FormalPro by Mentor Graphics

- 2)Conformal by Cadence'

- 3)Jasper Gold app by Cadence

- 4)Formality by Synopsys

- 5)SLEC by Calypto Design Systems(BU OF Mentor Graphics) [1]

# Chapter 3

# **Overview of SLEC**

## 3.1 Introduction to SLEC

SLEC stands for Sequential Logic Equivalence checker tool .It compares two designs - spec (specification) design and impl (implementation) design - to verify whether both designs are functionally equivalent or not. These designs may be at similar or different levels of abstraction. One of them may be be at abstraction or system level or RTL model and the other can be at RTL with deeper implementation.[2]

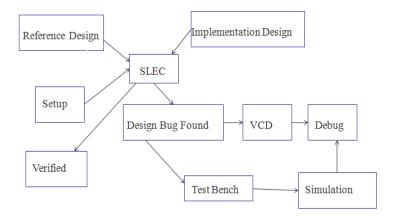

Figure 3.1: Overview Of SLEC [3]

SLEC provides:

- Formal Verification without the use of input test vectors.

- Generate Counter Example if designs are not functionally equivalent.

- Complex Bug Detection [2]

# 3.2 Advantages of SLEC

SLEC has several advantages as compared to other Logic Equivalence Checker.

- Easy and early detection of system-level and RTL functional bugs, without using test-benches.

- Reduces verification effort as there is no need for test-bench creation and modification

• Eliminates long simulation regressions and saves time

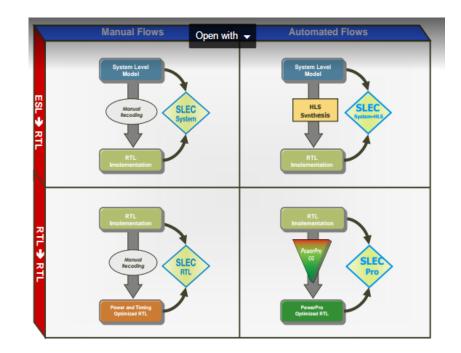

Figure 3.2: Versions and usage of SLEC [2]

### 3.3 Ability of SLEC

### 3.3.1 Equivalence Checking Compatibility

SLEC can perform equivalence checking between

- System-Level Models and manually created Register-Transfer Level (RTL) models.

- System-Level models and the RTL output produced by supported High-Level Synthesis (HLS) products such as Mentor Catapult.

- RTL models and the same RTL models with minor refinements in speed, area and power that may change their sequential behavior.

- RTL models and RTL models which have been optimized by various power optimization tools [2]

#### 3.3.2 Refinement Verification

- Resource Scheduling: whenever a design is refined or enhanced, resources are allocated and scheduled to implement functional behavior in order to meet the cost and performance targets. It may happen that a computation which was of single cycle in a design specification may become multi-cycled during the implementation, changing the timing of an interface.

- State Recoding: State machine encodings may be changed in order to achieve better and optimized implementation area, timing, and/or dynamic power. A state recoding which was binary encoded in the specification design may change to one-hot in the implementation design.

- Pipelining: Pipelines are often added to a design in order to improve throughput and performance. Pipeline refinements means inserting or modifying the number of pipeline stages in a design's data and control paths.

- Register Retiming: Register retiming is a common method of RTL optimization which is used to balance the amount of logic between flip-flops. Even if the state of both the RTL models are different, the interface behavior of the impl and spec designs are equal.

- Clock Gating: Clock gating is an optimization technique used to reduce dynamic power. Sequential changes can affect the design state, due to which the use of combinational equivalence checkers are prevented. SLEC can verify designs with sequential differences thus it can highlight errors which are caused due to clock gating and verify designs inspite of the differences in clock gating.

- Interface Refinements: whenever designs are refined, block interfaces may change to abstract data types. In order to preserve core functionality, interface protocols and timings may change.

- Additional Modes of Operation: An implementation design may have additional modes of operation as compared to the specification design. In order to verify High-level behaviors implementation inputs are constrained so that the additional modes of operation are disabled.[2]

### 3.3.3 Basic operation of SLEC

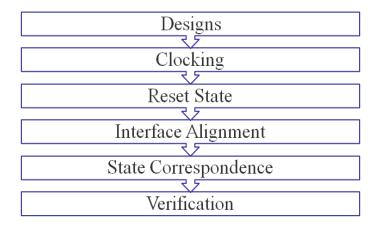

The inputs given to SLEC are specification design and implementation design.Both of them are formally verified. Figure 3.3 shows the basic steps involved:They are 1)Reading the designs 2)Providing clock to both the designs 3)providing reset states to both the designs 4)Providing Interface Alignment 5)State correspondence between both the designs 6)Finally verifying them[2]

Figure 3.3: Basic Operation of SLEC [2]

- Design: The two designs spec and impl are given as input and are read in. Portions of the designs such as large memories which cannot be analyzed by SLEC, must be black-boxed. The design files and libraries used for each design have to be specified by the user[2].

- Clocking: A clock has to be specified to achieve a common frame of reference for timing relationships between the two devices. SLEC supports one clock per design, however different phase of the clock can be used and the clock may be gated. For the cases where both of the designs has a single clock, no setup information has to be added for the spec and impl designs in the tcl file[2].

- Reset state:Reset states in any design are required to begin equivalence checking. This information can be provided in the .tcl file through explicit state values,reset sequences or VCD dumps.Normally reset values are generally set to zero[2].

- Interface Alignment: To verify the designs formally correspondence must be established between the design interfaces of spec and impl. If both the designs are cycle accurate that is they use same clock cycles for operation and even use matching names for input and output ports, all of this information can

be automatically interpreted. The Designs which have differences in timing, protocols, or data representation require additional setup information in the .tcl file. In that case the input and output ports in one design must be mapped to corresponding ports on the other design [2].

- State Correspondence: If the two designs have any common correspondence in state then it must be specified. This optional information helps SLEC in verification process. SLEC even tries to find as many state correspondences as possible between the two designs, before it attempts to prove the equivalence [2].

- Verification: The two designs can be verified using one of two modes: bug finding or full proof. Generally bug finding mode should is preferred to search for any functional differences between the designs. In this mode SLEC compares the designs over a bounded or fixed set of transactions. Full proof mode provides additional formal techniques which are to prove the designs equivalent which are not supported in the bug finding mode. If the designs are not equivalent, counterexamples are produced which demonstrate the differences. After SLEC completes its verification log files ,waveform files and test benches are generated for further analysis by the user [2].

## 3.4 Setup File

The operation of SLEC is controlled by a TCL command file. The command file provides problem setup information which identifies the designs and describes how the interface mappings and timings of the two designs should be compared. For equivalence checking, an instance of the top-level module of the specification design is named spec, while the comparable instance of the top-level module of the implementation design is named impl [2].

```

# Problem setup file for SLEC Tutorial.

# Designs

build_design -spec spec10.h

build_design -impl impl10.v

# Clocks

# Reset Constraints

# Input Constraints

# Timing

# I/O Mapping

# Verification

Verify

```

Figure 3.4: Setup File [2]

# 3.5 SLEC-HLS

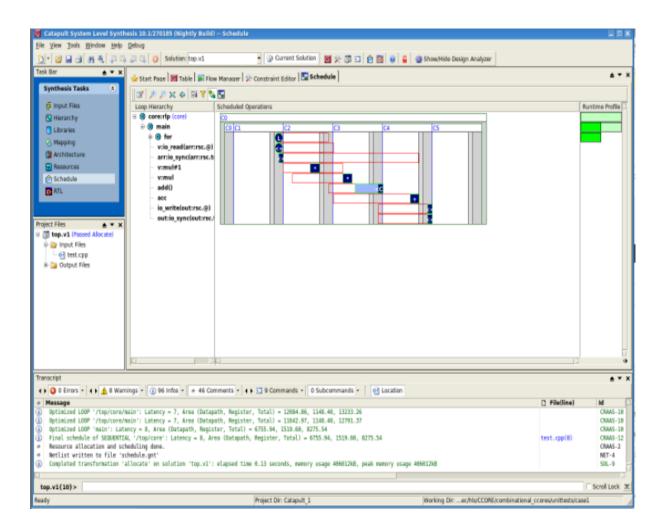

HLS stands for High Level Synthesis (HLS). HLS has the ability to generate production quality RTL implementation from high level abstraction languages like c and c++. In High level synthesis Algorithmic behavior written in C/C++ or System C is given as input to the HLS tool which then automatically synthesizes the algorithmic behavior to register transfer level (RTL) design. HLS maps top-level c++ variables to resources that would implement RTL. In this, resource synthesis is the process of mapping top-level C++ variables to resources that implement a RTL. Whenever an algorithm is converted into RTL with the help of HLS,various constraints such as scheduling has to be taken care with the hardware point of view. SLEC-HLS is verification of the RTL generated by the HLS tool Catapult. The two inputs given to SLEC-HLS are RTL generated by the HLS tool and the system level design in c or c++. The two designs are verified formally stating that they are functionally equivalent or not. This would verify that whether the RTL generated by the HLS tool catapult is functionally correct or not. If the two designs are not found equivalent a counter example is generated which can pinpont design bugs. The HLS flow of catapult is briefly described in the following stages: 1)Input Files 2)Hierarchy 3)Library 4)Mapping 5)Architecture 6)Resource

7)Generate RTL

### 3.5.1 SLEC-HLS Flow

This section would briefly describe the HLS flow used in SLEC The Input design for the SLEC HLS flow is shown in figure:

```

1 #pragma map_to_operator [CCORE]

2 int add(int x[8])

З

{

4

5

return (x[0] + x[1] + x[2]);

3

6

7 #pragma design top

8 void top(int arr[8],

int & out)

9 {

10

int temp = 0;

11

for ( int i = 0 ; i < 5 ; i++)</pre>

12

13

{

14

temp += arr[i];

}

15

16

temp += add( arr);

17

18

for ( int i = 5 ; i < 8 ; i++)</pre>

19

20

{

21

22

temp += arr[i];

}

23

out = temp;

24

25 }

```

Figure 3.5: Sample design for the HLS flow

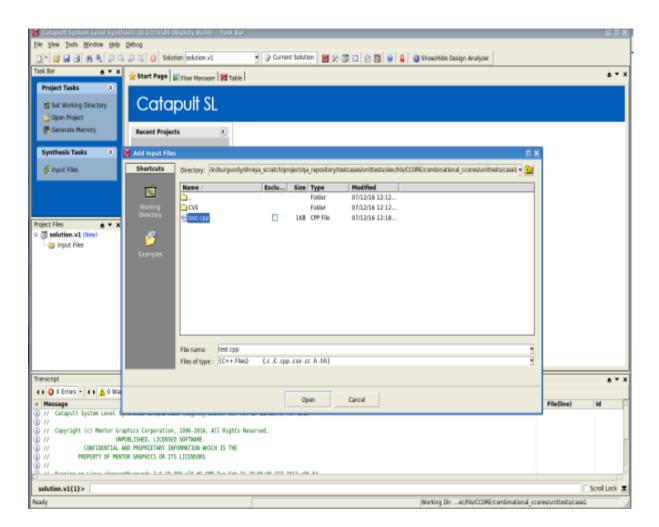

1) Input Files: This is the first step of the HLS flow. In this step the design file(c,c++ or system c) is given as input to the HLS tool. The following snippet depicts such a scenario:

Figure 3.6: Input files

2) Hierarchy: This step decides the hierarchy of the design. It would state which function would be the top level function and which functions will be the sub blocks.

| 🖁 Catapult System Level Synthe                              | esis 10.1/270185 (Nightly Build) Co  | nstraint Editor                             |                                                                                                                                             | _ = ×                      |                  |

|-------------------------------------------------------------|--------------------------------------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------|

| <u>Eile View T</u> ools <u>W</u> indow <u>H</u> elp !       | Debug                                |                                             |                                                                                                                                             |                            |                  |

| 🛅 • 📓 🖨 🗛 🚑 🐺 🕰                                             | Solution: solution.v1                | 🝷 🏠 Current Solution 🛛 📓 🎘                  | 🔟 🔯 🔯 😺 🔒 🤯 Show/Hide Design Analyzer                                                                                                       |                            |                  |

| Task Bar 🔺 🗙                                                | 🚽 Start Page 🛛 🛐 Flow Manager 🕅 🕅 Ta | shin & Constraint Editor                    |                                                                                                                                             | ≜ <del>-</del> x           |                  |

| Synthesis Tasks 🔹                                           | B e test.cpp                         |                                             |                                                                                                                                             |                            |                  |

|                                                             | int add(int, int, int)               | Function: void top(int *, int &)            |                                                                                                                                             |                            |                  |

| Input Files Hierarchy                                       | void top(int *, int &)               | Hierarchy Setting                           |                                                                                                                                             |                            |                  |

| C Libraries                                                 |                                      | O Inline                                    |                                                                                                                                             |                            |                  |

| U cibranes                                                  |                                      | Block                                       |                                                                                                                                             |                            |                  |

|                                                             |                                      | • Тор                                       |                                                                                                                                             |                            |                  |

|                                                             |                                      |                                             |                                                                                                                                             |                            |                  |

|                                                             |                                      |                                             |                                                                                                                                             |                            |                  |

|                                                             |                                      |                                             |                                                                                                                                             |                            |                  |

|                                                             |                                      |                                             |                                                                                                                                             |                            |                  |

|                                                             |                                      |                                             |                                                                                                                                             |                            |                  |

| oject Files ≜ ▼ X                                           |                                      |                                             |                                                                                                                                             |                            |                  |

| Solution.v1 (Passed Analyze                                 |                                      |                                             |                                                                                                                                             |                            |                  |

| eitest.cpp                                                  |                                      |                                             |                                                                                                                                             |                            |                  |

| 🖲 🃴 Output Files                                            |                                      |                                             |                                                                                                                                             |                            |                  |

|                                                             |                                      |                                             |                                                                                                                                             |                            |                  |

|                                                             |                                      |                                             |                                                                                                                                             |                            |                  |

|                                                             |                                      |                                             |                                                                                                                                             |                            |                  |

|                                                             |                                      |                                             |                                                                                                                                             |                            |                  |

|                                                             |                                      |                                             |                                                                                                                                             |                            |                  |

|                                                             |                                      | -                                           |                                                                                                                                             |                            |                  |

|                                                             |                                      | Settings Advanced                           |                                                                                                                                             | Apply Cancel 🔞             |                  |

|                                                             |                                      |                                             |                                                                                                                                             |                            |                  |

| anscript                                                    |                                      |                                             |                                                                                                                                             | ≜ <del>•</del> ×           |                  |

| 🕨 🕄 0 Errors 🝷 🚺 🏦 0 Warni                                  | ings • (i) 2 Infos • # 7 Comments    | A b 2 Commands - 0 Subcommands -            | G Location                                                                                                                                  |                            |                  |

| Message                                                     | n file "/in/hurgundu/shrava scratski | nniart/na rennsitory/testcases/unittorts/s  | lec/hls/CCORE/combinational ccores/unittests/case1/catapult.lo                                                                              | File(line) Id              |                  |

| Front End called with argume                                | ents: /in/burgundy/shreya_scratch    |                                             | <pre>slec/hls/CCORE/combinational_ccores/unittests/casel/tataputt.to<br/>slec/hls/CCORE/combinational_ccores/unittests/casel/test.cpp</pre> | CIN-69                     |                  |

| Edison Design Group C++/C Fr<br>Pragma 'hls design⇔' detect |                                      |                                             |                                                                                                                                             | CIN-1<br>test.cpp(1) CIN-6 |                  |

| Pragma 'hls_design <top>' det</top>                         | tected on routine 'top'              |                                             |                                                                                                                                             | test.cpp(7) CIN-6          |                  |

| Source file analysis complete                               |                                      | Janual Simo 8 62 controls manager - 2020    | 2010 reak serect uses 2010010                                                                                                               | CIN-68<br>S0L-9 —          |                  |

| ) Completed transformation 'ar                              | natyze on solution 'solution.vl': e  | lapsed time 0.03 seconds, memory usage 3925 | оокь, реак непогу usage зэдэөжв                                                                                                             | SUL-9                      |                  |

| solution.v1{3}>                                             |                                      |                                             |                                                                                                                                             | Scroll Lock 🕱              |                  |

| adv                                                         |                                      | Project Dir: Catapult 1                     | Working Dir:ec/hls/CCORE/combinational                                                                                                      |                            |                  |

|                                                             |                                      | roject bit. cataput_1                       | morking bit internatecontercombinational                                                                                                    | conception theory cases    | I                |

|                                                             |                                      |                                             |                                                                                                                                             |                            |                  |

|                                                             | project/qa_repository/testcases      | /unittests/slec/hls/CCORE/combinationa      | l_ccores/unittests/casel/test.cpp [POS=0001,0001][4%]                                                                                       | [LEN=22]                   |                  |

| test.cpp* 22L, 322C                                         |                                      |                                             |                                                                                                                                             |                            |                  |

| i 😔 🛎 🤤 f                                                   | 2 🖉 Shell No. 3 - K                  | onsole 🛛 👎 slec_user_manual.pdf - Ado 🕻     | Gvim [7] • 🗋 Pidgin [2] •                                                                                                                   |                            | 12<br>👔 📾 😡 Wedr |

| ( V) 🤛 😪 🖉 (                                                | 3 4 🔀 Catapult Syst                  | tem Level S 🎾 shreyap - Konqueror 🛛 🔞       | Firefox [2]                                                                                                                                 |                            | 2016             |

Figure 3.7: Hierarchy step

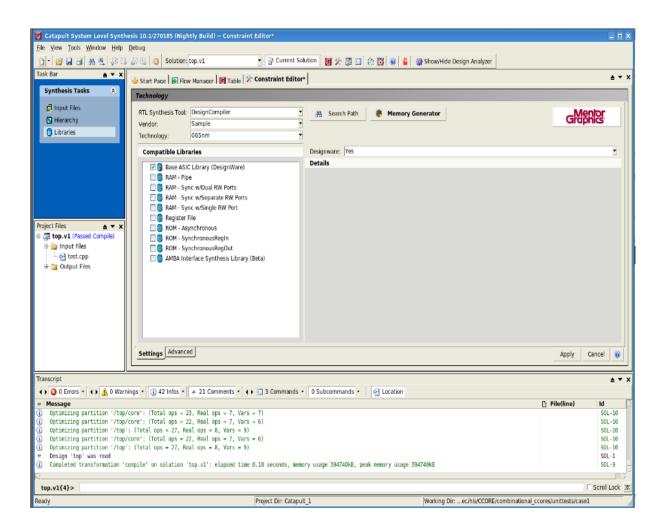

3) Libraries: This step of HLS provides us various options such as technology(65 or 90nm) that has to be used for the verification. It also gives various other options of design constraints such as synthesis tool, target hardware technology, compatible libraries and design hierarchy.

Figure 3.8: Library step

4)Mapping: This step of HLS is used to set clock, reset, enable and handshaking signals. It is also used to select process in HLS. It is also used to specify handshaking signals.

| 🖉 Catapuit System Level Synt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | hesis 10.1/270185 (Nightly Build) Co                                          | onstraint Editor*                    |                                                                                            | _ 0 X                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------|--------------------------------------------------------------------------------------------|----------------------------|

| Eile Yiew Tools Window Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                               |                                      |                                                                                            |                            |

| 💁 🖉 🖬 🗃 🗿 🖓 🖉 🖓 🖄                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                               | Garrent Solution                     | 🛿 🛠 🔞 🔟 👔 😨 🔒 🍘 Show,Hide Design Analyzer                                                  |                            |

| Task Bar 🔺 🗙 🛪                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 👍 Start Page 🖌 🖬 Flow Manager 🕅                                               | Table 🔀 Constraint Editor            |                                                                                            | ± <del>+</del> ×           |

| Synthesis Tasks 🛞                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Instance Hierarchy                                                            | Module                               | Process: core                                                                              |                            |

| o input Files                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 🗟 👩 Solution                                                                  | 🗟 🚺 top                              |                                                                                            |                            |

| Hierarchy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 🖶 💽 top                                                                       | - S core (clk)                       |                                                                                            |                            |

| Libraries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | add:inst                                                                      |                                      |                                                                                            |                            |

| Mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                               |                                      | ns 0.00 5.00 10.00 15.00 20.00                                                             |                            |

| C Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                               |                                      |                                                                                            |                            |

| Resources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                               |                                      | Process Clock: Clk                                                                         | -                          |

| 🖒 Schedule                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                               |                                      | Add Clock X Delete                                                                         | Rename                     |

| 👩 RTL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                               |                                      | Frequency:                                                                                 | 100 🔮 MHz                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                               |                                      | Period:                                                                                    | 10 🛫 ns                    |