## Hardware Based Implementation of CCSDS Formatted Data Packets

### Major Project Report

Submitted in partial fulfillment of the requirements

for the degree of

Master of Technology

in

**Electronics & Communication Engineering**

(Embedded Systems)

By

Princy Teli

(15 MECE30)

Electronics & Communication Engineering Department Institute of Technology Nirma University Ahmedabad-382481 May 2017

## Hardware Based Implementation of CCSDS Formatted Data Packets

#### Major Project Report

Submitted in partial fulfillment of the requirements

for the degree of

#### Master of Technology

$\mathbf{in}$

## Electronics & Communication Engineering

(Embedded Systems)

By

Princy Teli (15MECE30)

Under the guidance of

**External Project Guide:**

#### Mrs.Bela Vaidya

Scientist Engineer(SF),

SAC-ISRO,

Ahmedabad.

Internal Project Guide: Dr. N.P.Gajjar Professor, EC Department, Institute of Technology, Nirma University, Ahmedabad.

**Electronics & Communication Engineering Department**

Institute of Technology Nirma University Ahmedabad-382 481 May 2017

## Declaration

This is to certify that

- a. The thesis comprises my original work towards the degree of Master of Technology in Embedded Systems at Nirma University and has not been submitted elsewhere for a degree.

- b. Due acknowledgment has been made in the text to all other material used.

- Princy Teli 15MECE30

## Disclaimer

"The content of this thesis does not represent the technology, opinions, beliefs, or positions of SAC-ISRO, its employees, vendors, customers, or associates."

## Certificate

This is to certify that the Major Project entitled "Hardware based Implementation of CCSDS Formatted Data Packets" submitted by Princy Teli (15MECE30), towards the partial fulfillment of the requirements for the degree of Master of Technology in Embedded Systems, Nirma University, Ahmedabad is the record of work carried out by her under our supervision and guidance. In our opinion, the submitted work has reached a level required for being accepted for examination. The results embodied in this major project, to the best of our knowledge, haven't been submitted to any other university or institution for award of any degree or diploma.

Date:

Place: Ahmedabad

Dr. N.P.Gajjar

Internal Guide

Program Coordinator

Dr. D.K.Kothari Head, EC **Dr. Alka Mahajan** Director, IT

## Certificate

This is to certify that the Major Project entitled "Hardware Based Implementation of CCSDS Formatted Data Packets" submitted by Princy Teli (15MECE30), towards the partial fulfillment of the requirements for the degree of Master of Technology in Embedded Systems, Nirma University, Ahmedabad is the record of work carried out by her under our supervision and guidance. In our opinion, the submitted work has reached a level required for being accepted for examination.

> Mrs. Bela Vaidya Scientist Engineering(SF), SAC-ISRO, Ahmedabad

### Acknowledgements

I would like to express my gratitude and sincere thanks to **Dr. Alka Mahajan**, Director, Institute of Technology **Dr. Dilip Kothari** Professor and Head of Electronics and Communication Engineering Department, and PG Coordinator of M.Tech Embedded Systems program for allowing me to undertake this thesis work and for his guidelines during the review process.

I take this opportunity to express my profound gratitude and deep regards towards **Dr. N.P.Gajjar**, guide of my major project for his exemplary guidance, monitoring and constant encouragement throughout the course of this thesis. The blessing, help, and guidance given by him time to time shall carry me a long way in the journey of life on which I am about to embark. I heartily express my gratitude to the management and staff of Space Applications Centre, ISRO, Ahmedabad, for providing the most compatible environment for working along with the bonus of information about a very dynamic field of their latest works and providing their valuable resources for the implementation of Project work. I would like to thank, **Mr. D.R. Goswami** (Group Director, PCEG) and **Mr. Ashish Mishra** (Head), for their motivation and support throughout the course of project work at the PCSVD-PCEG-SEDA, SAC. I particularly record my profound gratitude to **Mrs. Bela Vaidya**, my project guide for her proficient and enthusiastic guidance, for always helping, giving me good suggestions, solving my doubts and guide me to complete my project in a better way.

Lastly, I thank almighty, my parents, brother and friends for their constant encouragement without which this assignment would not be possible.

> - Princy Teli 15MECE30

#### Abstract

In the field of satellite-based Data Reception, two major parameters, rate, and quality of data transmission are required to meet standard. CCSDS (Consultative Committee for Space Data System) is a protocol for satellite Data Communication. CCSDS standard allows configuring the rate and quality of data transmission across various platforms of a satellite. It defines the implementation for data exchange, in addition to facilitate interoperability between satellites as well as the satellite to ground station.In order to support CCSDS in ground segment, the overall requirement can be split into two broad categories, namely (1) Real Time Data Acquisition and (2) CCSDS Prescribed Processing.

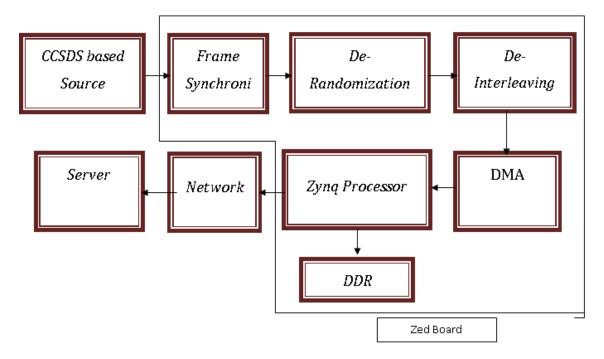

The project is targeted to implement the CCSDS protocol in the ground segment using the FPGA-based real-time platform at 50 MHz. CCSDS processing typically comprises of Attach Sync Marker, Randomization and Reed-Solomon(RS) Encoding at the transmitter side and the Frame Synchronization, De-randomization and the Reed-Solomon Decoding and the Data acquisition System at the receiver side. The Real Time data Acquisition is continuous DMA(Direct Memory Access) of decoded data of satellite and sustained transfer to the host. Here the blocks of CCSDS at transmitter and receiver side are designed, simulated and implemented using VHDL. The hardware platform used is Xilinx based Zynq Soc (Z7020) and the simulation is carried out using Xilinx VIVADO. The real-time data acquisition system is implemented using the built-in ARM core of Zynq.

The testing of Transmitter side is carried out by implementation of ramp pattern of 50 MHz. It is given as an input of RS encoder and generates the parities for error correction of transmitted signal. At the receiver side encoded data is given as an input of decoder. For the testing of data acquisition system AXI IP of Ramp generator is implemented and that is given as input of AXI DMA.

## Contents

| Declaration                            |  |  |   |   |  |  |     | iii  |

|----------------------------------------|--|--|---|---|--|--|-----|------|

| Disclaimer                             |  |  |   |   |  |  |     | iv   |

| Certificate                            |  |  |   |   |  |  |     | v    |

| Certificate                            |  |  |   |   |  |  |     | vi   |

| Acknowledgements                       |  |  |   |   |  |  |     | vii  |

| Abstract                               |  |  |   |   |  |  |     | viii |

| List of Figures xi                     |  |  |   |   |  |  | xiv |      |

| List of Tables                         |  |  |   |   |  |  |     | xv   |

| Abbreviation Notation and Nomenclature |  |  |   |   |  |  |     | xvi  |

| 1 Introduction                         |  |  |   |   |  |  |     | 1    |

| 1.1 Motivation                         |  |  | • | • |  |  | •   | 1    |

| 1.2 Objective                          |  |  |   | • |  |  | •   | 1    |

| 1.3 Scope                              |  |  | • | • |  |  | •   | 2    |

| 1.4 Requirements                       |  |  |   | • |  |  | •   | 2    |

| 1.5 Thesis Organization                |  |  |   |   |  |  |     | 2    |

| <b>2</b> | Lite                                                                                                                                         | erature                                                                                                | e Review                                                                                                                                                                                                                                                                                                                                          | 4                                                                                              |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

|          | 2.1                                                                                                                                          | CCSE                                                                                                   | S Standard                                                                                                                                                                                                                                                                                                                                        | 4                                                                                              |

|          |                                                                                                                                              | 2.1.1                                                                                                  | CCSDS Specified Data Transmission Process                                                                                                                                                                                                                                                                                                         | 5                                                                                              |

|          |                                                                                                                                              | 2.1.2                                                                                                  | CCSDS Specified Data Reception Process                                                                                                                                                                                                                                                                                                            | 7                                                                                              |

|          | 2.2                                                                                                                                          | Tools                                                                                                  | and Technology                                                                                                                                                                                                                                                                                                                                    | 8                                                                                              |

|          |                                                                                                                                              | 2.2.1                                                                                                  | Processing System                                                                                                                                                                                                                                                                                                                                 | 9                                                                                              |

|          |                                                                                                                                              | 2.2.2                                                                                                  | Processing System External Interface                                                                                                                                                                                                                                                                                                              | 10                                                                                             |

|          |                                                                                                                                              | 2.2.3                                                                                                  | Programmable Logic                                                                                                                                                                                                                                                                                                                                | 10                                                                                             |

|          |                                                                                                                                              | 2.2.4                                                                                                  | Special Resources                                                                                                                                                                                                                                                                                                                                 | 11                                                                                             |

|          |                                                                                                                                              | 2.2.5                                                                                                  | Programmable Logic External Interfaces                                                                                                                                                                                                                                                                                                            | 12                                                                                             |

|          | 2.3                                                                                                                                          | Vivad                                                                                                  | o IDE                                                                                                                                                                                                                                                                                                                                             | 12                                                                                             |

|          |                                                                                                                                              | 2.3.1                                                                                                  | Vivado Design Flow for Zynq                                                                                                                                                                                                                                                                                                                       | 12                                                                                             |

|          |                                                                                                                                              | 2.3.2                                                                                                  | System Setup and Requirements                                                                                                                                                                                                                                                                                                                     | 15                                                                                             |

|          |                                                                                                                                              | 2.3.3                                                                                                  | An Outline of the Design Flow                                                                                                                                                                                                                                                                                                                     | 16                                                                                             |

|          |                                                                                                                                              |                                                                                                        |                                                                                                                                                                                                                                                                                                                                                   |                                                                                                |

| 3        | Des                                                                                                                                          | sign an                                                                                                | d Implementation of FPGA-Based CCSDS Specified Base                                                                                                                                                                                                                                                                                               | -                                                                                              |

| 3        |                                                                                                                                              | U                                                                                                      | d Implementation of FPGA-Based CCSDS Specified Base<br>FA Simulator                                                                                                                                                                                                                                                                               | -<br>17                                                                                        |

| 3        |                                                                                                                                              | d DA                                                                                                   |                                                                                                                                                                                                                                                                                                                                                   | 17                                                                                             |

| 3        | ban                                                                                                                                          | d DA                                                                                                   | TA Simulator                                                                                                                                                                                                                                                                                                                                      | <b>17</b><br>17                                                                                |

| 3        | <b>ban</b><br>3.1                                                                                                                            | d <b>DA</b><br>Introc<br>Synch                                                                         | <b>FA Simulator</b><br>luction                                                                                                                                                                                                                                                                                                                    | 17<br>17<br>18                                                                                 |

| 3        | <b>ban</b><br>3.1<br>3.2                                                                                                                     | d DAT<br>Introd<br>Synch<br>Pseud                                                                      | <b>FA Simulator</b><br>luction                                                                                                                                                                                                                                                                                                                    | 17<br>17<br>18<br>18                                                                           |

| 3        | <ul> <li>ban</li> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> </ul>                                                                  | Introd<br>Synch<br>Pseud<br>RS-Er                                                                      | <b>FA Simulator</b> luction         nonization         o Random Sequence Generator                                                                                                                                                                                                                                                                | <ol> <li>17</li> <li>17</li> <li>18</li> <li>18</li> <li>20</li> </ol>                         |

| 3        | <ul> <li>ban</li> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> </ul>                                                                  | d DAT<br>Introd<br>Synch<br>Pseud<br>RS-Er<br>Hard                                                     | <b>FA Simulator</b> luction         nonization         o Random Sequence Generator         ncoding Algorithm                                                                                                                                                                                                                                      | <ol> <li>17</li> <li>18</li> <li>20</li> <li>25</li> </ol>                                     |

| 3        | <ul> <li>ban</li> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> </ul>                                                     | d DAT<br>Introd<br>Synch<br>Pseud<br>RS-Er<br>Hard<br>Schem                                            | <b>TA Simulator</b> luction         nonization         o Random Sequence Generator         ncoding Algorithm         ware Implementation in Xilinx FPGA using VHDL                                                                                                                                                                                | <ol> <li>17</li> <li>18</li> <li>20</li> <li>25</li> <li>26</li> </ol>                         |

| 3        | <ul> <li>ban</li> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> <li>3.6</li> <li>3.7</li> </ul>                           | d DAT<br>Introd<br>Synch<br>Pseud<br>RS-Er<br>Hard<br>Schem<br>Device                                  | <b>FA Simulator</b> luction         luction         ronization         co Random Sequence Generator         ncoding Algorithm         ware Implementation in Xilinx FPGA using VHDL         natic View                                                                                                                                            | <ol> <li>17</li> <li>17</li> <li>18</li> <li>20</li> <li>25</li> <li>26</li> <li>27</li> </ol> |

|          | <ul> <li>ban</li> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> <li>3.6</li> <li>3.7</li> <li>Imp</li> </ul>              | d DAT<br>Introd<br>Synch<br>Pseud<br>RS-Er<br>Hard<br>Schem<br>Device                                  | <b>FA Simulator</b> luction         luction         ronization         o Random Sequence Generator         ncoding Algorithm         ware Implementation in Xilinx FPGA using VHDL         natic View         e Utilization         utation of FPGA-Based CCSDS Specified Baseband Data                                                           | 17<br>17<br>18<br>18<br>20<br>25<br>26<br>27                                                   |

|          | <ul> <li>ban</li> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> <li>3.6</li> <li>3.7</li> <li>Imp</li> </ul>              | d DAT<br>Introd<br>Synch<br>Pseud<br>RS-Er<br>Hard<br>Schem<br>Device                                  | <b>FA Simulator</b> luction         luction         ronization         o Random Sequence Generator         ncoding Algorithm         ware Implementation in Xilinx FPGA using VHDL         natic View         e Utilization         utation of FPGA-Based CCSDS Specified Baseband Data                                                           | 17<br>17<br>18<br>20<br>25<br>26<br>27<br>28                                                   |

|          | <ul> <li>ban</li> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> <li>3.6</li> <li>3.7</li> <li>Imp</li> <li>Pro</li> </ul> | ad DAT<br>Introd<br>Synch<br>Pseud<br>RS-En<br>Hard<br>Schem<br>Device<br>olemen<br>ocessing<br>Introd | <b>FA Simulator</b> luction         luction         ronization         co Random Sequence Generator         ncoding Algorithm         incoding Algorithm         ware Implementation in Xilinx FPGA using VHDL         natic View         e Utilization         utilization         etation of FPGA-Based CCSDS Specified Baseband Data         g | <ol> <li>17</li> <li>17</li> <li>18</li> <li>20</li> <li>25</li> <li>26</li> <li>27</li> </ol> |

|          | 4.4                  | RS-Decoding Algorithm                                                  | 30 |

|----------|----------------------|------------------------------------------------------------------------|----|

|          | 4.5                  | Hardware Implementation in Xilinx FPGA using VHDL $\ . \ . \ . \ .$    | 38 |

|          | 4.6                  | Schematic View                                                         | 40 |

|          | 4.7                  | Device Utilization                                                     | 42 |

| <b>5</b> | Har                  | rdware Based Data Acquisition System                                   | 43 |

|          | 5.1                  | Introduction                                                           | 43 |

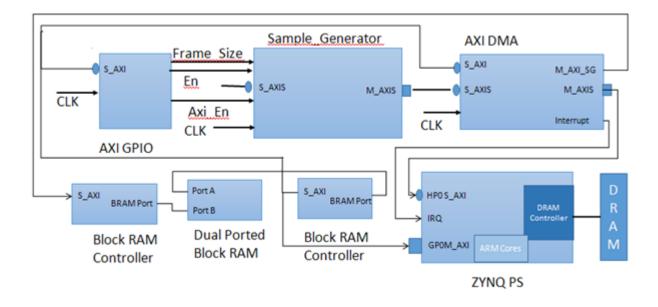

|          | 5.2                  | Embedded Hardware Design and Interface with Zynq Processor $\ . \ .$ . | 45 |

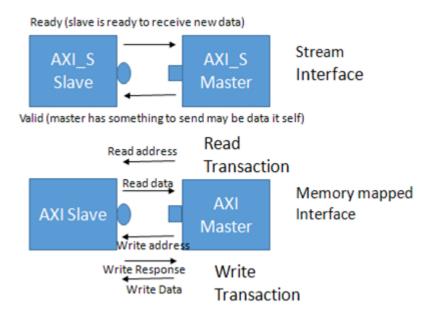

|          |                      | 5.2.1 AXI Standard                                                     | 45 |

|          |                      | 5.2.2 AXI DMA                                                          | 47 |

| 6        | Des                  | sign Implementation of Data Acquisition System                         | 50 |

|          | 6.1                  | DMA in Direct Register Mode                                            | 50 |

|          |                      | 6.1.1 Programmin Sequence for booting the linux with our hardware      |    |

|          |                      | on Zynq Processor                                                      | 51 |

|          |                      | 6.1.2 Programming Sequence for DMA in Direct Register Mode             | 52 |

|          | 6.2                  | DMA in Scatter Gather Mode                                             | 54 |

|          |                      | 6.2.1 Programming Sequence for DMA in Scatter Gather Mode $\therefore$ | 54 |

| 7        | $\operatorname{Res}$ | sults                                                                  | 57 |

|          | 7.1                  | Results for Data Transmission Process                                  | 57 |

|          |                      | 7.1.1 Simulation Results                                               | 57 |

|          |                      | 7.1.2 Implementation Results                                           | 59 |

|          | 7.2                  | Results for Data Reception Process                                     | 61 |

|          |                      | 7.2.1 Simulation Results                                               | 61 |

|          | 7.3                  | Results for Data Acquisition System                                    | 62 |

|          |                      | 7.3.1 Results for DMA in Direct Register mode                          | 62 |

|          |                      | 7.3.2 Results for DMA in Scatter-Gather mode                           | 64 |

| 8        | Cor                  | nclusion and Future Scope                                              | 65 |

|          | 8.1                  | Conclusion                                                             | 65 |

| 8.2     | Future Scope | <br> | <br> | <br> | • | <br>• |  | • | • | • |  | • |  | • | • | 65 |

|---------|--------------|------|------|------|---|-------|--|---|---|---|--|---|--|---|---|----|

| Bibliog | graphy       |      |      |      |   |       |  |   |   |   |  |   |  |   |   | 66 |

## List of Figures

| 2.1 | Data Transmission and Reception Process[1]                                              | 5  |

|-----|-----------------------------------------------------------------------------------------|----|

| 2.2 | Frame Generation                                                                        | 6  |

| 2.3 | $Frame \ Format[1]  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $    | 7  |

| 2.4 | Zynq Architecture[2]                                                                    | 9  |

| 2.5 | Vivado Design Flow[3]                                                                   | 13 |

| 2.6 | System Setup[3]                                                                         | 15 |

| 2.7 | Design Flow [3] $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 16 |

| 3.1 | Block diagram of Pseudo Random Sequence Generator[1] $\ldots$                           | 19 |

| 3.2 | Reed-Solomon Encoder Block Diagram                                                      | 21 |

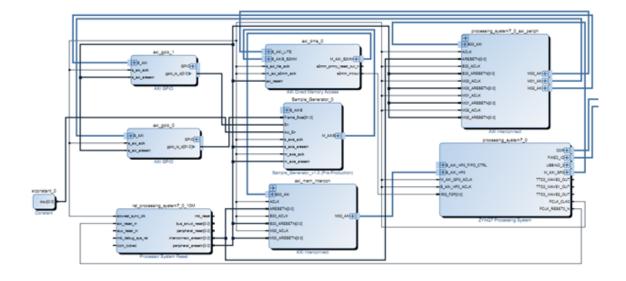

| 3.3 | RTL View for Data Transmission Process                                                  | 27 |

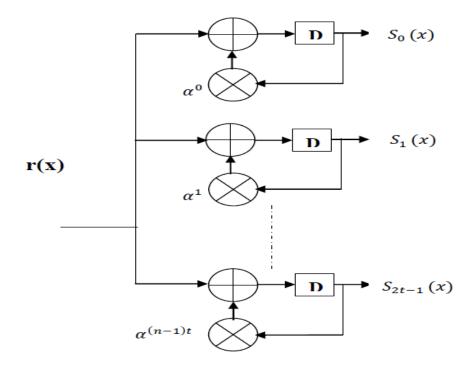

| 4.1 | Block Diagram of Syndrome Generation[5]                                                 | 31 |

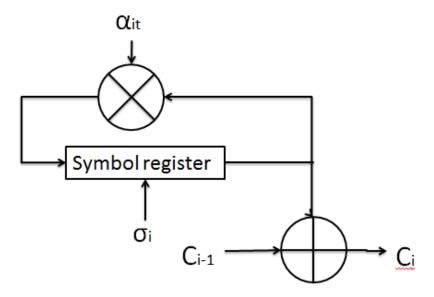

| 4.2 | Block Diagram of Chain Search[5]                                                        | 34 |

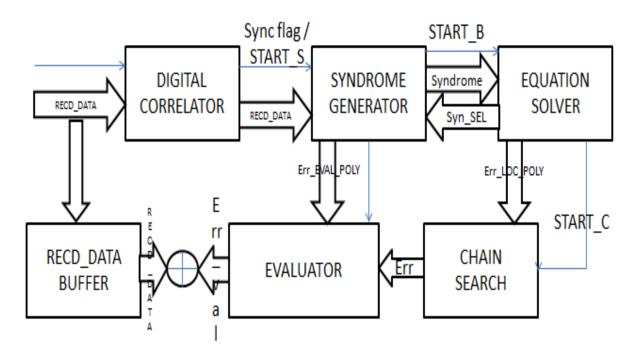

| 4.3 | Block Diagram of Data Reception Process                                                 | 38 |

| 4.4 | Schematic View for Data Reception Process                                               | 41 |

| 4.5 | Schematic View for Data Reception Process                                               | 41 |

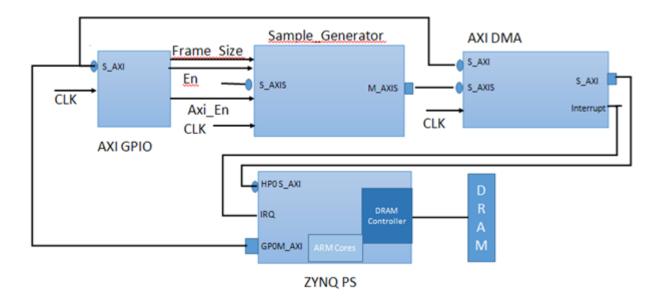

| 5.1 | Block diagram                                                                           | 44 |

| 5.2 | AXI Signal for Transaction                                                              | 47 |

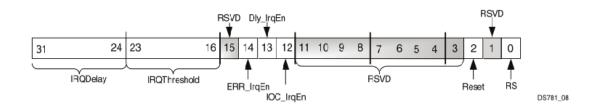

| 5.3 | DMA Controlled Register in Direct Register $Mode[11]$                                   | 48 |

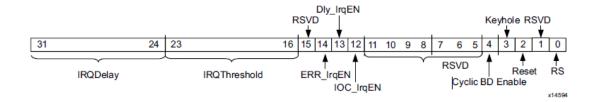

| 5.4 | DMA Controlled Register in Scatter Gather $Mode[11]$                                    | 49 |

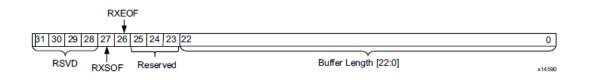

| 5.5 | Controlled Register for Scatter Gather Discriptor[11]                                   | 49 |

| 6.1  | Generalized Block diagram for DMA in Direct Register Mode                      | 51 |

|------|--------------------------------------------------------------------------------|----|

| 6.2  | Implementation Block Diagram for DMA in Direct Register Mode                   | 53 |

| 6.3  | Generalized Block Diagram for DMA in Scatter Gather Mode $\ . \ . \ .$         | 54 |

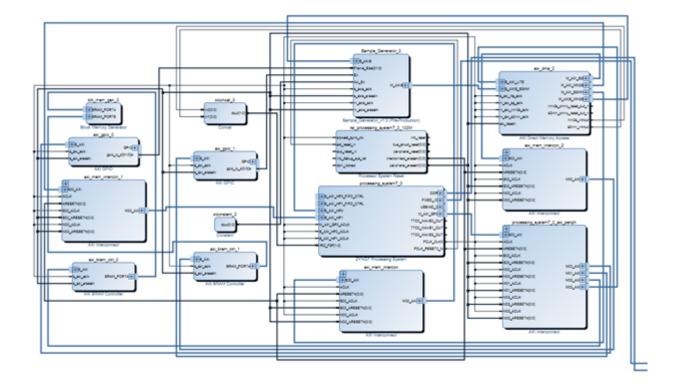

| 6.4  | Implementation Block Diagram for DMA in Scatter Gather Mode                    | 56 |

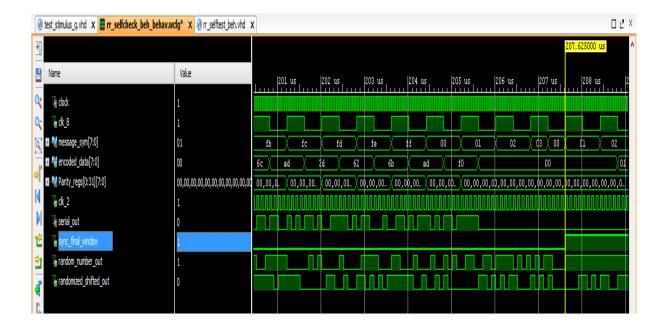

| 7.1  | Simulation Result for Data Transmission Process at the start of packet         | 57 |

| 7.2  | Simulation Result for Data Transmission Process at the end of the              |    |

|      | Packet                                                                         | 58 |

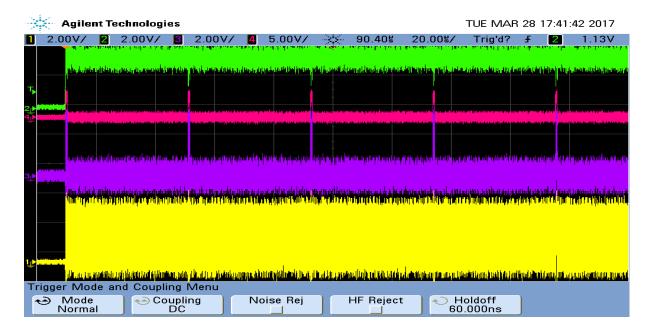

| 7.3  | Implementation Result of continuous data transmission                          | 59 |

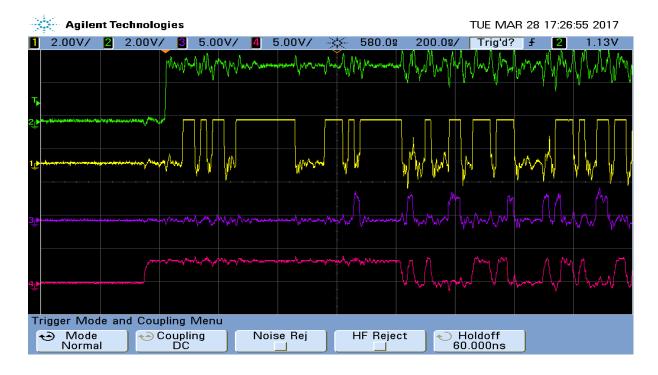

| 7.4  | Implementation Result at the start of the Packet $\ldots \ldots \ldots \ldots$ | 60 |

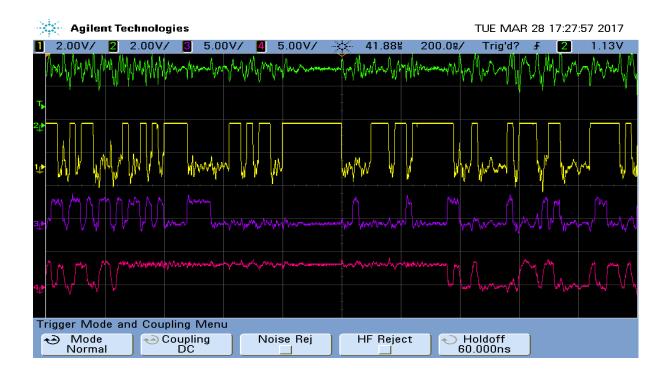

| 7.5  | Implementation Result at the end of the packet                                 | 60 |

| 7.6  | Simulation Results of Data Decoding Procedure                                  | 61 |

| 7.7  | Simulation Results of Final Decoded Data                                       | 62 |

| 7.8  | Transferred data with destination address at the start of frame                | 63 |

| 7.9  | Transferred data with destination address at the end of frame $\ldots$ .       | 63 |

| 7.10 | Transferred Data from the DMA in scatter-gather mode                           | 64 |

## List of Tables

| 3.1 | Step to Step Procedure of encoder with respect to clock | 24 |

|-----|---------------------------------------------------------|----|

| 3.2 | Device Utilization                                      | 27 |

| 4.1 | Device Utilization                                      | 42 |

## Abbreviation Notation and Nomenclature

| ARM     | Advanced RISC Machines                       |

|---------|----------------------------------------------|

| ASM     | Attached Sync Marker                         |

| AXI     | Amba Extensible Interface                    |

| BUFG    | Global Buffer                                |

| CAN     | Controller Area Network                      |

| CCSDS   | Consultative Committee for space Data System |

| DMA     | Direct Memory Access                         |

| ELF     | Executable and Linking Format                |

| FF      | Flip Flop                                    |

| FPGA    |                                              |

| GPIO    | General Purpose Input Output                 |

| I2C     | Inter Integrated Circuit                     |

| IDE     | Integrated Development Environment           |

| IO      | Input Output                                 |

| JTAG    | Joint Test Action Group                      |

| LDPC    | Low Density Parity Checker                   |

| LUT     | Look Up Table                                |

| LUTRAM  | Look Up Table based Random Access Memory     |

| PL      | Programmable Logic                           |

| PRBS    | Pseudo Random Binary Sequence                |

| PS      |                                              |

| RS      | Reed Solomon                                 |

| SD Card | Secure Digital Secure Digital                |

| SDK     | Software Development Kit                     |

| SoC     | System on Chip                               |

| SPI     | Serial Peripheral Interface                  |

| VHDL    |                                              |

| VHSIC    | Very High Scale Integrated Circuit         |

|----------|--------------------------------------------|

| UARTU    | niversal Asynchronous receiver Transmitter |

| USB      | Universal Serial Bus                       |

| ZedBoard | . Zynq Evaluation and Development Board    |

## Chapter 1

## Introduction

## 1.1 Motivation

In recent times the number of Electro-Optical Imaging Sensors being developed by ISRO has gone up substantially. Traditionally, the interfaces and formats related to data were specific to different payloads. However, in order to meet shorter turnaround time ISRO is adopting CCSDS standards. Data Acquisition and Testing are extremely crucial activities in the process of sensor development.

So I have taken up the development of the real-time data acquisition system of CCSDS formatted data streams, and the CCSDS Prescribed Processing that may contribute to the development of future sensors being developed in ISRO.

### 1.2 Objective

The prime objective is the study of CCSDS standard and its implementation for payload data acquisition and processing in Real time. While there can be different implementations, one of them can be a solution comprising of FPGA and Microcontroller. To develop this type of an application, I need a development board, which has FPGA and processor preferably, on a single platform. Xilinx Zedboard is one such platform, which can fulfill this requirement and to develop an application, it also provides a Xilinx Vivado IDE. So my second objective is to study the Zynq platform and Vivado design suite and finally to develop and deliver a working solution, meeting the above objectives.

### 1.3 Scope

This project can be used as a real-time high-speed data reception system of the satellite. It can do data decoding and acquisition of the real-time data.

## 1.4 Requirements

Requirements are

- Knowledge of Windows and Linux Platform

- Xilinx Vivado IDE

- Each Device on Zynq Soc and Device Functionality

- Knowledge of C Language

- VHDL Programming

- Knowledge of FPGA

- Xilinx Software Development Kit

- Visual Studio

## 1.5 Thesis Organization

The rest of the thesis organized as follows.

**Chapter 1** contains Motivation, Objective and the scope of the project also including the requirements for the project.

**Chapter 2** describes Literature review part, and the background study of the CCSDS standard, Frame Formation in data transmission and reception process, basic tools, technologies and hardware used in the data acquisition systems.

**Chapter 3** describes the Design and Implementation of CCSDS specified baseband data simulator with the brief description of all the processing blocks and algorithm applied on the actual data to transmit also including the simulation and the implementation results.

**Chapter 4** describes the Design and Implementation of CCSDS specified baseband data processing with the brief description of all the processing blocks and the algorithm applied to the received data to decode also including the simulation results.

**Chapter 5** describes the interface and the hardware used of the data acquisition system. It includes the description of DMA registers for the specific length of data transfer says direct register mode of DMA and also includes the scatter-gather mode of DMA for continuous data transfer.

Chapter 6 describes the hardware implementation for the data transfer, Processing sequence and test results.

Chapter 7 contains conclusion and future scope of the project.

## Chapter 2

## Literature Review

### 2.1 CCSDS Standard

The Consultative Committee for Space Data System(CCSDS) has published a set of standards for reliable space communication, which have been accepted worldwide. The purpose of this proposed standard is to specify synchronization and channel coding schemes used with telemetry space data link protocol[1]. The recommended standard proposed a packetized transmission scheme which provides the specification in synchronization and channel coding scheme in terms of the data formats and procedures. Standard provides the functions like frame synchronization, pseudo-randomization, and channel coding scheme to enable a reliable data transfer through space link[1]. It provides additional functionality necessary for transferring data packets over a space link[1].

The CCSDS proposed standard provides frame synchronization using a sync marker. It specifies a pseudo randomization to improve data reception using a random number generator[1]. And give an optional Reed-Solomon error correction codes to provide noise immunity[1].

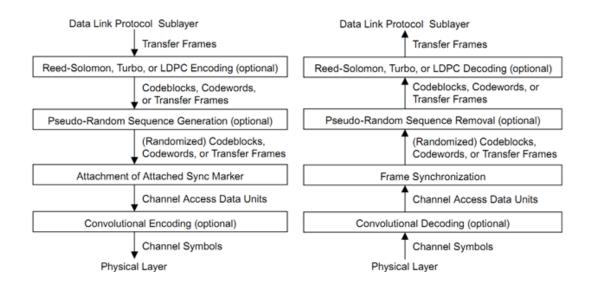

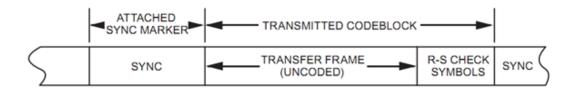

Figure 2.1 shows the layers of the data transmission and the reception process. At the transmitter side how the data formatted and the at the reception side how it will be decoded. Figure 2.2 shows how the frame generation of this layered architecture implemented practically using a multiplexer. And Figure 2.3 shows the location of frame sync, actual data and the parities for the error correction of transfer frame in every data frame.

Figure 2.1: Data Transmission and Reception Process[1]

#### 2.1.1 CCSDS Specified Data Transmission Process

#### Attached Sync Marker

Frame synchronization is necessary for proper decoding and subsequent processing of the Transfer Frames[1]. Furthermore, it is necessary for synchronization of the pseudo-random generator. The data unit consists of the ASM and the Transfer Frame[1]. The Transfer Frame, Codeword, may or may not be randomized. The ASM shall immediately follow the end of the preceding codeword[1].

#### **Pseudo-Randomizer**

In order for the receiver system to work properly, every data capture system at the receiving end requires that the incoming signal have sufficient bit transition density

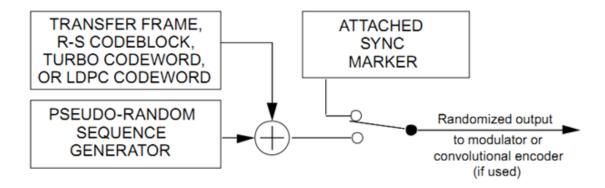

Figure 2.2: Frame Generation

[1]

and allow proper synchronization of the decoder[1]. In order to ensure proper receiver operation, the data stream must be sufficiently random[1].

The Pseudo-Randomizer defines the preferred method to ensure sufficient randomness for all combinations of CCSDS recommended modulation and coding schemes[1]. The presence or absence of pseudo-randomization is fixed for a Physical Channel and is managed by the receiver. Transfer Frame shall be randomized by exclusive-Oring the first bit of the Transfer Frame with the first bit of the pseudo-random sequence, followed by the second bit of the Transfer Frame with the second bit of the pseudorandom sequence, and so on[1]. On the receiving end, the original Transfer Frame shall be reconstructed using the same pseudorandom sequence[1].

#### **Reed-Solomon Encoding**

With the Reed-Solomon Codes specified only certain specific lengths of Transfer Frames may be contained within the codewords data space[1]. In some cases, these lengths can be shortened at a small sacrifice in coding gain. Since these R-S codes have a symbol length of 8 bits, the length of the codeword is a multiple of the interleaving depth, which provides octet compatibility[1]. The Reed-Solomon encoder reads in k data symbols, computes the (n - k) parity symbols, and appends the parity

Figure 2.3: Frame Format[1]

symbols to the k data symbols for a total of n symbols. The encoder is essentially a 2t tap shift register where each register is m bits wide.

#### 2.1.2 CCSDS Specified Data Reception Process

#### Synchronization

Codeblock synchronization of the Reed-Solomon decoder is achieved by Synchronization of the Attached Sync Marker associated with each code block [1].

#### **De-Randomizer**

At the receiving end, the original Frame is reconstructed using the same pseudo random sequence. After locating the ASM in the received data stream, the pseudorandom sequence is exclusive-ORed with the data bits immediately following the ASM[1]. The pseudorandom sequence is applied by exclusive-Oring the first bit following the ASM with the first bit of the pseudo-random sequence, followed by the second bit of the data stream with the second bit of the pseudo-random sequence, and so on[1].

#### **RS-Decoder**

The Reed-Solomon decoder tries to correct errors and/or erasures by calculating the syndromes for each codeword. Based upon the syndromes, the decoder is able to determine the number of errors in the received block[6, 8]. If there are errors present, the decoder tries to find the locations of the errors using the Berlekamp-Massey algorithm by creating an error locator polynomial. The roots of this polynomial are found using the Chien search algorithm. Using Forney's algorithm, the symbol error values are found and corrected. For an RS (n, k) code where n - k = 2T, the decoder can correct up to T symbol errors in the code word. Given that errors may only be corrected in units of single symbols (typically 8 data bits), Reed-Solomon codes work best for correcting burst errors[9].

### 2.2 Tools and Technology

Zynq devices are newly proposed to be System-on-Programmable-Chip. The general architecture of the Zynq comprises two sections: the Processing System (PS), and the Programmable Logic (PL) and they can be used separately or together. And each section has the separate power circuitry, which can enable either the PS or PL and be supporting powered down mode if not in use[2]. However, when both parts of the Zynq are used together represents the most compelling use and therefore it is important to understand the reliable structure of both sections, as well as the interfaces between them[2].

For high-speed logic the PL section is ideal for implementation. It has Configurable Logic Blocks (CLBs) for arithmetic and data flow subsystems and Input/ Output Blocks (IOBs) for interfacing, while the software routines and/or operating systems are supported by the PS section[2]. So the overall functionality of any fully functioned and designed system can be efficiently partitioned between hardware and software. Links between the PL and PS are made using industry standard Advanced Extensible Interface (AXI) connections.[2] Figure 2.4 shows the Zynq Architecture which contains Programmable Logic and the Processing System, which are connected via AXI bus. All the hardware peripheral implemented on FPGA and the process will operate it as per the requirement.

Figure 2.4: Zynq Architecture[2]

#### 2.2.1 Processing System

All Zynq devices have almost same architecture, As an Application Processing unit it contains a dual-core ARM Cortex-A9 processor[2]. It is a hard coded on the device. It also consists soft processor like Xilinx MicroBlaze, which is formed by combining the element of programmable logic elements. Hard coded processor can achieve higher performance as compared to soft processor[2].

ARM processing unit contains processing engine, Floating point unit, Memory Management Unit, and cache memory[2]. It has Snoop Control Unit and some interfaces with PL too. To program a deployed components on the Pl section there is a support of Xilinx Software Development Kit which includes an ARM instruction set[2].

#### 2.2.2 Processing System External Interface

The Zynq Processing System has many interfaces by which it communicates with external peripherals and also with the PL section. External interfaces is achieved via Multiplexed Input/Output(MIO) and Extended MIO[2].

The Zynq PS features a variety of interfaces, both between the PS and PL, and between the PS and external components[2].

I/O Interface:

- SPI (x2)

- I2C (x2)

- CAN (x2)

- UART (x2)

- GPIO

- SD (x2)

- USB (x2)

- Ethernet

#### 2.2.3 Programmable Logic

The second principal part of the Zynq architecture is the programmable logic. This is based on the Artix-7 and Kintex-7 FPGA fabric[2].

**The Logic Fabric:** The PL part of the Zynq device is depicted with various features highlighted. The PL is predominantly composed of general purpose FPGA logic fabric, which is composed of slices and Configurable Logic Blocks (CLBs), and there are also Input/ Output Blocks (IOBs) for interfacing[2].

Configurable Logic Block (CLB) CLBs are small, regular groupings of

**logic:** Elements that are laid out in a two-dimensional array on the PL, and connected to other similar resources via programmable interconnects. Each CLB is positioned next to a switch matrix and contains two logic slices[2].

- Slice A sub-unit within the CLB, which contains resources for implementing combinatorial and sequential logic circuits. Zynq slices are composed of 4 Lookup Tables, 8 Flip-Flops, and other logic[2].

- Lookup Table (LUT) A flexible resource capable of implementing (i) a logic function of up to six inputs; (ii) a small Read Only Memory (ROM); (iii) a small Random Access Memory (RAM); or (iv) a shift register. LUTs can be combined together to form larger logic functions, memories, or shift registers, as required.[2]

- Flip-flop (FF) A sequential circuit element implementing a 1-bit register, with reset functionality. One of the FFs can optionally be used to implement a latch[2].

- Switch Matrix A switch matrix sits next to each CLB, and provides a flexible routing facility for making connections (i) between elements within a CLB; and (ii) from one CLB to other resources on the PL[2].

#### 2.2.4 Special Resources

The Block RAMs in the Zynq-7000 are equivalent to those on Xilinx 7 series FP-GAs, and they can implement Random Access Memory (RAM), Read Only Memory (ROM), and First In First Out (FIFO) buffers, while also supporting Error Correction Coding (ECC)[2].

#### 2.2.5 Programmable Logic External Interfaces

The PL includes another hard IP component: the XADC block. This is a dedicated set of Analogue to Digital Converter (ADC) mixed-signal hardware, which features two separate 12-bit ADCs both capable of sampling external analogue input signals at 1Msps[2].

**clocks** The PL receives four separate clock inputs from the PS, and additionally has the facilities to generate and distribute its own clock signals independently of the PS[2].

**Programming and Debug** A set of JTAG ports are provided in the PL section to facilitate configuration and debugging of the PL[2].

#### 2.3 Vivado IDE

Vivado IDE is an integrated development environment for creating the hardware system part of the SoC design, i.e. the processor, memories, peripherals, external interfaces and bus connections. Vivado IDE interacts with other tools in the Vivado Design Suite, and also includes facilities for integrating and packaging IP, which enhances possibilities for design reuse[3]. SDK is a software design suite based on the popular Eclipse platform, which includes driver support for all Xilinx IPs, GCC library support for ARM and NEON extensions using the C and C++ languages, and tools for debugging and profiling[3].

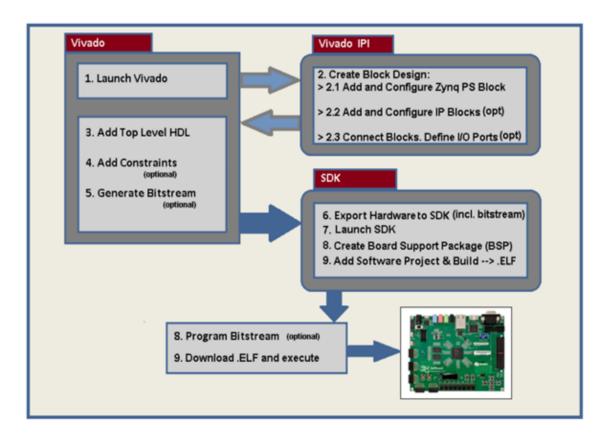

#### 2.3.1 Vivado Design Flow for Zynq

- The implementation process begins with launching Vivado, which is from design entry through bitstream generation[3].

- From Vivado, Create Block Design and configure settings to make the appropriate design decisions such as selection/de-selection of dedicated PS I/O peripherals, memory configurations, clock speeds, etc[3].

Figure 2.5: Vivado Design Flow[3]

- At this point, you may also optionally add IP from the IP catalog or create and add your own customized IP. Connect the different blocks together by dragging signals/nets from one port of an IP to another. Use the design automation capability of the IP Integrator to automatically connect blocks together[3].

- When finished, generate a top-level HDL wrapper for the system[3].

- Ensure that the appropriate PL related design constraints are defined as required by the tools. If a supported evaluation board is specified during project creation (i.e.: the ZedBoard) then constraints may not be needed since the software is board aware[3]. If any signal coming from the PL section to an I/O pin is not defined then the tools will generate an error during the bit-stream generation[3]. Also, do not include pin constraints which are connected to

the dedicated pins as the tools will generate error messages. This is done via creation/addition of a Xilinx Design Constraints (XDC) file to the Vivado project[3].

- Generate the bit- stream for configuring the logic in the PL if soft peripherals or other HDL are included in the design, or if any hard peripheral IO were routed through the PL[3]. At this stage, the hardware has been defined in ;system;[3]. hdf, and if necessary a bit-stream ;system; bit has been generated. The bitstream could be programmed into the FPGA from within Vivado, or it could be done from within SDK[3].

- Now that the hardware portion of the embedded system design has been built, export the design to the SDK to create the software design. A convenient method to ensure that the hardware for this design is automatically integrated with the software portion is achieved by Exporting the Hardware[3]. In order to export the design successfully, the Design Block MUST be open and the implemented design, if exists, MUST be open, otherwise the tools will report an error. Once the hardware has been exported, as a separate step, the SDK can then be launched[3].

Figure 2.5 shows the graphical representation of this Vivado design flow for creating any system on the Zync board.

### 2.3.2 System Setup and Requirements

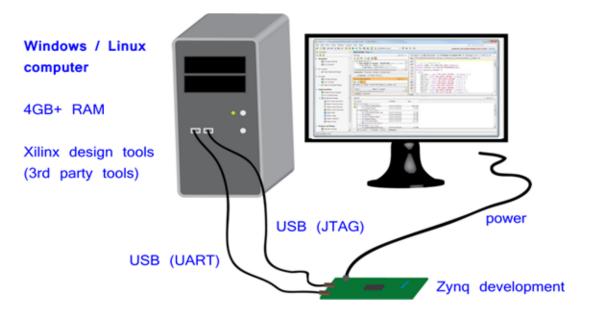

Figure 2.6 shows the setup for the development of the any system based on the Zynq Board.

Figure 2.6: System Setup[3]

#### 2.3.3 An Outline of the Design Flow

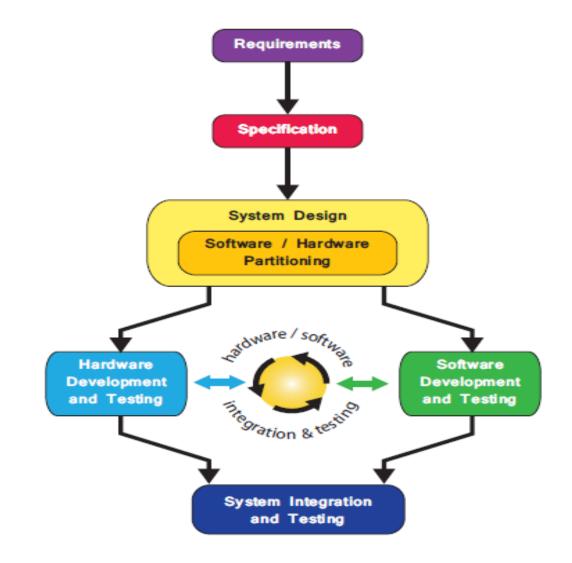

Figure 2.7 shows the work flow to develop any system. It shows the step to step procedure for implementation of any new system to follow.

Figure 2.7: Design Flow [3]

## Chapter 3

# Design and Implementation of FPGA-Based CCSDS Specified Baseband DATA Simulator

### 3.1 Introduction

CCSDS based data transmission standard is planned for future programs such as GISAT. The space data link protocols are defined for creating transfer frames from the space sensor data, received from the space packet service defined by the Space Packet Protocol, these transfer frames can be transmitted, they must be encoded using error correction codes, Synchronized using CCSDS specified Sync Marker and Randomize using Pseudo Random Sequence. Sync marker provides the synchronization between two frames in the space data packets. Randomization is used for the proper transition of bits in the communication channel. And the encoder facilitates the reception of the Baseband data stream in the event of any errors which are introduced due to the noisy channel environment of the space link. For this purpose, the transfer frame is encoded using the ReedSolomon(RS) Code as defined for the CCSDS data transmission standard. The reception and baseband data acquisition of such CCSDS encoded serial streams with RS coding requires the design and development of RS decoder unit. Before that, it is required to develop a Data Simulator with CCSDS RS encoding, equivalent to that proposed for the satellite sensor. The subsequent sections in this technical note provide a brief on RS Coding and explain the design, development and implementation details of FPGA-based of RS Encoder (255,223). The design of the RS encoder is general purpose in nature.

### 3.2 Synchronization

Synchronization is necessary for proper decoding of any transmitted code-blocks or the transfer frames. Here synchronization is necessary for Reed-Solomon code-blocks and subsequent processing of the Transfer Frames[1]. Furthermore, it is necessary for synchronization of the pseudo-random sequence generator because after the attachment of sync the random number generation and simultaneously the randomization of encoded data will start. If the Physical Channel is not Reed-Solomon, turbo or LDPC coded the synchronization is achieved by using a stream of fixed-length Frames with an Attached Sync Marker (ASM) between them[1]. The data unit that consists of the ASM and the Frame is called the Channel Access Data Unit. The ASM is NOT a part of the encoded data space of the Reed-Solomon Codeblock, and it is not presented to the input of the Reed-Solomon encoder or decoder[1].

### 3.3 Pseudo Random Sequence Generator

In order for the receiver system to work properly, every data capture system at the receiving end requires that the incoming signal has sufficient bit transition density, and allow proper synchronization of the decoder[1]. In order to ensure proper receiver operation, the data stream must be sufficiently random. The Pseudo-Randomizer defined in this section is the preferred method to ensure sufficient randomness for

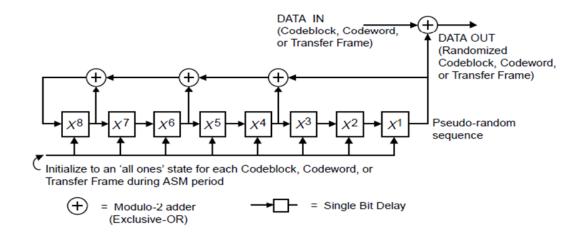

Figure 3.1: Block diagram of Pseudo Random Sequence Generator[1]

all combinations of CCSDS-recommended modulation and coding schemes. The method for ensuring sufficient transitions is to exclusive-OR each bit of the Frame with a standard pseudo-random sequence[1]. If the pseudo-randomizer is used, on the sending end it is applied to the Reed-Solomon code block after encoding. On the receiving end, it is applied to derandomize the data after Frame synchronization but before Reed-Solomon decoding. The pseudo-random sequence is applied starting with the first bit of the Frame[1]. On the sending end, the Frame is randomized by exclusive-Oring the first bit of the Frame with the first bit of the pseudo-random sequence, followed by the second bit of the Frame with the second bit of the pseudo-random sequence, and so on. The pseudo-random sequence shall NOT be exclusive-ORed with the ASM[1]. Figure 3.1 shows the block diagram of Pseudo Random Sequence Generator in HDL using the simple D flip-flop. Initially, the value of the register is one and with respect to clock it will generate a random sequence of bits and after implementation, we will be noticed that it will repeat the bits after 255 clock cycles.

### 3.4 RS-Encoding Algorithm

The ReedSolomon (RS) codes are particularly useful when the communication channel is prone to burst errors, and on channels where the set of input symbols is large. RS codes are nonbinary cyclic BCH codes i.e. the symbols made of mbit binary sequences, where m2. There are 2m1 symbols in an RS codeword[4]. To be able to correct errors in t symbols, there must be r = 2t parity check symbols among the 2m1 symbols. These mbit symbols are considered as elements of a finite field of 2m1 elements, also called a 'Galois Field' which is explained in the next section[4].

An important characteristic of RS codes which makes them desirable to be used is that they have the largest possible code minimum distance among all block codes, in terms of number of symbols in which two codewords differ, for the same input and output block length[4]. For RS Codes, this code minimum distance dmin = n - k + 1. So, this code is capable of correcting t or fewer errors where, t = (dmin - 1)/2 = (n - k)/2. The most attractive RS codes have high code rates (k/n), i.e. low redundancy. The (255, 223) RS code, i.e. with m = 8, t = 16 has become a standard and widely used code. A modified version of this code suited to needs of space data systems is defined by CCSDS[4].

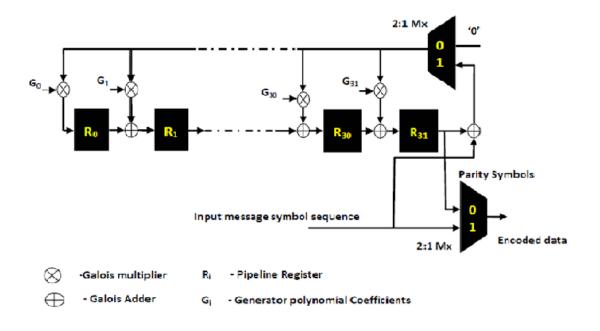

Linear Feedback Shift Register Method In the linear feedback shift register method [10], the polynomial division can be achieved efficiently by means of an n k stage shift register. This method lends itself to easier hardware implementation as shown in Figure 3.2, as the process is divided into unit processes, which are in the form of either combinational (XOR, AND, OR) or sequential logic elements (latches) and hence, this method is more amenable for implementation in programmable digital logic devices described in VHDL or Verilog[10]. In the figure below, the block diagram for (255, 223) RS Encoder is given which is implemented using n - k = 32 stage shift register. Each stage stores an 8bit symbol (m=8). Two multiplexers control the inputs to the shift register as well as the output that is shifted out[10].

Figure 3.2: Reed-Solomon Encoder Block Diagram

#### [1]

Introduction to Galois Fields A finite field with  $p^n$  elements is denoted by GF  $(p^n)$ , where p is a prime number and is also called the Galois Field, in honor of the founder of finite field theory, variste Galois[4]. Arithmetic operations (addition, subtraction, multiplication) on integers are done, as usual, followed by reduction modulo p. For instance, in GF (5),  $4+3 = (7 \mod 5) = 2$ . Division is multiplication by the inverse modulo p. Elements of  $GF(p^n)$  may be represented as polynomials of degree strictly less than n with coefficients in GF(p). Operations are then performed modulo R where R is an irreducible polynomial of degree n over GF(p)[4]. The addition of two polynomials P and Q are done as usual i.e. W = P + Q. The multiplication may be done by first computing W =  $P \cdot Q$  as usual, then computing the remainder modulo R. But there exist better ways to implement this more efficiently[4]. A particular case of interest is GF(2) i.e. when the prime is 2, where addition is exclusive OR (XOR) and multiplication is AND. It is conventional to express elements of GF( $2^n$ ) as binary numbers. They can also be expressed as

polynomials where the coefficient of each term of the polynomial is same as the corresponding bit in element's binary expression[4].

Obtaining Galois field GF  $(2^n)$  The field GF  $(2^n)$  is called the extension of the binary field GF(2)[4]. Besides the numbers 0 and 1, there are additional unique elements in the extension field that represented with a new symbol  $\alpha$ , called the primitive element of the field. Each nonzero element in GF  $(2^n)$  can be represented by a power of  $\alpha$ . To obtain the field GF  $(2^n)$ , an infinite set of elements F is formed by starting with the elements 0, 1,  $\alpha$ , and generating additional elements by progressively multiplying the last entry by  $\alpha$ [4], which yields the following:

$$\mathbf{F}{=}\;0,1,\alpha,\alpha^2,\alpha^3,...,\alpha^j=0,\alpha^0,\alpha^1,\alpha^2,\alpha^3,...,\alpha^j$$

To obtain the finite set of elements of GF  $(2^n)$  from F, a condition must be imposed on F so that it may contain only 2m elements and is closed under multiplication. The condition that closes the set of field elements under multiplication is characterized by the irreducible polynomial shown below[4]:

$$\alpha^{2m-1} + 1 = 0 orequivalently, \quad \alpha^{2m-1} = 1 = \alpha^0 \tag{3.1}$$

Using this polynomial constraint, any field element that has a power equal to or greater than 2m1 can be reduced to an element with a power less than 2m1, as follows[4]:

$$\alpha^{2m+n} = \alpha^{2m-1} \alpha^{n+1} \tag{3.2}$$

Therefore, the elements of a finite field[4],

$$GF(2^{n}) = 0, \alpha^{0}, \alpha^{1}, \alpha^{2}, \alpha^{3}, ..., \alpha^{j}, ..., \alpha^{2n-1}$$

(3.3)

Obtaining the polynomial representation using a Primitive polynomial An irreducible polynomial f(X) of degree m is said to be primitive if the smallest positive integer n for which f(X) divides  $X^{n+1}$  is  $n = 2^m - 1$ . A polynomial A divides B if the division yields a nonzero quotient and a zero remainder[4]. Also, the primitive element is a root of the primitive polynomial i.e.  $f(\alpha)$ .i.e.  $f(\alpha) = 0$ This equation can be used to represent each element of the Galois Field as distinct polynomial of degree m1 or less as illustrated by the following example[4]: Let us take the example of GF (2<sup>3</sup>) i.e. m=3, for which we have primitive polynomial f(X) =  $1 + X + X^3$ . In this case, we will have  $2^3 = 8$  elements which can be represented as distinct polynomials of degree m - 1 = 2. Using the above relation by putting X =  $\alpha$ , polynomial becomes[4],  $\alpha^3 + \alpha + 1 = 0$  So,

$$\alpha^3 = \alpha + 1 \tag{3.4}$$

$$\alpha^4 = \alpha^3 \cdot \alpha = (\alpha + 1) \cdot \alpha = \alpha^2 + \alpha \tag{3.5}$$

Similarly,

$$\alpha^5 = \alpha^4 \cdot \alpha = (\alpha^2 + \alpha) \cdot \alpha = \alpha^2 + \alpha + 1 \tag{3.6}$$

$$\alpha^6 = \alpha^5 \cdot \alpha = (\alpha^2 + \alpha + 1) \cdot \alpha = \alpha^2 + 1 \tag{3.7}$$

$$\alpha^7 = \alpha^6 \cdot \alpha = (\alpha^2 + 1) \cdot \alpha = 1 = \alpha^0 \tag{3.8}$$

Since,  $\alpha^7 = \alpha^0$ , we have only 8 elements in GF (2<sup>3</sup>)[4].

#### ENCODING PROCEDURE

- (n, k) = (2<sup>(m-1)</sup>, 2<sup>(m-1-2t)</sup>) = (7, 3) double symbol error correcting RS code Where 2t = n - k is number of parity symbol and t is symbol error here 2t = 4 roots[4]

- Input message symbol sequence : 010 110 111

- Input symbol length : 3

- Generator Polynomial:

$$G(x) = (x - \alpha^{1})(x - \alpha^{2})(x - \alpha^{3})(x - \alpha^{4})$$

(3.9)

$$= \alpha^{3} + \alpha^{1}x + \alpha^{0}x^{2} + \alpha^{3}x^{3} + x^{4}$$

(3.10)

$$= g_0 + g_1 x + g_2 x^2 + g_3 x^3 + \dots [4]$$

(3.11)

|            | [4]        |            |                                      |                                      |                                      |                                      |                                  |            |  |  |  |  |  |

|------------|------------|------------|--------------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|----------------------------------|------------|--|--|--|--|--|

| Input      |            |            |                                      | Feedback                             | 0                                    |                                      |                                  |            |  |  |  |  |  |

|            |            |            |                                      |                                      |                                      |                                      |                                  |            |  |  |  |  |  |

|            |            |            |                                      |                                      |                                      |                                      | -                                |            |  |  |  |  |  |

| $\alpha^1$ | $\alpha^3$ | $\alpha^5$ | 0                                    | 0                                    | 0                                    | 0                                    | $\alpha^5$                       | $\alpha^5$ |  |  |  |  |  |

|            | $\alpha^1$ | $\alpha^3$ | $\alpha^5 \cdot \alpha^3 = \alpha^1$ | $\alpha^5 \cdot \alpha^1 = \alpha^6$ | $\alpha^5 \cdot \alpha^0 = \alpha^5$ | $\alpha^5 \cdot \alpha^3 = \alpha^1$ | $\alpha^1 + \alpha^3 = \alpha^0$ | $\alpha^5$ |  |  |  |  |  |

|            |            |            |                                      | $\alpha^6 + \alpha^0 = \alpha^6$     | $\alpha^5 + 0 = \alpha^5$            | $\alpha^1 + 0 = \alpha^1$            |                                  |            |  |  |  |  |  |

|            |            | $\alpha^1$ | $\alpha^0 \cdot \alpha^3 = \alpha^3$ | $\alpha^0 \cdot \alpha^1 = \alpha^1$ | $\alpha^0 \cdot \alpha^0 = \alpha^0$ | $\alpha^0 \cdot \alpha^3 = \alpha^3$ | $\alpha^2 + \alpha^1 = \alpha^4$ | $\alpha^3$ |  |  |  |  |  |

|            |            |            |                                      | $\alpha^1 + \alpha^1 = 0$            | $\alpha^6 + \alpha^0 = \alpha^2$     | $\alpha^5 + \alpha^3 = \alpha^2$     |                                  |            |  |  |  |  |  |

|            |            |            | $\alpha^4 \cdot \alpha^3 = \alpha^0$ | $\alpha^4 \cdot \alpha^1 = \alpha^5$ | $\alpha^4 \cdot \alpha^0 = \alpha^4$ | $\alpha^4 \cdot \alpha^3 = \alpha^0$ |                                  | $\alpha^1$ |  |  |  |  |  |

|            |            |            |                                      | $\alpha^5 + \alpha^3 = \alpha^2$     | $\alpha^4 + 0 = \alpha^4$            | $\alpha^0 + \alpha^2 = \alpha^6$     |                                  |            |  |  |  |  |  |

|            |            |            |                                      |                                      |                                      |                                      |                                  | $\alpha^6$ |  |  |  |  |  |

|            |            |            |                                      |                                      |                                      |                                      |                                  | $\alpha^4$ |  |  |  |  |  |

|            |            |            |                                      |                                      |                                      |                                      |                                  | $\alpha^2$ |  |  |  |  |  |

|            |            |            |                                      |                                      |                                      |                                      |                                  | $\alpha^0$ |  |  |  |  |  |

Table 3.1: Step to Step Procedure of encoder with respect to clock

Table 3.1 shows the step to step encoding procedure with respect to the clock. It shows the Input sequence, register contents, Feedback and the Output at every clock cycle.

After the third clock cycle, the register contents are the four parity symbols, Then switch in RS encoder block is change its position and the parities symbols contained in the register are shifted to the output. So the output of the encoder will be[4],

$$U(x) = \alpha^{0} + \alpha^{2}x + \alpha^{4}x^{2} + \alpha^{6}x^{3} + \alpha^{1}x^{4} + \alpha^{3}x^{5} + \alpha^{5}x^{6}$$

(3.12)

# 3.5 Hardware Implementation in Xilinx FPGA using VHDL

The Hardware based CCSDS ReedSolomon Encoder is implemented in FPGA and described in VHDL. It is based on the linear feedback shift register implementation. VHDL Blocks The entire design, development is carried out using VHDL (Xilinx). The task has been divided into the following functional blocks to facilitate the modular implementation, and ease of simulation and final testing.

encoder\_top.vhd: This is the top module of RSEncoder which contains many sub-modules:

- Test Stimulus module

- Data Encoder module.

- PRBS Generator

- Mux

- Clock Divider module

- Parallel to Serial Converter and Randomizer module

#### Test\_Stimulus.vhd:

This module implements control logic for RS Encoder it generates controls signals like start, reset data input and data output registers data path as well as it generates input block sequence of rs encoder. For this Design and implementation, the ramp signal of 50 MHz is generated as an input of (255,223) RS encoder block design.

#### data\_encoder.vhd:

Implements data path for RS Encoder in 32 LFSR architecture, which reduces the latency of RS Encoder to 3 clock pulses. Input and output message data are registered through input and output registers which ensure glitch free operation and both the registers are controlled by enable signals which avoid unnecessary switching of the data path and in turn saves power.

#### mux.vhd:

This module implements the parametric multiplexer that is used to implement switches in the data path. It selects either data or parities goes out and also selects either sync or encoded data goes out.

#### clk\_divider.vhd:

This module divides the onboard clock frequency by eight because RS-Encoder performs byte operations and finally output will be serial.

#### parl\_ser\_conv.vhd:

This module converts byte of encoded data into the serial stream of bits.

#### DATA\_shifter:

This module performs shift operation of serial data to manage the sync period.

#### $rs\_encode\_pack.vhd:$

The package that defines data types and functions for projects. This VHDL package has been developed to provide the RS encoder functions. It provides Galois addition and multiplication functions.

## 3.6 Schematic View

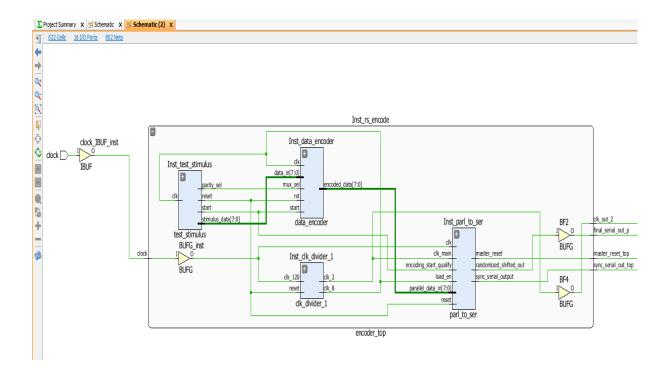

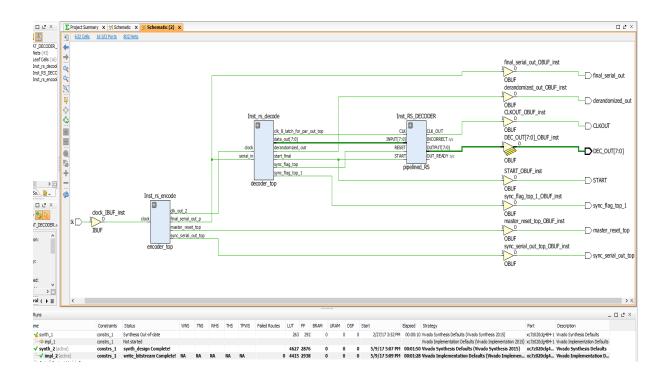

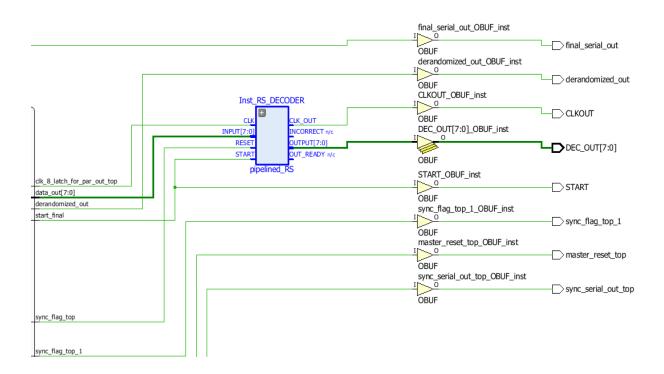

Figure 3.3 shows the schematic view of the data simulator. As shown in the figure, the clock is taken as an input of a data encoder from the onboard clock oscillator. It shows the implemented components for data simulator. and we get an encoded, randomized and frame synchronized serial data as an output.

Figure 3.3: RTL View for Data Transmission Process

# 3.7 Device Utilization

Table 3.2 shows the available Devices on Zed board to implement our logic and how much are used in the implementation of Data Simulator.

| Resources | Utilization | Available | Utilization % |  |

|-----------|-------------|-----------|---------------|--|

| LUT       | 334         | 53200     | 0.63          |  |

| LUTRAM    | 2           | 17400     | 0.01          |  |

| FF        | 399         | 106400    | 0.38          |  |

| IO        | 29          | 200       | 14.50         |  |

| BUFG      | 6           | 32        | 18.75         |  |

27

# Chapter 4

# Implementation of FPGA-Based CCSDS Specified Baseband Data Processing

### 4.1 Introduction

As a part of the design and development efforts towards the realization of the ground data reception systems for the future Remote Sensing Sensors, which will transmit the data in the CCSDS formats, the design and development were taken up for the individual hardware modules required to be implemented for the total data reception chain. CCSDS standards propose a packetized transmission scheme consisting of independent layers which separately process the data. This packetized data are attached with sync marker, randomized and encoded with CCSDS Prescribed processing. So the satellite data reception scheme consisting of the frame synchronization, de-randomization and the decoding of the transmitted data. For the encoding of the space data Forward error correcting codes have become commonplace in modern digital communications. These codes work by adding extra information (redundancy) to the original data. The encoded data can then be stored or transmitted. When data is recovered it may have errors introduced, because of radio frequency interference noise in the transmission channel. The added redundancy allows a decoder (with certain restrictions) to detect which parts of the received data are corrupted and correct them. The number of errors the code can correct depends on the amount of redundancy added. As a part of the design and development efforts towards the realization of the ground data reception systems for the future Remote Sensing Sensors, which will transmit the data in the CCSDS formats, the design and development were taken up for the individual hardware modules required to be implemented for the total data reception chain. The RS decoder module is one such element which is required to realize the error correction before the formation of the actual information/data packets can be done.

### 4.2 Frame Synchronization

The Frame Synchronization is one such module which is essential to synchronize the data frame before the actual decoding procedure starts[1]. At the transmitter side, it has attached the some specified known bit pattern to synchronize the data frame so at the ground data reception system it should be identified and removed for the further processing of the actual data. For that digital correlator is designed and implemented using VHDL[1].

### 4.3 De-Randomization

In order for the receiver system to work properly, every data capture system at the receiving end requires that the incoming signal has sufficient bit transition density, and allow proper synchronization of the decoder[1]. The data stream is sufficiently random. The method for ensuring sufficient transitions is to exclusive-OR each bit of the Received Frame with a standard pseudo-random sequence. The pseudo-randomizer is used, on the sending end so it is required to de-randomize the data

after Frame synchronization but before Reed-Solomon decoding. The pseudo-random sequence is applied starting with the first bit of the Frame. Implementation of the standard sequence is same as done for transmitting side[1].

### 4.4 RS-Decoding Algorithm