## Developing Arm Architecture Verification Tools and Solutions

Major Project Report

Submitted in fulfillment of the requirements for the degree of

Master of Technology in Electronics & Communication Engineering (Embedded Systems)

By

## Khushnuma Jhunjhunwala

## (16 MECE06)

Electronics & Communication Engineering Department Institute of Technology Nirma University Ahmedabad-382 481 May 2018

## Developing Arm Architecture Verification Tools and Solutions

Major Project Report

Submitted in fulfillment of the requirements for the degree of

Master of Technology in Electronics & Communication Engineering (Embedded Systems)

By

## Khushnuma Jhunjhunwala

## (16MECE06)

External Project Guide: Mr. Saurov Kanti Shyam Staff Engineer, Arm embedded Technologies Pvt. Ltd., Bangalore. Internal Project Guide: Prof. Vijay Savani EC Department, Institute of Technology, Nirma University, Ahmedabad.

Electronics & Communication Engineering Department Institute of Technology-Nirma University Ahmedabad-382 481 May 2018

## Declaration

This is to certify that

- a. The thesis comprises my original work towards the degree of Master of Technology in Embedded Systems at Nirma University and has not been submitted elsewhere for a degree.

- b. Due acknowledgment has been made in the text to all other material used.

- Khushnuma Jhunjhunwala 16MECE06

## Certificate

This is to certify that the Major Project entitled "Developing Arm architecture verification tools and solutions" submitted by Khushnuma Jhunjhunwala (16MECE06), towards the partial fulfillment of the requirements for the degree of Master of Technology in Embedded Systems, Nirma University, Ahmedabad is the record of work carried out by her under our supervision and guidance. In our opinion, the submitted work has reached a level required for being accepted for examination. The results embodied in this major project, to the best of our knowledge, haven't been submitted to any other university or institution for award of any degree or diploma.

Date:

Place: Ahmedabad

Prof. Vijay Savani

Internal Guide

**Dr. D. K. Kothari** Section Head, EC

Dr. N.P. Gajjar

**Program Coordinator**

**Dr. Alka Mahajan** Director, IT

iv

## Certificate

This is to certify that the Major Project entitled "Developing Arm architecture verification tools and solutions" submitted by Khushnuma Jhunjhunwala (16MECE06), towards the fulfillment of the requirements for the degree of Master of Technology in Embedded Systems, Nirma University, Ahmedabad is the record of work carried out by her under our supervision and guidance. In our opinion, the submitted work has reached a level required for being accepted for examination.

Mr. Saurov Kanti Shyam Staff Engineer Arm Embedded Technologies Pvt. Ltd. Bangalore

## Acknowledgements

I am profoundly grateful to Mr. Saurov Kanti Shyam, Staff Engineer at Arm, Bangalore for his expert guidance and continuous encouragement throughout the internship period in preparing me for the project of Developing Arm architecture verification tools and solutions.

I would like to express my sincere thanks to **Dr. N.P. Gajjar**, PG Coordinator of M.Tech Embedded Systems for providing me an opportunity to pursue my internship at Arm, Bangalore. Would also like to thank **Prof. Vijay Savani** for his exemplary guidance, mentoring and constant encouragement.

At last I must express my sincere heartfelt gratitude to all the employees of Arm who directly or indirectly helped me during the course of this work.

> - Khushnuma Jhunjhunwala 16MECE06

## Contents

| De | eclara                                | ation                                                                                                                                                                                                                                                          | iii                                                                                                                    |

|----|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Ce | ertific                               | cate                                                                                                                                                                                                                                                           | iv                                                                                                                     |

| A  | cknov                                 | vledgements                                                                                                                                                                                                                                                    | vi                                                                                                                     |

| Al | ostra                                 | $\mathbf{ct}$                                                                                                                                                                                                                                                  | xi                                                                                                                     |

| Al | brev                                  | viation Notation and Nomenclature                                                                                                                                                                                                                              | xii                                                                                                                    |

| 1  | <b>INT</b><br>1.1<br>1.2<br>1.3       | <b>RODUCTION</b> Motivation         Objective         Outline of Thesis                                                                                                                                                                                        | <b>1</b><br>1<br>1<br>2                                                                                                |

| 2  | <b>Arm</b><br>2.1<br>2.2              | ARCHITECTURE VERIFICATION TOOLS         Architectural Verification         RIS and MP-RIS Tool                                                                                                                                                                 | <b>4</b><br>4<br>6                                                                                                     |

| 3  | UN<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5 | <b>IFIED TARGET CONFIGURATION</b> BackgroundProblem StatementChallengesProposalImplementation3.5.1Resource configuration user interface software tool3.5.2Directly mapped parameters3.5.3Derived parameters3.5.4Structure of Unified Target Configuration Tool | <ol> <li>10</li> <li>11</li> <li>11</li> <li>12</li> <li>13</li> <li>13</li> <li>14</li> <li>15</li> <li>16</li> </ol> |

| 4  | MP<br>4.1<br>4.2<br>4.3               | RIS TOOL         Introduction         Features of MP RIS Tool         Test Topology                                                                                                                                                                            | <b>19</b><br>19<br>20<br>20                                                                                            |

|          | 4.4   | Design Configuration                   | 22        |

|----------|-------|----------------------------------------|-----------|

|          | 4.5   | RIS Tool Recipes                       | 23        |

|          |       | 4.5.1 Bring-up Recipes                 | 24        |

|          |       | 4.5.2 Micro-architecture Recipes       | 25        |

|          |       | 4.5.3 Functional Recipes               | 25        |

|          | 4.6   | Test Generation Process                | 25        |

|          | 4.7   | RIS Tool Wrapper                       | 26        |

| <b>5</b> | PR    | EGENERATION QA - RECIPE QA             | 30        |

|          | 5.1   | Introduction                           | 30        |

|          | 5.2   | Recipe QA Execution                    |           |

|          | 5.3   | Knob Randomization Report              | 36        |

|          | 5.4   | Checks for crosses                     | 38        |

|          | 5.5   | Checks for configs                     | 40        |

| 6        | PO    | STGENERATION QA - TEST LENGTH ANALYSIS | <b>43</b> |

|          | 6.1   | Introduction                           | 43        |

|          | 6.2   | Working                                | 44        |

|          | 6.3   | Execution of the tool                  | 45        |

|          | 6.4   | Reading MP RIS QA Logs                 | 47        |

| <b>7</b> | CO    | NCLUSION AND FUTURE WORK               | 49        |

|          | 7.1   | Conclusion                             | 49        |

|          | 7.2   | Future Work                            | 50        |

| R        | efere | nces                                   | 51        |

# List of Figures

| 2.1  | Arm compliance framework                                                                                                                | 5  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2  | Working of RIS Generator [6]                                                                                                            | 7  |

| 2.3  | Memory organization for RIS Generator [6]                                                                                               | 9  |

| 3.1  | Architecture configuration as input to RIS tool                                                                                         | 10 |

| 3.2  | Unified Target Configuration                                                                                                            | 12 |

| 3.3  | Resource configuration user interface software tool flow                                                                                | 14 |

| 3.4  | Directly mapped parameters example                                                                                                      | 15 |

| 3.5  | Example Equations                                                                                                                       | 15 |

| 3.6  | $CCSIDR Register [7] \dots \dots$ | 16 |

| 3.7  | CCSIDR Register field description [7]                                                                                                   | 17 |

| 3.8  | Flow of tool for RIS tool input architecture config YAML file generation                                                                | 18 |

| 4.1  | RIS tool test topology                                                                                                                  | 21 |

| 4.2  | Design configuration files                                                                                                              | 23 |

| 4.3  | Recipe design configuration                                                                                                             | 24 |

| 4.4  | Recipe Types                                                                                                                            | 25 |

| 4.5  | Test generation process                                                                                                                 | 26 |

| 4.6  | MP RIS tool Block Diagram                                                                                                               | 27 |

| 4.7  | MP RIS tool Block Diagram                                                                                                               | 28 |

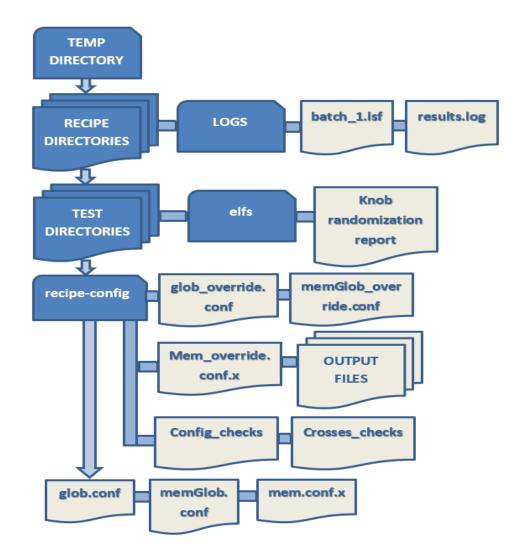

| 5.1  | MP RIS Tool temp directory structure                                                                                                    | 30 |

| 5.2  | MP RIS Tool temp directory structure                                                                                                    | 31 |

| 5.3  | MP RIS Tool temp directory structure                                                                                                    | 32 |

| 5.4  | MP RIS tool temp directory structure block diagram                                                                                      | 33 |

| 5.5  | Recipe QA help                                                                                                                          | 34 |

| 5.6  | Recipe QA execution                                                                                                                     | 35 |

| 5.7  | Recipe QA list of configs                                                                                                               | 36 |

| 5.8  | Output knob randomization report                                                                                                        | 37 |

| 5.9  | Crosses_details file snapshot                                                                                                           | 38 |

| 5.10 | Output checks for crosses file                                                                                                          | 39 |

| 5.11 | Config_details file snapshot                                                                                                            | 40 |

| 5.12 | Output checks for configs file                                                                                                          | 42 |

#### LIST OF FIGURES

| 6.1 | Post-generation QA Tool block diagram            | 43 |

|-----|--------------------------------------------------|----|

| 6.2 | Help option of tool to verify test length        | 44 |

| 6.3 | Output of tool to verify test length             | 44 |

| 6.4 | AEM Tarmac file                                  | 45 |

| 6.5 | Analysis of output of tool to verify test length | 46 |

| 6.6 | QA Logs file                                     | 47 |

### Abstract

Processor architecture verification is the process of uncovering bugs in the design of the processor. The ultimate goal of architectural verification is to deliver the design to market as bug free as possible. It is one of the biggest challenge industry is facing today, as the verification effort is often more than the design effort.

"Random Instruction Sequencer (RIS)" tools are most commonly used across the processor design industry for verification and validation of processor design. Thus developing RIS tools would simplify the process of processor design verification which may prove helpful to considerably reduce time to product.

The work presented here introduces a unified target configuration generation tool, for auto generation of architecture configuration files used to configure RIS tool. It achieves significant reduction in resource utilization by automating the process of configuration file generation which is being hand coded otherwise. It also includes development of Pre-generation and Post-generation Quality Assurance Tools for the MP RIS Tool which is used for verification of multi-processor environment. The Pre-generation QA tool discards the invalid test cases before generation and hence increases the efficiency of the MP RIS Tool by saving time and resources being used to generate invalid test cases. Whereas the Post-generation QA tool does the analysis of the generated test case to subsequently reduce the percentage of overhead instructions added compared to actually required instructions in a generated test case.

## Abbreviation Notation and Nomenclature

| RIS | Random Instruction Sequencer   |

|-----|--------------------------------|

| RTL |                                |

| ISA | Instruction Set Architecture   |

| AEM | Architecture Envelop Model     |

| ISG | Instruction Stream Generator   |

| AVS | Architecture Validation Suites |

| DVS | Device Validation Suites       |

| ACS | Architecture Compliance Suites |

| PEs | Processing Elements            |

|     | Executable Linkable Format     |

| GUI | Graphical User Interface       |

| CSV | Comma Separated Value          |

| SOC | System On Chip                 |

| IPS | Instructions Per Second        |

| QA  | Quality Assurance              |

|     |                                |

# Chapter 1 INTRODUCTION

### **1.1** Motivation

Verification is one of the biggest challenge industry is facing. The verification effort is often more than the design effort as the design complexity of the processor architecture is increasing these days [3]. "Random Instruction Sequencer" (RIS) tools are most commonly used across the processor design industry for functional verification and validation of processor design. These tools are used most of the times to find bugs in design for a stable RTL (Register Transfer Level) design that is not at a matured level. RIS tools effectively generates test scenarios that are hard to anticipate. These completely random sequences of instructions prove to be useful for exploring corner cases in the RTL design. These sequences are more effective when the bugs are related to a sequence of events that happen in a short time span [1].

The verification results depends upon the quality of results produced by the instruction sequence generator, the availability of time and also the number of computational resources available. The time and resources are limited most of the times so we need to tune the instruction sequence generator i.e. the RIS tool to target specific areas in the design [1].

## 1.2 Objective

RIS tools are popularly recognized as an efficient approach for verifying corner cases for processor architecture verification environment that are hard to anticipate. To cover most of corner cases RIS tools uses random test libraries. Thus improvements in randomization that the RIS tools take would help us to increases the hit rate of corner cases which are hard to acknowledge by writing directed tests for different scenarios.

The objective of this project "Developing Arm architecture verification tools and solutions" can be divided into various phases:

- a. Unified Target Configuration generation: With Unified Target Configuration we look forward at developing a common interface which auto-generates different standard files in RIS tool acceptable format.

- b. **Pre-generation Recipe QA:** With this approach we plan to improve the coverage of the test sequences generated by RIS tool by adding some directed aspects to the recipe specific knobs taking random values from a previously defined range of acceptable values. And also increasing the efficiency of the RIS tool used for verification of multi processor design by discarding the invalid test cases before their generation.

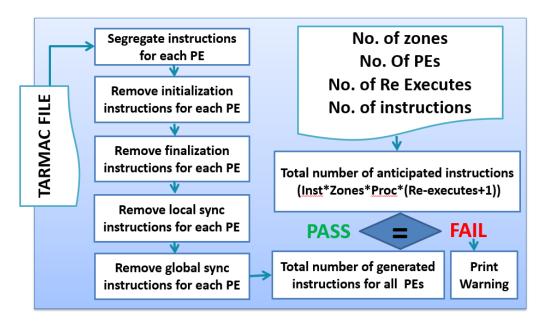

- c. **Post-generation Recipe QA:** This approach is used to verify the length of the generated test cases against the anticipated length to ensure that the overhead added is at an optimum level to not decrease the efficiency of the random test generator. Thus the percentage of overhead added is first analyzed and then the instruction count is given such that we get higher number of useful instructions then the overhead instructions.

## **1.3** Outline of Thesis

This Thesis is put together in five chapters, a brief information about each of them are discussed below:

• Chapter 2 : Arm architecture verification tools

An introduction to the Random Instruction Sequencer Tool and also description of how it is more effective than the Deterministic approach to cover corner cases.

• Chapter 3 : Unified Target Configuration Detailed description of the unified approach of generating the architectural configuration yaml file in RIS tool compatible format. Also includes the flow of taking specifications from the partner and storing it in a database and querying it to get appropriate values.

#### • Chapter 4 : MP RIS Tool

This chapter includes the detailed description of the MP RIS tool and its working. It also includes detailed procedure of generating the test cases using various Arm tools and procedures. It defins various components and plugins used in the tool like the recipes, knobs, zones, the wrapper script tool and much more.

#### • Chapter 5 : Pre-generation QA - Recipe QA

It describes in detail a newly developed plugin for Quality Assurance of the generated test cases from the MP RIS Tool. Also includes the level of randomization achieved by the architectural parameters and how to improve it to achieve better coverage. This chapter describes how this Pre-generation Tool helps to increase the efficiency of the MP RIS Tool.

#### • Chapter 6 : Post-generation QA - Test Length Analysis

This chapter describes the Post-generation tool made for the MP RIS tool and its working. It gives a detailed explanation of why we require to analyze a test case after it is generated. Also includes the study of optimum number of instruction count to make the generated test case efficient despite of all the overhead instructions that are added to the test cases that are generated.

#### • Chapter 7 : Conclusion and Future Work

Describes concluding remarks on how the Arm verification tools i.e. the RIS Tools are developed in this project to enhance their functionality. It also describes the proposed work that can be done in future.

## Chapter 2

## Arm ARCHITECTURE VERIFICATION TOOLS

## 2.1 Architectural Verification

Verification here refers to the entire process of uncovering bugs in the architectural design of the processor. The ultimate goal of architectural verification is to deliver the design to market as bug free as possible. It is the process of ensuring that a design of processor meets specified requirements. It reduces the cost of late bugs in a design by ensuring proper functional coverage of the entire design that is being tested. Thus it saves us from loss of revenue invested in respin of production samples.

The verification methodology at Arm verifies the RTL or the AEM (Architecture Envelop Model) against its ISA (Instruction Set Architecture). Here the AEM is a highly configurable fast model of Arm processor. The verification process has to fill in the gap between the architecture specification given by the ISA and the detailed processor implementation [4]. Thus there needs to be a mapping between the architecture level and the micro architecture level of the processor which is useful in the process of verification of the processor design.

The verification of microprocessor architecture design relies majorly on simulation based techniques. These stimuli are then executed on RTL design model of the processor architecture or on AEM and then the results are analyzed to check the correctness of the design. The stimulus are the sequence of instructions which may be generated using automated tools which are commonly known as Instruction Stream Generators (ISG) [5].

The stimulus for verification of arbitrary architecture design can be deterministic, random or constraint-based stimuli [5].

#### • Deterministic simulation

This methodology is the most common way of generating test stimulus. The two ways for generating test cases for deterministic simulation are:

- 1 AVS (Architecture Validation Suites) and

- 2 DVS (Device Validation Suites)

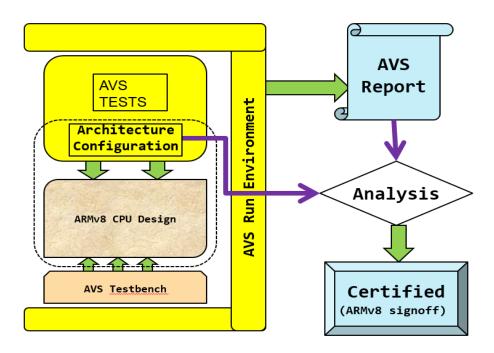

AVS focuses on checks for architectural functionality whereas DVS focuses on behaviour of a specific core [3]. Thus AVS does the checks on ISA and the exception model that is implemented. Its working is as shown in figure 2.1. On the other hand DVS checks:

- **1** IMPLEMENTATION DEFINED features

- 2 Scenarios dependent on timings

- 3 Scenarios related to stress testing and

- 4 Scenarios which are not covered fully by AVS

These test suits are the Arm "Architecture Compliance Suites" (ACS). The limitation that they have is due to the effort that is required to generate the test cases and the performance that is achieved by the simulation tool [3].

Figure 2.1: Arm compliance framework

#### • Random stimulus generation

It is most effective way of verifying corner cases that are hard to anticipate using the deterministic simulation approach. With the help of templates describing generation tasks RIS tools generate random stimulus which are nothing but a sequence of random instructions [3].

#### • Constrain Based simulation

These type of simulation is not truly random but cover certain areas of functionality in a systematic way keeping everything else random [5]. Addition of semi-directed instruction sequences that are deterministic in nature increases chances of covering desired corner cases with less investment in time [6].

## 2.2 RIS and MP-RIS Tool

The functional verification of the microprocessor design or the SOC (System On Chip) is one of the most critical phase of the entire design life cycle as it takes two third of the entire design cycle time. So we need to develop efficient tools in terms of time and completeness. Thus various methodologies proposed for function verification of the processor are as explained below [8].

An approach to test program generation known as Model Based Test-Generation, allows the complex knowledge of testing to be incorporated in the logic of model itself. Then this knowledge base is used in conjunction with the architectural model to generate test cases. Another test generation methodology assumes that the netlist of the processor is available and it requires the library of macros to be developed. These macros are written manually in such a way that they are able to excite all functions of the processor [8].

RIS generator tools are used to generate sequences of random instructions which act as stimuli for verification of processor design. The MP-RIS tool is the RIS tool that generates instruction sequences for multiprocessor systems. These instructions focuses on the data sharing and memory coherency in the multiprocessor environment.

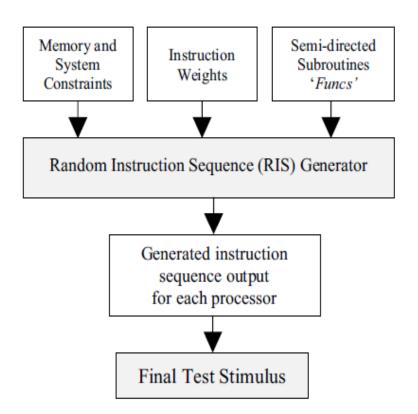

The instructions can be focused uniquely to one processor or the multiprocessor environment where virtual to physical memory map or address and data space is shared. By defining such constraints we can generate different level of traffic specifying the interactions between processors and memory subsystem for multiprocessing elements. Thus using this approach the data coherency in a multiprocessing environment is stress tested [6]. RIS tools are highly configurable tools which provide options to generate test scenarios stressing some particular functionality of the processor. This can be done by providing weight to instructions as shown in figure 2.2. Thus the test sequence generated have some specific subset of the Instruction Set (ISA) that can be used to stress out some particular functional area of the processor [6].

Figure 2.2: Working of RIS Generator [6]

RIS tools takes various configuration files as inputs to generate test sequences targeting one particular area of processor that needs to be stressed. They are described as below:

#### • Memory and System Constraints

This gives information about the memory space that is available for generator, attributes of cache like how many levels of cache are implemented and their size, virtual memory organization, system memory map and the configuration of the knobs i.e. the values of the architecture specific parameters [6].

#### • Instruction Weights

The user gives weights to instructions or group of instructions based on the intent of the test and the final instruction sequence that is generated has the distribution of instruction based on these weights [6].

#### • Semi-directed Subroutines

These semi directed codes are targeted to test a specific processor functionality like linecross. This directed chunk of code is called funcs. They target some specific scenarios in the processor [6].

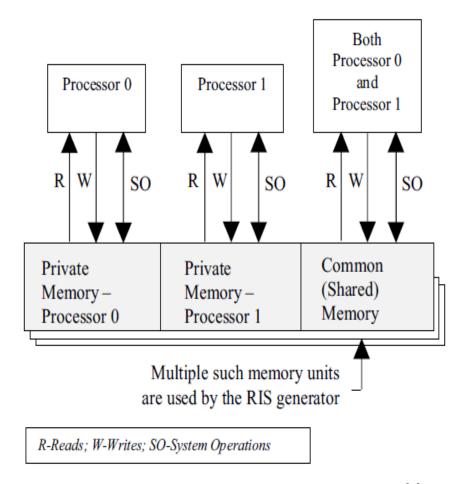

For multiprocessor systems environment stress testing can be done by a very common method of cache load store operations or writing to a shared memory between different processors. Thus the address generation must be such that the data is shared between multiple processors. Thus for memory coherency testing the MP-RIS generator have a memory model where each processor from a cluster have private memory region to which only that specific processor can write during the test and there is a shared memory region which can be accessed by more then one processing element [6].

Figure 2.3: Memory organization for RIS Generator [6]

The figure 2.3 shows two processing elements each with private memory region and sharing one common memory region. Now different random instructions trigger processors to access these regions. The number of processing elements PEs accessing the shared memory are configurable for a RIS generator.

Now the generated instruction sequences are in Executable Linkable Format (ELF) which can be built using Arm tool chain to get executed. These instruction sequences are fed to either AEM model i.e. the software model of the processor or they are run on the processor RTL for verifying them.

## Chapter 3

## UNIFIED TARGET CONFIGURATION

## 3.1 Background

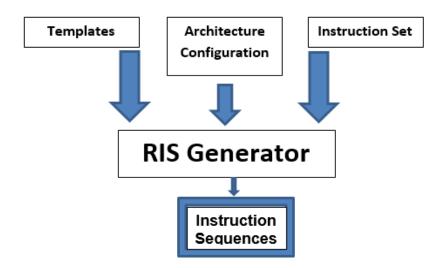

Both AVS and RIS tool require architecture configuration files for different implementations as an input to generate different test cases. Target configuration files captures this architecture specific configuration parameters and their values. Partners are approached multiple times by Partner Enablement team and tool engineers for generating these target configuration files. And then these files are hand coded referring to the engineering specifications. The input structure of the RIS Tool is as shown in figure 3.1

Figure 3.1: Architecture configuration as input to RIS tool

## 3.2 Problem Statement

- Partners need to be approached multiple times for same target configuration data but in different format and for different use cases.

- There is no automation for both AVS and RIS tool, thus configuration files are hand coded. This leads to various problems as listed below:

- Human error

- Tedious job

- Requires more resources

- Takes more time

- Future maintainability is a problem.

- Multiple files needs to be changed to reflect changes in architecture specifications.

## 3.3 Challenges

- A single automated application.

- Generates the configuration as required by RIS tool and AVS, without changing present output format.

- Syncing and Maintainability across several teams (DV engineers, Partner Enablement team, RIS tool engineers)

- No inter dependency across teams. AVS and RIS teams should be able to make progress without info specific to the others being filled in.

- Future maintainability must be possible.

- Realistic value based on the existing methodologies and Partners response.

- Would need to meet some key real-world requirements like handling incomplete information.

- Being extremely quick and easy to hack in new requirements.

- Would need to be updated regularly and kept in sync across all active projects.

## 3.4 Proposal

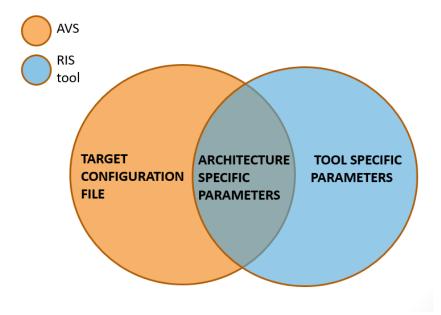

Figure 3.2: Unified Target Configuration

The architecture configuration yaml file that is fed to RIS tool consists of 2 parts 1) Tool specific parameters 2) Architecture specific parameters. After studying the target configuration file it is established that the architecture specific part of the architecture configuration yaml file that is fed to RIS tool can be derived from the target configuration file. This can be realized using a venn diagram as shown in figure 3.2

The parameters in the architecture specific of the yaml file parts can be obtained from target config file in two ways:

- Some parameters of the yaml file have a direct mapping to the parameters of target config file just with both the parameters having different names.

- Some parameters of the yaml file can be derived from the existing parameters in the target config file with the help of some equations.

### 3.5 Implementation

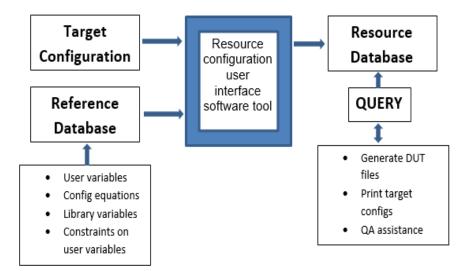

The target configuration file is parsed to a resource configuration user interface software tool which pushes the values of the parameters in a database. So to implement unified target configuration we need to auto-generate the yaml file containing architectural configuration in RIS tool acceptable format. Thus we need to follow certain steps as listed below:

- Parse the Target Configuration file to the resource configuration user interface software tool so that it gets the value of the parameters.

- Add equations in the tool for the derived parameters. This is one time configuration in the tool.

- Now query the database of the tool to get the value of the desired parameter.

- Now map the name of the parameter with the name that is accepted by RIS tool.

- Assign the value of the parameter fetched to the RIS tool parameter.

- Print the List of architecture configuration parameters in yaml format and in order acceptable by the tool.

#### 3.5.1 Resource configuration user interface software tool

This software is used to collect the architectural configurations from the partner and the working of this tool is explained by figure 3.3. It is in development stage, but once it is developed then partners can directly provide architectural configurations through a GUI which would in turn flood the database with values to the specific architectural parameter. So now instead of Parsing values through GUI we parse target configuration file to the software which would later on generate this target configuration file.

Now we use this software to integrate equations of the derived parameters and to calculate their values and also query the values of directly mapped parameters.

Figure 3.3: Resource configuration user interface software tool flow

#### 3.5.2 Directly mapped parameters

Some of the architecture configuration parameters that are to be included in the RIS tool yaml file can be directly mapped to the parameters in target configuration file with just the names of both parameters being different. Some examples of such directly mapped parameters are shown in figure 3.4.

For these parameters we need to query the database of the tool for the values of target config parameter and to generate the yaml file we need to map that value fetched by querying with the corresponding RIS tool parameter. Example: We query the database of the tool to find value for cpu.has\_el3 which comes out to be TRUE. Then we need to assign this value that is TRUE to

cpu[0].exceptLevel.MonitorPrivLevel.present that is the name of RIS tool parameter. And print cpu[0].exceptLevel.MonitorPrivLevel.present = TRUE in tool acceptable format and order. This mappings file is in CSV (Comma Separated Value) format. The tool uses CSV parser to read this mappings file given as command line input.

| RIS Tool Parameters                            | Target_Config_Parameters |  |  |

|------------------------------------------------|--------------------------|--|--|

| cpu[0].excepLevel.MonitorPrivLevel.present     | cpu.has_el3              |  |  |

| cpu[0].excepLevel.MonitorPrivLevel.rw32Support | cpu.has_el3_32           |  |  |

| cpu[0].excepLevel.MonitorPrivLevel.rw64Support | cpu.has_el3_64           |  |  |

| cpu[0].excepLevel.HypervisorPrivLevel.present  | cpu.has_el2              |  |  |

Figure 3.4: Directly mapped parameters example

### 3.5.3 Derived parameters

```

uint32 t Mask 12 3 = 0x1FF8;

uint32 t Mask 27 13 = 0xFFFE000;

uint32 t sys.16 icache sets

= ((cpu0.L6 ICACHE CCSIDR RESET) & (Mask 27 13)) >> 13 + 1;

sys.16 icache sets.attribute

= { (usr var, 0), (raven var, 1), (alias, "cpu.cache.cacheLevel.l6Cache.IcacheSet") };

uint32_t sys.16_icache_ways

= ((cpu0.L6_ICACHE_CCSIDR_RESET) & (Mask_12_3)) >> 3 + 1 ;

sys.16 icache ways.attribute

= { (usr var, 0), (raven var, 1), (alias, "cpu.cache.cacheLevel.16Cache.IcacheWays") };

uint32 t sys.16 icache linelen = ((cpu0.L6 ICACHE CCSIDR RESET & 0x7) + 4);

sys.l6_icache_linelen.attribute = {(usr_var, 0), (raven_var, 1), (lib_name, RAVEN)};

= ((sys.16 icache sets) * (sys.16 icache ways) * (1 << sys.16 icache linelen)) ;

uint32 t sys.16 icache size

= { (usr var, 0), (raven var, 1), (alias, "cpu.cache.cacheLevel.l6Cache.IcacheSize") };

sys.16 icache size.attribute

```

Figure 3.5: Example Equations

Some of the architecture configuration parameters that are to be included in the RIS tool yaml file can be derived from parameters in target configuration file with the help of some equations as shown in figure 3.5. These equations needs to be integrated in the Resource configuration user interface software tool. The example of some equations is as above. In this example icache sets, ways ,line length and cache size is derived from the value of the CCSIDR Register (Current Cache Size ID Register).

## CCSIDR, Current Cache Size ID Register

The CCSIDR characteristics are:

#### Purpose

Provides information about the architecture of the currently selected cache.

Figure 3.6: CCSIDR Register [7]

Different bit fields of the CCSIDR Register give us information about different features of cache. The detailed description of bit fields is as shown in figure 3.7. This description is available in Architectural Reference Manual [7]. And by studying it various equations can be derived for derived parameters as stated above.

Here the bit field [2:0] of the CCSIDR Register gives us information of the cache linesize. So if we have the information of the CCSIDR register and if we want to calculate linesize we need to follow reverse process. For example if the value of CCSIDR [2:0] is 1 then we need to write and equation that would add 4 to the value of bit field from bit 2 to 0 and then take an antilog with binary as base that is 2 thus the result obtained is nothing but the number of bytes in a cache line that is the linesize of a cache.

Similarly number of sets is given by bitfield [27:13] and associativity that is bitfields [12:3] is the number of ways cache lines can be arranged into. From all these parameters we can also find the cache size as it is the multiplication of cache linesize, cache sets and also cache ways.

#### 3.5.4 Structure of Unified Target Configuration Tool

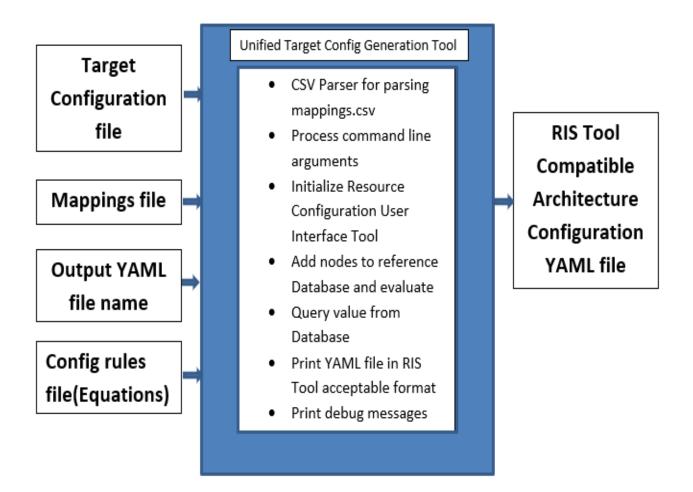

This Unified Target Configuration generation tool is a python based tool for the auto generation of architecture configuration yaml file in RIS tool acceptable format. This tool takes the mappings file, target configuration file and the an optional name of output yaml file. Then it parses these three command line arguments provided while executing the python script using argparser module. Now these command line arguments are processed. The mappings file which describes the directly mapped parameter is given in CSV format so it is parsed using CSV parser module.

The target configuration file is used to initialize resource configuration user

#### **Field descriptions**

The CCSIDR bit assignments are:

| 31 28   | 27 13   | 3 12 3        | 2 0      |

|---------|---------|---------------|----------|

| UNKNOWN | NumSets | Associativity | LineSize |

#### UNKNOWN, bits [31:28]

Reserved, UNKNOWN.

#### NumSets, bits [27:13]

(Number of sets in cache) - 1, therefore a value of 0 indicates 1 set in the cache. The number of sets does not have to be a power of 2.

#### Associativity, bits [12:3]

(Associativity of cache) - 1, therefore a value of 0 indicates an associativity of 1. The associativity does not have to be a power of 2.

#### LineSize, bits [2:0]

(Log<sub>2</sub>(Number of bytes in cache line)) - 4. For example:

For a line length of 16 bytes:  $Log_2(16) = 4$ , LineSize entry = 0. This is the minimum line length.

For a line length of 32 bytes:  $Log_2(32) = 5$ , LineSize entry = 1.

Figure 3.7: CCSIDR Register field description [7]

interface tool. While initialization the tool is built and the values of target configuration parameters is stored into the tool database and also the derived parameters are calculated with the help of equation integrated into the software. Now this database is being queried to get the values of the required parameters and finally an output yaml file is generated in RIS tool acceptable format. The block diagram of tool structure for the unified configuration generation tool is shown in figure 3.8. Some debug messages are also printed depending on the verbosity level that we have given to the resource configuration user interface tool.

An extra added feature is that we can include the equations for the derived parameters in a file and pass these equations to the tool. Thus this feature enables to directly calculate the derived parameters from the equations without the need for explicitly re-building the resource configuration user interface tool. Thus this tool provides a functionality to directly add the equations to the reference database of the resource configuration user interface tool.

Figure 3.8: Flow of tool for RIS tool input architecture config YAML file generation

Thus with the help of this tool we get a single automated application which generates RIS tool acceptable input configuration file and that too without changing present format. But since we know that the RIS tool specific YAML file and the target configuration file cannot be mapped fully with each other thus this tool can auto generate the RIS tool specific YAML file only upto 90 to 95 percentage and the remaining RIS tool specific details such as its memory map parameter info is required to be added explicitly.

# Chapter 4 MP RIS TOOL

### 4.1 Introduction

An SOC (System On Chip) can contain multiple clusters of processors and verification of such multi core environments is a big challenge, as the bugs are difficult to find and are often found late in the design cycle. There are different approaches to multicore verification and one of them is a Random Instruction Stream (RIS) generator tool. Here we would be talking about Arms own MP RIS tool developed by engineers of Architecture & Technology Group which uses a testing approach to target memory subsystem components critical to multicore functionality, such as Cache and Memory Hierarchy, cross-core coherency transactions, and the Load Store pipeline [10].

The verification of a processor having multiple core design is becoming more and more challenging due to the increasing complexity in the design of processor, weakly ordered memory, bus protocols, and presence of multiple levels i.e. multiple hierarchies of caches in memory subsystem. Arm architecture also defines some attributes and characteristics which are required to support devices and memory in system memory map which would further increase the complexity. Making the memory consistent and coherent is a key issue which needs to be addressed as different processors access same shared memory locations. As an example a unified or shared cache and update a single shared address space. The possibility of incoherence arises if there are multiple actors with access to caches and memory. Thus there are chances that they might access same address location. In modern systems, these actors are DMA engines, processor cores, and external devices which are able to read and/or write to caches and memory [11]. Thus we need to maintain a system that is coherent by observing same value for any particular address.

The MP RIS tool generates the output in the form of native Arm executables. The source file obtained from the generator is compiled using Arm assembly tool-chain. Then these test sequences generated are intended to run in a top-level simulation based environment. The MP RIS generator provides the functionality to the user to control many aspects of the test which includes: Deciding upon the number, location and also the size of address spaces. It also allows the mix of instructions that will operate on the defined memory regions. Now these memory regions are also configurable so that the same regions can be shared between the Processing Elements (PEs). To allow such sharing we need to define address constraints to trigger various sharing scenarios and invoke snoops and cache-line migrations. The sharing scenarios are predefined in the form of assembly sequences and they are divided into various zones [9].

## 4.2 Features of MP RIS Tool

MP RIS tool focuses on memory sub-system operations and cross-PE coherency transactions in Multi-Processor/Cluster systems. It is a static RIS generator and known for achieving higher generation rate i.e. greater than 1000 Instructions Per Second (IPS). It offers full support of ARM v8-A AArch64 execution state. The AArch32 A32 (ARM) ISA is partially supported, and no support is available for AArch32 T32 (Thumb) ISA. Instruction recipes i.e. the test cases targeting to test some particular intent or some particular feature of the processor design are predefined and the logic is embedded into the tool. Thus we can functionally verify specific operations and micro-architectural features [10].

The features targeted by the MP RIS Tool are:

- Multi-processor memory coherency.

- Barriers.

- Cache and TLB maintenance operations.

- Message passing (Exclusive operations, Load Acquire or Store Release, Atomics).

- Load-store dependencies and hazards.

- Generate traffic to maximize use of load-store pipeline and evictions.

### 4.3 Test Topology

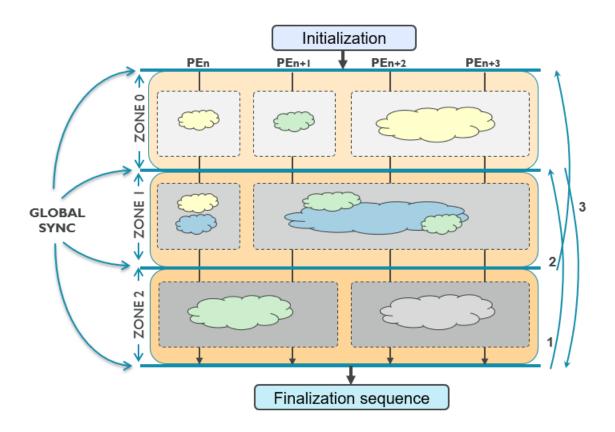

The threads executed by PEs are partitioned into equal number of zones. The transition between two zones is called global synchronization point as shown in figure 4.1. A zone or iteration specifies the number of 'independent' test sections

within the test case. Within each test section there is register initialization, pointer register setup, data tables and comparison tables [9]. In each such test section i.e. inside each zones there are scenarios. Scenarios are nothing but threads associated with memory dependencies. So inside each scenarios there is memory dependencies between different PEs.

Figure 4.1: RIS tool test topology

. The MP RIS tool provides functionality to configure memory share percentage between PEs in different scenarios. All PEs are synchronized in time both at the beginning and also at the end of each zone. The initialization sequence is used to set up the test environment, and the finalization sequence simply does the clean up task. The intent of MP RIS Tool is mainly to generate stimulus that creates interesting bus traffic between PEs within a memory subsystem. The sequence of events for test generation is:

- Initialization sets up the test environment.

- Threads execute in each PE.

- All threads synchronize globally.

- Partition the test flow into Zones.

- Zone order defines the initial test sequence.

- Scenarios include one or more PEs. Scenarios define memory dependencies between PEs.

- Re-execution of Zones in a random order.

- Finalization sequence performs clean up.

There is an optional (configurable) re-execution of the zone, or even the entire testcase. This re-execution helps in stressing the timing relations between the cores and caches that are cold in the first pass, and warm in the second pass.

The generator itself is written in C++, accompanied by a host of libraries in Python, Arm Assembly, and XML utils. The ouput of the tool is a testcase in Arm assembly format. It also produces associated files required to assemble and link the testcase into an Executable and Linkable Format (ELF) file. Modern RTL simulators can consume these ELF files as a memory-resident image during simulation.

## 4.4 Design Configuration

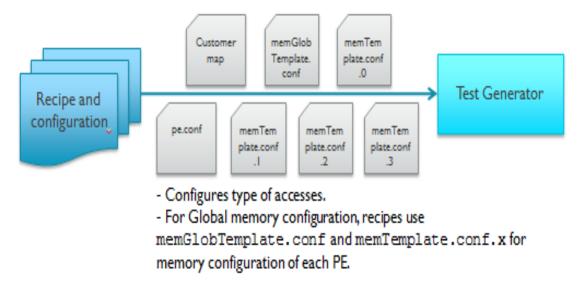

The target designs configuration is the first input to the tool, in the form of files in a user-defined configuration directory (config-dir). They have the files as in figure 4.2 and figure 4.3:

Figure 4.2: Design configuration files

#### • Customer Map:

The target designs physical memory map, with regions dedicated for I/O, peripherals, ROM, Interrupt Controller etc. The available regions excluding the above regions are where the MP RIS Tool places its test data pages.

• pe.conf:

Specifies the system configuration of the target design. It has inputs for number of clusters, number of PEs in each cluster, L1/L2/L3 cache parameters, feature enables, architecture etc.

• Overrides:

Override files for recipe knobs.

## 4.5 **RIS** Tool Recipes

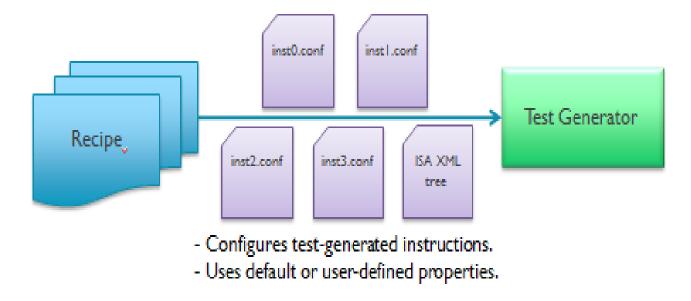

The tools inputs are configuration files, and the Armv8 ISA specified in XML format. The configuration files are organized as recipes that define the intent of the test. A recipe specifies the design space that the test targets, and provides maximum possible coverage in that space through knob randomization. Different generation runs of the recipe yield test cases that take in different combinations of the same knobs, that provide uniqueness in their own ways, and stress the same piece of logic

Figure 4.3: Recipe design configuration

from ever-so-slightly different angles. A recipe includes instruction configuration files and memory configurations for every core and global memory configuration file that can be used to tune the instruction stream. The memory configuration files specify bias for different Armv8 memory attributes, cache indexing, page crossing, cacheline crossing etc.

The tool also provides an override capability for these files, so users can specify an overriding value for specific or a set of knobs, to be fixed for the entire regression while other knobs are randomized. Users can generate tests using recipe categories in accordance with the maturity of their RTL design. The MP RIS Tool offers several regression script options for a convenient test-generation process.

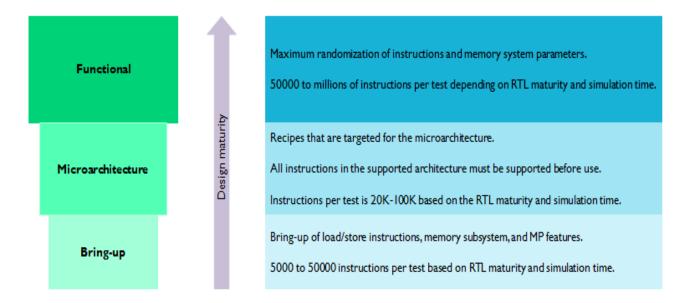

Recipes are organized into three categories bring-up, functional, and microarchstress. A block level view is as shown in figure 4.4

#### 4.5.1 Bring-up Recipes

These recipes focus on the initial bring-up of load and store instructions, the memory subsystem and basic data-side MP features. These are the first set of MP RIS Tool recipes the user will focus on with the generated tests ranging between 5,000 and 50,000 instructions depending on design maturity and available resources.

Figure 4.4: Recipe Types

#### 4.5.2 Micro-architecture Recipes

These recipes are focused on distinct features in the architecture with the expectation that all available instructions and memory features are implemented and verified at unit level. Architectural features that are addressed include EL switching, exercising different features in the MMU, and interleaving various types of instructions so as to create hazards and address dependencies. These are the second set of recipes the user will focus on with the generated tests ranging between 20,000 and 100,000 instructions depending on design maturity and available resources.

#### 4.5.3 Functional Recipes

Functional recipes are the final set of MP RIS Tool tests for the user to concentrate on since they are intended for mature designs. These recipes are expected to be used with tests ranging from around 50K to 1M plus instructions in length and focus on maximally randomizing the instructions and memory parameters.

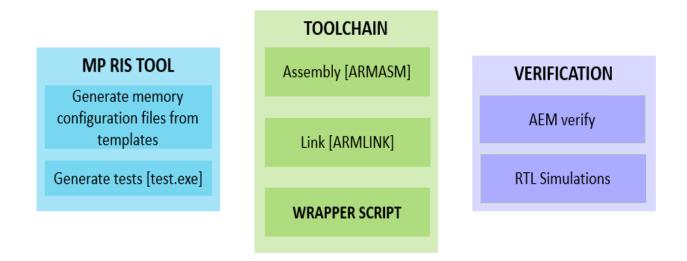

### 4.6 Test Generation Process

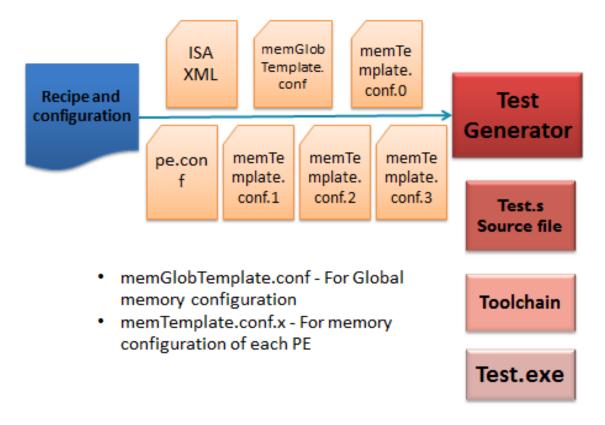

The output from the generator is an assembly test file, and a scatter file that specifies addresses in the physical memory for ELF loading by the linker. The final

Figure 4.5: Test generation process

ELF is created after assembling and linking these files. The components involved are as shown in figure 4.5

The installation of the MP RIS Tool provides a tool binary (.exe) and a tool wrapper script. The binary generates the assembly and scatter files associated with a test. However, to generate an ELF file that can be run in simulation, an additional step is required to assemble and link the files output by the tool binary file. Thus, generating a test ELF file involves 2 steps:

- 1 Invoke MP RIS Tool binary to generate the tests assembly and scatter file.

- 2 Invoke the ARM assembler and linker to build an ELF test file.

Moreover, the resulting ELF test can be disassembled which becomes useful for debugging purposes. The wrapper script provided with the installation combines the steps above into a single operation. The detailed explanation of working of the wrapper script is provided in next section.

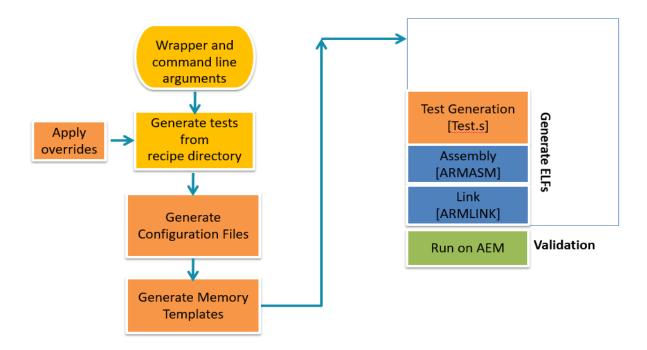

### 4.7 RIS Tool Wrapper

The MP RIS Tool wrapper is a shell script for the RIS/Verification tool. Its intent is to orchestrate the steps needed to configure, run and analyze a MP RIS

Figure 4.6: MP RIS tool Block Diagram

Tool regression from test generation to results validation. The wrapper allows a user to configure knobs that pertain to recipe values that influence test generation. A user can specify one set of knob values to one or more recipes or allow the MP RIS Tool wrapper to randomize knob values for them. The wrapper script provides a command-line interface that allows the user to control test generation by selecting recipes and parameters that define the intent, topology and size of the test.

The wrapper script manages the following:

- Environment setup

- Memory / Configuration setup

- Test Generation

- Assembly

- Linking

Figure 4.7: MP RIS tool Block Diagram

- AEM Verification

- Post test Validation MP RIS Tool QA

The MP RIS Tool wrapper can override a design configuration. For that we need to specify a path to configuration directory that contains required files. The wrapper will use the values specified in these files in the place of the default values. The configuration override directories are required to have the following files:

- customer\_map

- glob\_override.conf

- memGlob\_override.conf

- pe.conf

Thus this wrapper script is used to invoke all the procedures in a proper predefined sequence for generating the test case. Ablock level view of all the components involved is shown in figure 4.6. It reads the recipe directory for basic configuration of knobs. These knobs are overwritten if the same knobs are present in the override.conf file. Now the final list of knobs and their values is overwritten by the config files. Then by using these knobs and assigning some particular value to these knobs the MP RIS Tool generates a test case containing sequence of instructions. These generated test cases are in the form of a source file i.e. .s file which needs to be assembled and linked further to generate an ELF file and this is done using Arm assembly and linking tools. Now this generated ELF file is used to verify the AEM model and also the RTL design of the processor as also explained by figure 4.7. Thus this MP RIS Tool proves to be efficient to cover the corner cases for a multicore environment. This tool also requires some Quality Assurance mechanism to keep a check on the quality of the generated test cases. The already available QA tool and the newly developed plugins for QA are discussed in upcomming chapters.

### Chapter 5

# PREGENERATION QA -RECIPE QA

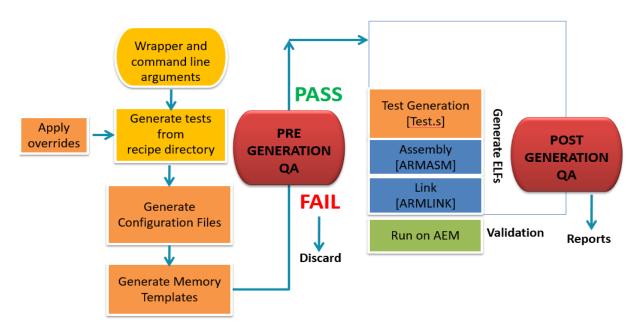

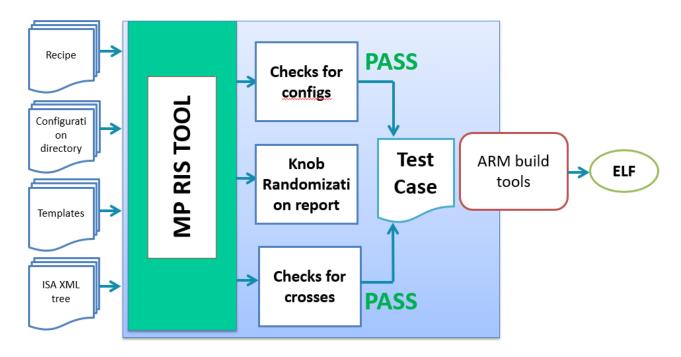

### 5.1 Introduction

It is a tool that performs trace-based QA checks on MP tests from the MP RIS generator and measures test intent to help to tune generation. It also points to test issues that could potentially cause the Device Validation teams to pursue debug of a false failure. Thus as a result it increases quality of MP RIS tests used for validation and in turn decreases the probability of post-silicon bugs.

Figure 5.1: MP RIS Tool temp directory structure

The Pre-generation tool script is integrated with the wrapper script and is

called by the wrapper script after it generates the final set of knobs and corresponding values after applying all the overrides. Figure 5.1 shows where the pre-generation as well as the post generation tools are included in the execution cycle of the MP-RIS Tool. The pre-generation QA i.e. the recipe QA is divided into 3 phases as explained by figure 5.2:

- Checks for configs

- Checks for crosses

- Knob randomization report

Figure 5.2: MP RIS Tool temp directory structure

Now the MP RIS tool takes various parameters from the users like the name of recipe, the config which is to be applied i.e. the path to config directory, test count etc. And then the MP RIS Tool applies all these overrides and generates a final list of knobs and their corresponding value to generate tests. Thus for each test it creates a temporary directory and this test can belong to any recipe thus the MP RIS Tool put this test directory inside a recipe directory to which it belongs.

Inside every test directory we have the basic recipe config directory which gives the basic set of knobs for that particular recipe. Now this knobs are overwritten by the \_override.conf files to give a final list of knobs and values. If the config directory is specified by the user then the knobs and values present in the config directory are also considered for overwriting the final list of knobs. The final list of knob and values taken by the MP RIS tool is not dumped anywhere and it just does the overrides on the fly during run time.

| [khusun01@login4 /arm/projectscratch/pd/metl/khusun01/bakup/re<br>[khusun01@login4 /arm/projectscratch/pd/metl/khusun01/bakup/re<br>batch 1.lsf el_switch evict_ildst l<br>datapload_stcmoirr el_switch_el2 evict_scale n<br>dos_strex_ronce_sameidx evict_cmoirr interleaved_spr_seq n<br>[khusun01@login4 /arm/projectscratch/pd/metl/khusun01/bakup/re<br>[khusun01@login4 /arm/projectscratch/pd/metl/khusun01/bakup/re<br>7_uao_v8_2_a64_np4_nz4_ni500_sh100_re1_2424180454_le_21112017<br>9_uao_v8_2_a64_np4_nz4_ni500_sh100_re1_1134313636_le_21112017<br>[khusun01@login4 /arm/projectscratch/pd/metl/khusun01/bakup/re<br>ni500_sh100_re1_2424180454_le_21112017/<br>[khusun01@login4 /arm/projectscratch/pd/metl/khusun01/bakup/re<br>sh100_re1_2424180454_le_21112017] [s | <pre>cipeQA/anvil_2017T121235418]\$ ls .ogs nstore_stb stb_stress vipt_loadstore vipt_meon vipt_meon vipt_meon vipt_exipeQA/anvil_20171121235418]\$ cd uao/ cipeQA/anvil_20171121235418/uao]\$ ls elfs knob_randomization ccipeQA/anvil_20171121235418/uao]\$ cd 7_uao_v8_2_a64_np4_nz4_ </pre> |  |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | customer map memGlob override.conf                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| anvil.disasm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | glob override.conf mem override.conf.0                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

| anvil.elf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | instr override.conf mem override.conf.1                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| anvil.exe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | lib anvil pgedit.a mem override.conf.2                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

| anvil.o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | lib anvil pgt.a mem override.conf.3                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| anvil aem.tarmac                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | lib bootswc.a pe.conf                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| anvil asm.log                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | lib bootswc common.a pg.dat                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| anvil gen.log                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | lib handlers.a pg.h                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| anvil link.log                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | lib_intrhand.a pg.hs                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| cloud bias.conf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | lib swc.a pg.s                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| confTemplate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | lib uhandler.a pg.scat                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

| config checks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | load file ns recipe-config                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| crosses checks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | load file s                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| [khusun01@login4 /arm/projectscratch/pd/metl/khusun01/bakup/re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| sh100 rel 2424180454 le 21112017]\$ cd recipe-config/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| [khusun01@login4 /arm/projectscratch/pd/metl/khusun01/bakup/re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | cipeQA/anvil 20171121235418/uao/7 uao v8 2 a64 np4 nz4 ni500                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| sh100 rel 2424180454 le 21112017/recipe-config]\$ ls                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |