# Power and Leakage Saving Technique in Memory

Major Project Report

Submitted in partial fulfillment of the requirements for the degree of

Master of Technology In Electronics & Communication Engineering (VLSI Design) By Prachi Vyas (17MECV17)

Electronics & Communication Engineering Department Institute of Technology Nirma University Ahmedabad - 382 481 May,2019

# Power and Leakage Saving Technique in Memory

Major Project Report

Submitted in partial fulfillment of the requirements for the degree of

Master of Technology

In

Electronics & Communication Engineering (VLSI Design)

By

Prachi Vyas (17MECV17)

Under the Guidance of

## **Internal Guide**

## External Guide

Dr. N M Devashrayee Professor (VLSI Design) Nirma University Mr. Naveen Batra Engineering Manager Synopsys India Pvt Ltd.

Electronics & Communication Engineering Department Institute of Technology Nirma University Ahmedabad - 382 481 May, 2019

## Declaration

This is to certify that

- The thesis comprises my original work towards the degree of Master of Technology in VLSI Design at Nirma University and has not been submitted elsewhere for a degree.

- 2. Due acknowledgment has been made in the text to all other material used.

Prachi Vyas (17MECV17)

## Certificate

This is to certify that the Major Project entitled **"Power and Leakage Saving Technique in Memory"** submitted by **Prachi Vyas (17MECV17)**, towards the partial fulfillment of the requirements for the degree of Master of Technology in VLSI Design, Nirma University, Ahmedabad is the record of work carried out by her under our supervision and guidance. In our opinion, the submitted work has reached a level required for being accepted for examination. The results embodied in this major project, to the best of our knowledge, haven't been submitted to any other university or institution for award of any degree or diploma.

Dr N. M. Devashrayee Internal Guide Dr N. M. Devashrayee PG Coordinator (VLSI Design)

Dr D. K. Kothari Head, EC Dept. Dr Alka Mahajan Director, IT - NU

Date :

Place : Ahmedabad

## Acknowledgment

Let me take the opportunity to express my deep regards to Mr. Naveen Batra (Project Manager) for assigning me such project and providing his guidance and constant encouragement during the project. I would also like to thank Mr. Rohit Sharma (Mentor) for his guidance, help and inspiring me to put my best efforts.

I would like to express my gratitude & sincere thanks for generous assistance to my guide Dr. N M Devashryee, Professor, VLSI Design, Institute of Technology, Nirma University, Ahmedabad for his guidance and constant encouragement during my course of project. Special thanks to all faculties who has always been an inspiration and guided us with their experience.

I would like to express my gratitude towards my parents for constant support and encouragement in life. I also wish to express my heartfelt appreciation to my friends and colleagues at Intel who have rendered their support throughout my project, both explicitly and implicitly.

> - Prachi Vyas (17MECV17)

#### Abstract

The performance and cost of an ASIC depends heavily on the quantity and quality of embedded SRAM included in the design. SRAM memory, there are still several options available to configure the memory instances to dramatically reduce cost or improve performance. If these configuration options are either unavailable in the memory compiler or are not chosen properly, the overall design will suffer. Power and Leakage plays a major role to check the product quality before it goes to market. While advanced Pre-Si Quality Assurance checks can catch design errors, it can miss physical bugs which can only be identified by Post-Si validation. Today, low power memory is given most priority in VLSI design. Low power feature for on-chip SRAMs is becoming increasingly important, especially for battery-operated portable application. So, the power reduction for one cell is the vital role in memory design techniques. As the technology growing portable device (e.g. Cell phone, PDA) increases, the Static Power Consumption (Leakage Power) and dynamic power became a significant issue. Leakage current in standby mode is the major part of power loss. SRAM continues to be an important macro block of SoCs. There is some technique through which we can reduce the power dissipation like by using dualrail voltage, address decoding schemes, assist technique, by applying different rmi settings, power gating, etc. Analyzing the memory operation by applying different power supply to periphery and array by inserting level shifter in design and read and write margin is very important to achieve also done some analysis by changing wordline and bitline voltage and try to reduce leakage in memory and also analyze the 6T SRAM parameters and 6T SRAM with different schemes to achieve less leakage and power.

This thesis outlines the architecture of the Memory Chips and its Design Flow and how the efficient methodologies have been proposed for reducing leakage current and Power in Memory design. Its built to check behavior of chip with the different technology on die. The thesis will focus more on the various approaches used for Pre-Silicon Power and Leakage Saving strategy for the Memory based Designs and extend the lifetime of digital circuits.

# **Table of Contents**

|   | A    | ostract                                        | i  |

|---|------|------------------------------------------------|----|

|   | Та   | ble of Contents                                | v  |

|   | Li   | st of Table                                    | vi |

|   | Li   | st of Figures                                  | ix |

|   | Li   | st of Abbreviation                             | X  |

| 1 | Intr | oduction                                       | 1  |

|   | 1.1  | 4T SRAM cell with Polysilicon Resistor Load    | 2  |

|   | 1.2  | Conventional SRAM                              | 3  |

|   | 1.3  | SRAM Design parameters                         | 5  |

|   |      | 1.3.1 Read current                             | 5  |

|   |      | 1.3.2 Leak current                             | 6  |

|   |      | 1.3.3 Flip time                                | 6  |

|   |      | 1.3.4 Static Noise Margin (SNM)                | 7  |

|   |      | 1.3.5 SRAM SNM and Operating Voltage Variation | 8  |

|   | 1.4  | Disadvantages of 6T SRAM                       | 9  |

|   | 1.5  | Motivation                                     | 10 |

|   | 1.6  | Objectives                                     | 10 |

|   | 1.7  | Overview of the Thesis                         | 11 |

| 2 | Lite | rature Survey                                  | 12 |

|   | 2.1  | Introduction to Compiler                       | 12 |

|   | 2.2  | High Speed Memory Compiler                     | 13 |

| 2.3                                                                                                                                            | Monte                                                                                                  | Carlo Simulation                                                                                                                                                                                                                                                                              | 16                                                                                                                                                                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                | 2.3.1                                                                                                  | Global and Local MC                                                                                                                                                                                                                                                                           | 17                                                                                                                                                                                                                                                       |

| 2.4                                                                                                                                            | Memor                                                                                                  | y Architecture Blocks                                                                                                                                                                                                                                                                         | 18                                                                                                                                                                                                                                                       |

|                                                                                                                                                | 2.4.1                                                                                                  | SRAM Design                                                                                                                                                                                                                                                                                   | 19                                                                                                                                                                                                                                                       |

|                                                                                                                                                | 2.4.2                                                                                                  | Precharge Circuit                                                                                                                                                                                                                                                                             | 19                                                                                                                                                                                                                                                       |

|                                                                                                                                                | 2.4.3                                                                                                  | Sense Amplifier                                                                                                                                                                                                                                                                               | 20                                                                                                                                                                                                                                                       |

|                                                                                                                                                | 2.4.4                                                                                                  | Write Driver                                                                                                                                                                                                                                                                                  | 22                                                                                                                                                                                                                                                       |

|                                                                                                                                                | 2.4.5                                                                                                  | Address Decoding Schemes in Memory                                                                                                                                                                                                                                                            | 23                                                                                                                                                                                                                                                       |

|                                                                                                                                                | 2.4.6                                                                                                  | Timing control schemes                                                                                                                                                                                                                                                                        | 24                                                                                                                                                                                                                                                       |

|                                                                                                                                                | 2.4.7                                                                                                  | Muxing and Banking                                                                                                                                                                                                                                                                            | 25                                                                                                                                                                                                                                                       |

|                                                                                                                                                | 2.4.8                                                                                                  | Level Shifter                                                                                                                                                                                                                                                                                 | 25                                                                                                                                                                                                                                                       |

|                                                                                                                                                | 2.4.9                                                                                                  | Corebias                                                                                                                                                                                                                                                                                      | 26                                                                                                                                                                                                                                                       |

|                                                                                                                                                | 2.4.10                                                                                                 | Level Detector                                                                                                                                                                                                                                                                                | 27                                                                                                                                                                                                                                                       |

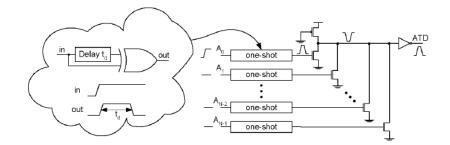

|                                                                                                                                                | 2.4.11                                                                                                 | Address Transition Detector                                                                                                                                                                                                                                                                   | 28                                                                                                                                                                                                                                                       |

|                                                                                                                                                | 2.4.11                                                                                                 |                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                          |

| N                                                                                                                                              |                                                                                                        |                                                                                                                                                                                                                                                                                               | 20                                                                                                                                                                                                                                                       |

|                                                                                                                                                | nory Rea                                                                                               | ad and Write Margin                                                                                                                                                                                                                                                                           | 29                                                                                                                                                                                                                                                       |

| <b>Men</b><br>3.1                                                                                                                              | nory Rea                                                                                               |                                                                                                                                                                                                                                                                                               | <b>29</b><br>29                                                                                                                                                                                                                                          |

|                                                                                                                                                | nory Rea<br>Memor                                                                                      | ad and Write Margin                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                          |

| 3.1<br>3.2                                                                                                                                     | nory Rea<br>Memor<br>Memor                                                                             | ad and Write Margin y Read Operation                                                                                                                                                                                                                                                          | 29                                                                                                                                                                                                                                                       |

| 3.1<br>3.2                                                                                                                                     | nory Rea<br>Memor<br>Memor                                                                             | ad and Write Margin<br>y Read Operation                                                                                                                                                                                                                                                       | 29<br>31                                                                                                                                                                                                                                                 |

| 3.1<br>3.2<br>Basi                                                                                                                             | nory Re:<br>Memor<br>Memor<br>c of Pow<br>Power                                                        | ad and Write Margin<br>y Read Operation                                                                                                                                                                                                                                                       | 29<br>31<br><b>33</b>                                                                                                                                                                                                                                    |

| <ul> <li>3.1</li> <li>3.2</li> <li>Basi</li> <li>4.1</li> <li>4.2</li> </ul>                                                                   | nory Rea<br>Memor<br>Memor<br><b>c of Pow</b><br>Power<br>Leakag                                       | ad and Write Margin   y Read Operation   y Write Operation <b>ver Leakage</b> e Current in Sub-Micrometre Gate                                                                                                                                                                                | <ul> <li>29</li> <li>31</li> <li><b>33</b></li> <li>33</li> <li>35</li> </ul>                                                                                                                                                                            |

| <ul> <li>3.1</li> <li>3.2</li> <li>Basi</li> <li>4.1</li> <li>4.2</li> </ul>                                                                   | nory Rea<br>Memor<br>Memor<br><b>c of Pow</b><br>Power<br>Leakag                                       | ad and Write Margin   y Read Operation   y Write Operation                                                                                                                                                                                                                                    | <ul><li>29</li><li>31</li><li><b>33</b></li><li>33</li></ul>                                                                                                                                                                                             |

| <ul> <li>3.1</li> <li>3.2</li> <li>Basi</li> <li>4.1</li> <li>4.2</li> </ul>                                                                   | nory Rea<br>Memor<br>Memor<br>c of Pow<br>Power<br>Leakag                                              | ad and Write Margin   y Read Operation   y Write Operation <b>ver Leakage</b> e Current in Sub-Micrometre Gate                                                                                                                                                                                | <ul> <li>29</li> <li>31</li> <li><b>33</b></li> <li>33</li> <li>35</li> </ul>                                                                                                                                                                            |

| <ul> <li>3.1</li> <li>3.2</li> <li>Basi</li> <li>4.1</li> <li>4.2</li> <li>Tech</li> </ul>                                                     | nory Rea<br>Memor<br>Memor<br>c of Pow<br>Power<br>Leakag<br>niques t<br>Increas                       | ad and Write Margin   y Read Operation   y Write Operation   orer Leakage   e Current in Sub-Micrometre Gate   to reduce Power and Leakage in Memory                                                                                                                                          | <ul> <li>29</li> <li>31</li> <li>33</li> <li>33</li> <li>35</li> <li>38</li> </ul>                                                                                                                                                                       |

| <ul> <li>3.1</li> <li>3.2</li> <li>Basi</li> <li>4.1</li> <li>4.2</li> <li>Tech</li> <li>5.1</li> </ul>                                        | nory Rea<br>Memor<br>Memor<br>c of Pow<br>Power<br>Leakag<br>nniques f<br>Increas<br>Supply            | ad and Write Margin   y Read Operation   y Write Operation   y Write Operation <b>ver Leakage</b>                                                                                                                                                                                             | 29<br>31<br>33<br>35<br>38<br>38                                                                                                                                                                                                                         |

| <ul> <li>3.1</li> <li>3.2</li> <li>Basi</li> <li>4.1</li> <li>4.2</li> <li>Tech</li> <li>5.1</li> <li>5.2</li> </ul>                           | nory Rea<br>Memor<br>Memor<br>c of Pow<br>Power<br>Leakag<br>nniques f<br>Increas<br>Supply<br>Power S | ad and Write Margin   y Read Operation   y Write Operation   y Write Operation <b>ver Leakage</b>                                                                                                                                                                                             | 29<br>31<br>33<br>33<br>35<br><b>38</b><br>38<br>38<br>38                                                                                                                                                                                                |

| <ul> <li>3.1</li> <li>3.2</li> <li>Basi</li> <li>4.1</li> <li>4.2</li> <li>Tech</li> <li>5.1</li> <li>5.2</li> <li>5.3</li> </ul>              | nory Re:<br>Memor<br>Memor<br>C of Pow<br>Power<br>Leakag<br>Increas<br>Supply<br>Power S<br>Low Po    | ad and Write Margin   y Read Operation   y Write Operation   y Write Operation <b>rer Leakage</b>                                                                                                                                                                                             | 29<br>31<br>33<br>33<br>35<br><b>38</b><br>38<br>38<br>38<br>38                                                                                                                                                                                          |

| <ul> <li>3.1</li> <li>3.2</li> <li>Basi</li> <li>4.1</li> <li>4.2</li> <li>Tech</li> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> </ul> | nory Re:<br>Memor<br>Memor<br>C of Pow<br>Power<br>Leakag<br>Increas<br>Supply<br>Power S<br>Low Po    | ad and Write Margin   y Read Operation   y Write Operation   y Write Operation <b>ver Leakage</b> e Current in Sub-Micrometre Gate to reduce Power and Leakage in Memory ing Challenges of Power Voltage Reduction (Voltage Scaling) Saving Features in SRAM compilers ower design Techniques | 29<br>31<br><b>33</b><br>33<br>35<br><b>38</b><br>38<br>38<br>38<br>38<br>38<br>38<br>39                                                                                                                                                                 |

|                                                                                                                                                | 2.3                                                                                                    | 2.3.1<br>2.4 Memory<br>2.4.1<br>2.4.2<br>2.4.3<br>2.4.3<br>2.4.4<br>2.4.5<br>2.4.6<br>2.4.7<br>2.4.8<br>2.4.9                                                                                                                                                                                 | 2.3.1Global and Local MC2.4Memory Architecture Blocks2.4.1SRAM Design2.4.2Precharge Circuit2.4.3Sense Amplifier2.4.4Write Driver2.4.5Address Decoding Schemes in Memory2.4.6Timing control schemes2.4.7Muxing and Banking2.4.8Level Shifter2.4.9Corebias |

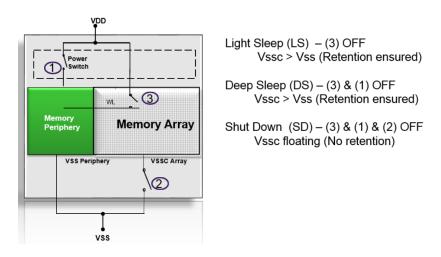

|    | 5.7    | Leakage during Power Modes                           | 42 |

|----|--------|------------------------------------------------------|----|

|    | 5.8    | Power Saving Features- CD/Bank/CM Selection          | 43 |

|    | 5.9    | Assist Techniques                                    | 44 |

|    |        | 5.9.1 Read Assist Technique                          | 44 |

|    |        | 5.9.2 Write Assist Technique                         | 45 |

|    | 5.10   | Level shifter (Dual Rail)                            | 46 |

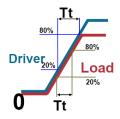

|    |        | 5.10.1 Tradeoff between Slope, Delay, and Leakage    | 47 |

|    |        | 5.10.2 Power Reduction by reducing Array Voltage     | 47 |

|    |        | 5.10.3 Power reduction by reducing periphery voltage | 48 |

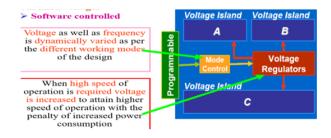

|    | 5.11   | Dynamic Voltage and Frequency Scaling                | 48 |

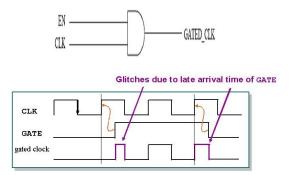

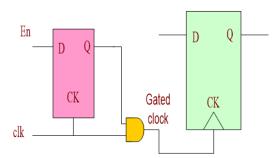

|    | 5.12   | Clock-Gating                                         | 49 |

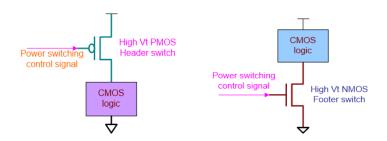

|    | 5.13   | Power-Gating Design                                  | 50 |

|    | 5.14   | Multi-Voltage Design (Multi-VDD)                     | 53 |

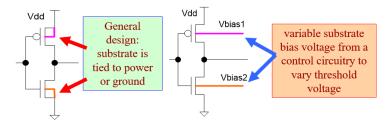

|    | 5.15   | Adaptive Body-Biasing (ABB)                          | 54 |

|    | 5.16   | Power-Aware Placement                                | 54 |

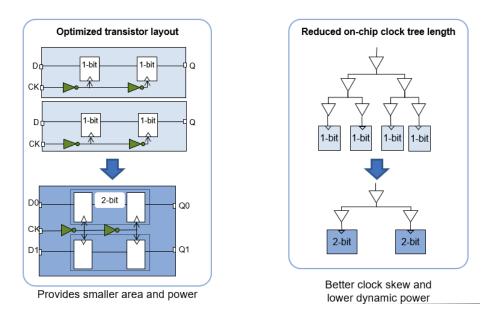

|    | 5.17   | Multibit Register Support                            | 54 |

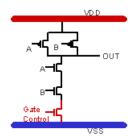

|    | 5.18   | Variable Threshold CMOS (VTCMOS)                     | 56 |

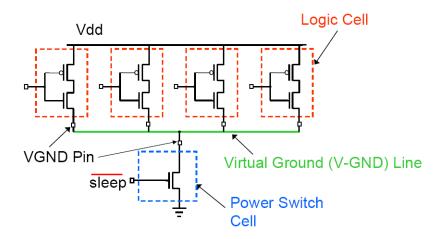

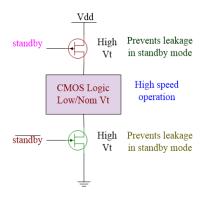

|    | 5.19   | Multiple Threshold CMOS (MTCMOS) Circuits            | 56 |

|    | 5.20   | RM Settings                                          | 56 |

| 6  | Resu   | lts                                                  | 59 |

|    | 6.1    | Conclusion                                           | 59 |

|    | 6.2    | Future Work                                          | 60 |

| Re | eferen | ces                                                  | 61 |

6

# **List of Tables**

| 2.4.1 Power Modes                                  | 26 |

|----------------------------------------------------|----|

| 5.4.1 Low Power Design Technique                   | 39 |

| 5.6.1 LS,DS and SD Modes                           | 41 |

| 5.7.1 Power and Leakage in LS, DS SD mode          | 43 |

| 5.7.2 Power and Leakage in LS, DS SD mode          | 43 |

| 5.9.1 Read Assist wl Driver                        | 45 |

| 5.9.2 Write Assist Modes                           | 45 |

| 5.10. Pass/Fail criteria by decrease array voltage | 48 |

| 5.10.2 Pass/Fail by reducing periphery voltage     | 48 |

| 5.20.1RM Settings Description                      | 57 |

| 5.20.2RM Settings Description                      | 58 |

| 6.1.1 Result                                       | 59 |

# **List of Figures**

| 1.1.1 4T SRAM cell with Polysilicon Resistor Load               | 2  |

|-----------------------------------------------------------------|----|

| 1.2.1 SRAM Cell (6T)                                            | 3  |

| 1.3.1 Iread in 6T SRAM                                          | 5  |

| 1.3.2 Ileake in 6T SRAM                                         | 6  |

| 1.3.3 SNM with VOH and VOL                                      | 8  |

| 1.3.4 6T SNM                                                    | 8  |

| 1.3.5 SRAM cell SNM deviation vs. bit line voltage              | 9  |

| 1.3.6 Read and Write safe and marginal regions of an SRAM cell  | 9  |

| 2.1.1 Compiler Architecture                                     | 13 |

| 2.3.1 Relationship between parameter verification and yield     | 16 |

| 2.4.1 Basic SRAM block Structure                                | 18 |

| 2.4.2 CR in SRAM                                                | 19 |

| 2.4.3 PR in SRAM                                                | 20 |

| 2.4.4 Precharge Circuit                                         | 20 |

| 2.4.5 Sense Amplifier                                           | 22 |

| 2.4.6 Write Drivers                                             | 22 |

| 2.4.7 4-1 pass transistor Column Decoder with a read predecoder | 23 |

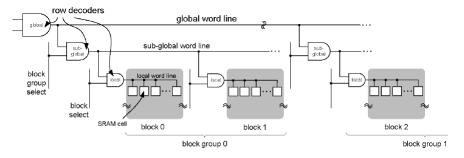

| 2.4.8 DWL HWD Multi-Stage Row Decoder Architectures             | 24 |

| 2.4.9 Delay line timing Loop and Replica timing Loop            | 24 |

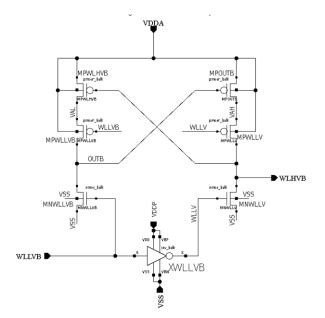

| 2.4.10Level Shifter                                             | 26 |

| 2.4.1 1Corebias                                                 | 27 |

| 2.4.12Address Transition Detector                               | 28 |

| 3.1.1 Memory Read Operation                          | 30 |

|------------------------------------------------------|----|

| 3.1.2 Memory Read Operation Measurement              | 30 |

| 3.2.1 Memory Write Operation                         | 31 |

| 3.2.2 Memory Write Operation Measurement             | 32 |

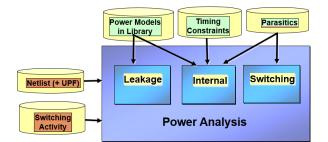

| 4.1.1 Power Analysis Requirement                     | 34 |

| 4.2.1 Leakage in MOS                                 | 35 |

| 4.2.2 DIBL                                           | 36 |

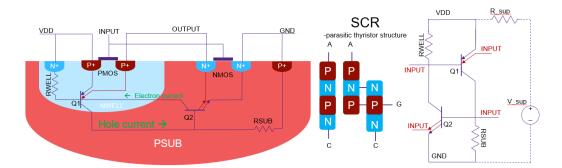

| 4.2.3 Latchup in CMOS                                | 37 |

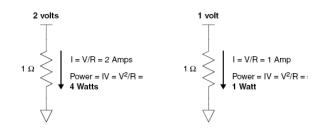

| 5.2.1 Voltage Scaling                                | 39 |

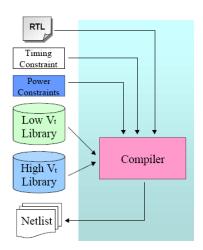

| 5.5.1 Multi-Vt Synthesis Flow                        | 40 |

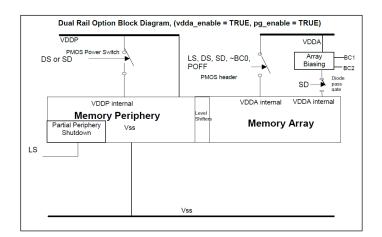

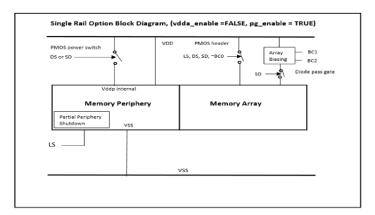

| 5.6.1 Dual Rail Block Diagram                        | 42 |

| 5.6.2 Single Rail Block Diagram                      | 42 |

| 5.8.1 Different Memory Design Wide and Tallest       | 43 |

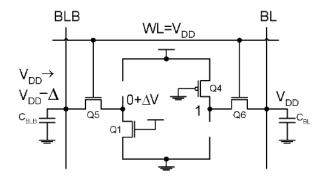

| 5.9.1 Write Assist Schematic                         | 46 |

| 5.9.2 Write Assist Negative Bump                     | 46 |

| 5.10. Level Shifter Driver and Load                  | 47 |

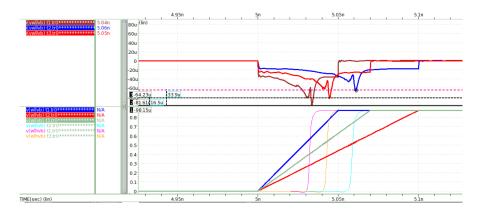

| 5.10.2 Leakage in Dual Rail (LS)                     | 47 |

| 5.11. DVFS                                           | 49 |

| 5.12. Latch free Clock Gating                        | 50 |

| 5.12.2 Latch based Clock Gating                      | 50 |

| 5.13. Power Gating                                   | 51 |

| 5.13.2 Fine Grain Topologies                         | 52 |

| 5.13.3Cross Grain Topologies                         | 52 |

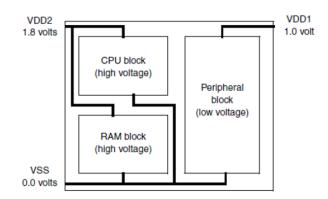

| 5.14. Multi Vdd                                      | 54 |

| 5.17. Multibit Registers                             | 55 |

| 5.18.1VTCMOS                                         | 56 |

| 5.19. IMTCMOS                                        | 56 |

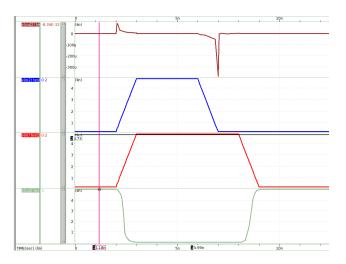

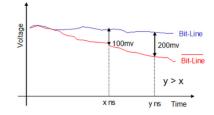

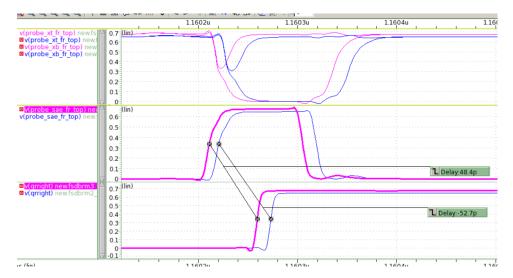

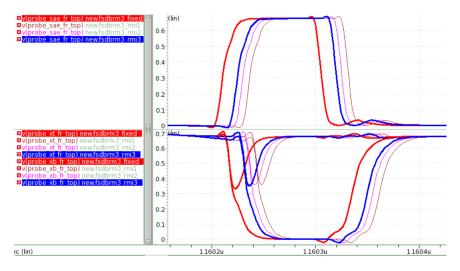

| 5.20. Woltage Vs Time Behaviour of Bit Lines Signals | 57 |

| 5.20.2 Read Margin Settings for Read Margin          | 58 |

| 5.20.3 Read Margin Internal Settings |  | . 58 |

|--------------------------------------|--|------|

|--------------------------------------|--|------|

## List of Abbreviation

| PMU  | - Performance Monitoring Unit       |

|------|-------------------------------------|

| IoT  | - Internet of Things                |

| HSSP | - High Speed Single Port            |

| MC   | - Monte Carlo                       |

| BIST | - Built in Self-Test                |

| WM   | - Write Margin                      |

| RM   | - Read Margin                       |

| PVT  | - Process, Voltage, and Temperature |

| SRAM | - Static Random-Access Memory       |

| HDSP | - High Density Single Port          |

| SoC  | - System on Chip                    |

| SNM  | - Static Noise Margin               |

| VLSI | - Very Large-Scale Integration      |

| DS   | - Deep Sleep Mode                   |

| LS   | - Light Sleep Mode                  |

| SAE  | - Sense Amplifier Enable            |

| DRAM | - Dynamic Random-Access Memory      |

| RPB  | - Row Per Column                    |

| CPS  | - Column per Segment                |

| DSM  | - Deep sub-micron                   |

| SA   | - Sense Amplifier                   |

| СМ   | - Column Muxing                     |

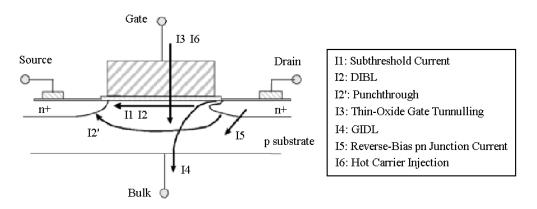

| DIBL | - Drain Induced Barrier Lowering    |

| GIDL | - Gate Induced Drain Lowering       |

| MB   | - Multi Bits                        |

| PG   | - Power Gating                      |

| SA   | - Sense Amplifier                   |

| WE   | - Write Enable                      |

| SD   | - Shut Down Mode                    |

|      |                                     |

# Chapter 1

## Introduction

Batteries power mobile devices and many electronic systems. In such systems, optimization of power is a key design constraint. System-on-chip (SoC) designers spend significant amounts of time trying to save battery life in such systems. Along with technology scaling down and higher operating speeds of CMOS VLSI circuits, the leakage power is getting enhanced. As process geometries are becoming smaller, device density increases and threshold voltage as well as oxide thickness decrease to keep pace with performance. Thus Static power consumption is a major concern in nanometer technologies. As memories occupy a larger and larger percentage of SoCs, it is imperative to select memories and memory compilers that provide flexible power management techniques. Power management within memories is key to continuing to extend the battery life, especially in all the mobile devices we use every day.

The embedded Static Random-Access Memory (SRAM) has become vital part of complex processors now days. The dominant area on chip is consumed by the memories. According to SIA road map, this area consumption will increase to 94% by 2014. One of the biggest advantages of SRAM over DRAM and other primary memories is its speed due to static storage. Similarly, the dissipation is the prime threat.

So, efforts should be made for designing and testing of new designs used on different technology on die and different methodology gives the reduction in power, leakage.

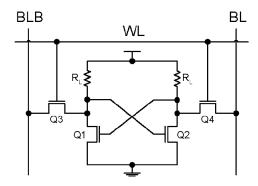

### 1.1 4T SRAM cell with Polysilicon Resistor Load

The main advantage of static 4t cells with polysilicon resistor load is the approximately 30% smaller area as compared to 6t SRAM cells. Due to higher electron mobility, all transistors in a PRL cell are normally NMOS. The load resistor serves to compensate for the off-state leakage of the pull-down devices. On one hand, the value of RL must be as high as possible to retain a reasonable noise margin NML, i.e., to limit the 0 level rise and reduce the static power consumptions. On the other hand, a high RL severely increase the low-to-high propagation delay if Vdd/2 precharge is used and it also increase the cell size. Furthermore, precharging the bit lines to Vdd/2 can compromise the cell stability with scaling of the Vdd/Vth ratio. Precharge of bit lines to full Vdd can alleviate the requirement for low-to-high cell transition current at the cost of the additional precharge time required for a full-Vdd precharge and the associated power consumption. The upper resistance limit on RL is put by the requirement. The lower limit on RL is put by the required noise immunity and power consumption requirements. The technological variations of RL caused by the limitations of doping and annealing techniques pose another constraint on the increase of RL.

Figure 1.1.1: 4T SRAM cell with Polysilicon Resistor Load

Ratioed inverters comprising the cell have lower gain in the transition region and produce in-

herently less steep VTCs, which reflects on the SNM values and the recovery time from a metastable state of such cells. The reduction of Vdd from the standard 5v to 3.3v,2.5v and so on, i.e., the switch from constant-voltage scaling to constant-filed scaling to combat the short-channel effects, revealed non-satisfactory low-voltage stability of PRL cells. Moreover, the extra technological steps of forming high-resistivity polysilicon are not a part of the standard logic technological steps of forming high-resistivity polysilicon are not a part of the standard logic technological process. Insufficient tolerance to soft errors, which is directly linked to the SNM, adds to the list of disadvantages of a PRL cell. These factors prohibit using the PRL SRAM cell in SoCs traditionally implemented using standard full CMOS process.

### **1.2 Conventional SRAM**

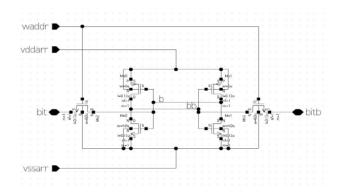

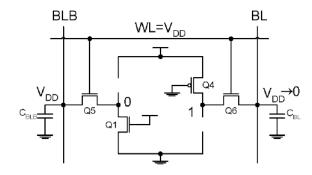

SRAM cell is the most important block of memory. SRAM called static random-access memory. It has a property to store the data for the long duration of time till power supply is provided. A 1-bit SRAM cell is made up of two inverters connected back-to-back (i.e. CMOS latch) with two complementary access transistors, with two stable states, whose output depend on the data stored in two inverters. The written data in the memory cell can be read as logic1or logic 0. The data can be accessed through bit lines (read and write operation) in SRAM cell as shown in Figure. It is most popular memory cell due to its high stability and lowest static power dissipation. When WL is enabled (i.e. WL=1) access transistors are turned ON for read and write operation which is connected to the bit lines of the cell.

Figure 1.2.1: SRAM Cell (6T)

**Write Operation:**In a write operation bl is charged to high (i.e. VDD) and blb is a charge to low, now word line is enabled (i.e. WL=1) and access transistors are turned ON and the information is stored into the SRAM Cell. After the fulfilment of write operation, the access transistors turn off, and data is stored for read operation.

**Read Operation:**In a read operation, both the bitlines is precharged to high (i.e. VDD) and the word line (i.e. WL=1) is enabled. It is well known that driver transistor has stronger driving strength than the access transistor because of one bitline is pulled down via memory cell. Thus, the information at bit lines will be sensed by SA.

SRAM v/s DRAM: RAMs can be categorized mainly into two types, each having its own advantages and disadvantages: SRAM and DRAM. Each of them holds the data in different way. Periodic refreshing of data is required in DRAM to retain the information while SRAM does not requires refreshing because the transistors indeed will continue to hold the data till the power supply is ON. This leads SRAM to have some advantages, one of which is faster speed for the read and write operation. In DRAM for refresh cycle, additional circuit and timing are needed which creates some complications and makes it slower as well as less desirable than the SRAM. One major disadvantage of DRAM is the much higher power consumption and dissipation because of the charging and discharging of capacitors. SRAM structure is rather simple as compared to DRAM and hence it is easier to create an interface to access the memory. A large number of transistors are required by the SRAM structure in order to store a certain amount of memory. On the other hand, DRAM structure needs a capacitor and transistor to store one bit of data whereas SRAM requires 6 transistors. The number of transistors used determines the storage capacity in a memory module.

So, a DRAM module will have 6 times more the capacity when compared to a SRAM module. This ultimately reduces the price which is the major concern for most of the buyers. As DRAM is cheaper, it has been the mainstream in computer for main memory despite of being slower and consuming more power compared to SRAM. On the other hand, SRAM is still used in devices where speed is a major concern rather than the capacity. SRAMs are mostly used in the cache memory of the processors where speed is more important. Optical drives, Hard drives and other devices use SRAM for cache memory and buffers.

### **1.3 SRAM Design parameters**

The proper designing of 6T SRAM bitcell is very important because it directly affects various parameters. For e.g. if we increase the pull-down transistor size significantly to improve the read operation, then there will be difficulty in write operation and the cell wont flip. Similarly, if we increase the pass transistor size to increase the read current then leak current and power dissipation also increases. So, one needs to size the transistors such that every parameter is optimized. The various design parameters include Read current, leak current, Read SNM (Static Noise Margin), Flip time, Read Margin etc. Here we will discuss them in detail.

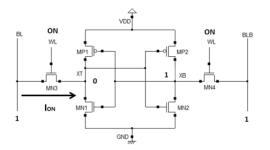

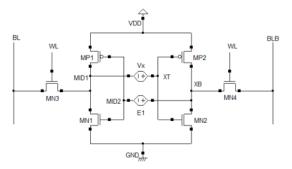

#### **1.3.1 Read current**

Figure 1.3.1: Iread in 6T SRAM

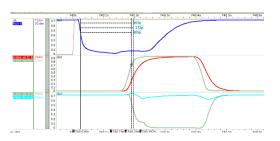

Figure shows how read current is measured. Read current is the current flowing through the pass transistor when word line turns ON for the read operation. When word line is turned ON, the pass transistor connected to node storing 0 is turned ON and current flows from bitline to ground via pull down transistor. As shown in the figure, XT is at 0 and XB is at 1. BL and BLB are precharged to VDD. Read current is the current flowing through MN3 when WL is turned ON. Read current should be as high as possible because it determines the worst read/leak ratio

through which we can estimate the maximum number of physical rows possible.

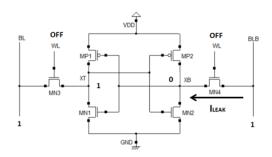

#### **1.3.2** Leak current

Leak current is the current flowing through the pass transistor when word line is OFF, and the cell is in idle state. Even when the word line is OFF, leakage current flows from bitline to ground via pass gate and pull-down transistor. As shown here in the figure, the cell is in idle state with XT and XB storage nodes at 1 and 0 respectively.

Figure 1.3.2: Ileake in 6T SRAM

Leak current is the current flowing through MN4 when wordline is OFF. Leak current should be as low as possible because it determines the worst read/leak ratio through which we can estimate the maximum number of physical rows possible. Leak current also determines the static power dissipation in the memory array. So large leakage current is not affordable since it can also flip the cell.

#### 1.3.3 Flip time

Flip time is the time required by the cell to flip its value. When we are performing write operation, one bitline is at VDD while other is at ground. When WL turns ON, bitline which is at VDD discharges and after some time cell flipping takes place. This time required to flip the cell is flip time. There are two ways to determine flip time. 1) WL driven: - For WL driven, it is the time required for cell to flip from WL rise 50% to the storage nodes getting flipped. 2) BL

driven: - For BL driven, it is the time required for cell to flip from 50% fall of BL to the storage nodes getting flipped.

#### **1.3.4** Static Noise Margin (SNM)

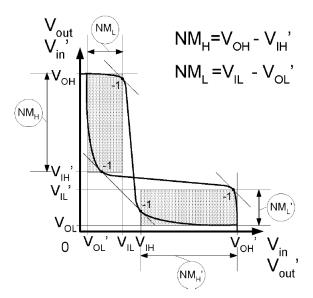

Static Noise Margin in 6T SRAM is the maximum noise voltage that can be tolerated at the storage nodes which does not flip the cell value. It is a very important design parameter as it determines the stability of the cell. The NM defined using the VTC. In general, the NM is the maximum spurious signal that can be accepted by the device when used in a system while still maintaining the correct operation. It is assumed that noise is present long enough for the circuit to react, i.e. the noise is static or dc.

An ideal inverter would have tolerated a change in the input voltage (Vin) without any change in the output voltage (Vout) until the input voltage reaches the switching point. The switching point is presented in fig. as dVout/dVin=1 the switching point of an ideal inverters is equidistant from the logic levels. However in real inverters the switching point is not equidistant from the logical levels and the transition region is characterized by the finite slope as shown in fig. SNM Definition: Noise margin high and noise margin low are defined as below, Where VIL is the maximum input voltage level recognized as logical 0, VIH is the minimum input voltage level recognized as a logical 1, VOL is the maximum logical 0 output voltage, VOH is the minimum logical 1 output voltage as shown in fig. NMH = VOH -VIH and NML = VIL - VOL

SNM can be determined by the butterfly curve as shown in figure above. This curve is nothing but VTC (Voltage Transfer Characteristic) of two back to back connected inverters. SNM is the largest possible square which can be fit in these curves. The next figure shows how we can actually measure SNM in 6T SRAM circuit. Noise can occur at any of the storage nodes. Here we take worst case possible where noise voltage is applied at both the storage nodes. Vx is voltage source and E1 is VCVS. When Vx is increased, E1 also increases. To measure SNM for this circuit WL is turned ON for read operation and simultaneously Vx is also increased.

Figure 1.3.3: SNM with VOH and VOL

The voltage Vx at which the cell flips are the SNM of 6T.

Figure 1.3.4: 6T SNM

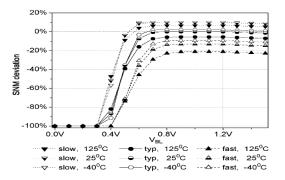

#### 1.3.5 SRAM SNM and Operating Voltage Variation

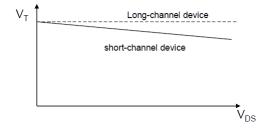

High temperature; the best case SNM occurs for the slow process corner and low temperature. Variation in the operating voltages, such as the supply (Vdd), bit line (Vbl) or word line (Vwl) voltages, strongly impact and SRAM cells SNM. The worst case SNM is typically observed for the fast process corner and high temperature the best case snm occurs for the slow process corner and low temperature. We swept Vdd,Vbl and Vwl one at a time from 0 to 1.5v and measured the corresponding snm. Fig depicts the SNM depends on Vbl while the Vdd, Vwl and Vblb are at the typical 1.2v the situation when one of the bit lines is driven from Vdd to the

ground corresponds to a wrte operation. Overwriting the data stored in a sram cell becomes zero at Vbl ¡0.3v for the typical process corner. Note that the SNM does not decreases immediately once Vbl start decreasing. The reduction of Vbl begins to reduce the SNM once Vbl-Vwl will be less then Vthaccess and the access transistors enters the linear mode.

Figure 1.3.5: SRAM cell SNM deviation vs. bit line voltage

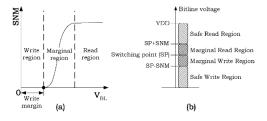

Fig a show the read and write regions of a SRAM cell as a function of the bit line voltage. A write operation is possible in the region where the bit line voltage is at or below the voltage point where the SNM is zero. This voltage region is called the write margin. The WM is an important design parameter as its also define the cell stability to various disturbances. A balance between cell stability (SNM), cell area and access speed (read current) must be found, which may not maximize the cell stability.

Figure 1.3.6: Read and Write safe and marginal regions of an SRAM cell

### 1.4 Disadvantages of 6T SRAM

6T SRAM is the most widely used for memory but with the advancement in CMOS technology and decreasing channel length, CMOS is facing lot of problems. At low channel length, stability, leakage current and power dissipation are of major concern. So, a more robust SRAM is required. The disadvantages of 6T are:

- Low cell stability

- Low read current

- High read time

- High leakage

- More power dissipation

- Cannot be operated at ultralow voltage

### **1.5** Motivation

Today, low power memory is given most priority in VLSI design. The power is most important aspect for todays technology. With the rapid progress in semiconductor technology, chip density and operation frequency have increased, making the power consumption in battery-operated portable devices a major concern. High power consumption reduces the battery service life. Speed, Size, and Price are the three major concern. By emerging battery-operated application on one hand and shrinking technologies of deep sub-micron (DSM) regime on the other hand, leakage power dissipation is rapidly playing a significant role in the total power dissipation as threshold voltage become small. Transistor leakage is a growing problem in re-configurable devices and will soon become the dominant source of power dissipation.

### 1.6 Objectives

The objective is to reduce the power requirement and leakage in memory by understanding the different parts of memory architecture and sub circuits used in memory chips.

• Optimize Memory architecture and bit-cell design.

- Low power memory techniques

- Test the design under the different checks by varying PVT.

- Understanding of the methodologies and tools used for testing.

## **1.7** Overview of the Thesis

In this thesis,

**Chapter 2** is the Literature Survey which will discuss about the common challenges faced in memory chip design, Process variation testing, memory architecture used for testing and importance of each component in memory architecture.

Chapter 3 will discuss about the read and write operation of memory.

Chapter 4 will discuss about the types of leakage current in device and power.

**Chapter 5** will discuss about the implementation of few of the test scenarios and the results obtained.

Chapter 6 will cover result discussion and work conclusion.

## Chapter 2

## **Literature Survey**

## 2.1 Introduction to Compiler

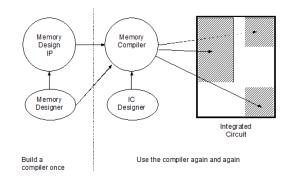

Compiler is software system that takes a users specification and automatically generates and IC. Compiler can be parameterized by number of words, number of bits per word, desired aspect ratio, number of sub banks, degree of column muxing, etc. Area, delay, and energy consumption complex function of design parameters of compiler. Memory Compilers and Logic Libraries supporting a wide range of foundries and process technologies from 250-nm to 7-nm FinFET. Optimized for low power, high performance and high density, Design Ware Memory Compilers offer advanced power management features such as light sleep, deep sleep, shut down and dual power rails, allowing designers to meet the stringent low-power requirements of today's SoCs.

- Pomwerful performance: A variety of memory compilers with multiple periphery VT options, power management modes and rich feature sets optimized for a wide range of applications.

- Proven Architecture, Flexible Design Options: Silicon-proven architecture provides optimized PPA for all types of SoC designs, ranging from performance-critical too costsensitive and low-power applications.

- Improve Yield: Memories support BIST and redundancy to improve yield and postsilicon performance tuning.

• Energy Efficient Design: Multiple power management modes support low leakage requirements for IoT SOC design.

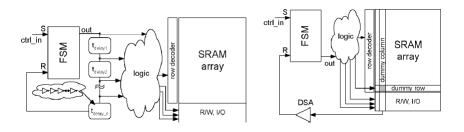

Figure 2.1.1: Compiler Architecture

## 2.2 High Speed Memory Compiler

7nm product family of memory compilers provides a powerful dashboard of options that enables SoC designers to explore trade-offs between performance, area, power, and statistical yield to generate optimal memory configurations.

#### **HSSP features: -**

- Memory instances optimized for speed, without compromising quality.

- Memory compilers that leverage the standard foundry delivered bit cells to ensure high yield and reliability.

- Memory compilers that provide an option for including redundancy capabilities for repair purposes.

- Memory compilers with options for advanced power management modes, such as Light Sleep, Deep Sleep and Shut Down.

- Proprietary circuit design techniques, including high-speed sense amplifiers, fast clocking, and fast bit line recovery, to achieve the high-speed required by todays high-performance applications.

High-Speed memory compilers offer six configuration modes, some of which provide features to support Test and Repair. Each of these features may be combined with advanced power management. They are classified based on built in muxes or bist enable, redundancy enable scan enable. They are defined as below:

- Lite mode without Built-in test muxes or repair.

- Lite Redundancy mode that adds redundancy to Lite mode.

- Integrated Test Lite mode that incorporates fully scannable input and output signals.

- STAR Lite mode that adds redundancy to IT-Lite.

- Integrated Test mode that incorporates built-in test muxes and other test circuitry to enable at-speed testing along with fully scannable input and output signals.

**Redundancy:** Redundancy is a system design in which a component is duplicated so if it fails there will be a backup. This feature enables the memory to repair bit-cell which are faulty. So the bit-cell which are faulty would be replaced by additional bit-cell.

**Read Margin Control:** All the arrays of bit-cell would have pre-charged before any operation will going to happen. During the read operation of memory disconnect the pre-charge signal for the selected cell and when the pre-charge is disconnected, one bit-line will start discharging towards the node where '0' is stored. the difference signal between two bit-lines will fed to sense amplifier and it will resolve the output, but it will resolve the output correctly when sufficient difference voltage will be created between two bit-line and that will ensure by RMcontrol.

**Dual Rail Functionality:** Separate voltage rails for the array and the periphery may be enabled at the instance level, with level shifters in the periphery. This will reduce dynamic power as well as static power but somehow these features will degrade the performance.

**BIST Interface:** This is an important feature of the memory compiler. It is the methodology at which circuit can verify its operation itself. After enabling this feature all bist design is activated and this would be test mode, so all the data or address comes from the external pin will isolated.

**Bit-write Feature:** In this feature can write a specific bit of word in memory instead of whole word. This feature would enable by external pin and it will all other bit of a word and the specific bit that will write in a memory will AND with the control signal and the specific bit will be written into the memory.

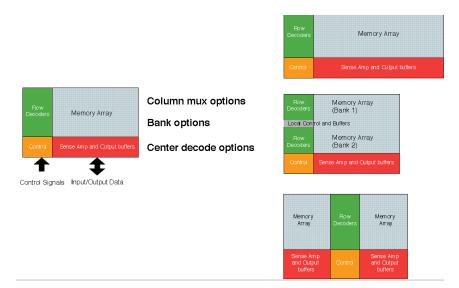

**Performance Boosters:** There are several performance boosting features available within the 7nm compilers. The performance enhancement obtained with each option. The Centre Decode option allows for a trade-off between area and performance. When center decode is set too TRUE, it improves instance performance at the cost of area. Banks (BK) Setting the number of banks provides a compile time option to split the memory into more than one bank. Memory banking is efficient for large instances. It improves performance and active power at the cost of area. Column Mux (CM) Allows you to change the aspect ratio of the instance for chip floorplan for a trade-off between area and performance.

**Optional Periphery Transistor Threshold Voltage Selection:** A compile-time option, periphery Vt, is offered to select the periphery transistor threshold voltage implant (Vt). The array transistor threshold implants remain unchanged by this compile-time option.Complier Provides power saving design techniques to implement these features:

- Source Biasing

- Fine-grained Power Gating

- Use of Long channel devices

- Integrated Power Gating

- Integrated Level Shifters

### 2.3 Monte Carlo Simulation

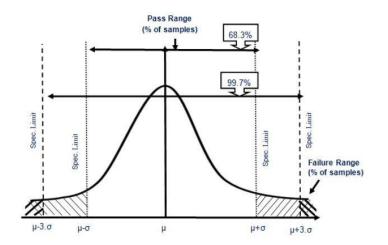

Leakage can easily be considered by this methodology by using Monte Carlo to characterize the leakage current of N worst-case cells as a lognormal. As technology is scaled down to leading edge nodes, chip design engineers face numerous challenges in maintaining the historical figures of performance improvement and the density increase. Performance of the chip, its lifetime and the product yield cannot be determined accurately at the design stage since the chip parameters- such as impurity doping and oxide thickness- cannot be precisely resolute. Process variation is one of the perilous aspects of semiconductor fabrication which impacts the chip performance, yield and the reliability. Process variation is basically defined as the variance in the intended design parameters and the actual (fabricated) design parameters of a circuit and hence reduce the reliability's and yields of chip designs. The relationship between parameter variation and the yield can be viewed in this figure.

Figure 2.3.1: Relationship between parameter verification and yield

It is important to use such design methodologies which consider the impact of process variation, environmental variation and the uncertainty in temperatures on the chip performance. To ensure the functionality of the design on silicon one must be able to replicate the variability on CAD tools in order to predict the yield. In other words, the design tools and the methodologies from system level down to physical level have to embrace variability impact on VLSI chips which requires "Statistical-analysis". For advanced processes, number of corners have expanded which leads to increased design efforts and prolonged time-to-market. Pre-defined corner simulations cannot predict the product yield as they characterize worst case corner only and are pessimistic in nature.

In VLSI circuit design during simulation, we run the design through various PVT (Process, voltage, and Temperature) corners with an aim that the circuit should be able to reliably operate at all the extreme conditions. These PVT variations can be generalized as,1) Temperature from as low as -40 to as high as 125C; 2)Voltage 10% variation from its nominal value; 3) Process This is generally two letter convention where first letter is the behaviour of NMOS and second letter is of PMOS. TT, SS, FF, SF and FS are the corners generally used. Letter T stands for Typical (Nominal VT), F for Fast (Low VT) and S for Slow (High VT).

#### 2.3.1 Global and Local MC

The Monte Carlo simulations can be done in two ways for any given design, Global Monte, and Local Monte. Again, the corner files for these two will be different. These are:

**Global Monte:** We can think of this Monte run as unconstrained in a way that the variations in this case can span over different process corners. In the figure, each dot represents one Monte Carlo run and as we can see it will spread the variation by introducing a VT change in its every single run. The span of the variations in this global Monte run is spread across the process corners as its name also suggests, Global MC.

**Local MC:** This Monte run is constrained to a particular process corner. In general, first step is to run the design at various PVT coroners to find the worst one. Then second step is to run the Monte on this particular corner to see the functionality on worst of worst corner. Let us say the worst corner in the first step was found to be SS then the Monte variations will look something like this, this is Local Monte as the scope of variations is limited to a particular corner. Both the methods have their own set of applications and used across industry to emulate the silicon behaviour during simulation and have a working silicon in one go.

### 2.4 Memory Architecture Blocks

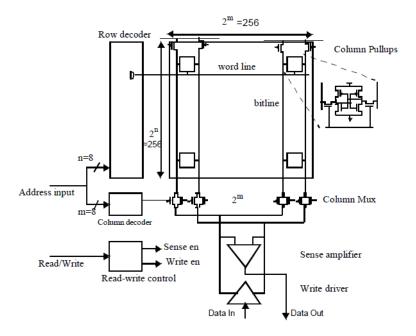

Figure 2.4.1: Basic SRAM block Structure

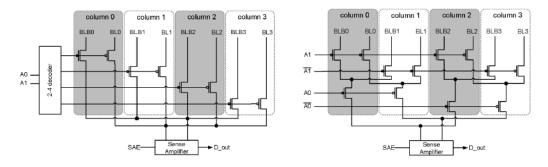

A row decoder gated by the timing block decodes X row address bits and selects one of the word lines WL0 to WLn-1. If an SRAM array of N rows and M buts is arranged in a page manner, an additional Z-decoder activates the accessed page. Above figure shows an example with four pages of NxM arrays with the corresponding I/O circuitry. Memories can be bit-oriented or word-oriented. In a bit-oriented memory, each address accesses a single bit. Whereas in a word-oriented memory, a word consisting of n (8,16,32 or 64) bits is accessed with each address. Column decoders or column MUXs (YMUX) addressed by Y address bits are often used to allow sharing of a single sense amplifier among 2,4 or more columns. Most of the modern SRAMs are self-timed. All the internal timing is generated by the timing block within an SRAM instance. The main SRAM building blocks will be described in more detail in the following sections.

#### 2.4.1 SRAM Design

The Memory chip architecture and its design flow should be understood properly for the integration in the Memory chip and its tastings. We will consider some of the more recent SRAM cells: a resistive load four-transistor(4T) SRAM cell, a six-transistor (6T) CMOS SRAM cell are already described in section 1 introduction.

**CR** (**cell ratio**): The deltaV depended on the CR. Large CR provides higher read current Iread (and hence -the speed) and SNM at the expense of larger area taken by the driver transistors. Whereas smaller CRs make for a more compact cell with moderate speed and noise margins. Both for ensuring cell stability and reducing the leakage current of the access transistors.

Figure 2.4.2: CR in SRAM

**PR (pull-up ratio):** To pull the write 1 node below Vthn, the W/L of the pull-up transistors has to be less than 3-4 W/L of the access transistors. The exact maximum allowed PR is defined by the Vthn process option and by the switching threshold of inverters.

#### 2.4.2 Precharge Circuit

To perform the read and write operation in SRAM the bit lines are charged through pre- charge circuit (PCH). PCH Circuit is made up of two PMOS transistors, whose output depends on PCH clock. During the charging of bit lines, a third transistor is placed between them for equalizing of any voltage difference on bit lines. It is mandatory to equalize the voltage on both bit lines

Figure 2.4.3: PR in SRAM

for proper read operation. As the read and write operations are completed a small variation in voltage is developed across both bit lines which require the PCH circuit to again pre-charge the bit lines equal to the supply voltage.

Figure 2.4.4: Precharge Circuit

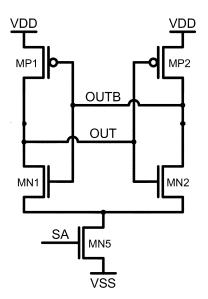

#### 2.4.3 Sense Amplifier

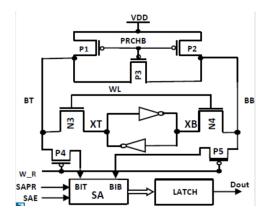

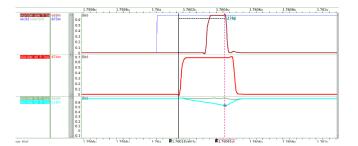

Sense Amplifier analysis to determine the offset, sense delay and its characterization methodology. Amplifies the differential voltage between bit-lines. Typically consists of cross-coupled inverters with stacked NMOS pull-down transistor. Major part of power consumption in memory system. Play dominant role during read operation. Different sensing schemes are there. The working principal of the SA is as follows: during read operations it senses small voltage difference between beltlines. Offset Voltage: It is a minimum differential voltage between beltlines.

After accessing the memory (Read cycle), a differential signal develops between the bitlines. This differential signal is fed to the input of the bitline sense amplifier to determine what data is stored in the bitcell. Since it takes time for the differential signal on the bitlines to develop, the greater the time delay prior to strobing the sense amplifier, the greater will be the differential signal at the input to the sense amplifier. A low sense amplifier differential signal is susceptible to noise and sense amplifier input voltage offset. Higher input differential voltage results in greater reliability of the sensed data. However, delaying the time when the sense amplifier is strobed results in a longer cycle time, reducing maximum operating speed and increasing access time. Hence the trade-off memory speed verses yield/reliability. The longer you wait, the easier it is for the sense amplifier to determine what was stored in the memory cell. Thus, the term Robustness. The longer you wait, the longer it takes to access the cell (i.e., access time). Thus, the term Speed Trade-off.

For read operation, we precharge RLB and RBLB both to VDD. Now suppose data stored at XT is 0 and that at XB is 1. We want to read XT i.e. 0. When wordline is turned ON, current starts to flow from RBL to pass gate to pull down transistor to ground. On the opposite side, no current flows because XB and RBLB both are at VDD. As current flows through XT, RBL discharges to ground. This discharge rate is very low since the sizing of transistors is very small. Hence, we need sense amplifier to sense this differential voltage and increase the read speed by pulling RBL to ground. When a sufficient differential voltage of about 50-100 mv is established between RBL and RBLB, SAE signal goes high and sense amp comes in the picture. The voltage at node QB is VDD and voltage at node Q is VDD-dV. Hence the Vgs of N2 will be lower than the Vgs of N1. So according to the drain current equation which depends directly on Vgs, the current flowing through N1 will be larger than the current flowing through N2. As these are cross coupled inverters, it forms a positive feedback and more current starts flowing through N1 as compared to N2. In this way node Q is pulled down to logic 0 before node QB because of the bistable nature of this structure. The node Q is connected to output data buffer. In this way sense amplifier increases the read speed because its size is much larger than the bitcell. For each column there is a sense amplifier, so we can afford larger sizing of its transistors because at a time only 1 cell will be operating in a column. Normally the size of sense amplifier transistors is about 10 times that of bitcell, but it may vary depending on the bitline load and speed requirement.

Figure 2.4.5: Sense Amplifier

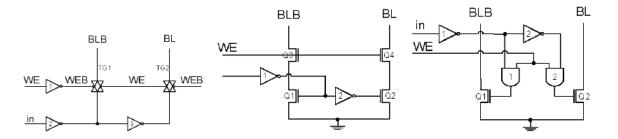

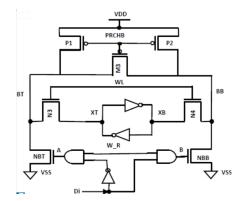

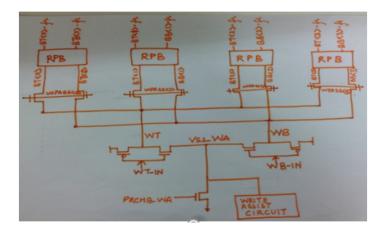

#### 2.4.4 Write Driver

The function of the SRAM write drivers is to quickly discharge one of the bit lines from the precharge level to below the write margin of the SRAM cell. Normally write driver is enabled by the write enable (WE) signals and drivers the bit line using full swing discharge from the precharge level to ground. A greater discharge of the highly capacitive bit lines is required for a write operation, a write operation can be carried out faster than a read operation. Only one write driver is needed for each SRAM column. Thus, the area impact of a larger write drivers is not multiplied by the number of cells in the column and hence the wryer drivers can be sized up if necessary. Some of the typical write driver circuits are presented in below figure.

Figure 2.4.6: Write Drivers

#### 2.4.5 Address Decoding Schemes in Memory

A decoding scheme is also discussed in this paper which describes how to choose the best predecoding and post-decoding schemes based on minimum pre-decoded lines, minimum stack size in post decoder and maximum granularity of xdecoders. In a typical random-access memory architecture, the row and column to be selected are determined by decoding binary address information. For example, an n-bit decoder for row selection has 2n output lines, one of which is activated. The column decoder takes m inputs and produce 2m bitline access signal. The bit selection is done using multiplexer circuit to direct the corresponding memory cell output to data registers. In total 2n \* 2m cells are stored in memory array. An n-bit decoder requires 2n logic levels, each with n inputs.

- Side Decode Addressing: Word lines other signals being driven from side. (Unbalanced, especially for wider memories) Power Compromised performance on wider memories.

- Center Decode Addressing: Word lines other signals being driven from center. (Balanced) Reduces RC delay Power improves performance.

- Memory Addressing: Addressing is considered as 2n, where n is the number of address bits.

Figure 2.4.7: 4-1 pass transistor Column Decoder with a read predecoder

For a 11 bit of address you can help manage addressing scheme in below fashion. LSB used for column decoding, MSB for Row decoding. If CM=4, A0 and A1 will be used for column decoding. A2-A10 will be used for 512 rows. If bank type architecture supported and bank=2, A2 will be used for bank and A3-A10 will be used for 256 rows.

(a) Divided Word Line (DWL) row decoder architecture.

(b) Hierarchical Word Decoding (HWD) [37] row decoder architecture.

Figure 2.4.8: DWL HWD Multi-Stage Row Decoder Architectures

#### 2.4.6 Timing control schemes

The timing control block controls precharge, word line, sense amplifier clocking and write drivers activation to ensure the correct write and read operation. If timing relation not ensure then timing hazards may arise like if the address changes before the read operation is complete. Suppose precharge is deactivated in this case more than one SRAM cell will be discharging the bit lines which may lead to reading erroneous data. Basic timing control methods employed in SRAM include Direct clocking, Self-timed replica loop and Delay line using a multitude of inverter to define the timing intervals.

Figure 2.4.9: Delay line timing Loop and Replica timing Loop

#### 2.4.7 Muxing and Banking

The two main options available to a memory compiler are the horizontal muxing (or banking depth) and the vertical partitioning. Consider an example 64-kbit memory logically organized as 2048 words of 32 bits each it would be impractical both from the memory design viewpoint and the system design viewpoint to implement this memory directly as an array of memory cells 2048 tall by 32 wides. Each word-width slice of memory can be referred to as a bank, and the total number of words on a row is the banking depth. By using one of these two techniques, the aspect ratio of the memory may be adjusted to a preferable physical aspect ratio.

This results in wasted dynamic power dissipation, which is the largest drawback of deep muxing. The main advantage of the banked approach is that extra circuitry may be added in between bank slices to disable unused memory banks when they are not accessed thereby saving dynamic power when compared to the interleaved muxing approach. Unfortunately, much of the power savings will be offset by the need to drive the bus to the mux elements at the bottom of the memory. The extra circuitry also requires more area to implement. For these reasons, interleaved muxing is the preferred solution for all but the very largest of memory instances (in the multi-megabit range).

#### 2.4.8 Level Shifter

Level Shifter circuitry is used to switch the voltage domain of the word line passing into the array of bit cells to a desired voltage. With this split, memory is able to execute in a dual rail mode which provides the flexibility to execute the core of the memory with a different voltage then the peripheral section of the memory. Generally Buffer type or Latch Type Level Shifters are available. A Level shifter is placed in the rail voltage domain of the cell. Otherwise a new voltage area is required for such Level Shifter placement. Level shifters are added to ensure that blocks operating at different voltages will operate correctly when integrated together in the SoC. Level shifters must ensure the proper drive strength and accurate timing as signals transition from one voltage level to another. Level shifters can be inserted during the synthesis or implementation stage. In memory for each block separate level shifter is being used mostly

we analyses the 3 blocks level shifter one wordline selection second control block and 3rd is lcen control block.

| Mode | BC2 | BC1 | LS | DS | SD | BC0 | Mode                                                  |

|------|-----|-----|----|----|----|-----|-------------------------------------------------------|